1

Изобретение относится к области вычислительной техники и может использоваться при построении интегральных запоминающих устройств для электронных вычислительных машин (ЭВМ) и устройств цифровой автоматики.

Известны полупроводниковые запоминающие устройства (ЗУ) динамического типа, построенные на элементах со взаимосвязанными п-р-п и р-п-р транзисторами 1. Основным недостатком этих устройств является разрушение информации при считывании.

Наиболее близким техническим решением является запоминающее устройство, содержащее матричный накопитель, каждая ячейка которого содержит п-р-п и р-п-р транзисторы, база п-р-п транзистора соединена с коллектором р-п-р транзистора, коллектор п-р-п транзистора соединен с базой р-п-р транзистора и разрядным формирователем и адресный формирователь 2.

Недостатком такого ЗУ является то, что считывание в нем происходит с разрещением информации, а это приводит к удлинению цикла обращения, поскольку при каждом считывании из матрицы необходимую вновь записывать считанную информацию, а это, в

свою очередь, усложняет схемы управления ЗУ. Разрушение информации, хранимой в виде зарядов на барьерных емкостях р-п переходов элемента, обусловлено тем, что прн считывании адресный формирователь подает импульс только на п-эмиттер прибора, а другой эмиттерный р-п пере.ход остается закрытым. В результате ток считывания протекает только через п-ргл транзистор элемента и вызывает изменение заряда на его коллекторной емкости.

Целью изобретения является повышение быстродействия устройства за счет неразрушающего считывания информации.

Поставленная цель достигается тем, что разнополярные выходы адресного формирователя подключены к эмиттерам п-р-п и р-п-р транзисторов соответственно, а тем, что адресный формирователь содержит многоэмиттерный транзистор, база которого подключена к первому резистору и базе первого транзистора, коллектор многоэмиттерного транзистора через диод подключен к базе второго транзистора, эмиттер которого подключен к шине нулевого потенциала и через второй резистор к эмиттеру первого транзистора, коллектор второго транзистора соединен с третьим резистором.

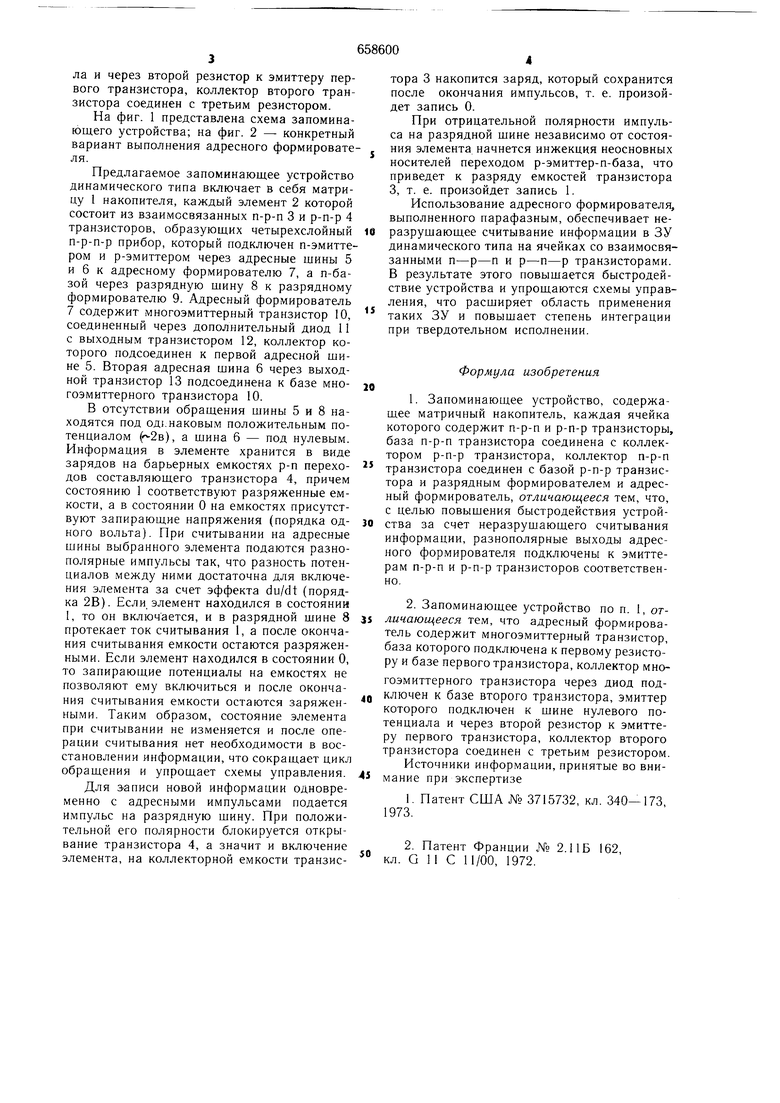

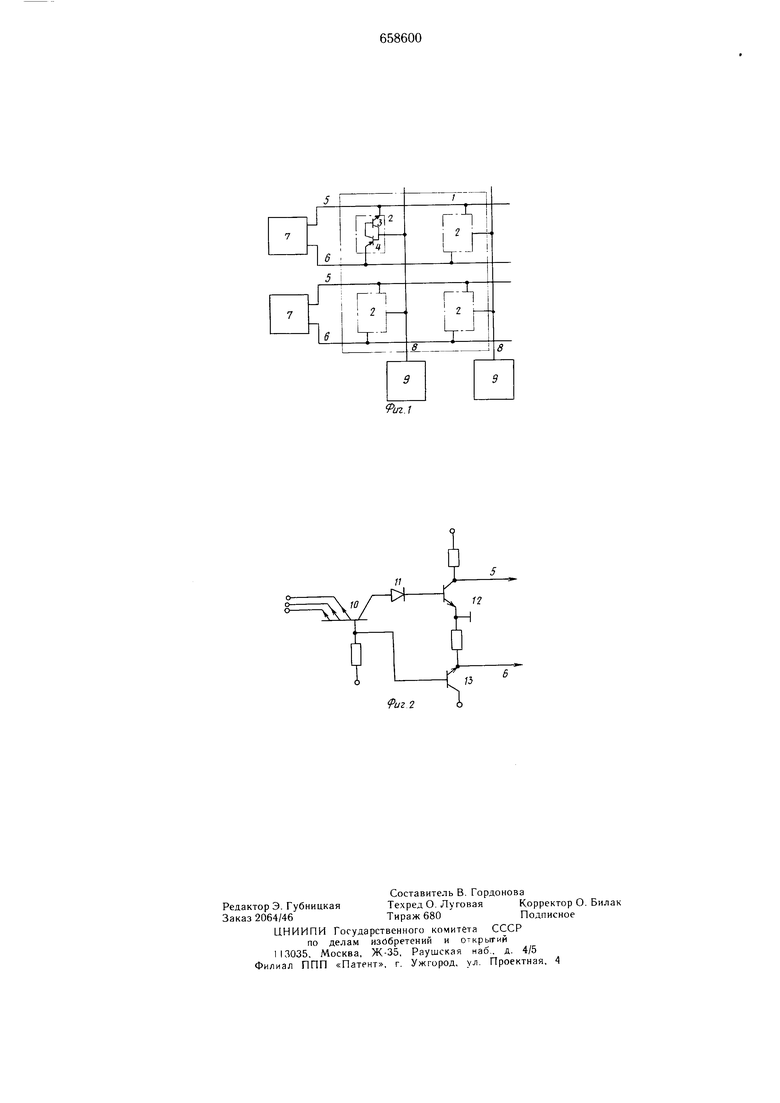

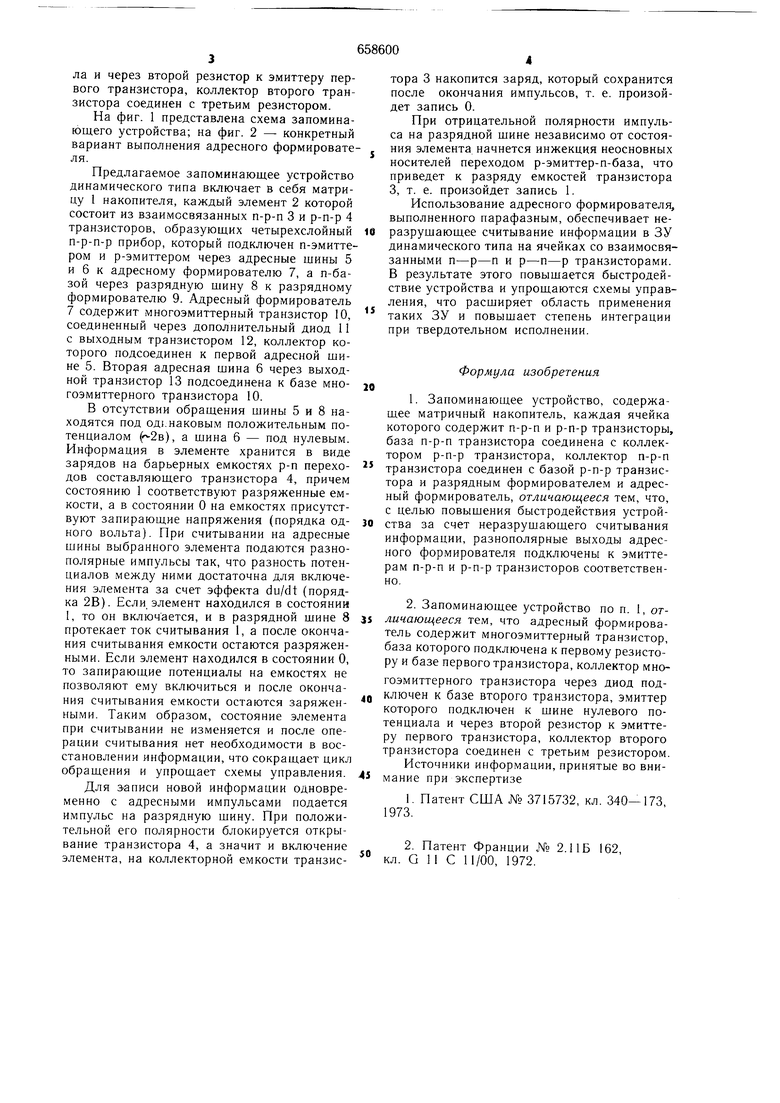

На фиг. 1 представлена схема запоминающего устройства; на фиг. 2 - конкретный вариант выполнения адресного формирователя.

Предлагаемое запоминающее устройство динамического типа включает в себя матрицу 1 накопителя, каждый элемент 2 которой состоит из взаимосвязанных п-р-п 3 и р-п-р 4 транзисторов, образующих четырехслойный п-р-п-р прибор, который подключен п-эмиттером и р-эмиттером через адресные шины 5 и 6 к адресному формирователю 7, а п-базой через разрядную шину 8 к разрядному формирователю 9. Адресный формирователь 7 содержит многоэмиттерный транзистор 10, соединенный через дополнительный диод 11 с выходным транзистором 12, коллектор которого подсоединен к первой адресной шине 5. Вторая адресная шина 6 через выходной транзистор 13 подсоединена к базе многоэмиттерного транзистора 10.

В отсутствии обращения шины 5 и 8 находятся под одкнаковым положительным потенциалом (), а шина 6 - под нулевым. Информация в элементе хранится в виде зарядов на барьерных емкостях р-п переходов составляющего транзистора 4, причем состоянию 1 соответствуют разряженные емкости, а в состоянии О на емкостях присутствуют запирающие напряжения (порядка одного вольта). При считывании на адресные шины выбранного элемента подаются разнополярные импульсы так, что разность потенциалов между ними достаточна для включения элемента за счет эффекта du/dt (порядка 2В). Если элемент находился в состоянии I, то он включается, и в разрядной щине 8 протекает ток считывания 1, а после окончания считывания емкости остаются разряженными. Если элемент находился в состоянии О, то запирающие потенциалы на емкостях не позволяют ему включиться и после окончания считывания емкости остаются заряженными. Таким образом, состояние элемента при считывании не изменяется и после операции считывания нет необходимости в восстановлении информации, что сокращает цикл обращения и упрощает схемы управления.

Для записи новой информации одновременно с адресными импульсами подается импульс на разрядную шину. При положительной его полярности блокируется открывание транзистора 4, а значит и включение элемента, на коллекторной емкости транзистора 3 накопится заряд, который сохранится после окончания импульсов, т. е. произойдет запись 0.

При отрицательной полярности импульса на разрядной шине независимо от состояния элемента начнется инжекция неосновных носителей переходом р-эмиттер-п-база, что приведет к разряду емкостей транзистора 3, т. е. произойдет запись 1.

Использование адресного формирователя, выполненного парафазным, обеспечивает неразрущающее считывание информации в ЗУ динамического типа на ячейках со взаимосвязанными п-р-п и р-п-р транзисторами. В результате этого повыщается быстродействие устройства и упрощаются схемы управления, что расщиряет область применения таких ЗУ и повышает степень интеграции при твердотельном исполнении.

Формула изобретения

. Запоминающее устройство, содержащее матричный накопитель, каждая ячейка которого содержит п-р-п и р-п-р транзисторы, база п-р-п транзистора соединена с коллектором р-п-р транзистора, коллектор п-р-п

транзистора соединен с базой р-п-р транзистора и разрядным формирователем и адресный формирователь, отличающееся тем, что, с целью повышения быстродействия устройства за счет неразрушающего считывания информации, разнополярные выходы адресного формирователя подключены к эмиттерам п-р-п и р-п-р транзисторов соответственно.

2. Запоминающее устройство по п. 1, отличающееся тем, что адресный формирователь содержит многоэмиттерный транзистор, база которого подключена к первому резистору и базе первого транзистора, коллектор многоэмиттерного транзистора через диод подключен к базе второго транзистора, эмиттер которого подключен к шине нулевого потенциала и через второй резистор к эмиттеру первого транзистора, коллектор второго транзистора соединен с третьим резистором.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3715732, кл. 340-173, 1973.

2. Патент Франции № 2.11Б 162, кл. G 11 С 11/00, 1972.

6 :

г

г

пг

Г

У

Pin.l

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| Запоминающее устройство | 1976 |

|

SU608197A1 |

| Полупроводниковое постоянное запоминающее устройство | 1978 |

|

SU886053A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Запоминающее устройство | 1985 |

|

SU1305774A2 |

| Запоминающее устройство | 1985 |

|

SU1310896A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1575234A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1983 |

|

SU1088068A1 |

| Матричный накопитель | 1986 |

|

SU1343443A1 |

fuz2

Авторы

Даты

1979-04-25—Публикация

1974-11-10—Подача