Ua

US

Uc

S

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноканальное устройство для управления многофазным тиристорным регулятором напряжения | 1981 |

|

SU1053257A1 |

| Устройство для одноканального управления преобразователем на двухоперационных вентилях | 1988 |

|

SU1536491A1 |

| Одноканальное устройство для управления многофазным тиристорным преобразователем | 1987 |

|

SU1436220A1 |

| Устройство для управления преобразователем с непосредственной связью,питающим вентильный двигатель | 1984 |

|

SU1310967A1 |

| Устройство для управления вентильным преобразователем | 1984 |

|

SU1251260A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1589395A1 |

| Дискретно-цифровой электропривод | 1985 |

|

SU1350800A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1991 |

|

SU1797158A1 |

| Устройство для одноканального фазового управления вентильным преобразователем | 1982 |

|

SU1083325A1 |

| Устройство для управления параллельным инвертором тока с выпрямительно-индуктивным компенсатором | 1991 |

|

SU1781804A1 |

Изобретение относится к электротехнике и может быть использовано в тирис- торных преобразователях. Цель изобретения - упрощение. За счет введения блока запуска 6 и блока блокировки запуска 8 и выполнения распределителя 4 по кольцевой схеме обеспечивается упрощение схемы при сохранении функциональных возможностей. 2 ил.

GO ГО

СО

Изобретение относится к электротехнике и может быть использовано для управления многофазными тиристорными преобразователями.

Цель изобретения - упрощение устройст-. ва для управления многофазными тиристорными преобразователями.

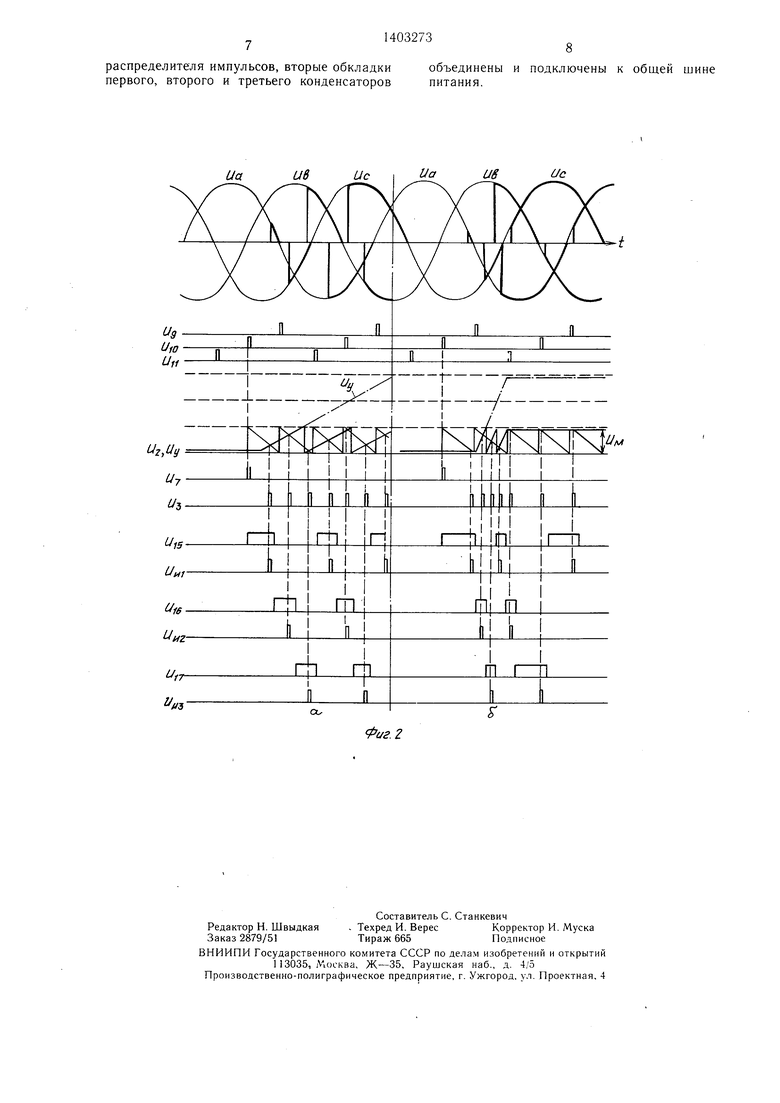

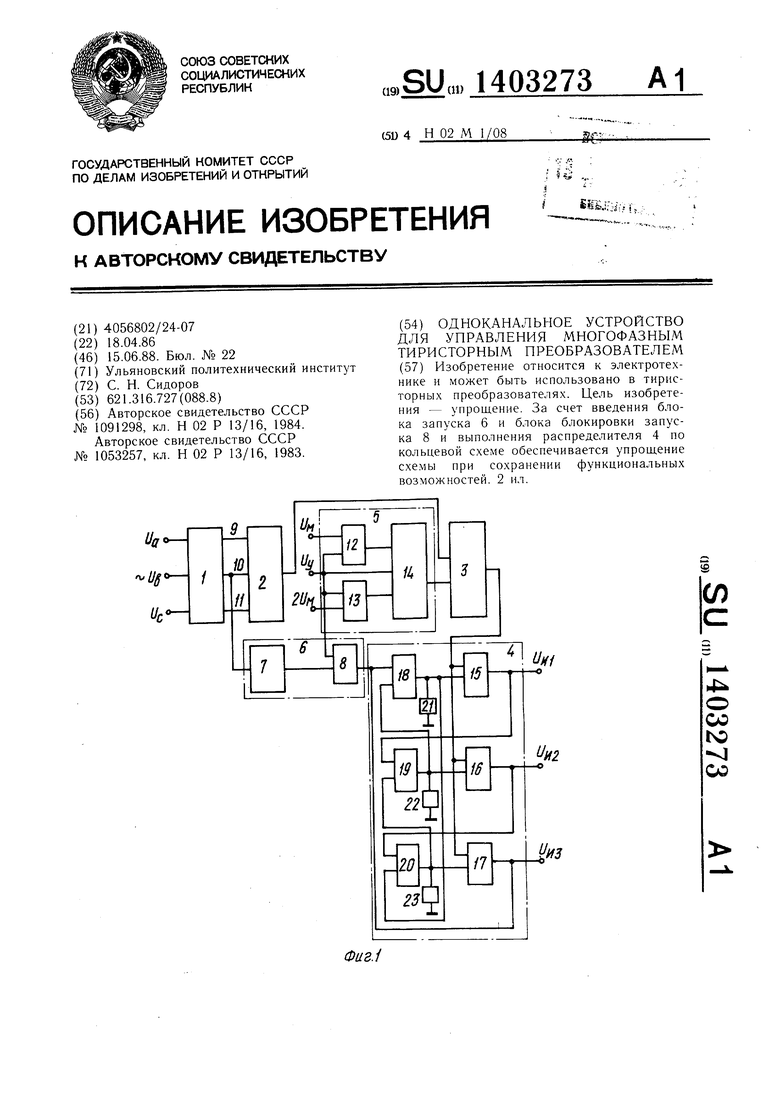

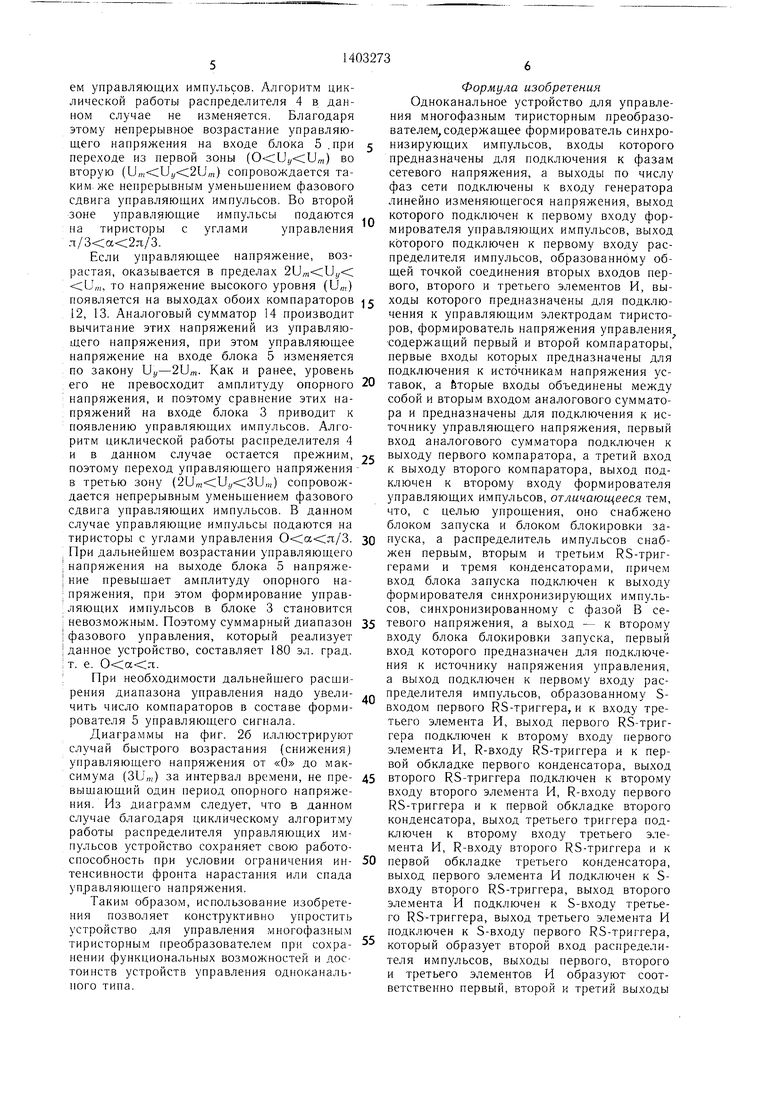

На фиг. 1 представлена схема устройства; на фиг. 2 - временные диаграммы, поясняющие работ у устройства в случаях сравнительно медленного (а) и быст- рого (б) возрастания управляющего напряжения по линейному закону.

Устройство содержит формирователь 1 синхронизирующих импульсов, генератор 2 линейно изменяющегося напряжения, форми- рователь 3 управляющих импульсов, распределитель 4 управляющих импульсов, формирователь 5 yпpaвляюпJ.eгo напряжения и блок 6 запуска, содержащий формирователь 7 импульсов запуска и блок 8 блокировки запуска. Фор1мирователь синхрони- зирующих импульсов имеет три выхода 9-11 по числу силовых тиристоров, формирователь управляющего напряжения содержит компараторы 12, 13 и аналоговый сумматор 14, распределитель управляюпдих им- пульсов содержит двухвходовые элементы И 15-17 и RS-триггеры 18-20 с параллельно подключенными на выходах конденсаторами 21-23.

Формирователь I синхронизирующих им- пульсов входами подключен к источнику трехфазного сетевого напряжения, а выходами 9-II - к входу генератора линейно изменяющегося напряжения. Выход последнего подключен к первому входу формирователя 3 управляющих импульсов, выход которого связан с параллельно соединенными первыми входами элементов И 15-17. Компаратор 12 первым входом подключен к источнику напряжения уставки (Um), а компаратор 13 первым входом - к ис- точнику двойного напряжения уставки (2Um)- Вторыми входами оба компаратора подключены к источнику напряжения управления (Uy), а выходами вместе с выходом источника управляющего напряжения соединены с входом аналогового сумматора 14, при этом выход последнего подключен к второму входу формирователя 3 управляющих импульсов. Элементы И 15-17 и RS- триггеры 18-20 образуют кольцевую схему распределителя управляющих импульсов. При этом триггер 18 выходом подключен к второму входу эле.мента И 15, а также к R-входу триггера 20. Выход элемента И 15, предназначенный для подключения к управляющему входу тиристора фазы А, подключен к S-входу триггера 19, выход которого подключен к второму входу элемента И 16, а также к R-входу триггера 18. Выход элемента И 16, предназначенный для подключения к управляю;

20 25

ЗО 35 .- 45 50

55

щему входу тиристора фазы С, подключен к S-входу триггера 20, выход которого подключен к второму входу элемента И 17 и R-входу триггера 19. Выход элемента И 17 подключен к S-входу триггера 18 и служит для подключения к управляюще.му входу тиристора фазы В. S-вход триггера 18 подключен также к выходу блока 8 блокировки запуска, одним входом подключенного к источнику управляющего напряжения (U,), а вторым входом - к выходу формирователя 7 импульсов запуска, вход которого подключен к выходу формирователя 1 синхроимпульсов фазы В.

Работу устройства рассмотрим применительно к трехфазному регулятору напряжения, выполненному на симметричных тиристорах (симисторах).

Устройство работает следующим образом.

Первоначальный запуск устройства осуществляется подачей напряжений питания, а также напряжений сети на входы блока 1 и уставок на входы блоков 12, 13. Запуск должен осуществляться при нулевом или достаточно малом напряжении управления на входе блока 5, не превыщаю- щем амплитуды опорного напряжения U,,U,,,. В противном случае выход блока 6 запуска оказывается блокирован с помощью элемента 8, в результате запуск не состоится и его следует повторить после установки требуемой величины начального напряжения управления. Необходимо также, чтобы триггеры 18-20 находились в первый мо.мент после осуществления запуска в исходном состоянии «О.

При подаче напряжений сети на входы блока 1 на его выходах формируются кратковременные синхронизирующие импульсы, совпадающие с моментами прохождения фазных напряжений сети через нуль (фиг. 2). При этом импульсы на выходе 9 опережают на л/3 радиан импульсы на выходе 10, а последние также на л/3 радиан опережают импульсы на выходе 11. С приходом каждого синхроимпульса происходит запуск генератора 2 периодически изменяющегося опорного напряжения пилообразной формы, поэтомучастота этого напряжения в 6 раз превышает частоту сетевого напряжения и имеет амплитудное значение U,,,. Одновременно с эти.м первый синхроимпульс, выделивн1ИЙся на одном из выходов блока 1, например на выходе 10, синхронизируемом напряжением фазы В, поступает также на вход формирователя 7 запускающих импульсов. Данный формирователь представляет собой одновибратор, срабатывание которого происходит однократно после подачи напряжения питания в момент поступления на его вход первого синхроимпульса. При срабатывании на выходе формирователя выделяется такой

же кратковременный импульс, который подается далее на один из входов блока 8. При условии, НТО на втором его входе присутствует достаточно малое напряжение управления Uj,Um, запускающий импульс пропущен этим блоком на свой выход, а далее - на S-вход триггера 18. Происходящий при этом переход указанного триггера в единичное состояние приводит к появлению на втором входе элемента И 15 напряжения высокого уровня. При этом данный элемент подготовлен к тому, чтобы первый управляющий импульс, выделивщий- ся на выходе формирователя 3, был пропущен этим элементом на управляющий вход тиристора фазы А. При этом поступление сигнала высокого уровня с выхода триггера 18 на R-вход триггера 20 не изменяет исходное состояние последнего.

После осуществления запуска управляющее напряжение на входе блока 5 может принимать ненулевые значения Рассмотрим работу устройства при возрастании управляющего напряжения по линейному закону (фиг. 2). Возрастание управляющего напряжения сопровождается появлением на выходах компараторов 12, 13 напряжения нулевого или высокого уровней в зависимости от того, в каких пределах находится в данный момент величина управляющего напряжения. При этом напряжение высокого уровня должно быть точно равно амплитуде опорного напряжения U.

Тогда, если управляющее напряжение находится в пределах , на выходах обоих компараторов в результате сравнения управляющего напряжения с напряжениями уставок выделяется напряжение нулевого уровня. При этом на вход аналогового сумматора 14 подается лищь управляющее напряжение Uy. Повторившееся значение управляющего напряжения с выхода аналогового сумматора поступает на вход формирователя 3 управляющих импульсов, на котором производится сравнение этого напряжения с опорным. В моменты равенства этих двух напряжений на выходе блока 3 формируются управляющие импульсы для всех трех тиристоров. Фаза этих импульсов относительно начала полуволн сетевых напряжений в соответствии с известным вертикальным принципом зависит от величины управляющего сигнала. Далее управляющие импульсы постулают на параллельно включенные первые входы элементов И 15-17 распределителя 4. К моменту поступления первого управляющего импульса после запуска лищь один из элементов И распределителя, а именно элемент И 15, готов передать этот импульс на свой выход. Остальные элементы И 16, 17 блокированы, так как к этому моменту триггеры 19, 20 находятся в состоянии «О. В даль- нейщем работа каналов распределителя

происходит по принципу кольцевой схемы. Сформированный на выходе элемента И 15 управляющий импульс подается на управляющий электрод тиристора фазы А и одновременно на S-вход очередно о триггера 19. Последующий за этим переход триггера 19 в единичное состояние приводит к появлению напряжения высокого уровня на втором входе элемента 14 16. Одновременно с этим

Q положительное напряжение с выхода триггера 19 поступает на R-вход предыдущего триггера 18, возвращая последний в исходное нулевое состояние. Благодаря, наличию параллельного конденсатора на выходе триггера 18 возврат этого триггера

в нулевое состояние не приводит к мгновенному блокированию элемента И 15, поэтому управляющий импульс, выделивщийся на выходе данного элемента, имеет необходимую конечную длительность. Теперь к

моменту поступления с выхода формирователя 3 второго управляющего импульса в подготовленном состоянии оказывается элемент И 16, а остальные элементы И 15-17 распределителя блокированы. Второй управляющий импульс подается с выхода эле5 мента И 16 на управляющий вход тиристора фазы С и одновременно на S-вход очередного триггера 20. Единичный уровень напряжения с выхода триггера 20 подается на R-вход триггера 19, что приводит к возврату последнего в исходное

состояние и последующей блокировке элемента И 16. Одновременно с этим напряжение высокого уровня подается на второй вход элемента И 17, и он оказывается в подготовленном состоянии. Так как остальные элементы И 15, 16 распределителя

5 в это время блокированы, третий управляющий импульс с выхода формирователя 3 пропускается элементом И 17 на тиристор фазы В, а также на S-вход триггера 18. В дальнейшем работа устройства

0 происходит аналогично. В связи с тем, что управляющее напряжение по уровню не превышает амплитуду опорного сигнала, управляющие импульсы подаются на тиристоры в данном случае с углами управления .

5 Если управляющее напряжение возрастает и оказывается в пределах U,,,,,,,TO на выходе компаратора 12 появляется напряжение высокого уровня (U,,,), а на выходе компаратора 13 напряжение по-прежнему нулевое. На входе аналогового сумматора

0 выходные напряжения компараторов вычитаются из управляющего напряжения, при этом на выходе сумматора 14 формирует- . ся управляющее напряжение, изменяющееся по закону и,,- и„|. Как видно из диас грамм на фиг. 2, это напряжение по уровню не превосходит амплитуду опорного напряжения, поэтому сравнение управляющего и опорного напряжений на входе блока 3 по-прежнему сопровождается формированием управляющих импульсов. Алгоритм циклической работы распределителя 4 в данном случае не изменяется. Благодаря этому непрерывное возрастание управляющего напряжения на входе блока 5 .при переходе из первой зоны (,) во вторую (U,,,,,,) сопровождается таким, же непрерывным уменьщепием фазового сдвига управляющих импульсов. Во второй зоне управляющие импульсы подаются на тиристоры с углами управления ..

Если управляющее напряжение, возрастая, оказывается в пределах ,, ;U,,,, то напряжение высокого уровня (U) появляется на выходах обоих компараторов 12, 13. Аналоговый сумматор 14 производит вычитание этих напряжений из управляющего напряжения, при этом управляющее напряжение на входе блока 5 изменяется по закону Uj,-2и„|. Как и ранее, уровень его не превосходит амплитуду опорного напряжения, и поэтому сравнение этих напряжений на входе блока 3 приводит к появлению управляющих импульсов. Алгоритм циклической работы распределителя 4 и в данном случае остается прежним, поэтому переход управляющего напряжения в третью зону ,,;3Um) сопровождается непрерывным уменьшением фазового сдвига управляющих импульсов. В данном случае управляющие импульсы подаются на тиристоры с углами управления . При дальнейщем возрастании управляющего напряжения на выходе блока 5 напряже- ; ние превыщает амплитуду опорного на- : пряжения, при этом формирование управ- ляющих импульсов в блоке 3 становится ; невозможным. Поэтому суммарный диапазон : фазового управления, который реализует I данное устройство, составляет 180 эл. град. ; т. е. .

: При необходимости дальнейшего расщи- рения диапазона управления надо увеличить число компараторов в составе формирователя 5 управляющего сигнала.

Диаграммы на фиг. 26 иллюстрируют случай быстрого возрастания (снижения) управляющего напряжения от «О до максимума (Зи,,,) за интервал времени, не превышающий один период опорного напряжения. Из диаграмм следует, что в данном случае благодаря циклическому алгоритму работы распределителя управляющих импульсов устройство сохраняет свою работоспособность при условии ограпичения интенсивности фронта нарастания или спада управляющего напряжения.

Таким образом, использование изобретения позволяет конструктивно упростить устройство для управления многофазным тиристорным преобразователем при сохранении функциональных возможностей и достоинств устройств управления одноканаль- ного типа.

5

0

5

0

5

0

5

0

5

Формула изобретения Одноканальное устройство для управления многофазным тиристорным преобразователем, содержащее формирователь синхронизирующих импульсов, входы которого предназначены для подключения к фазам сетевого напряжения, а выходы по числу фаз сети подключены к входу генератора линейно изменяюплегося напряжения, выход которого подключен к первому входу формирователя управляющих импульсов, выход которого подключен к первому входу распределителя импульсов, образованному общей точкой соединения вторых входов первого, второго и третьего элементов И, выходы которого предназначены для подключения к управляющим электродам тиристоров, формирователь напряжения управления содержащий первый и второй компараторы, первые входы которых предназначены для подключения к источника.м напряжения уставок, а бторые входы объединены между собой и вторым входом аналогового сумматора и предназначены для подключения к источнику управляющего напряжения, первый вход аналогового сумматора подключен к выходу первого компаратора, а третий вход к выходу второго компаратора, выход подключен к второму входу формирователя управляющих импульсов, отличающееся тем, что, с целью упрощения, оно снабжено блоком запуска и блоком блокировки запуска, а распределитель импульсов снабжен первым, вторым и третьим RS-триг- герами и тремя конденсаторами, причем вход блока запуска подключен к выходу формирователя синхронизирующих импульсов, синхронизированному с фазой В сетевого напряжения, а выход - к второму входу блока блокировки запуска, первый вход которого предназначен для подключения к источнику напряжения управления, а выход подключен к первому входу распределителя импульсов, образованному S- входом первого RS-триггера, и к входу третьего элемента И, выход первого RS-триггера подключен к второму входу первого элемента И, R-входу RS-триггера и к первой обкладке первого конденсатора, выход второго RS-триггера подключен к второму входу второго элемента И, R-входу первого RS-триггера и к первой обкладке второго конденсатора, выход третьего триггера подключен к второму входу третьего элемента И, R-входу второго RS-триггера и к первой обкладке третьего конденсатора, выход первого элемента И подключен к S- входу второго RS-триггера, выход второго элемента И подключен к S-входу третьего RS-триггера, выход третьего эле.мента И подключен к S-входу первого RS-триггера, который образует второй вход распределителя импульсов, выходы первого, второго и третьего элементов И образуют соответственно первый, второй и третий выходы

распределителя импульсов, вторые обкладкиобъединены и подключены к общей шине

первого, второго и третьего конденсаторовпитания.

OU

| Устройство для одноканального фазового управления тиристорным преобразователем | 1982 |

|

SU1091298A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Одноканальное устройство для управления многофазным тиристорным регулятором напряжения | 1981 |

|

SU1053257A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1988-06-15—Публикация

1986-04-18—Подача