Изобретение относится к измерительной технике, а именно к устройствам для измерения разности фаз двух напряжений, и может быть испол зовано в радиотехнических устройствах, а также в следящих многодвигательных электроприводах.

Цель изобретения - повьшение точности и расширение диапазона рабочих частот фазового дискриминатора.

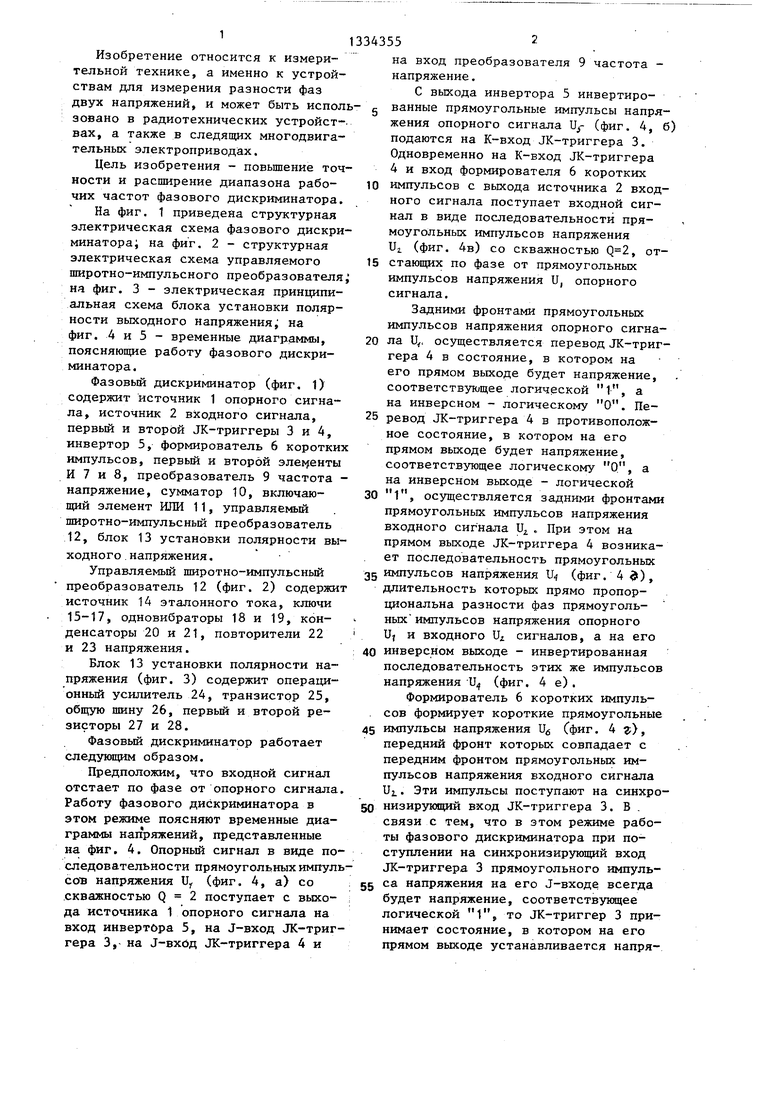

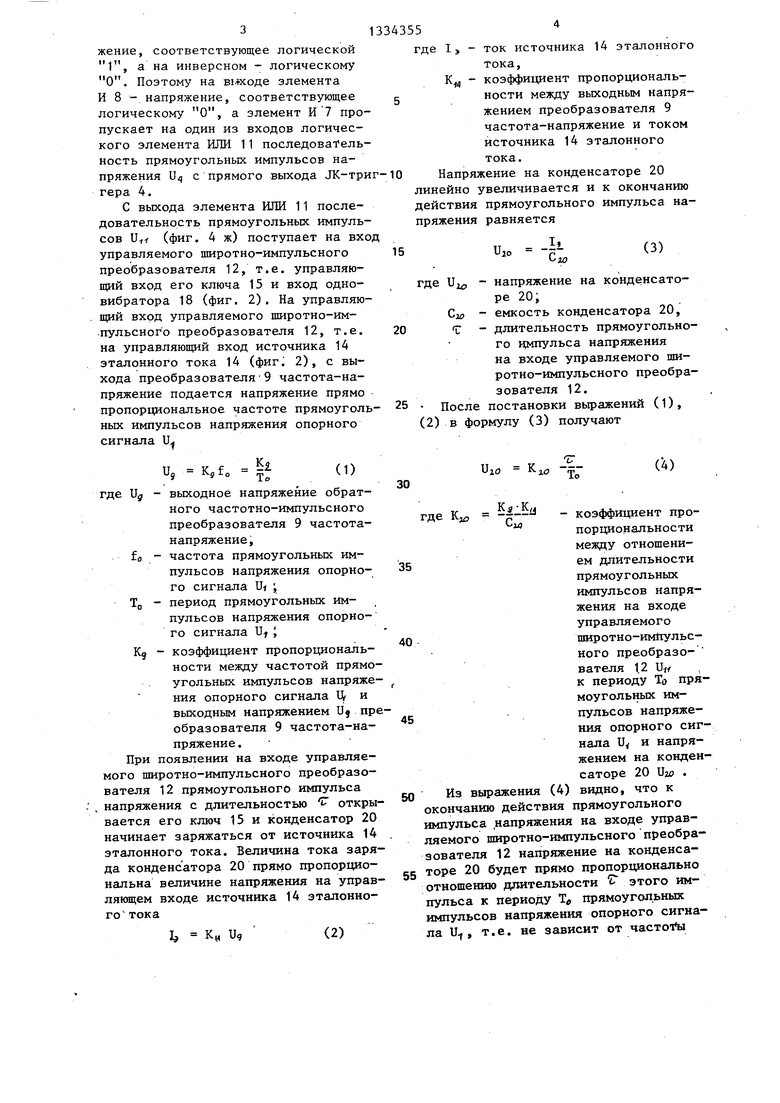

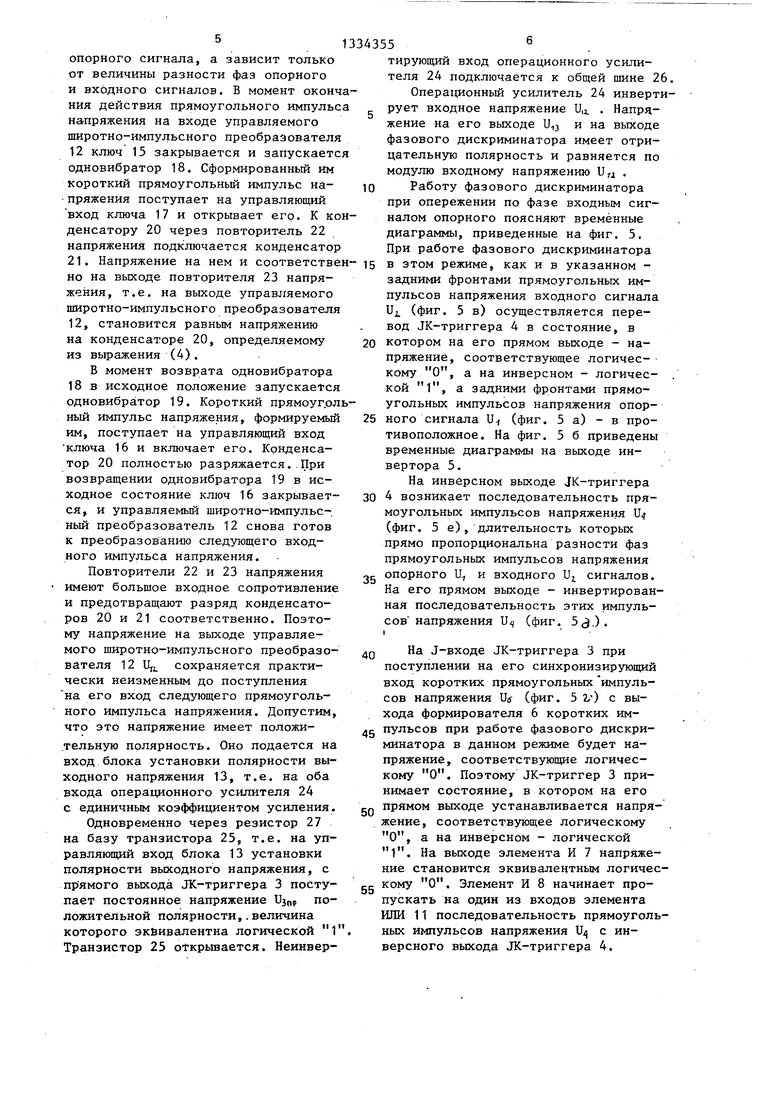

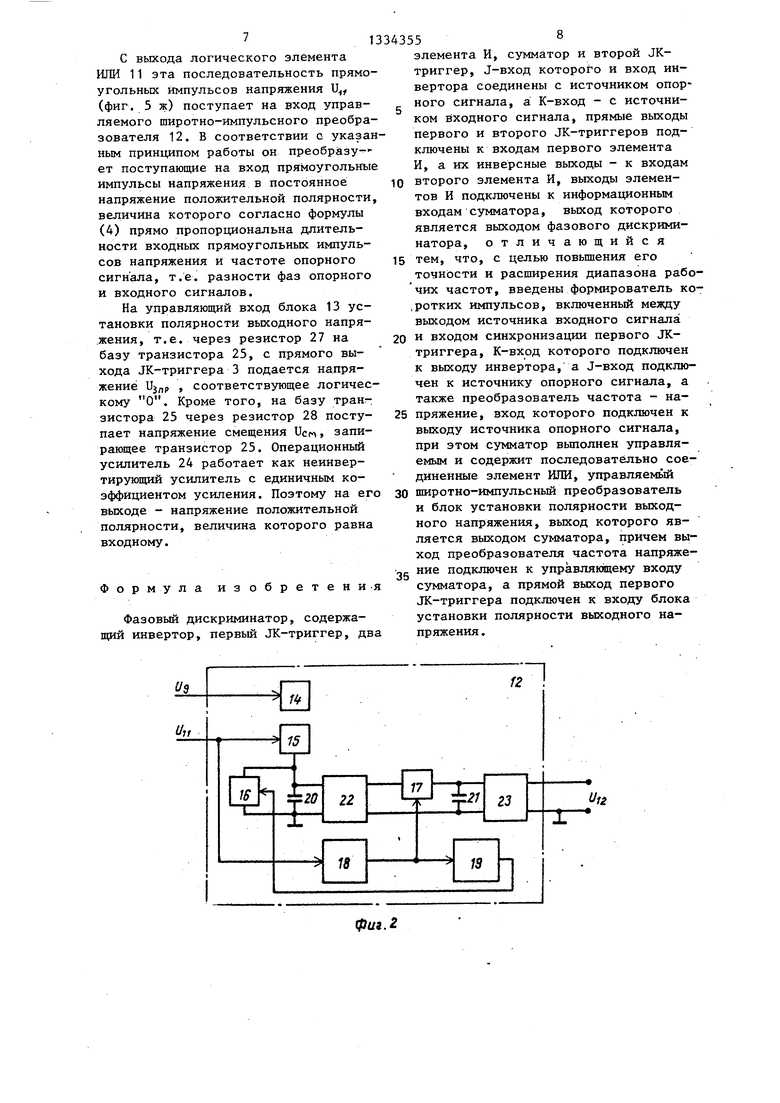

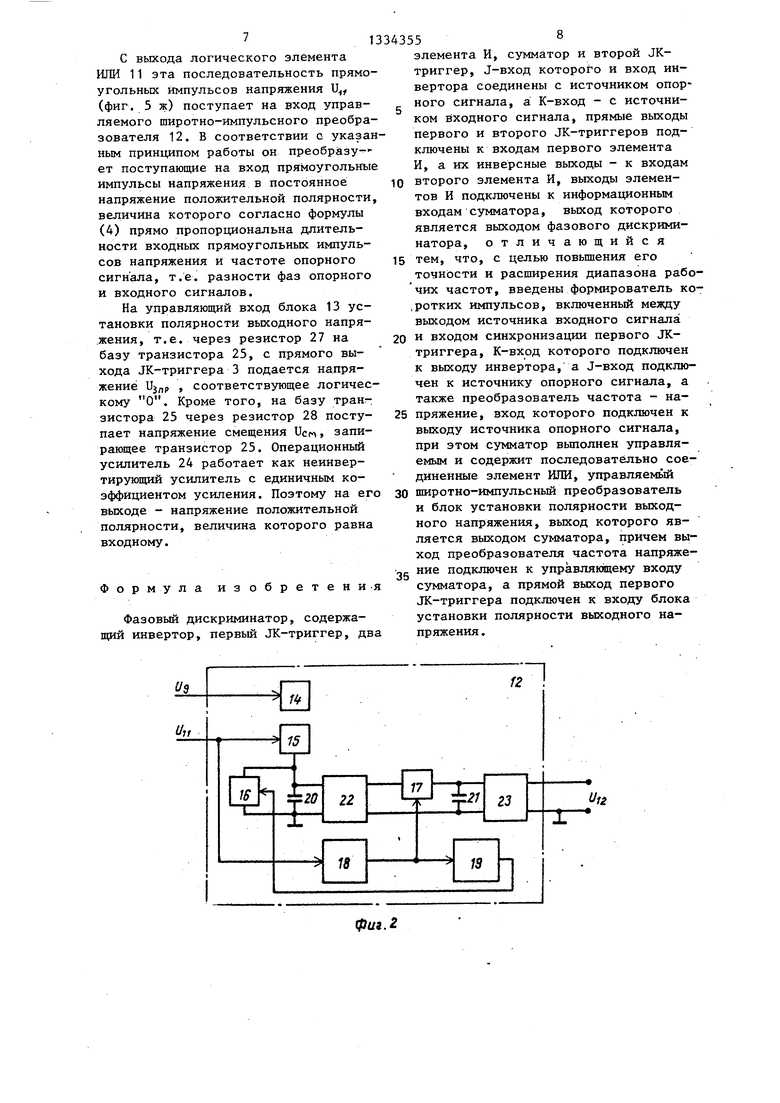

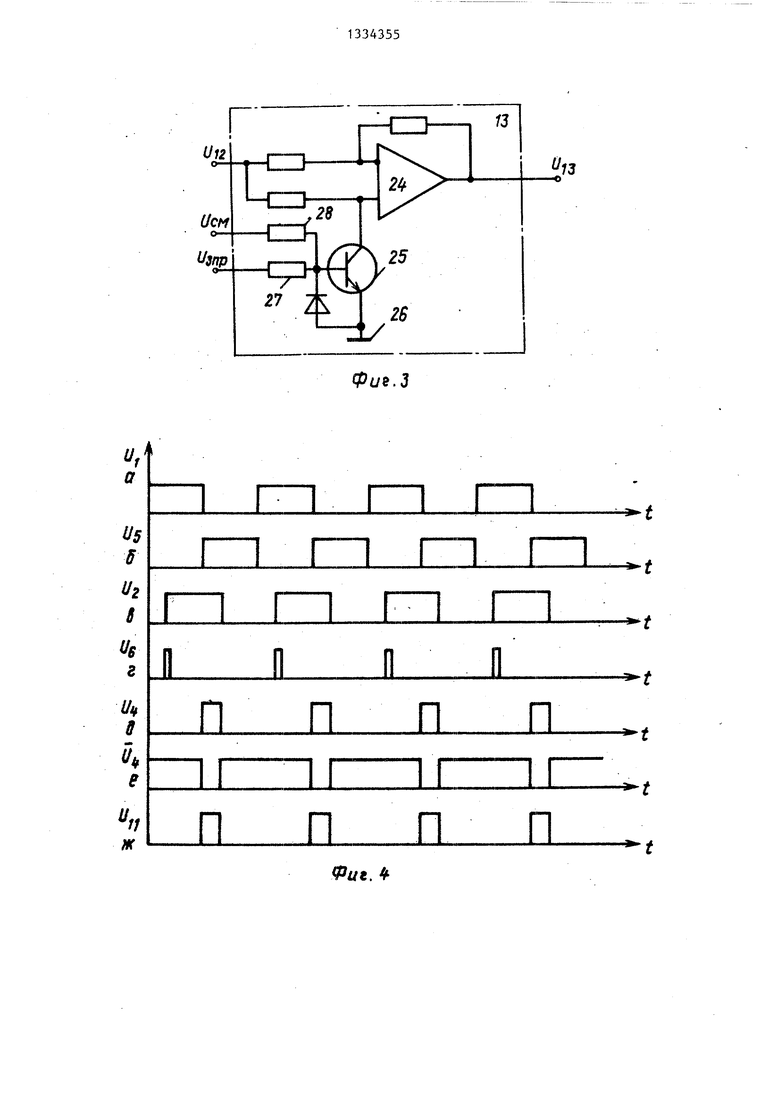

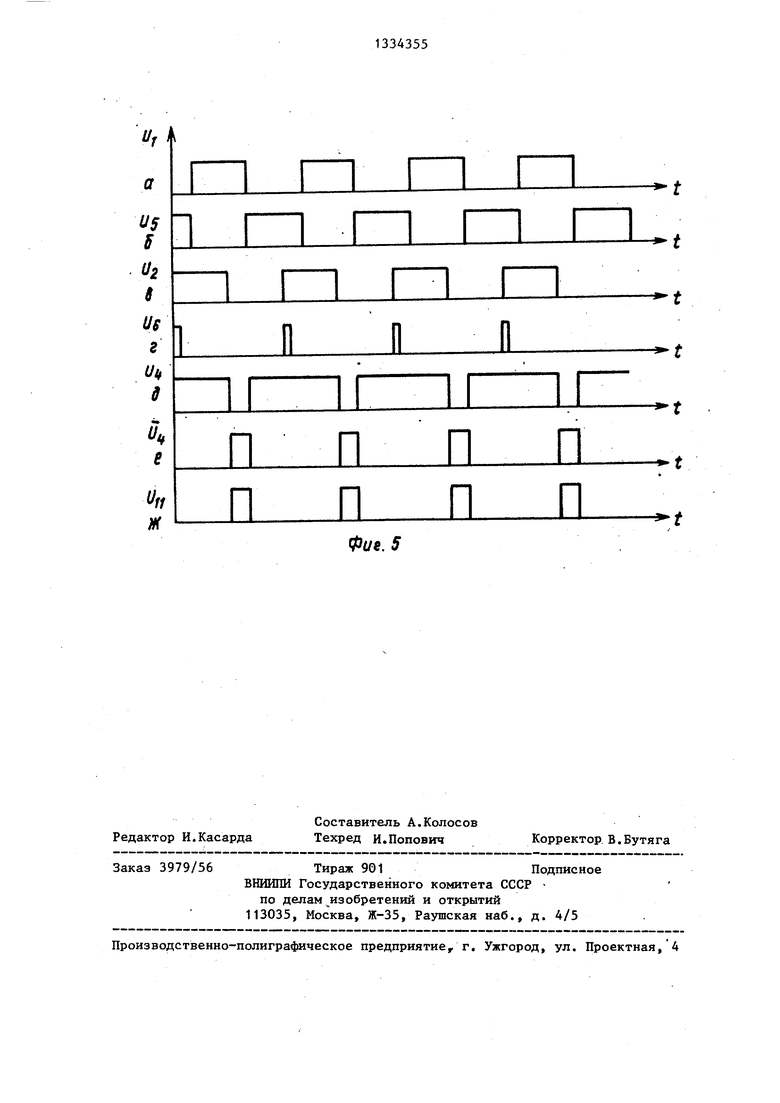

На фиг. 1 приведена структурная электрическая схема фазового дискриминатора; на фиг. 2 - структурная электрическая схема управляемого пшротно-импульсного преобразователя на фиг. 3 - электрическая принципиальная схема блока установки полярности выходного напряжения на фиг. 4 и 5 - временные диаграммы, поясняющие работу фазового дискриминатора.

Фазовый дискриминатор (фиг. 1) содержит источник 1 опорного сигнала, источник 2 входного сигнала, первый и второй JK-триггеры 3 и 4, инвертор 5, формирователь 6 коротки импульсов, первый и второй И 7 и 8, преобразователь 9 частота напряжение, сумматор 10, включающий элемент ИЛИ 11, управляемый широтно-импульсный преобразователь 12, блок 13 установки полярности выходного . напряжения ,

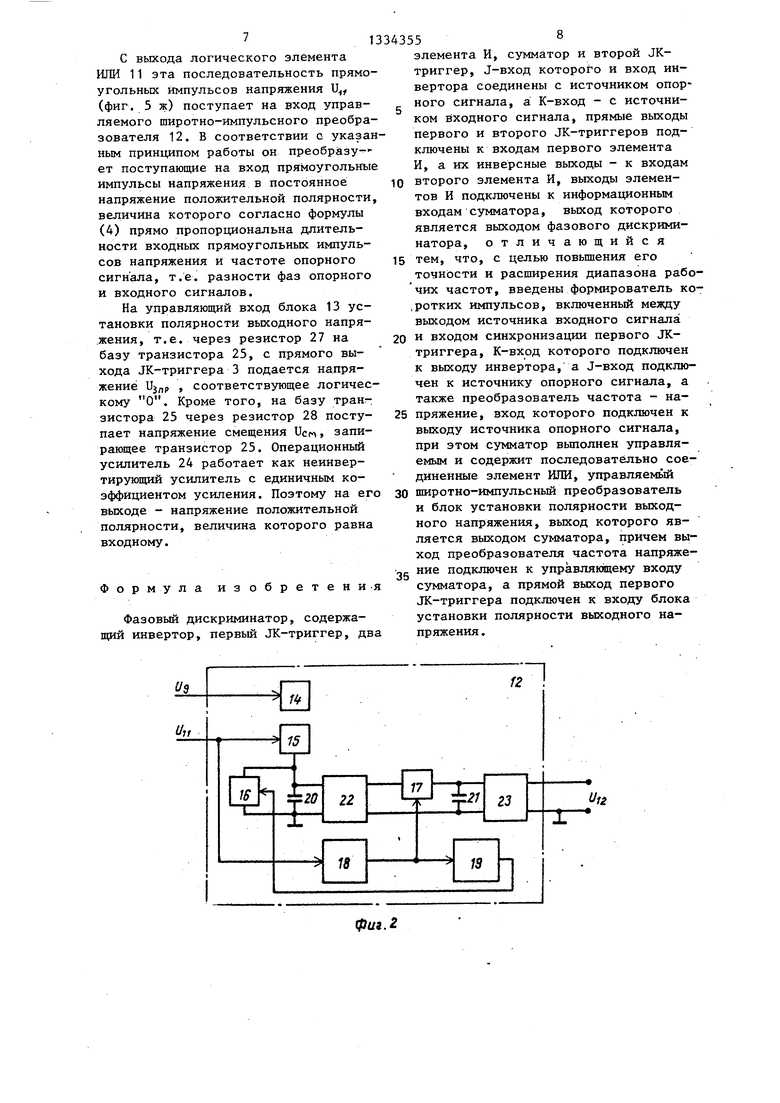

Управляемый широтно-импульсный преобразователь 12 (фиг. 2) содержи источник 14 эталонного тока, ключи 15-17, одновибраторы 18 и 19, конденсаторы 20 и 21, повторители 22 и 23 напряжения.

Блок 13 установки полярности напряжения (фиг. 3) содержит операционный усилитель 24, транзистор 25, общую шину 26, первьй и второй резисторы 27 и 28.

Фазовый дискриминатор работает следукнцим образом.

Предположим, что входной сигнал отстает по фазе от опорного сигнала Работу фазового дискриминатора в этом режиме поясняют временные диаграммы напряжений, представленные на фиг, 4, Опорный сигнал в виде последовательности прямоугольных импулсов напряжения U (фиг. 4, а) со скважностью Q 2 поступает с выхода источника 1 опорного сигнала на вход инвертбра 5, на J-вход JK-триг гера 3, на J-вхйд JK-триггера 4 и

на вход преобразователя 9 частота - напряжение.

С выхода инвертора 5 инвертированные прямоугольные импульсы напряжения опорного сигнала (фиг. 4, б) подаются на К-вход JK-триггера 3. Одновременно на К-вход JK-триггера 4 и вход формирователя 6 коротких импульсов с вькода источника 2 входного сигнала поступает входной сигнал в виде последовательности прямоугольных импульсов напряжения Ui (фиг. 4в) со скважностью , отстающих по фазе от прямоугольных импульсов напряжения U, опорного сигнала.

Задними фронтами прямоугольных импульсов напряжения опорного сигнала II,, осуществляется перевод JK-триггера 4 в состояние, в котором на его прямом вьшоде будет напряжение, соответствующее логической 1,

на инверсном - логическому О

а

Перевод JK-триггера 4 в противоположное состояние, в котором на его прямом выходе будет напряжение, соответствующее логическому О, а на инверсном выходе - логической

1, осуществляется задними фронтами прямоугольных импульсов напряжения входного сигнала U; . При этом на прямом выходе JK-триггера 4 возникает последовательность прямоугольных

импульсов напряжения U (фиг. 4 ), длительность которых прямо пропорциональна разности фаз прямоугольных импульсов напряжения опорного Uj и входного Ui сигналов, а на его

инверсном вькоде - инвертированная последовательность этих же импульсов напряжения и (фиг. 4 е).

Формирователь 6 коротких импульсов формирует короткие прямоугольные

импульсы напряжения U Сфиг. 4 ;), передний фронт которых совпадает с передним фронтом прямоугольных импульсов напряжения входного сигнала Uj.. Эти импульсы поступают на синхро- низирукяций вход JK-триггера 3. В . связи с тем, что в этом режиме работы фазового дискриминатора при поступлении на синхронизирующий вход JK-триггера 3 прямоугольного импульса напряжения на его J-входе всегда будет напряжение, ссответствуняцее логической 1, то ЛС-триггер 3 принимает состояние, в котором на его прямом выходе устанавливается напря

жение

1.

О.

, соответствующее логической а на инверсном - логическому Поэтому на вьесоде элемента

И 8 - напряжение, соответствующее логическому О, а элемент И 7 пропускает на один из входов логического элемента ИЛИ 11 пocлeдoвateль- ность прямоугольных импульсов напряжения и/) с прямого выхода ЛС-три гера 4.

С выхода элемента ИЛИ 11 последовательность прямоугольных импульсов Vn (фиг. 4 ж) поступает на вхо управляемого широтно-импульсного преобразователя 12, т.е. управляющий вход его ключа 15 и вход одно- вибратора 18 (фиг, 2). На управляющий вход управляемого широтно-им- пульсного преобразователя 12, т.е. на управляющий вход источника 14 эталонного тока 14 (фиг 2), с выхода преобразователя9 частота-напряжение подается напряжение прямо пропорциональное частоте прямоуголь ньк импульсов напряжения опорного сигнала U

и,

Kj f о

Ki То

(1)

где Uj - выходное напряжение обратного частотно-импульсного преобразователя 9 частота- напряжение,

fо - частота прямоугольных импульсов напряжения опорного сигнала Uf ;

TO - период прямоугольных импульсов напряжения опорного сигнала U J

Kg - коэффициент пропорциональности между частотой прямоугольных импульсов напряжения опорного сигнала IV и выходным напряжением Uj преобразователя 9 частота-напряжение .

При появлении на входе управляемого широтно-импульсного преобразователя 12 прямоугольного импульса напряжения с длительностью IT открывается его ключ 15 и конденсатор 20 начинает заряжаться от источника 14 эталонного тока. Величина тока заряда конденсатора 20 прямо пропорциональна величине напряжения на управляющем входе источника 14 эталонного тока

I, Ки и, (2)

4355

где

g Ю

- ток источника 14 эталонного

тока,

К - коэффициент пропорциональности между выходным напряжением преобразователя 9 частота-напряжение и током источника 14 эталонного тока.

Напряжение на конденсаторе 20 линейно увеличивается и к окончанию действия прямоугольного импульса напряжения равняется

и

10

-k

Cjff

(3)

где и

iff

0

5

(2)

напряжение на конденсаторе 20;

CJP - емкость конденсатора 20, ft - длительность прямоугольного цмпульса напряжения на входе управляемого широтно-импульсного преобразователя 12.

После постановки выражений (1), в формулу (3) получают

и

iu К

iO

1

тГ

(4)

где К

.K,j

М

5

0

5

(4)

коэффициент пропорциональное ти мезвду отношением длительности прямоугольных импульсов напряжения на входе управляемого широтно-имйульс- ного преобразо- вателя 1.2 к периоду То прямоугольных импульсов напряжения опорного сигнала и и напряжением на конденсаторе 20 Uio . видно, что к

0 Из выражения

окончанию действия прямоугольного импульса напряжения на входе управляемого широтно-импульсного преобразователя 12 напряжение на конденса5 торе 20 будет прямо пропорционально отношению длительности этого импульса к периоду Т прямоугольных импульсов напряжения опорного сигнала и , т.е. не зависит от часто1 ы

опорного сигнала, а зависит только от величины разности фаз опорного и входного сигналов. В момент окончания действия прямоугольного импульса напряжения на входе управляемого широтно-импульсного преобразователя 12 ключ 15 закрывается и запускается одновибратор 18. Сформированный им короткий прямоугольный импульс на- пряжения поступает на управляюсций вход ключа 17 и открывает его. К конденсатору 20 через повторитель 22 напряжения подключается конденсатор

21. Напряжение на нем и соответствен™ ig в этом режиме, как и в указанном но на выходе повторителя 23 напряжения, т.е. на выходе управляемого широтно-импульсного преобразователя 12, становится равным напряжению на конденсаторе 20, определяемому из выражения (4).

В момент возврата одновибратора 18 в исходное положение запускается одновибратор 19. Короткий прямоуг.оль- ный импульс напряжения, формируемый им, поступает на управляющий вход ключа 16 и включает его. Конденсатор 20 полностью разряжается..При возвращении одновибратора 19 в исходное состояние ключ 16 закрывается, и управляемый широтно-импульс- ный преобразователь 12 снова готов к преобразованию следующего входного импульса напряжения.

Повторители 22 и 23 напряжения имеют большое входное сопротивление и предотвращают разряд конденсаторов 20 и 21 соответственно. Поэтому напряжение на выходе управляемого широтно-импульсного преобразователя 12 и, сохраняется практически неизменным до поступления на его вход следующего прямоугольного импульса напряжения. Допустим, что это напряжение имеет положительную полярность. Оно подается на вход блока установки полярности выходного напряжения 13, т.е. на оба входа операционного усилителя 24 с единичным коэффициентом усиления.

Одновременно через резистор 27 на базу транзистора 25, т.е. на управляющий вход блока 13 установки полярности выходного напряжения, с прямого выхода JK-триггера 3 поступает постоянное напряжение Ujn положительной полярности,.величина которого эквивалентна логической 1. Транзистор 25 открьшается. Неинвер20

задними фронтами прямоугольных импульсов напряжения входного сигнала и (фиг. 5 в) осуществляется перевод JK-триггера 4 в состояние, в котором на его прямом выходе - напряжение, соответствующее логическому О, а на инверсном - логической 1, а задними фронтами прямоугольных импульсов напряжения опор- 25 ного сигнала U (фиг. 5 а) - в противоположное. На фиг. 5 б приведены временные диаграммы на выходе инвертора 5.

На инверсном выходе JK-триггера 4 возникает последовательность прямоугольных импульсов напряжения U (фиг. 5 е), длительность которых прямо пропорциональна разности фаз прямоугольных импульсов напряжения опорного и., и входного Uj сигналов. На его прямом выходе - инвертирован ная последовательность этих импульсов напряжения U (фиг. 53,).

30

35

40

45

50

55

На J-входе JK-триггера 3 при поступлении на его синхронизирующий вход коротких прямоугольных импульсов напряжения U (фиг. 5 i ) с выхода формирователя 6 коротких импульсов при работе фазового дискриминатора в данном режиме будет напряжение, соответствующие логическому О. Поэтому JK-триггер 3 принимает состояние, в котором на его прямом выходе устанавливается напря жение, соответствующее логическому О, а на инверсном - логической 1. На выходе элемента И 7 напряже ние становится эквивалентным логиче кому О. Элемент И 8 начинает пропускать на один из входов элемента ИЛИ 11 последовательность прямоугол ных импульсов напряжения с инверсного выхода JK-триггера 4.

тирующий вход операционного усилителя 24 подключается к общей шине 26.

Операционный усилитель 24 инвертирует входное напряжение Un . Напряжение на его выходе и на выходе фазового дискриминатора имеет отрицательную полярность и равняется по модулю входному напряжению U,i .

Работу фазового дискриминатора при опережении по фазе входным сигналом опорного поясняют временные диаграммы, приведенные на фиг. 5. При работе фазового дискриминатора

задними фронтами прямоугольных импульсов напряжения входного сигнала и (фиг. 5 в) осуществляется перевод JK-триггера 4 в состояние, в котором на его прямом выходе - напряжение, соответствующее логическому О, а на инверсном - логической 1, а задними фронтами прямоугольных импульсов напряжения опор- ного сигнала U (фиг. 5 а) - в противоположное. На фиг. 5 б приведены временные диаграммы на выходе инвертора 5.

На инверсном выходе JK-триггера 4 возникает последовательность прямоугольных импульсов напряжения U (фиг. 5 е), длительность которых прямо пропорциональна разности фаз прямоугольных импульсов напряжения опорного и., и входного Uj сигналов. На его прямом выходе - инвертированная последовательность этих импульсов напряжения U (фиг. 53,).

40

45

50

55

На J-входе JK-триггера 3 при поступлении на его синхронизирующий вход коротких прямоугольных импульсов напряжения U (фиг. 5 i ) с выхода формирователя 6 коротких импульсов при работе фазового дискриминатора в данном режиме будет напряжение, соответствующие логическому О. Поэтому JK-триггер 3 принимает состояние, в котором на его прямом выходе устанавливается напряжение, соответствующее логическому О, а на инверсном - логической 1. На выходе элемента И 7 напряжение становится эквивалентным логическому О. Элемент И 8 начинает пропускать на один из входов элемента ИЛИ 11 последовательность прямоугольных импульсов напряжения с инверсного выхода JK-триггера 4.

с выхода логического элемента ИЛИ 11 эта последовательность прямоугольных импульсов напряжения U (фиг. 5 ж) поступает на вход управляемого широтно-импульсного преобразователя 12. В соответствии с указанным принципом работы он преобразу-- ет поступающие на вход прямоугольные импульсы напряжения в постоянное напряжение положительной полярности, величина которого согласно формулы (4) прямо пропорциональна длительности входных прямоугольных импульсов напряжения и частоте опорного сигн ала, т.е. разности фаз опорного и входного сигналов.

На управляющий вход блока 13 установки полярности выходного напряжения, т.е. через резистор 27 на базу транзистора 25, с прямого выхода JK-триггера 3 подается напряжение Ujnp , соответствующее логическому О. Кроме того, на базу транзистора 25 через резистор 28 поступает напряжение смещения UCM , запирающее транзистор 25. Операционный усилитель 24 работает как неинвертирующий усилитель с единичным коэффициентом усиления. Поэтому на его выходе - напряжение положительной полярности, величина которого равна входному.

Формула изобретения

Фазовый дискриминатор, содержащий инвертор, первый JK-триггер, два

10

15

334355

элемента И, сумматор и второй JK- триггер, J-вход которого и вход инвертора соединены с источником опорного сигнала, а К-вход - с источником входного сигнала, прямые выходы первого и второго JK-триггеров подключены к входам первого элемента И, а их инверсные выходы - к входам второго элемента И, выходы элементов И подключены к информационным входам сумматора, выход которого является выходом фазового дискриминатора, отличающийся тем, что, с целью повышения его точности и расщирения диапазона рабочих частот, введены формирователь коротких импульсов, включенный между выходом источника входного сигнала и входом синхронизации первого JK- триггера, К-вхрд которого подключен к выходу инвертора, а J-вход подключен к источнику опорного сигнала, а также преобразователь частота - напряжение, вход которого подключен к выходу источника опорного сигнала, при этом сумматор вьшолнен управляемым и содержит последовательно соединенные элемент ИЛИ, управляемьй 30 широтно-имлульсный преобразователь и блок установки полярности выходного напряжения, выход которого является выходом сумматора, причем выход преобразователя частота напряжение подключен к управлякицему входу сумматора, а прямой выход первого JK-триггера подключен к входу блока установки полярности выходного напряжения ,

20

25

35

фиг. 2

Фцг.

Редактор И.Касарда

Составитель А.Колосов Техред И.Попович

Заказ 3979/56

Тираж 901Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор В.Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Ключевой фазоимпульсный преобразователь | 1984 |

|

SU1312730A2 |

| Устройство для стабилизации частоты вращения электродвигателя | 1989 |

|

SU1686681A1 |

| Широтно-импульсное устройство для программного управления приводом | 1981 |

|

SU1020799A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1481813A1 |

| Стабилизированный источник питания | 1986 |

|

SU1390736A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТОКА В ФАЗЕ АСИНХРОННОГО ЭЛЕКТРОПРИВОДА | 1991 |

|

RU2022442C1 |

| Электропривод | 1988 |

|

SU1656652A1 |

| Электропривод | 1987 |

|

SU1434532A1 |

| Электропривод постоянного тока | 1991 |

|

SU1786630A1 |

| Фазовый дискриминатор | 1981 |

|

SU970634A1 |

Изобретение относится к измерительной технике и обеспечивает повышение точности и расширение диапазона рабочих частот. Фазовый дискриминатор содержит источник 1 опорного сигнала, источники 2 входного сигнала, JK-триггеры 3 и 4, инвертор 5, формирователь 6 коротких импульсов, элементы И7 и8,. преобразователь 9 частота - напряжение, сумматор 10, состоящий из элемента ИЖ 11, управляемого широтно-импульсного преобразователя 12 и блока 13 установки полярности выходного напряжения. 5ил. (Л с DO- CO 4 00 ел сд фие.1

Авторы

Даты

1987-08-30—Публикация

1986-02-21—Подача