Я 15 18

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь сопротивления постоянному току в интервал времени | 1984 |

|

SU1237993A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1411974A1 |

| Преобразователь напряжения в интервал времени | 1984 |

|

SU1282331A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1444950A1 |

| Преобразователь напряжения вчАСТОТу | 1979 |

|

SU824437A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Преобразователь напряжение-время | 1986 |

|

SU1441470A1 |

Изобретение относится к электроизмерительной технике и может быть использовано в универсальных цифровых вольтметрах для линейного преобразования постоянного напряжения в интервал времени. Изобретение позволяет повысить точность преобразования. В преобразователь, содержащий источник 1 опорного напряжения, ключи 4, 5, 8, 9 и 17, блок 23 сравнения, операционные усилители 12, 13, 19, компаратор 20} буферный усилитель 6, токоо раничивающие элементы 2, 3, 15, 16, 18, 21, 22, выполненные на резисторах, накопительные элементы 11, 14, выполненные на конденсаторах, введен ключ 7. 1 з.п. ф-лы, 3 ил.

Вход

Фиг.1

Изобретение относится к электроизмерительной технике и может быть использовано в универсальных цифровых вольтметрах для линейного пре- образования постоянного напряжения в интервал времени.

Целью изобретения является повышение точности преобразования.

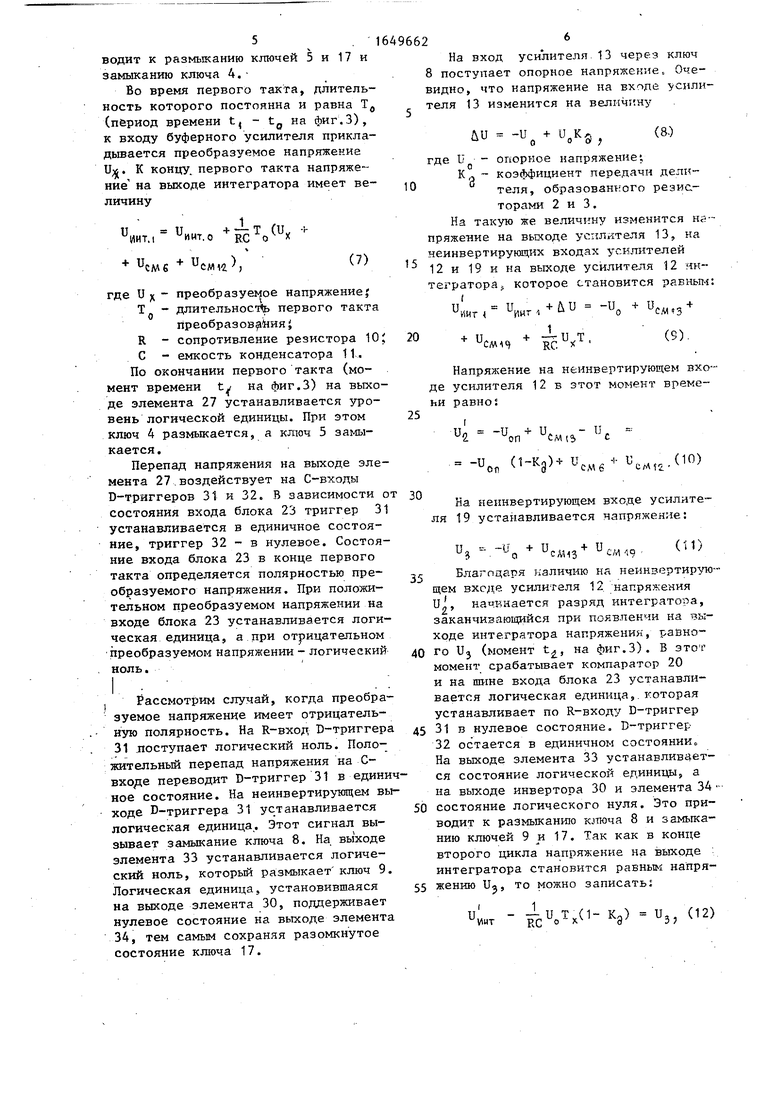

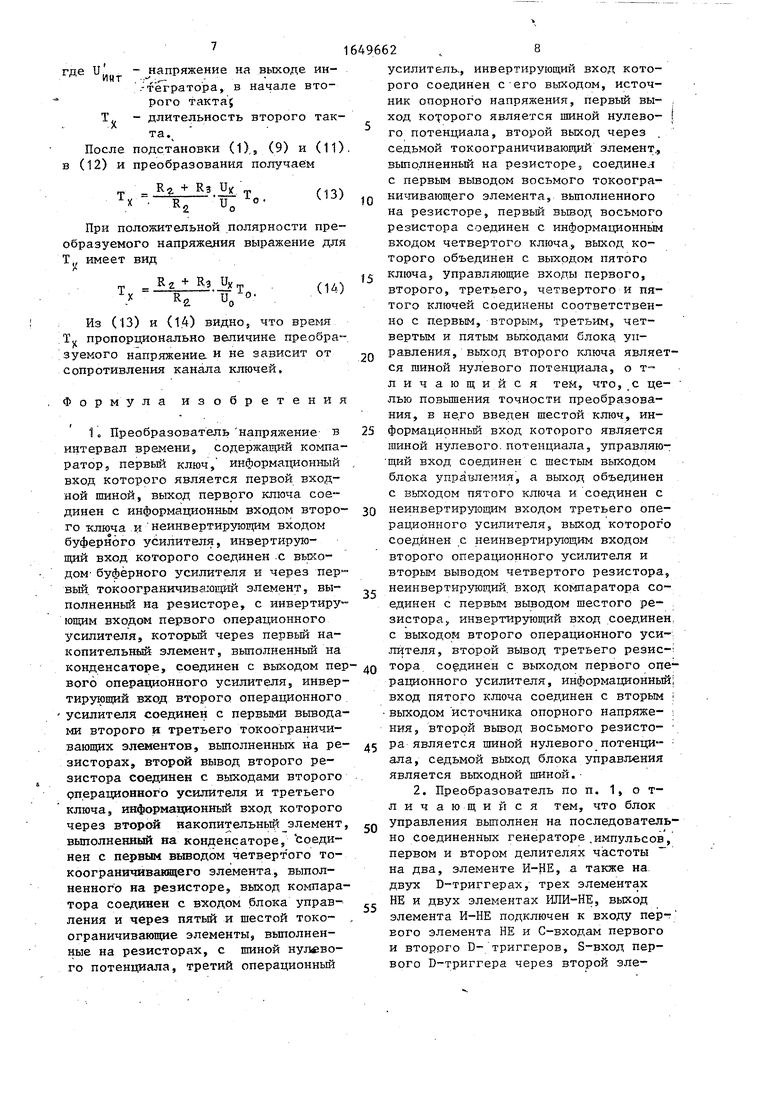

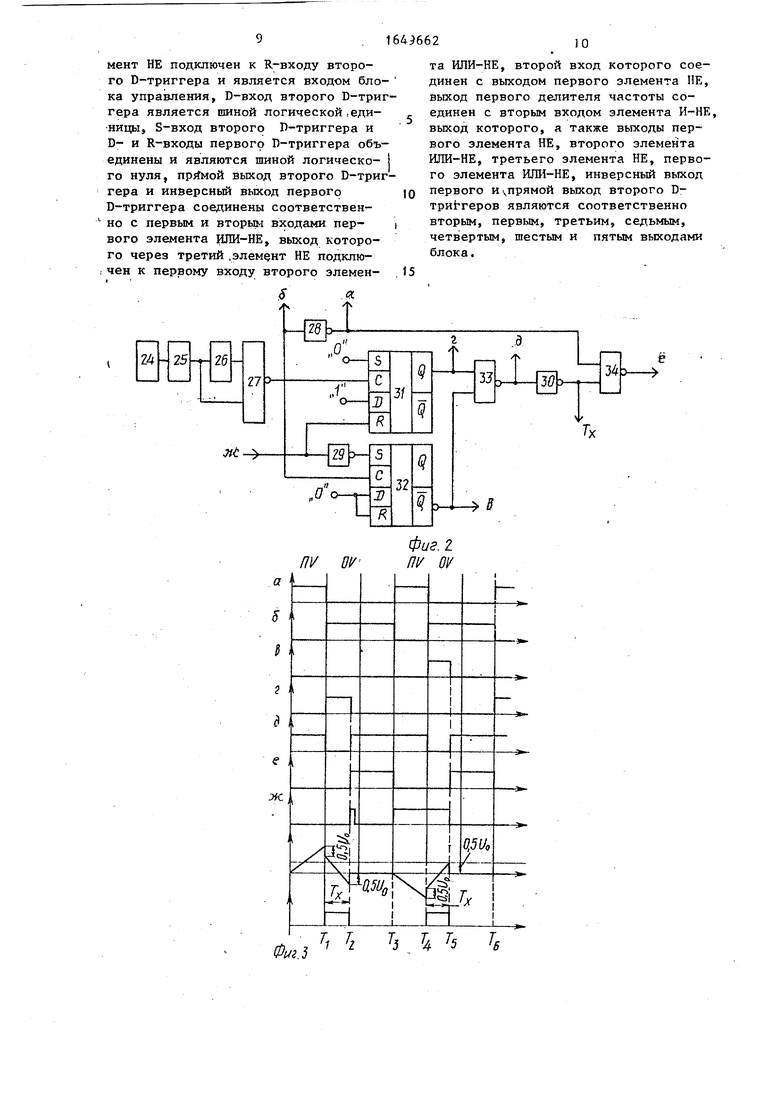

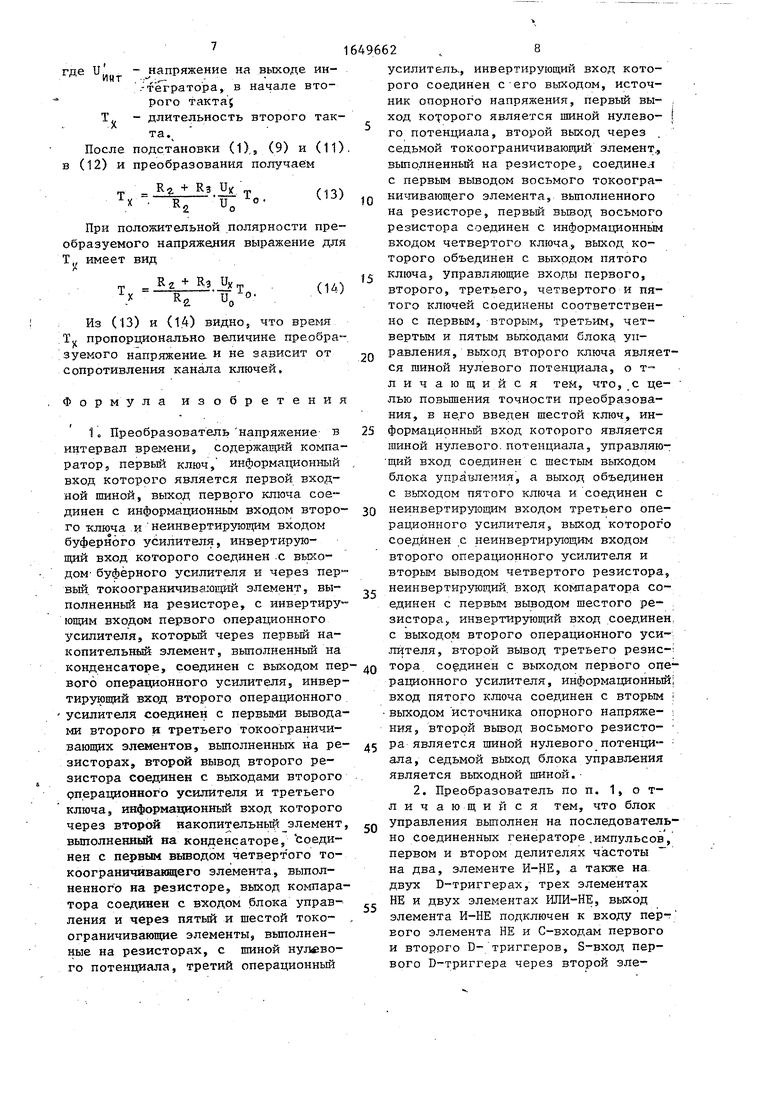

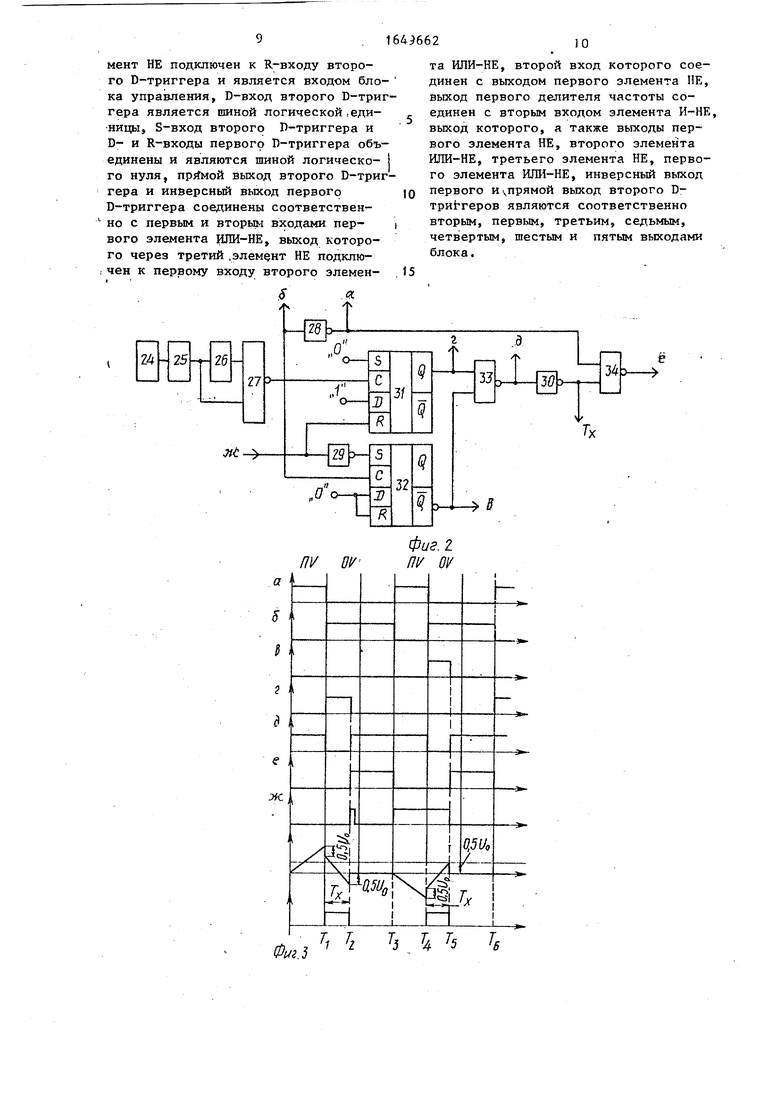

На фиг. 1 приведена структурная схема преобразователя$ на фиг. 2 - структурная схема блока управления; на фиг. 3 - временные диаграммы, поясняющие работу блока управления.

Преобразователь содержит источник 1 опорного напряжения, токгограничи- вающие элементы -2 и 3, выполненгые на резисторах, ключи 4 и 59 буферный усилитель 6, ключи 7т-9, токоог- раничивающий элемент 10, выполненный на резисторе, накопительный элемент 11, выполненный на конденсаторе, операционные усилители 12 и 13, накопительный элемент 14%, выполненный на конденсаторе, токоограничивающие эле- менты 165 выполненные на резисторах, ключ 17, токоограничивающий элемент 18, выполненный на резисторе, операционный усилитель 19, компаратор 20, токоограничивающие элементы 21 и 22 выполненные на резисторах и блок 23 управления.

Блок управления (фиг.2) содержи7 генератор 24 импульсов, делители 25 и 26 частоты, на два& элемент И-НЕ 27, элементы ЧЕ 28-30, D-триггеры 31 и 32 и элементы ШШ-НЕ 33 и 34.

На фиг.З обозначены: а - напряжение на выходе элемента НЕ 28,- Ј - нпряжение на выходе элемента И-НЕ 27 J & - напряжения на инвертирующем выходе D-триггера 32 $- напряжение на прямом выходе D-триггера 31; fy - напряжение на выходе элемента ИЛИ-НЕ 33} Q напряжение на выходе элемента ИЛИ-НЕ 34; К - напряжения на, входе блока 23; - напряжение на выходе усилителя 12.

Преобразователь работает в три тата. В исходном состоянии (до начала первого такта работы) ключи 5, 9. и 17 замкнуты. Вход буферного усилителя 6 соединен с общей шиной, а вхо усилителя 13 - с точкой соединения резисторов 2 и 3, образующих дели- тель, с коэффициентом передачи

к3

V

R,

(1)

где

R R5 сопротивление резистора 2, сопротивление резистора 3. Так как делитель подключен к выхо- ду источника 1, то на выходе усилителя 13 устанавливается напряжение, равное:

U

иоК9

+ U,

(1)

где U

U. о

СМ13

Кв опорное напряжение, напряжение смещения усилителя 13;

коэффициент передачи делителя, образованного резисторами 2 и 3.

На неинвертирующем входе усилителя 12 интегратора за счет глубокой отрицательной обратной связи устанавливается напряжение, равное:

UCM6 +

U

см г

(3)

где UCM6- напряжение смещения -буфер«

ного усилителя 6J UCM - напряжение смещения усилителя 12 интегратора. Предположим, что источник опорного напряжения имеет отрицательную полярность, тогда выражение (2) примет вид

(4У

и uoV

Напряжение на выходе усилителя равно

12

U,

ИНТ. О

UQK3

исшЗ +

и,

с«19

+ исме + . )

(5)

0

где

о кэи

5 U

опорное напряжение ,

коэффициент передачи делителя, образованного резисторами 2 и 3,

напряжение смещения усилителя 13 i

напряжение смещения усилителя 19. Конденсатор 14 заряжается до наCMt

см

пряжения,

ил

равного:

U, - Uft о

+

W

-иока

В начале первого такта работы (на фиг.З момент времени t0)Ha выходе элемента 27 блока 23 устанавливается состояние логического нуля, на выходе элемента 28 - состояние логической единицы, а на выходе элемента 34 - состояние логического нуля, Это при™

водит к размыканию ключей 5 и 17 и замыканию ключа 4.Во время первого такга, длительность которого постоянна и равна ТЛ

(период времени

t t на фиг.З),

к входу буферного усилителя прикладывается преобразуемое напряжение U. К концу, первого такта напряжение на выходе интегратора имеет величину

U

ИНТ. О

+ FK(UK

исмм.),

где U x - преобразуемое напряжение; Т - длительность первого такта

преобразования}

R - сопротивление резистора 10( С - емкость конденсатора 11. По окончании первого такта (момент времени t на фиг.З) на выходе элемента 27 устанавливается уровень логической единицы. При этом ключ 4 размыкается, а ключ 5 замыкается.

Перепад напряжения на выходе элемента 27 воздействует на С-вх.оды D-триггеров 31 и 32. В зависимости о состояния входа блока 23 триггер 31 устанавливается в единичное состояние, триггер 32 - в нулевое. Состояние входа блока 23 в конце первого такта определяется полярностью преобразуемого напряжения. При положительном преобразуемом напряжении на входе блока 23 устанавливается логическая единица, а при отрицательном преобразуемом напряжении - логический ноль.

, Рассмотрим случай, когда преобразуемое напряжение имеет отрицательную полярность. На R-вход D-триггера 31 поступает логический ноль. Положительный перепад напряжения на С- входе переводит D-триггер 31 в единичное состояние. На неинвертирующем выходе D-триггера 31 устанавливается логическая единица. Этот сигнал вызывает замыкание ключа 8. На выходе элемента 33 устанавливается логический ноль, который размыкает ключ 9. Логическая единица, установившаяся на выходе элемента 30, поддерживает нулевое состояние на выходе элемента 34, тем самым сохраняя разомкнутое состояние ключа 17.

На вход усилителя 13 через ключ 8 поступает опорное напряжение. Очевидно, что напряжение на входе усиливеличину

теля 13 изменится на

Ли -U +

U К л

О о )

(8-)

10

15

где

Г

20 25опорное напряжение , коэффициент передачи делителя, образованного резисторами 2 и 3.

На такую же величину изменится напряжение на выходе усилителя 13, на неинвертирующих входах усилителей 12 и 19 и на выходе усилителя 12 чн- тегратора которое становится равным: (

-U0

+ U

ели ч

icVUCAM3 +

(S)

Напряжение на неинвертирующем вхоусилителя 12 в этот момент време- равно;

U2 - Uon

исм5з- ис

-и

ол

(1-Кд)+ U

ем б

} и

CMt2

(Ю)

На неинвертирующем входе усилителя 19 устанавливается напряжение:

5

0

5

0

U, -- -U

UCA,13 +

и

(11)

щем

ч;.

о -слнз М .9

Благодаря ьаличию на неинзертирую-- входе усилителя 12 напряжения

на«р.нается разряд интегратора, заканчивающийся при появлении на выходе интегратора напряжения, равно™ го U5 (момент t, на фиг.З). В этот момент срабатывает компаратор 20 и на шине входа блока 23 устанавливается логическая единица, которая устанавливает по R-входу D-триггер 31 в нулевое состояние. D-триггер остается в единичном состоянии, выходе элемента 33 устанавливает32

На

ся состояние логической единицы, а на выходе инвертора 30 и элемента 34 состояние логического нуля. Это приводит к размыканию ключа 8 и замыканию ключей 9 и 17. Так как в конце второго цикла напряжение на выходе интегратора становится равным напря55 жению U«, то можно записатьJ

- ) J3J

(12)

е U

инт

- напряжение на выходе ин- -тегратора, в начале второго такта; Tv - длительность второго такА

Tav

После подстановки (1), (9) и (11) (12) и преобразования получаем

т JLL.UL3 Ј х R2 ио

(13)

При положительной полярности преобразуемого напряжения выражение для Т„ имеет вид

К

R,

R3 Ux

R,

.Ii Т

V0

(1U)

Из (13) и (14) видноs что время Т„ пропорционально величине преобразуемого напряжение и не зависит от сопротивления канала ключей.

Формула изобретения

конденсаторе, соединен с выходом пер дд тора соединен с выходом первого опевого операционного усилителя, инвертирующий вход второго операционного усилителя соединен с первыми выводами второго и третьего токоограничи- вающих элементов, выполненных на резисторах, второй вывод второго резистора соединен с выходами второго операционного усилителя и третьего ключа, информационный вход которого через второй накопительный элемент, выполненный на конденсаторе, соединен с первым выводом четвертого то- коограничивающего элемента, выполненного на резисторе, выход компаратора соединен с входом блока управления и через пятый и шестой токо- , ограничивающие элементы, выполненные на резисторах, с шиной нулевого потенциала, третий операционный

0

5

0

5

0

5

усилитель, инвертирующий вход которого соединен с его выходом, источник опорного напряжения, первый выход которого является шиной нулево- го потенциала, второй выход через седьмой токоограничивающий элемент, выполненный на резисторе,, соединел с первым выводом восьмого токоогра- ничивающего элемента, выполненного на резисторе, первый вывод восьмого резистора соединен с информационным входом четвертого ключа, выход которого объединен с выходом пятого ключа, управляющие входы первого, второго, третьего, четвертого и пятого ключей соединены соответственно с первым, вторым, третьим, четвертым и пятым выходами блока управления, выход второго ключа является шиной нулевого потенциала, о т- личающийся тем, что,с целью повышения точности преобразования, в него введен шестой ключ, информационный вход которого является шиной нулевого потенциала, управляющий вход соединен с шестым выходом блока управления, а выход объединен с выходом пятого ключа и соединен с неинвертирующим входом третьего операционного усилителя, выход которого соединен с неинвертирующим входом второго операционного усилителя и вторым выводом четвертого резистора, неинвертирующий вход компаратора соединен с первым выводом шестого резистора, инвертирующий вход соединен с выходом второго операционного усилителя, второй вывод третьего резис5

0

5

рационного усилителя, информационный, вход пятого ключа соединен с вторым выходом источника опорного напряжения, второй вывод восьмого резистора является шиной нулевого потенциала, седьмой выход блока управления является выходной шиной.

5 Ъ

д

та ИЛИ-НЕ, второй вход которого соединен с выходом первого элемента НЕ, выход первого делителя частоты соединен с вторым входом элемента И-НЕ, выход которого, а также выходы первого элемента НЕ, второго элемента ИЛИ-НЕ, третьего элемента НЕ, первого элемента ИЛИ-НЕ, инверсный выход первого непрямой выход второго D- триггеров являются соответственно вторым, первым, третьим, седьмым, четвертым, шестым и пятым выходами блока.

15

| Стронг Н | |||

| Конструирование надежного портативного цифрового муль- тиметра для жестких условий работы.- Электроника, 1977 | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

| УПРАВЛЯЕМЫЙ АЭРОСТАТ | 1925 |

|

SU3438A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1991-05-15—Публикация

1988-05-13—Подача