ч

СП СП

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения потери импульса | 1977 |

|

SU621081A1 |

| Устройство для обнаружения потери импульса | 1981 |

|

SU984018A1 |

| Устройство для контроля электромагнитного реле | 1987 |

|

SU1444716A1 |

| Устройство для обнаружения потери импульса | 1981 |

|

SU1046925A1 |

| Устройство допускового контроля периода сигнала | 1986 |

|

SU1325375A1 |

| Устройство для контроля последовательности периодических сигналов | 1983 |

|

SU1121675A1 |

| Устройство для контроля электромагнитного реле | 1991 |

|

SU1807453A1 |

| Устройство для контроля последовательности импульсов | 1975 |

|

SU748843A1 |

| Устройство для контроля последовательности импульсов | 1982 |

|

SU1064444A1 |

| Устройство для обнаружения потери | 1978 |

|

SU731572A2 |

Изобретение относится к импульсной технике и может быть использовано для обнаружения потери импульса в по- следовательностйх импульсов, например в исполнительных органах резервированных генераторов импульсов. Для достижения поставленной цели: повышение быстродействия и надежности - в устройство, содержащее квазиселектор 1, RS-триггер 2, элемент И 3, дополнительно введен элемент НЕ 4. В случае пропадания импульса из контролируемой последовательности устройство формирует сигнал, имеющий минимальную задержку относительно времени пропадания импульса. При этом устраняется возможность возникновения ло :ного сигнала срабатывания устройства и обеспечивается его высокое быстродействие при сохранении высокой надежности. 4 ил. с ю

(.f

Изобретение относится к импульсной технике и может быть использовано для обнаружения потери импульсов в последовательностях импульсов, например в исполнительных органах резервированных генераторов импульсов.

Цель изобретения - повышение быстродействия и надежности.

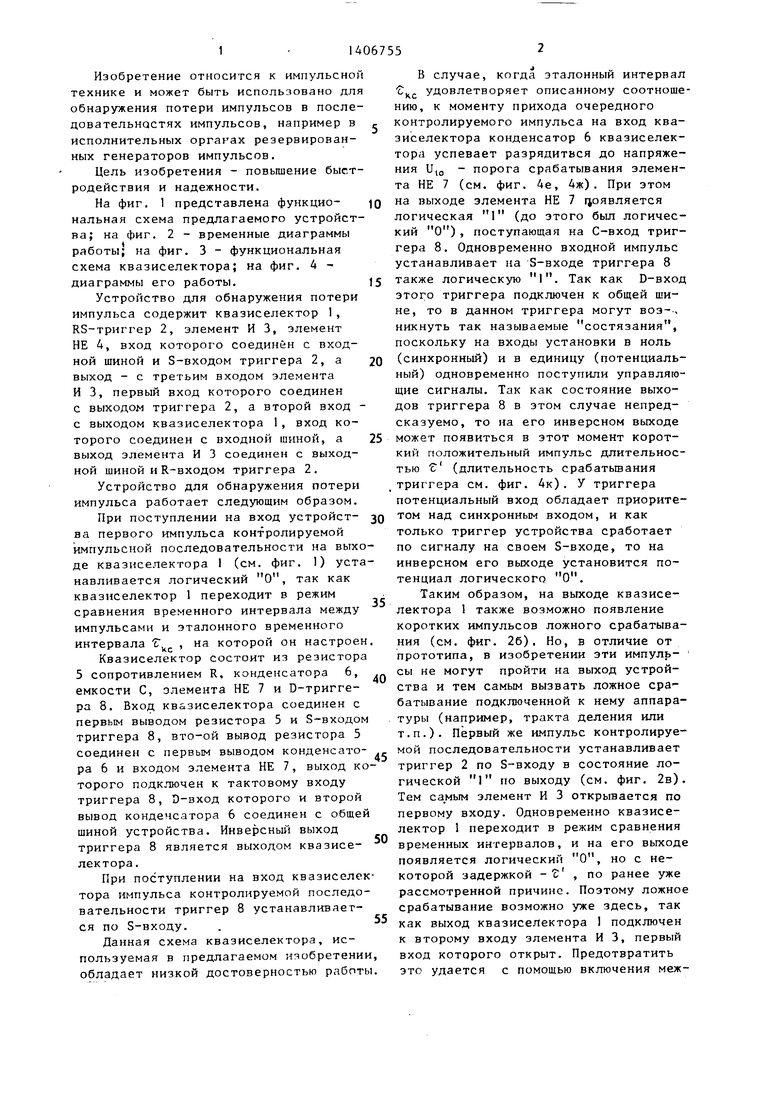

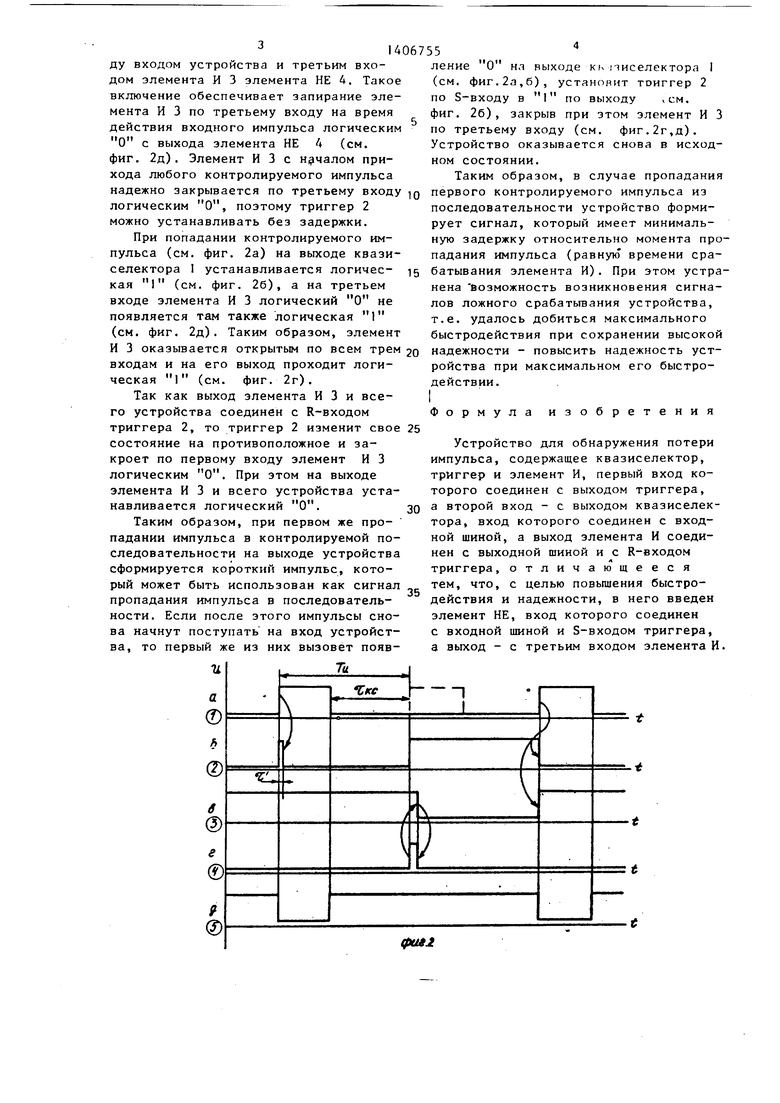

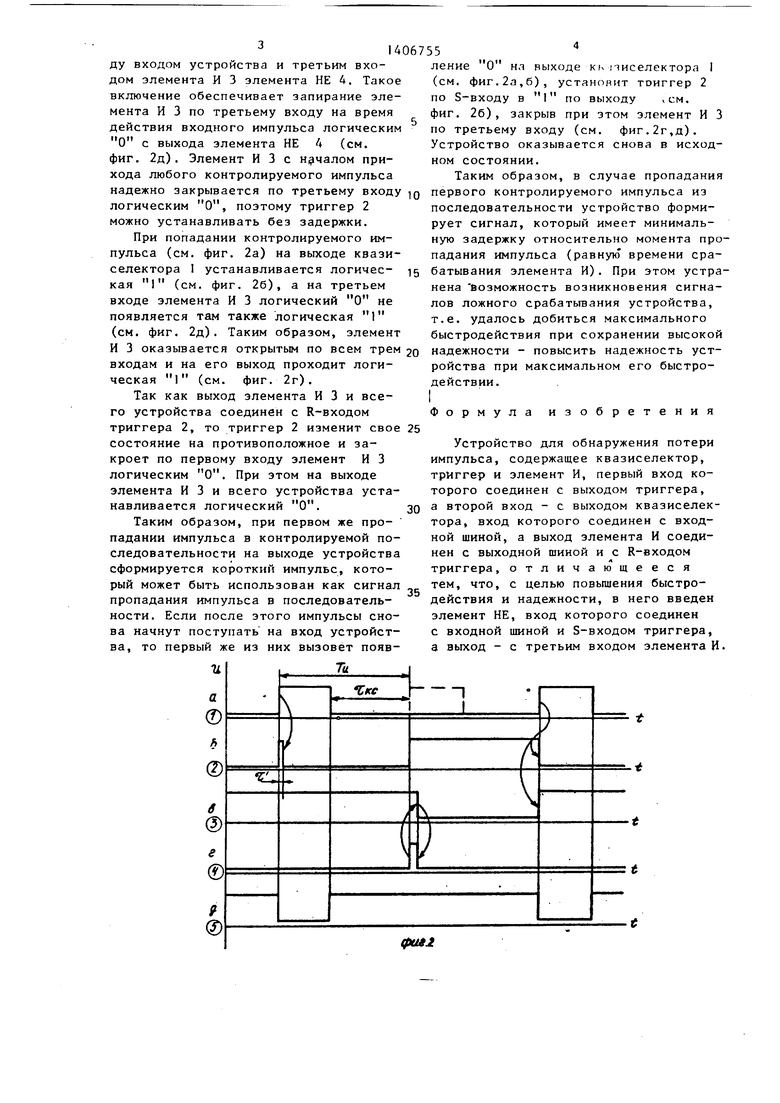

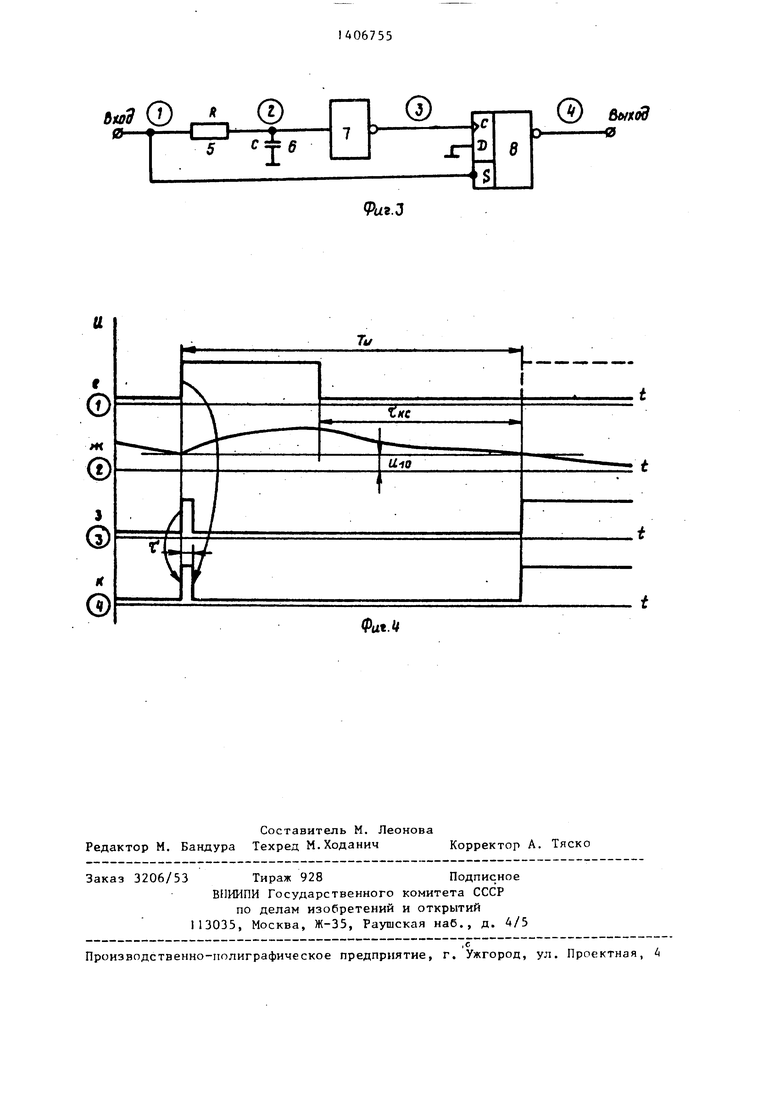

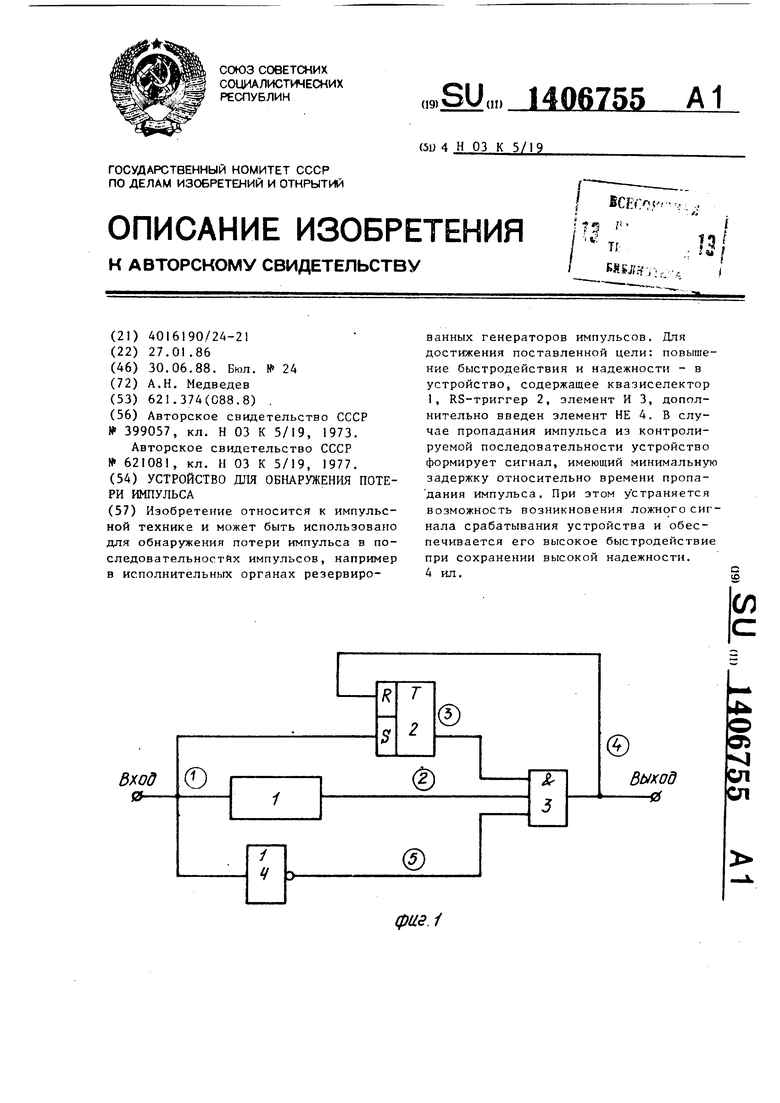

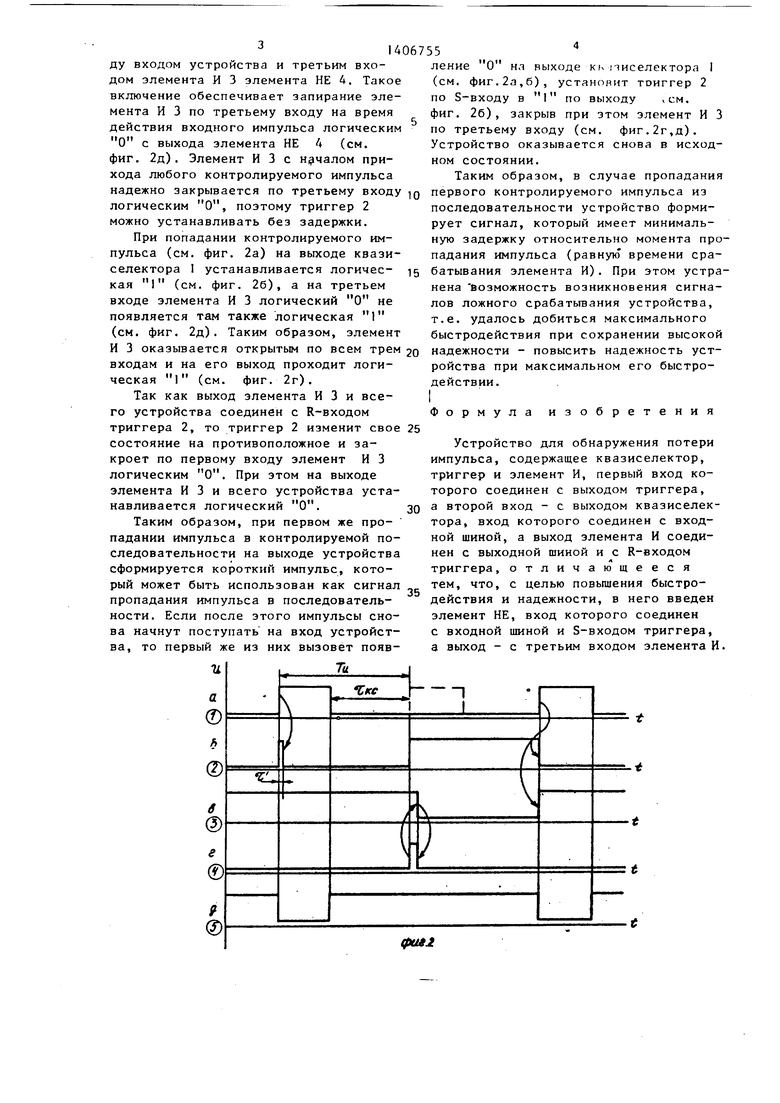

На фиг. 1 представлена функцио- нальная схема предлагаемого устройства; на фиг. 2 - временные диаграммы работы; на фиг. 3 - функциональная схема квазиселектора; на фиг. А - диаграммы его работы.

Устройство для обнаружения потери импульса содержит квазиселектор 1, RS-триггер 2, элемент И 3, элемент НЕ 4, вход которого соединён с входной шиной и S-входом триггера 2, а выход - с третьим входом элемента И 3, первый вход которого соединен с выходом триггера 2, а второй вход - с выходом квазиселектора 1, вход которого соединен с входной шиной, а выход элемента И 3 соединен с выходной шиной иR-входом триггера 2.

Устройство для обнаружения потери импульса работает следующим образом.

При поступлении на вход устройст- на первого импульса контролируемой импульсной последовательности на выходе квазиселектора 1 (см. фиг. 1) устанавливается логический О, так как квазиселектор 1 переходит в режим сравнения временного интервала между импульсами и эталонного временного интервала с , на которой он настроен

Квазиселектор состоит из резистора 5 сопротивлением R, конденсатора 6, емкости С, элемента НЕ 7 и D-тригге- ра 8. Вход квазиселектора соединен с первым выводом резистора 5 и S-входом триггера 8, вто-ой вывод резистора 5 соединен с первым выводом конденсато- ра 6 и входом элемента НЕ 7, выход которого подключен к тактовому входу триггера 8, D-вход которого и второй вывод конденсатора 6 соединен с общей шиной устройства. Инверсный выход триггера 8 является выходом квазиселектора.

При поступлении на вход квазиселектора импульса контролируемой последовательности триггер 8 устанавливается по S-входу.

Данная схема квазиселектора, используемая в предлагаемом изобретении обладает низкой достоверностью работы

5

0 5

g

,

5

В случае, когда эталонный интервал . удовлетворяет описанному соотноще- нию, к моменту прихода очередного контролируемого импульса на вход квазиселектора конденсатор 6 квазиселектора успевает разрядиться до напряжения и,о - порога срабатывания элемента НЕ 7 (см. фиг. 4е, 4ж). При этом на выходе элемента НЕ 7 появляется логическая 1 (до этого был логический О), поступающая на С-вход триггера 8. Одновременно входной импульс устанавливает на S-входе триггера 8 также логическую 1. Так как D-вход этого триггера подключен к общей шине, то в данном триггера могут воз- никнуть так называемые состязания, поскольку на входы установки в ноль (синхронный) и в единицу (потенциальный) одновременно поступили управляющие сигналы. Так как состояние выходов триггера 8 в этом случае непредсказуемо, то на его инверсном выходе может появиться в этот момент короткий положительный импульс длительностью с (длительность срабатьшания триггера см. фиг. 4к). У триггера потенциальный вход обладает приоритетом над синхронным входом, и как только триггер устройства сработает по сигналу на своем S-входе, то на инверсном его выходе установится потенциал логического О.

Таким образом, на выходе квазиселектора 1 также возможно появление коротких импульсов ложного срабатывания (см. фиг. 26). Но, в отличие от прототипа, в изобретении эти импуль- сы не могут пройти на выход устройства и тем самым вызвать ложное срабатывание подключенной к нему аппаратуры (например, тракта деления или т.п.). Первый же импульс контролируемой последовательности устанавливает триггер 2 по S-входу в состояние логической 1 по выходу (см. фиг. 2в). Тем элемент И 3 открывается по первому входу. Одновременно квазиселектор 1 переходит в режим сравнения временных интервалов, и на его выходе появляется логический О, но с некоторой задержкой - t , по ранее уже рассмотренной причине. Поэтому ложное срабатывание возможно уже здесь, так как выход квазиселектора 1 подключен к второму входу элемента И 3, первый вход которого открыт. Предотвратить это удается с помощью включения между входом устройства и третьим входом элемента И 3 элемента НЕ 4. Такое включение обеспечивает запирание элемента И 3 по третьему входу на время действия входного импульса логическим О с выхода элемента НЕ 4 (см. фиг. 2д). Элемент И 3 с началом прихода любого контролируемого импульса

надежно закрывается по третьему входу ,г, первого контролируемого импульса из О,

логическим О, поэтому триггер 2 можно устанавливать без задержки.

При попадании контролируемого импульса (см. фиг. 2а) на выходе квазиселектора I устанавливается логическая 1 (см. фиг. 2б), а на третьем входе элемента И 3 логический О не появляется там также логическая 1 (см. фиг. 2д). Таким образом, элемент

последовательности устройство форми рует сигнал, который имеет минималь ную задержку относительно момента п падания импульса (равную времени ср 15 батывания элемента И). При этом уст нена Возможность возникновения сигн лов ложного срабатьгаания устройства т.е. удалось добиться максимального быстродействия при сохранении высок

последовательности устройство формирует сигнал, который имеет минимальную задержку относительно момента пропадания импульса (равную времени сра- 15 батывания элемента И). При этом устранена Возможность возникновения сигналов ложного срабатьгаания устройства, т.е. удалось добиться максимального быстродействия при сохранении высокой

И 3 оказывается открытым по всем трем 2о надежности - повысить надежность уствходам и на его выход проходит логическая 1 (см. фиг. 2г).

Так как выход элемента И 3 и всего устройства соединен с R-входом триггера 2, то триггер 2 изменит свое состояние на противоположное и закроет по первому входу элемент И 3 логическим О. При этом на выходе элемента И 3 и всего устройства устанавливается логический О.

Таким образом, при первом же про- падании импульса в контролируемой последовательности на выходе устройства сформируется короткий импульс, который может быть использован как сигнал пропадания импульса в последовательности. Если после этого импульсы снова начнут поступать на вход устройства, то первый же из них вызовет появ

ление О нл выходе кьписелектора I (см. фиг.2а,б), устаноянт тоиггер 2 по S-входу в 1 по выходу ,см. фиг. 2б), закрыв при этом элемент И 3 по третьему входу (см. фиг.2г,д). Устройство оказывается снова в исходном состоянии.

Таким образом, в случае пропадания

первого контролируемого импульса из

последовательности устройство формирует сигнал, который имеет минимальную задержку относительно момента пропадания импульса (равную времени сра- батывания элемента И). При этом устранена Возможность возникновения сигналов ложного срабатьгаания устройства, т.е. удалось добиться максимального быстродействия при сохранении высокой

надежности - повысить надежность уст5

0

5

ройства при максимальном его быстродействии. I Формула изобретения

Устройство для обнаружения потери импульса, содержащее квазиселектор, триггер и элемент И, первый вход которого соединен с выходом триггера, а второй вход - с выходом квазиселектора, вход которого соединен с входной шиной, а выход элемента И соединен с выходной шиной и с R-входом триггера, отличающееся тем, что, с целью повышения быстродействия и надежности, в него введен элемент НЕ, вход которого соединен с входной шиной и S-входом триггера, а выход - с третьим входом элемента И.

Фиг. Л

Фut.l4

| УСТРОЙСТВО для ОБНАРУЖЕНИЯ ПОТЕРИ ИМПУЛЬСА | 0 |

|

SU399057A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для обнаружения потери импульса | 1977 |

|

SU621081A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-30—Публикация

1986-01-27—Подача