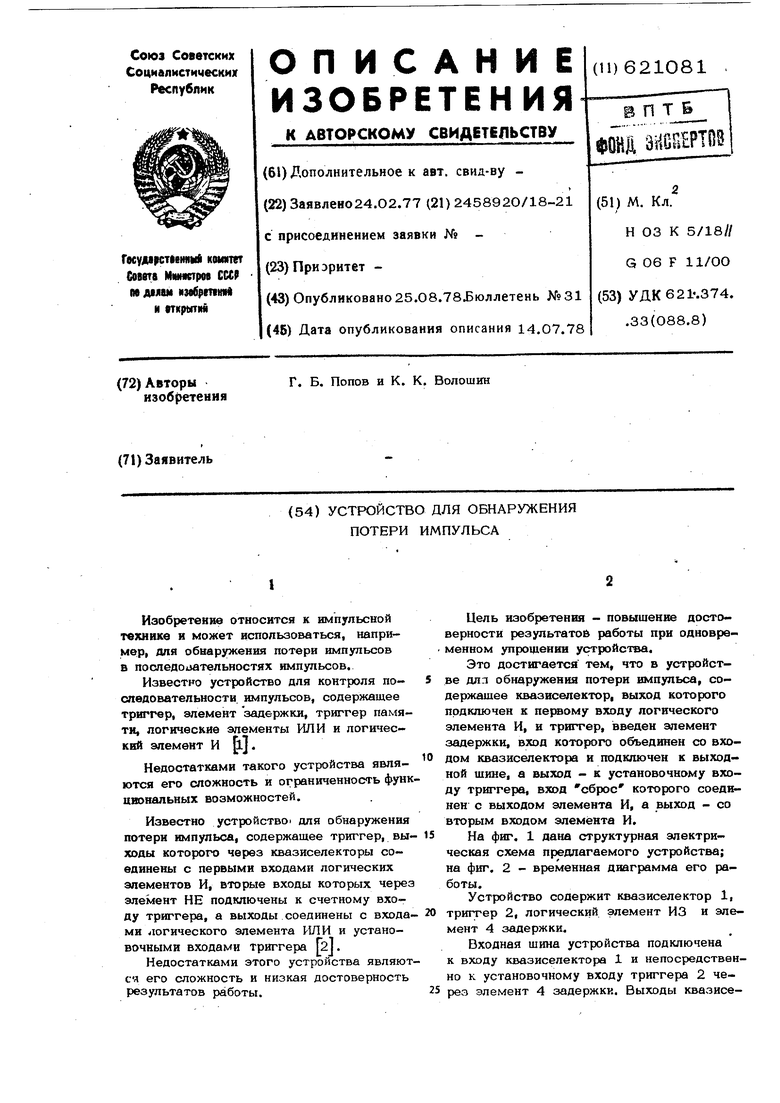

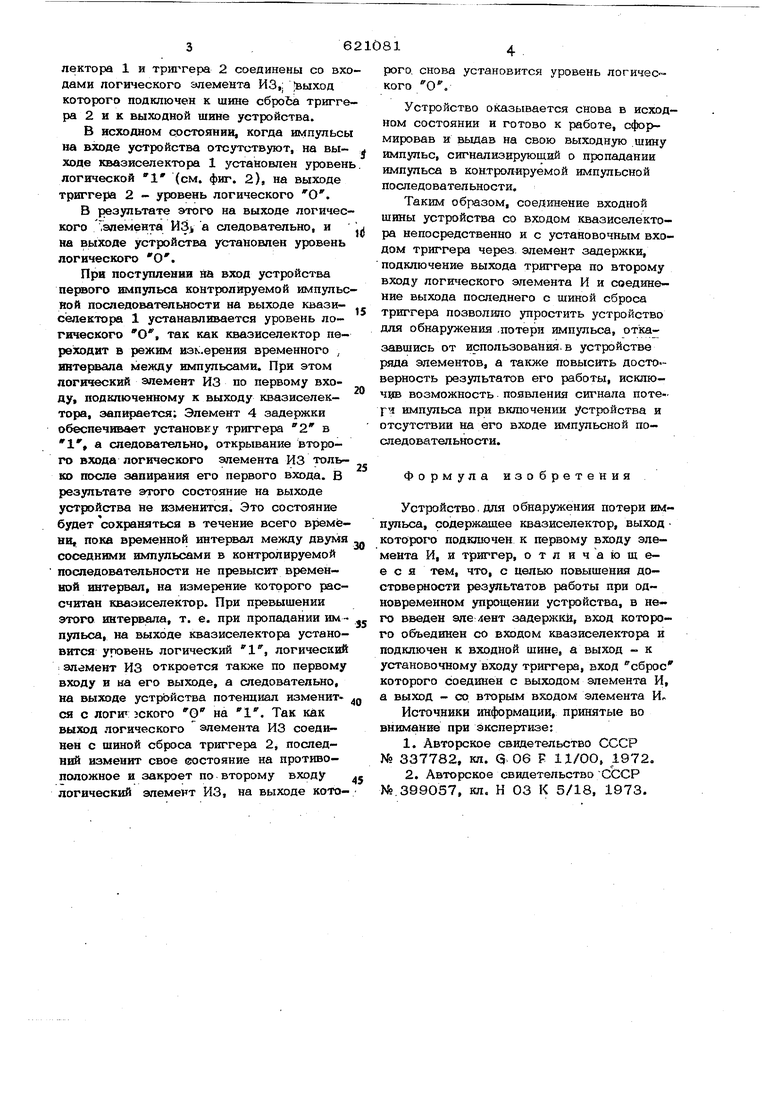

Изобретение откосится к импульсной технике и может использоваться, например, для обнаружения потери импульсов в последоллтельностях импульсов. Известно устройство для контроля последовательности, импульсов, содержащее триггер, элемент задержки, триггер памяти, логические элементы ИЛИ и логический элемент И . Недостатками такого устройства являются его сложность и ограниченность фун циональных возможностей. Известно устройство для обнаружения потери импульса, содержащее триггер, вы ходы которого через квазиселекторы соединены с первыми входами логических элементов И, вторые входы которых чере элемент НЕ подключены к счетному входу триггера, а выходы соединены с входа ми логического элемента ИЛИ и установочными входами триггера J2. Недостатками этого устройства являют ся его сложность и низкая достоверность результатов работы. Цель изобретения - повышение достоверности результатов работы при одновременном упрощении устройства. Это достигается тем, что в устройстве длл обнаружения потери импульса, содержашее квазиселектор, выход которого подключен к перэому входу логического элемента И, и триггер, введен элемент задержки, вход которого объединен со входом квазиселектора и подключен к выходной шине, а выход - к установочному входу триггера, вход сброс которого соединен с выходом элемента И, а выход - со вторым входом элемента И. На фиг. 1 дана структурная электрическая схема предлагаемого устройства; на фиг. 2 - временная диаграмма его работы. Устройство содержит квазиселектор 1, триггер 2, логический элемент ИЗ и элемент 4 задержки. Входная шина устройства подключена к входу квазиселектора 1 и непосредственно к установочному входу трнггера 2 через элемент 4 задержки. Выходы квазнселектора 1 и 2 соединены со вх дами логического элемента ИЗ,: ;выход которого подключен к шине сброЬа тригге ра 2 и к выходной шине устройства. В исходном состоянии, когда импульсы на входе устройства отсутствуют, на выходе квазиселектора 1 установлен уровен логической 1 (см. фиг. 2), на выходе триггера 2 - уртвень логического О. В результате этого на выходе логичес кого Тэпемента И3 а следовательно, и на выходе устройства установлен уровень логического О. При поступления на вход устройства первого импульса контролируемой импульс Ной последовательности на выходе квазис электора 1 устанавливается уровень логического О, так как квазиселектор переходит в режим изк.ерения временного , интерсала между импульсами. При этом логический элемент ИЗ по первому входу, подключенному к выходу квазисепектора, запирается; Элемент 4 задержки обеспечивает установку триггера 2 в I, а следовательно, открывание второго входа логического элемента ИЗ только после запирания его первого входа. В результате этого состояние на выходе устройства не изменится. Это состояние будет сохраняться в течение всего времени,, пока временной интервал между двумя соседними импульсами в контролируемой последовательности не превысит временной интервал, на измерение которого рассчитан квазиселектор. При превышении этого интершала, т. е. при пропадании импульса, на выходе квазиселектора установится уровень логический i, логический элемент ИЗ откроется также по первому входу и на его выходе, а следовательно, на выходе устройства потенциал изменит ся с логш эского О на 1. Так как выход логического элемента ИЗ соединен с шиной сброса триггера 2, последний изменит свое состояние на противоположное и закроет по второму входу логический элемент ИЗ, на выходе которого. снова установится уровень логического О. Устройство оказывается снова в исходном состоянии и готово к работе, сформировав и вьщав на свою выходную шину импульс, сигнализир5аощий о пропадании импульса в коатроляруемой импульсной последовательности. Таким образом, соединение входной шины устройства со входом квазиселектора непосредственно и с установочным входом триггера через элемент задержки, подключение выхода триггера по второму входу логического элемента И и соединение выхода последнего с шиной сброса триггера позволшо упростить устройство для обнаружения .потери импульса, отказавшись от использования, в устройстве р$ща элементов, а также повысить достоверность результатов его работы, исключда возможность появления сигнала поте-. f4 импульса при включении устройства и отсутствии на его импульсной последовательности. Формула изобретения Устройство, для обнаружения потери импульса, содержащее квазисеяектор, выход которого подключен к первому входу элемента И, и триггер, отл ичающее с я тем, что, с целью повышения достоверности резуяьтатов работы при одновременном упрощении устройства, в него введен эле /5ент задержки, вход которого объединен со входом квазиселектора и подключен к входной шине, а выход - к установочному входу триггера, вход сброс которого соединен с выходам элемента И, а выход - со вторым входом элемента И Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 337782, кл. (5.06 11/00, 1972. 2.Авторское свидетельство СССР №.399057, Ю1. Н 03 К 5/18, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения потерииМпульСОВ | 1979 |

|

SU834877A1 |

| Устройство для обнаружения потери импульса | 1986 |

|

SU1406755A1 |

| Устройство для обнаружения потери импульса | 1981 |

|

SU1046925A1 |

| Устройство для обнаружения потерииМпульСА | 1979 |

|

SU813742A1 |

| Устройство для обнаружения потери импульса | 1981 |

|

SU984018A1 |

| Устройство для контроля потери импульса | 1979 |

|

SU864535A1 |

| Устройство для контроля многоканальных импульсных последовательностей | 1982 |

|

SU1042171A1 |

| Устройство для контроля последовательности импульсов | 1975 |

|

SU748843A1 |

| Устройство для обнаружения потери импульса | 1985 |

|

SU1295397A1 |

| Устройство для обнаружения потери импульса | 1982 |

|

SU1095377A2 |

Авторы

Даты

1978-08-25—Публикация

1977-02-24—Подача