Изобретение относится к импульсной технике и может использоваться, например, для обнаружения потери импульсов в последовательности импульсов .

Известно устройство для обнаружения потери импульса, содержащее триггер, квазиселекторы, элементы И, элеме;нт НЕ, ИЛИ l J.

Недостатками этого устройства являются его сложность и низкая достоверность результатов работы.

Наиболее близким по технической сущности к изобретению является устройство для обнаружения потери импульсов, содержащее квазиселектор, вход которого подключен к входам устройства и элемента задержки, а выход - к первому входу элемента И, а выход элемента задержки соединен с S-входом RS-триггера, R-вход которого подключен к выходам элемента И устройства, а выход RS-триггера сое-, динен с вторым входом элемента И 2J,

Однако известное устройство будет работать неверно при потере подряд двух следующих друг за другом импуль сов последовательности, так как формирует сигнал лишь только о первом потерянном импульсе из последовательности, что снижает надежность обнаружения потери импульсов.

Цель изобретения - повьииенне нас дежности обнаружения потери импульсов.

Постсгвленная цель достигается тем, что в устройство для обнаружения потери импульса, содержащее квазисе4Q лектор, первый вход которогчэ подключен к входу устройства, а выход - к первому аходу элемента И, элемент , задержки, выход которого подключен к S-входу RS-триггера, выход которого соединен с вторым входом элемента

5 и, введен элемент ИЛИ, первый вход которого подключен к входу устройст аа и к R-входу RS-триггера, а. выход элемента ИЛИ подсоединен к второму входу квазиселектора, выход которого

20 соединен с выходом устройства и с входом элемента задержки, при этом выход элемента И подключен к второму входу Элемента ИЛИ.

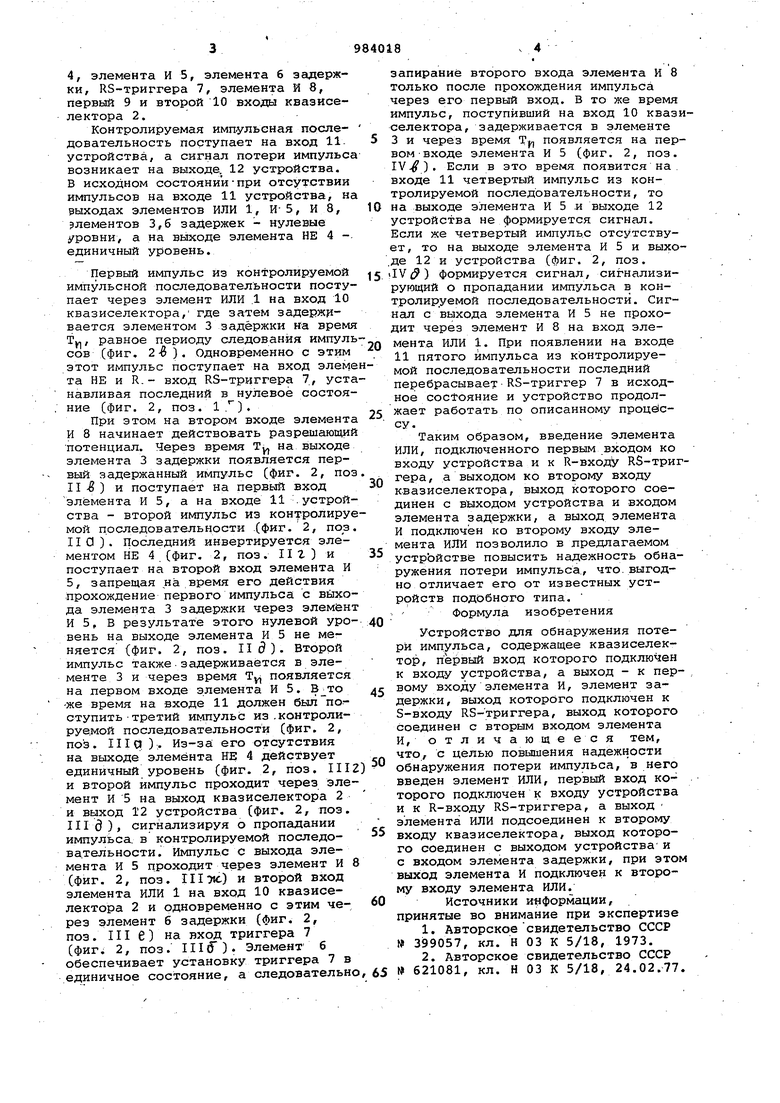

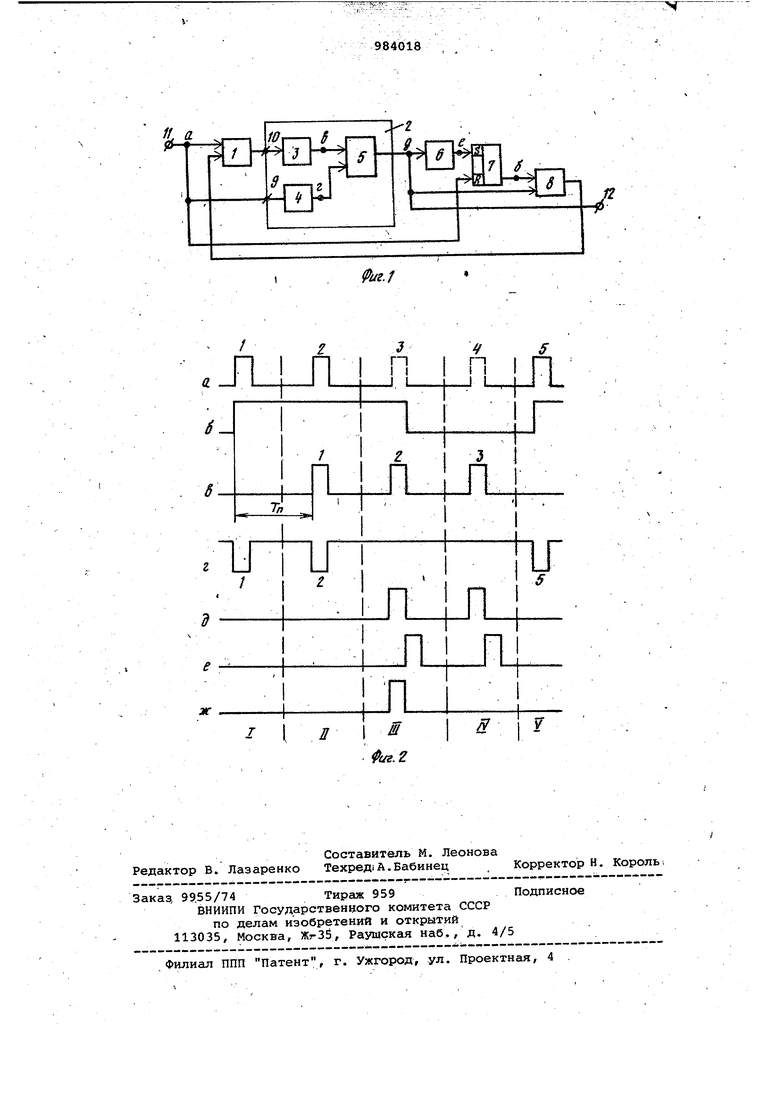

На фиг. 1 показана функциональная схема устройства , на фиг. 2 временные диаграммы его работы.

Устройство для обнаружения потери импульса состоит из элемента 1 ИЛИ, квазиселектора 2, состоящего

элемента НВ

30 из элемента 3 задержки, 4, элемента И 5, элемента 6 задержки, КЗ-триггера 7, элемента И 8, первый 9 и второй 10 входы кваэиселектора 2. Контролируемая импульсная последовательность поступает на вход 11устройства, а сигнал потери импульс возникает на выходе. 12 устройства. В исходном состоянии-при отсутствии импульсов на входе 11 устройства, н выходах элементов ИЛИ 1, И-5, И 8, элементов 3,6 задержек - нулевые уровни, а на выходе элемента НЕ 4 единичный уровень. Первый импульс из контролируемой импульсной последовательности посту пает через элемент ИЛИ .1 на вход 10 квазиселектора, где затем задержг вается элементом 3 задержки на врем Tj, равное периоду следования импул сов (фиг. 2-0 ). Одновременно с этим этот импульс поступает на вход элем та НЕ и R.- вход RS-триггера 7, уст навливая последний в нулевое состояние (фиг. 2, поз. 1 Т). При этом на втором входе элемента И 8 начинает действовать разрешающий потенциал. Через время Tyj на выходе элемента 3 задержки появляется первый задержанный импульс (фиг. 2, поз II-и ) и поступает на первый вход элемента И 5, а на входе 11 -.устройства - второй импульс из контролируе мой последовательности .(фиг. 2, поз 110). Последний инвертируется элементом НЕ 4 (фиг. 2, поз. IIZ) и поступает на второй вход элемента И 5, запрещая на время его действия прохождение первого импульса с выхода элемента 3 задержки через элемент И 5, В результате этого нулевой уровень на выходе элемента И 5 не меняется (фиг. 2, поз. II 5). Второй импульс также.задерживается в элементе 3 и через время Ту появляется на первом входе элемента И 5. же время на входе 11 должен был поступить третий импульс из.контролируемой последовательности (фиг. 2, поз. IIIq ),. Из-за его отсутствия на выходе элемента НЕ 4 дейса вует единичный уровень (фиг. 2, поз. II12 и второй импульс проходит через элемент И 5 на выход квазиселектора 2 и выход 12 устройства (фиг. 2, поз. IIIб), сигнализируя о пропадании импульса, в контролируемой последовательности. Импульс с выхода элемента И 5 ПРОХОДИТ через элемент И 8 (фиг. 2, поз. III ж) и второй вход элемента ИЛИ 1 на вход Ю квазиселектора 2 и одновременно с этим через элемент б задержки (фиг. 2, поз. III е) на вход триггера 7 (фиг. 2, поз. Illdi ). Элемент б обеспечивает установку триггера 7 в единичное состояние, а следовательно запирание второго входа элемента И 8 только после прохождения импульса через его первый вход. В то же время импульс, поступивший на вход 10 квазиселектора, задерживается в элементе 3 и через время Т появляется на первом-входе элемента И 5 (фиг. 2, поз. IV .). Если в это время появится на входе 11 четвертый импульс из контролируемой последовательности, то на выходе элемента И 5 .и выходе 12 устройства не формируется сигнал. Если же четвертый импульс отсутствует, то на выходе элемента И 5 и выходе 12 и устройства (фиг. 2, поз. IV с) формируется сигнал, сигнализирующий о пропадании импульса в контролируемой последовательности. Сигнал с выхода элемента И 5 не проходит через элемент И 8 на вход элемента ИЛИ 1. При появлении на входе 11 пятого импульса из контролируемой последовательности последний перебрасывает RS-триггер 7 в исходное состояние и устройство продолжает работать по описанному процессу. Таким образом, введение элемента ИЛИ, подключенного первым входом ко входу устройства и к R-входу RS-триггера , а выходом ко второму входу квазиселектора, выход которого соединен с выходом устройства и входом элемента задержки, а выход элемента И подключ эн ко второму входу элемента ИЛИ позволило в предлагаемом устрЬйстве повысить надежность обнаружения потери импульса, что. выгодно отличает его от известных устройств подобного типа. Формула изобретения Устройство для обнаружения потери импульса, содержащее квазиселектор, первый вход которого подключен к входу устройства, а выход - к первому входу элемента И, элемент задержки, выход которого подключен к S-входу RS-триггера, выход которого соединен с вторым входом элемента И, отличающееся тем, что, с целью повышения надежности обнаружения потери импульса, в него введен элемент ИЛИ, первый вход которого подключен к входу устройства и к R-входу RS-триггера, а выход элемента ИЛИ подсоединен к второму входу квазиселектора, выход которого соединен с выходом устройства и с входом элемента задержки, при этом выход элемента И подключен к второму входу элемента ИЛИ. Источники и|5формации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 3 Э9057, кл. Н 03 К 5/18, 1973. 2.Авторское свидетельство СССР № 621081, кл. Н 03 К 5/18, 24.02.77.

а S а IF

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения потери импульса | 1986 |

|

SU1406755A1 |

| Устройство для обнаружения потери импульса | 1977 |

|

SU621081A1 |

| Устройство для контроля последовательности импульсов | 1975 |

|

SU748843A1 |

| Устройство для обнаружения потери импульса | 1981 |

|

SU1046925A1 |

| Устройство для обнаружения потери | 1978 |

|

SU731572A2 |

| Устройство для обнаружения потери импульса | 1983 |

|

SU1157670A1 |

| Устройство для обнаружения потери импульса | 1982 |

|

SU1095377A2 |

| Устройство для обнаружения потерииМпульСА | 1979 |

|

SU813742A1 |

| Устройство для контроля многоканальных импульсных последовательностей | 1982 |

|

SU1042171A1 |

| Устройство для обнаружения потерииМпульСОВ | 1979 |

|

SU834877A1 |

Авторы

Даты

1982-12-23—Публикация

1981-07-31—Подача