1

Изобретение относится к системам телеавтоматического управления.

По основному авт. св. № 399057 известно устройство для обнаружения потери импульса, содержащее два квазиселектора, триггер со счетным и установочными входами, два двухвходовых логических элемента И, один логический элемент ИЛИ и элемент НЕ, выходы триггера соединены с входами квазиселекторов, выходы которых подключены к входам логических элементов И, вторые входы элементов И соединены с выходами элемента НЕ, вход которой подключен к счетному входу триггера, выходы логических элементов И соединены с входами логического элемента ИЛИ и с установочными входами триггера.

Недостатком устройства является низкая помехозащищенность, так как при поступлении на вход устройства случайных импульсов (помехи), не относящихся к контролируемой последовательности, устройство не выдает сигнала аварии. Если скорость поступления случайных импульсов достаточно велика, например периоды между поступлениями случайных импульсов не больше периода импульсов контролируемой последовательности, то полное выключение импульсов контролируемой последовательности не приведет к выработке сигнала аварии.

Цель изобретения - повыщение помехоустойчивости устройства для обнаружения

5 потери импульса.

Поставленная цель достигается тем, что в устройство введены дополнительный логический элемент И и два таймера, вход первого из которых соединен с входной щп10 ной и одним входом дополнительного логического элемента И, второй вход которого подключен к выходу первого таймера, выход дополнительного логического элемента И соединен с входом второго таймера, выход которого подключен к дополнительному входу логического элемента ИЛИ и выходу Зстройства.

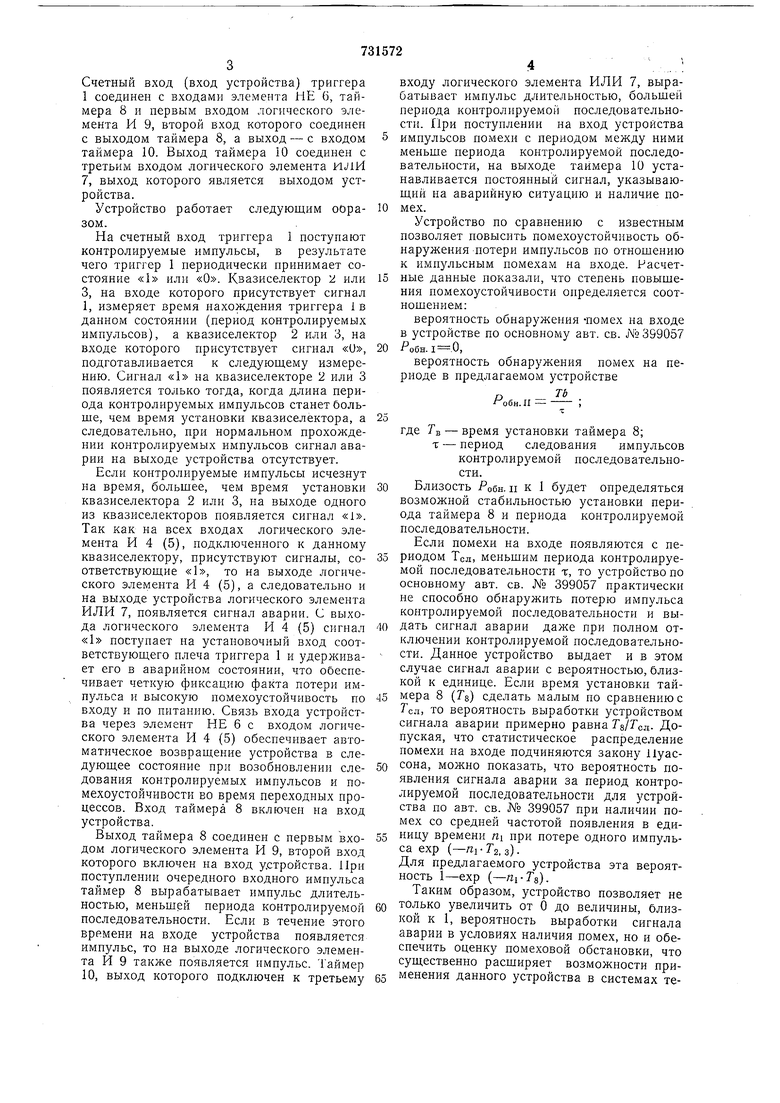

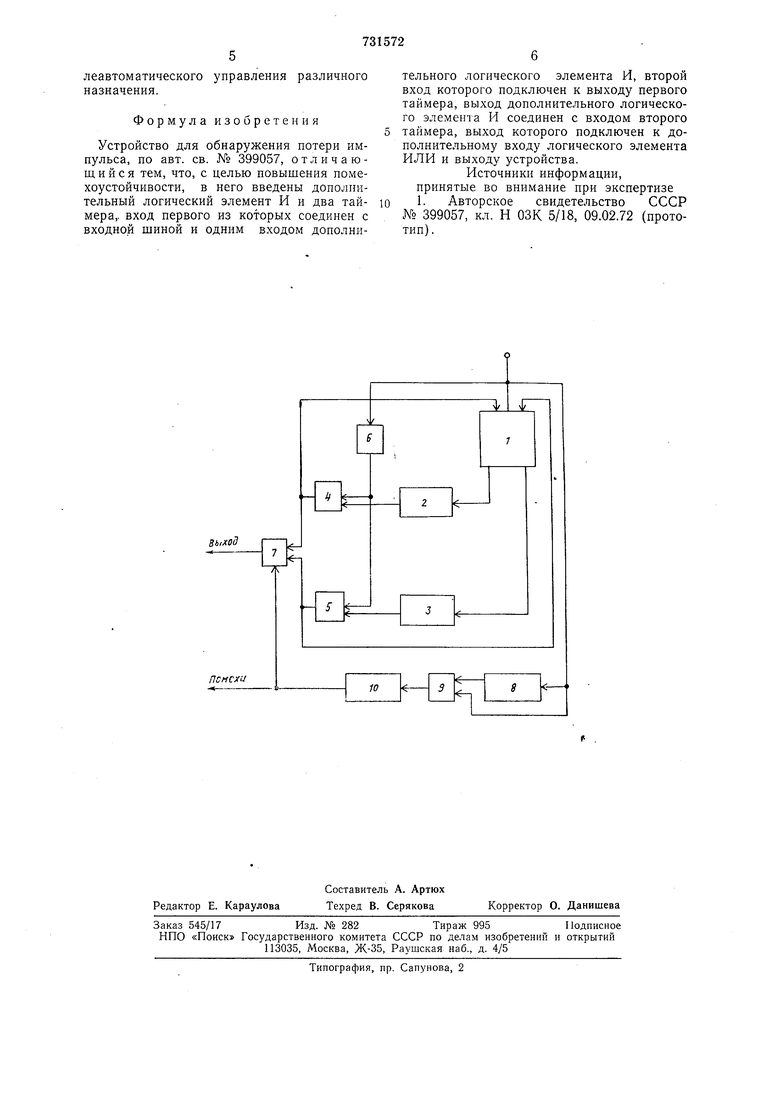

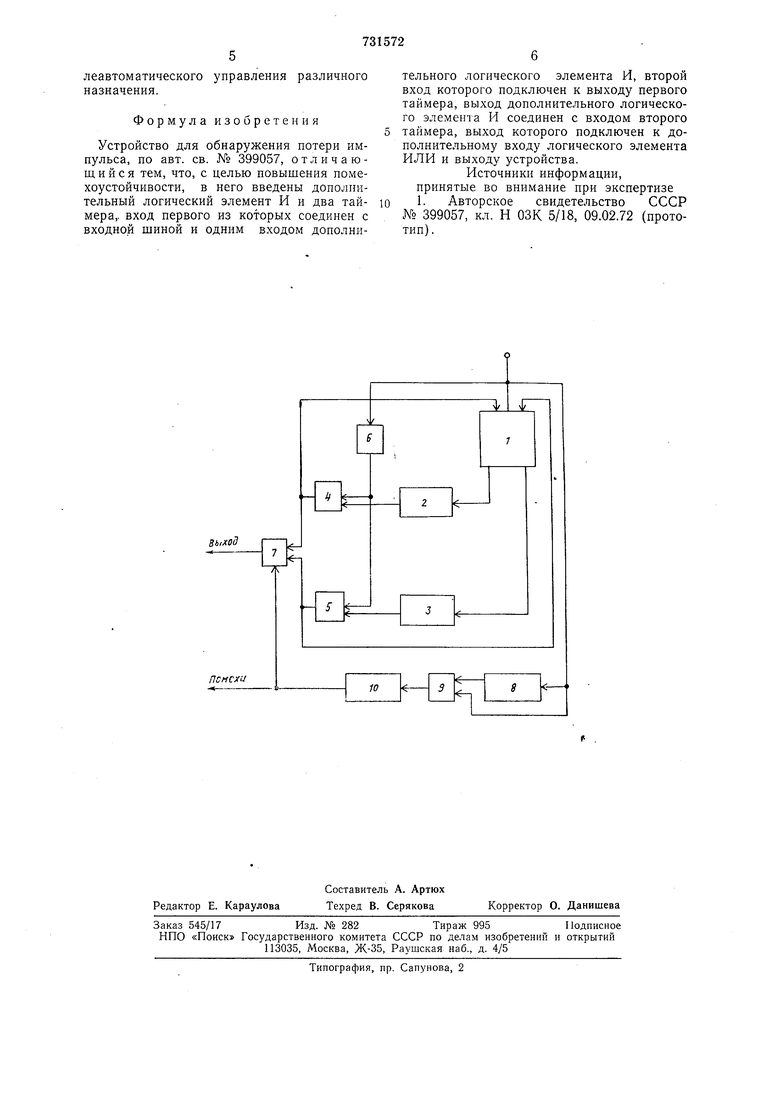

На чертеже представлена структурная электрическая схема устройства для обна20 ружения потери импульса.

Устройство содержит триггер 1, выходы которого соединены с входами квазиселекторов 2 и 3, а установочные входы - с выходами логических элементов И 4 и 5, первые входы которых соединены с выходом элемента НЕ 6, а вторые входы с выходами квазиселекторов 2 и 3 соответственно. Выходы логических элементов И 4 и 5 нагружены соответственно на первый и вто30 рой входы логического члрмента ИЛИ 7.

Счетный вход (вход устройства) триггера 1 соединен с входами элемента НЕ (5, таймера 8 и первым входом логического элемента И 9, второй вход которого соединен с выходом таймера 8, а выход - с входом таймера 10. Выход таймера 10 соединен с третьим входом логического элемента ИЛИ 7, выход которого является выходом устройства.

Устройство работает следующим ооразом.

На счетный вход триггера 1 поступают контролируемые импульсы, в результате чего триггер 1 периодически принимает состояние «I или «О. Квазиселектор 2 или 3, на входе которого присутствует сигнал 1, измеряет время нахождения триггера 1 в данном состоянии (период контролируемых импульсов), а квазиселектор 2 или 3, на входе которого присутствует сигнал «О, подготавливается к следующему измерению. Сигнал «1 на квазиселекторе 2 или 3 появляется только тогда, когда длина периода контролируемых нмпульсов станет больше, чем время установки квазиселектора, а следовательно, нри нормальном прохождении контролируемых импульсов сигнал аварии на выходе устройства отсутствует.

Если контролируемые импульсы исчезнут на время, больщее, чем время установки квазиселектора 2 или 3, на выходе одного из квазиселекторов появляется сигнал «1. Так как на всех входах логического элемента И 4 (5), подключенного к данному квазиселектору, присутствуют сигналы, соответствующие «1, то на выходе логического элемента И 4 (5), а следовательно и на выходе устройства логического элемента ИЛИ 7, появляется сигнал аварии. С выхода логического элемента И 4 (5) сигнал «1 поступает на установочный вход соответствующего плеча триггера 1 и удерл ивает его в аварийном состоянии, что обеспечивает четкую фиксацию факта потери импульса и высокую помехоустойчивость по входу н по питанию. Связь входа устройства через элемент НЕ 6 с входом логического элемента И 4 (5) обеспечивает автоматическое возвращение устройства в следующее состояние при возобновлении следования контролируемых импульсов и помехоустойчивости во время переходных процессов. Вход таймера 8 включеп на вход устройства.

Выход таймера 8 соединен с первым входом логического элемента И 9, второй вход которого включен на вход у.стройства. При поступлении очередного входного импульса таймер 8 вырабатывает импульс длительностью, меньщей периода контролируемой последовательности. Если в течение этого времени на входе устройства появляется импульс, то на выходе логического элемента И 9 также появляется импульс. Таймер 10, выход которого подключен к третьему

входу логического элемента ИЛИ 7, вырабатывает импульс длительностью, больщей периода контролируемой последовательности. При поступлении на вход устройства

импульсов помехи с периодом между ними меньще периода контролируемой последовательности, на выходе таймера 10 устанавливается постоянный сигнал, указывающий на аварийную ситуацию и наличие помех.

Устройство по сравнению с известным позволяет повысить помехоустойчивость обнаружения потери импульсов по отнощению к имнульсным помехам на входе. Расчетные данные ноказали, что степень повыщения помехоустойчивости определяется соотнощением:

вероятность обнаружения -помех на входе в устройстве по основному авт. св. № 399057

Робн.,

вероятность обнаружения помех на периоде в нредлагаемом устройстве о - ТЬ

оби.II -)

г

где Гв - время установки таймера 8;

т - период следования импульсов контролируемой носледовательности.

Близость Робн. II к I будет определяться возможной стабильностью установки периода таймера 8 и периода контролируемой последовательности.

Если помехи на входе появляются с периодом Тол, меньщим нериода контролируемой последовательности т, то устройство по основному авт. св. № 399057 практически не способно обнаружить потерю импульса контролируемой последовательности и выдать сигнал аварии даже при полном отключении контролируемой последовательности. Данное устройство выдает и в этом случае сигнал аварии с вероятностью,близкой к единице. Если время установки таймера 8 (Tg) сделать малым но сравнению с Гсл, то вероятность выработки устройством сигнала аварии примерно равна Допуская, что статистическое распределение помехи на входе подчиняются закону Пуассона, можно показать, что вероятность появления сигнала аварии за период контролируемой последовательности для устройства по авт. св. № 399057 при наличии помех со средней частотой появления в единицу времени HI при потере одного импульса ехр (-ЛгГг, з).

Для предлагаемого устройства эта вероятность 1-ехр (-ni-Ts). Таким образом, устройство позволяет не

только увеличить от О до величины, близкой к 1, вероятность выработки сигнала аварии в условиях наличия помех, но и обеспечить оценку помеховой обстановки, что существенно расширяет возможности применения данного устройства в системах телеавтоматического управления различного назначения.

Формула изобретения

Устройство для обнаружения потери импульса, по авт. св. № 399057, отличающийся тем, что, с целью повышения помехоустойчивости, в него введены дополнительный логический элемент И и два таймера,, вход первого из которых соединен с входной шиной и одним входом дополнительного логического элемента И, второй вход которого подключен к выходу первого таймера, выход дополнительного логического элемента И соединен с входом второго таймера, выход которого подключен к дополнительному входу логического элемента ИЛИ и выходу устройства.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР Afb 399057, кл. Н ОЗК 5/18, 09.02.72 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ОБНАРУЖЕНИЯ ПОТЕРИ ИМПУЛЬСА | 1973 |

|

SU399057A1 |

| Устройство для обнаружения потери импульса | 1977 |

|

SU621081A1 |

| Устройство для обнаружения потерииМпульСОВ | 1979 |

|

SU834877A1 |

| Устройство для обнаружения потерииМпульСА | 1979 |

|

SU813742A1 |

| Устройство для контроля скорости изменения частоты | 1979 |

|

SU885884A2 |

| Устройство для обнаружения потери импульса | 1981 |

|

SU1046925A1 |

| Устройство для контроля последовательности импульсов | 1975 |

|

SU748843A1 |

| Устройство для обнаружения потери импульса | 1986 |

|

SU1406755A1 |

| Устройство для обнаружения потери импульса | 1982 |

|

SU1095377A2 |

| Устройство для питания пьезокерамического преобразователя | 1981 |

|

SU1000120A2 |

Авторы

Даты

1980-04-30—Публикация

1978-02-24—Подача