(Л

эо

ю

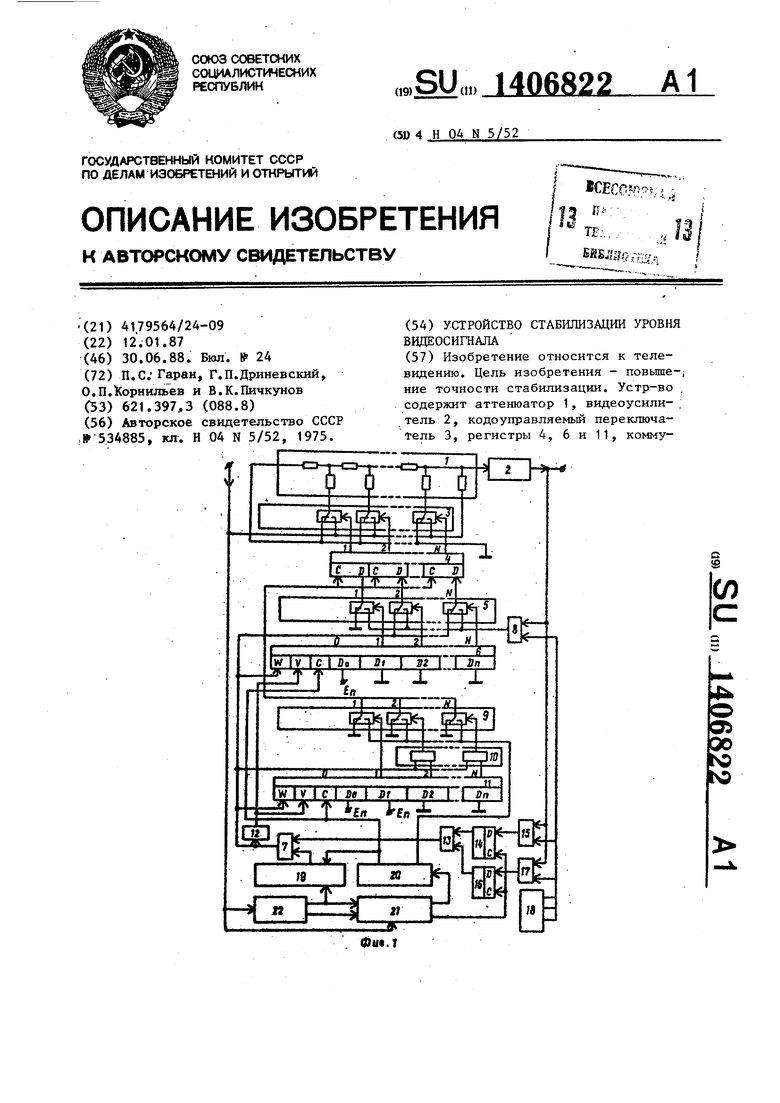

таторы 5 и 9, эл-т И 7, блоки сравнения 8, 15 и 17, блок эл-тов ИЛИ 10, эл-т задержки 12, эл-т ИЛИ 13, D-триггеры 14 и 16, источник 18 опорных напряжений, формирователь 19 импульсов запуска, г-р 20 тактовых импульсов, формирователь 21 стробирующих импульсов и селектор 22 синхроимпульсов строки полей. Цель достигается путем сокращения времени перестройки коэф. передачи аттенюатора 1, которым определяется уровень телевизионного сигнала. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство стабилизации уровня телевизионного сигнала | 1988 |

|

SU1536522A1 |

| УСТРОЙСТВО СТАБИЛИЗАЦИИ УРОВНЯ ВИДЕОСИГНАЛА | 1993 |

|

RU2060595C1 |

| Устройство для проверки электрического монтажа | 1986 |

|

SU1336035A1 |

| Устройство для преобразования телевизионного стандарта | 1986 |

|

SU1343562A1 |

| Цветная телевизионная камера | 1984 |

|

SU1233301A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ ВРЕМЕНИ | 1995 |

|

RU2082216C1 |

| Устройство для контроля многопроводного кабеля | 1986 |

|

SU1352415A1 |

| Преобразователь телевизионного стандарта | 1981 |

|

SU1016850A1 |

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

Изобретение относится к телевидению. Цель изобретения - повьше-; ние точности стабилизации. Устр-во . . содержит аттенюатор 1, видеоусили- , тель 2, кодоуправляемый переключатель 3, регистры 4, 6 и 11, комму

1

Изобретение относится к технике г телевидения и может быть использовано в видеотрактах телевизионных систем формирования видеосигнала из сигналов различных телевизионных датчиков.

Цель изобретения - повьшение точности стабилизации.

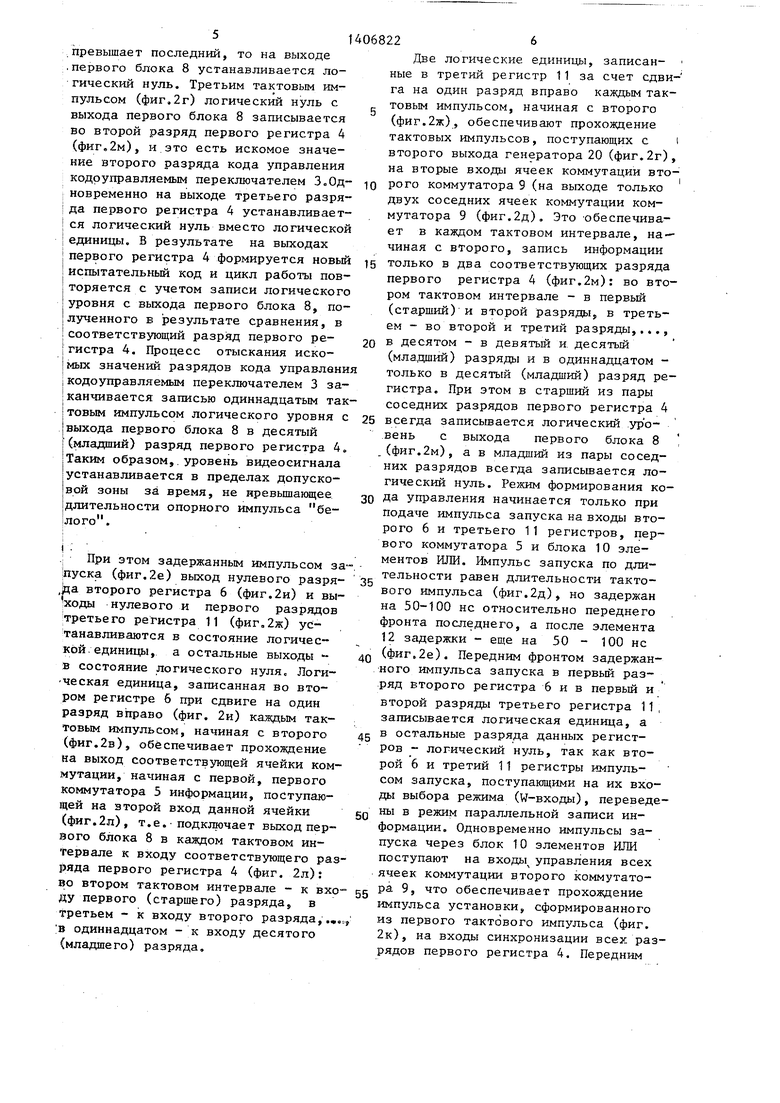

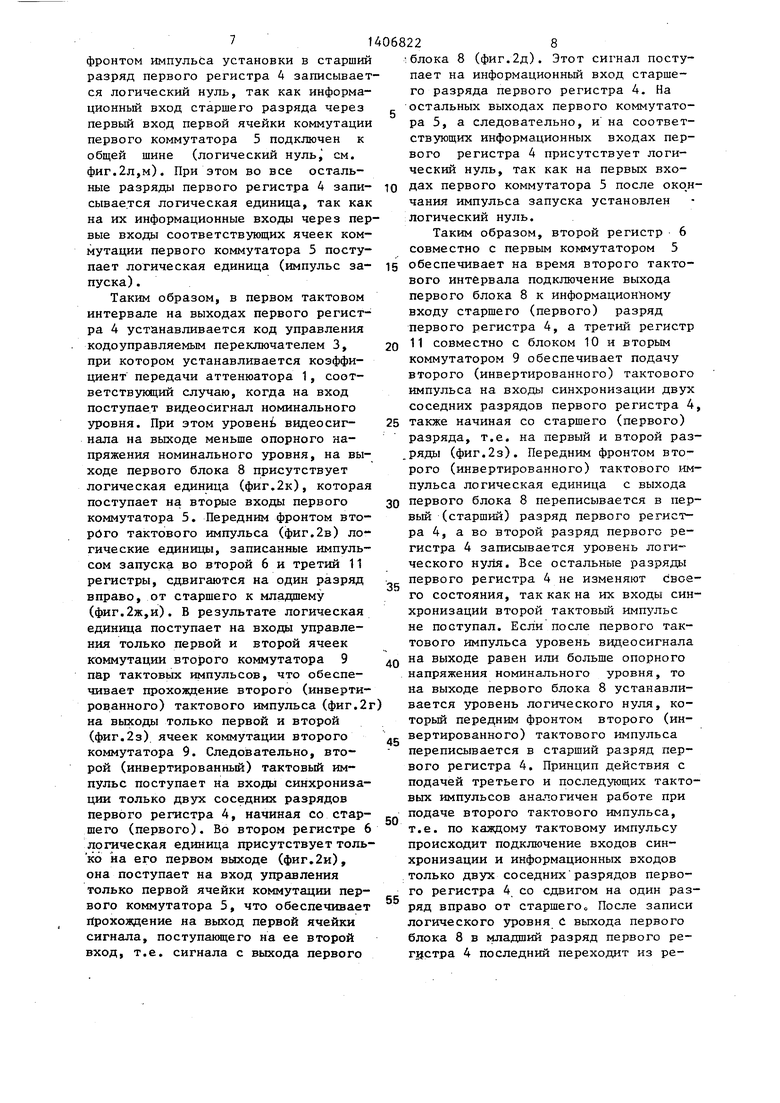

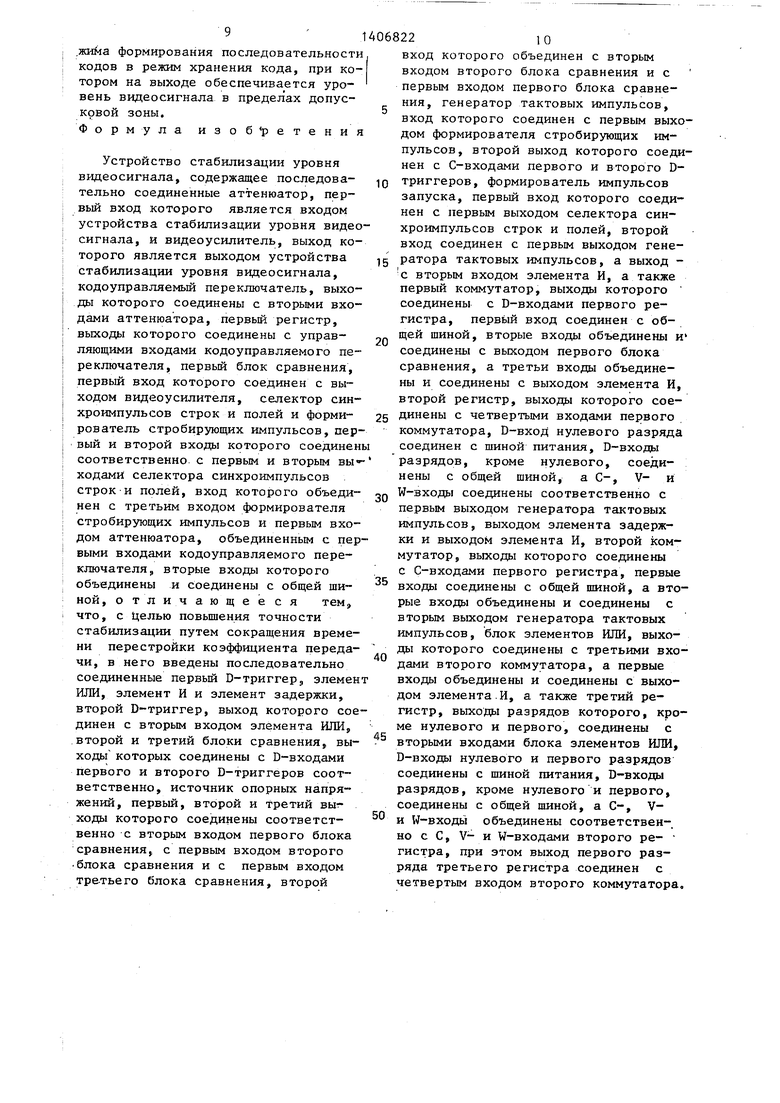

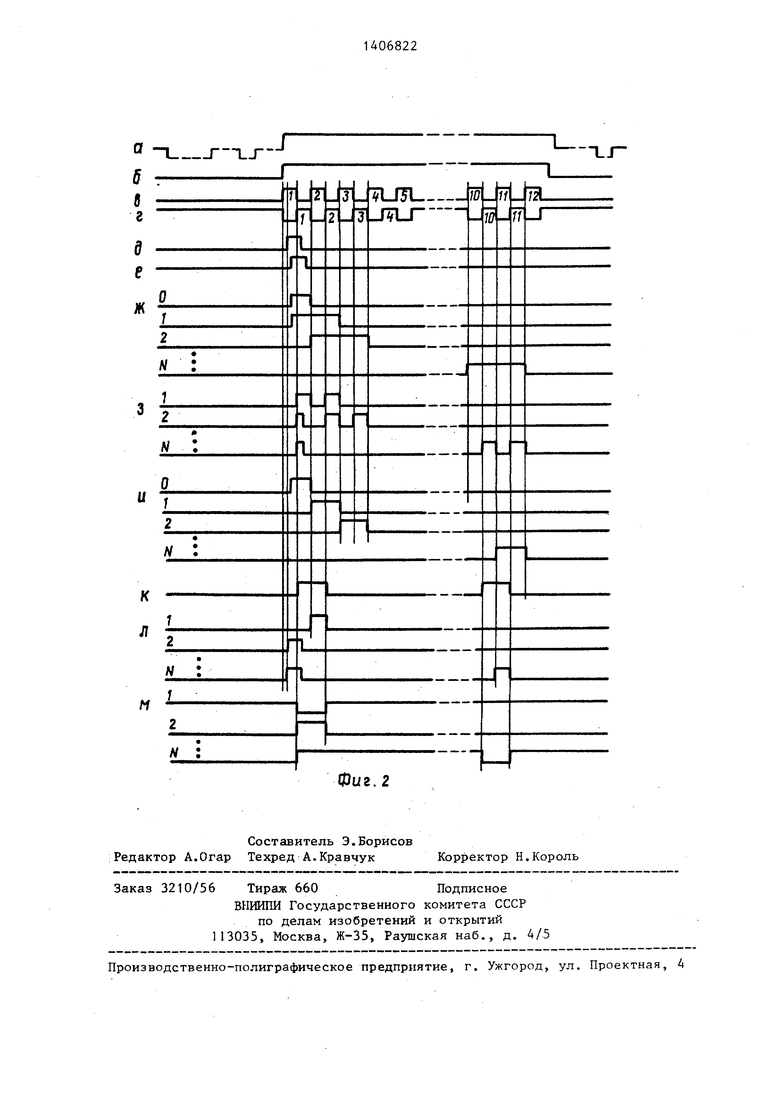

На фиг. 1 представлена электрическая структурная схема устройства, стабилизации уровня видеосигнала; на фиг.2 - временные диаграммы, поясняющие его работу.

Устройство стабилизации уровня видеосигнала (фиг.1) содержит аттенюатор 1, видеоусилитель 2, кодоуправ- ляемый переключатель 3, первый регистр 4, первый коммутатор 5, второй регистр 6, элемент И 7, первый блок 8 сравнения, второй коммутатор 9, блок 10 элементов ИЛИ, третий регистр 11, элемент 12 задержки, элемент ИЛИ 13, первый D-триггер 14, второй блок 15 сравнения, второй D- триггер 16, третий блок 17 сравнения источник 18 опорных напряжений, формирователь 19 импульсов запуска, генератор 20 тактовых импульсов, формирователь 21 стробирзтощих импульсов и селектор 22 синхроимпульсов строки полей.

Устройство стабилизации уровня, видеосигнала работает следующим образом.

При подаче питающих напряжений и полного телевизионного сигнала (фиг. 2а) видеосигнал через контакты кодо- управляемого переключателя 3 и аттенюатор 1 поступает на вход видеоусилителя ,2. Уровень телевизионного сигнала на выходе видеоусилителя 2

0

5

s

0

0

5

0

определяется коэффициентом передачи аттенюатора 1, который в момент включения может принять случайное значение в зависимости от состояния выходов первого регистра 4, которое может быть произвольным. Одновременно входной телевизионный сигнал поступает на вход селектора 22 синхроимпульсов строк и полей и на вход формирователя 21 стробирующих импульсов. Синхроимпульсы строк с выхода селектора 22 поступают на вход формирователя 21 стробирующих импульсов. Синхроимпульсы полей поступают на вход формирователя 21 и на вход формирователя 19 импульсов запуска для его сброса. В формирователе 21 стробирующих импульсов после отсчета 17 синхроимпульсов строк формируют импульс разрешения, который обеспечивает прохождение импульса, соответствующего опорному импульсу белого, передний фронт которого совпадает с передним фронтом импульса белого, а длительность короче импульса белого на 400-500 НС.

Стробирующий импуЛьс (фиг. 26) с выхода формирователя 21 запускает и синхронизирует работу генератора 20 тактовых импульсов (фиг.2в). Инвертированный стробирзтощий импульс с другого выхода формирователя 21 обеспечивает запись логических уровней, характеризующих величину уровня выходного видеосигнала, с выходов второго 15 и третьего 17 блоков в первый 14 и второй 16 D-триггеры соответственно. Логические уровни на выходах второго 15 и третьего 17 блоков формируются в результате сравнения уровней видеосигнала на выходе видеоусилителя 2 с опорными напряжениями от

31406822

источника 18 опорных напряжений, за- вого тактового импульса,

дающих верхний и нижний пороги. В случае если уровень видеосигнала на выходе устройства находится в зоне, ограниченной верхним и нижним порогами, на выходах второго 15 и третьего 17 блоков, а следовательно первого 14 и второго 16 D-триггеров и элемента ИЛИ 13 присутствует логический нуль.

Импульс запуска, вырабатываемый формирователем 19 импульса запуска (фиг.2д), в этом случае не происходит на выход элемента И 7 и состояние выходов регистра 4 остается неизменным. Следовательно, коэффициент передачи аттенюатора 1 не изменяется и регистр 4 остается в режиме хранения случайного кода управления кодоуправляемым переключателем 3.

При выходе уровня видеосигнала из зоны, ограниченной верхним и нижним порогами, на выходах второго 15 и третьего 17 блоков и, соответственно, первого 14 и второго D-триггеров и элемента ИЛИ 13 присутствует логическая единица. При этом импульс запуска, формируемый формирователем 19 в следукнцем телевизионном поле (полукадре), подается через элемент И 7 на входы выбора режима (W-входы) второго 6 и третьего 11 регистров, на входы блока 10 элементов ШШ, а также на первые сигнальные входы первого коммутатора 5 . (фиг.2л), а через элемент 12 задержки - на входы записи (V-входы) второго 6 и третьего 11,регистров с параллельной записью информации. Нулевые разряды второго 6 и третьего 11 регистров и первый разряд третьего регистра 11 используются как ЯЧЕЙКИ памяти для записи логической единицы при подаче импульса запуска, что в дальнейшем при их поразрядном сдвиге тактовыми импульсами вправо обеспечивает синхронное управление первым 6 и вторым 9 коммутаторами.

С подачей импульса запуска на вхо ды первого 6 и второго 11 регистров, первого коммзпгатора 5 и блока 10 ; элементов ИЛИ первый регистр 4 переводится из режима хранения в режим формирования искомого кода управления кодоуправляемым переключателем 3л со следующим алгоритмом работы. Импульсом установки (фиг.2з), форми- руемым вторым коммутатором 9 из пер-.

10

15

20

25

щего с выхода генератора ;импульсов, на выходе стар го) разряда первого реги да устанавливается логич а на всех остальных выхо регистра 4 устанавливает кая единица (фиг.2м). Эт равления (011... 11) чере переключатель 3 устанавли фициент передачи аттенюа ответствующий видеосигнал го уровня.

Полученный в результа видеосигнала на выходе ви ля 2 сравнивается первым опорным напряжением номин уровня, подаваемым с выхо ника 18.

Если уровень видеосигн номинального, то на выход блока 8 (фиг.2к) присутст вень логической единицы. товым импульсом - после и тановки он соответствует товому импульсу - (фиг.2г единица с выхода первого писывается в старпиш (пер 30 первого регистра 4 (фиг, есть искомое значение ст ряда кода управления кодо переключателем 3, который те должен обеспечить номи вень видеосигнала. Одновр писью этого искомого знач управления в первый разря регистра 4 на выходе втор первого регистра 4 устан логический нуль (после им тановки был уровень логич ницы), а на всех остальны (с 3-го по 10-й) первого остается логическая едини вательно, формируется нов называемый испытательный Tojjoro значение первого ( разряда определено .(в да единица) и остается неизм втором разряде установлен кий нуль. По этому испыта ду управления происходит (за счет старшего разряда ента передачи аттенюатора вательно, и увеличение ур сигнала на выходе. Вновь ный уровень видеосигнала нивается первым блоком 8 ным уровнем, ,и если он ра

35

40

45

50

55

вого тактового импульса,

0

5

0

5

поступающего с выхода генератора 20 тактовых ;импульсов, на выходе старшего (первого) разряда первого регистра 4 всег- да устанавливается логический нуль, а на всех остальных выходах первого регистра 4 устанавливается логическая единица (фиг.2м). Этот код управления (011... 11) через кодируемый переключатель 3 устанавливает коэффициент передачи аттенюатора 1, соответствующий видеосигналу допустимого уровня.

Полученный в результате уровень видеосигнала на выходе видеоусилителя 2 сравнивается первым блоком 8 с опорным напряжением номинального уровня, подаваемым с выхода источника 18.

Если уровень видеосигнала меньше номинального, то на выходе первого блока 8 (фиг.2к) присутствует уровень логической единицы. Вторым тактовым импульсом - после импульса ус- тановки он соответствует первому тактовому импульсу - (фиг.2г) логическая единица с выхода первого блока 8 за- писывается в старпиш (первый) разряд 0 первого регистра 4 (фиг,2м). Это и есть искомое значение старшего разряда кода управления кодоуправляемым переключателем 3, который в результате должен обеспечить номинальньш уровень видеосигнала. Одновременно с записью этого искомого значения кода управления в первый разряд первого регистра 4 на выходе второго разряда первого регистра 4 устанавливается логический нуль (после импульса установки был уровень логической единицы), а на всех остальных выходах (с 3-го по 10-й) первого регистра 4 остается логическая единица. Следовательно, формируется новый код, так называемый испытательный код, у ко- Tojjoro значение первого (старшего) разряда определено .(в данном случае единица) и остается неизменным, а во втором разряде установлен логический нуль. По этому испытательному коду управления происходит увеличение (за счет старшего разряда) коэффициента передачи аттенюатора 1, а следовательно, и увеличение уровня видеосигнала на выходе. Вновь установленный уровень видеосигнала снОва сравнивается первым блоком 8 с номинальным уровнем, ,и если он равен или

5

0

5

0

5

превышает последний, то на выходе .первого блока 8 устанавливается логический нуль. Третьим тактовым импульсом (фиг,2г) логический нуль с выхода первого блока 8 записывается во второй разряд первого регистра 4 (фиг.2м), и это есть искомое значение второго разряда кода управления кодруправляемым переключателем 3.Одновременно на выходе третьего разря- i да первого регистра 4 устанавливает- I ся логический нуль вместо логической I единицы. В результате на выходах I первого регистра 4 формируется новьй I испытательный код и цикл работы пов- i торяется с учетом записи логического I уровня с выхода первого блока 8, по- лученного в результате сравнения, в соответствующий разряд первого ре- iгистра 4. Процесс отыскания иско- Iмых значений разрядов кода управлени кодоуправляемым переключателем 3 за- {канчивается записью одиннадцатым тактовым импульсом логического уровня с выхода первого блока 8 в десятый (младший) разряд первого регистра 4. Таким образом,, уровень видеосигнала устанавливается в пределах допуско- вой зоны за время, не нревьппающее |длительности опорного импульса бе- |лого.

.; При этом задержанным импульсом за

iiycKa (фиг.2е) выход нулевого разряда второго регистра 6 (фиг.2и) и вы- ;ходы нулевого и первого разрядов |третьего регистра 11 (фиг,2ж) устанавливаются в состояние логической, единицы, а остальные выходы - в состояние логического нуля„ Логи- ческая единица, записанная во втором регистре 6 при сдвиге на один разряд вправо (фиг. 2и) каждым тактовым импульсом, начиная с второго (фиг.2в), обеспечивает прохождение на выход соответствующей ячейки коммутации, начиная с первой, первого коммутатора 5 информации, поступающей на второй вход данной ячейки (фиг.2л), т.е. подключает выход первого блока 8 в каждом тактовом интервале к входу соответствующего разряда первого регистра 4 (фиг. 2л): Во втором тактовом интервале - к вхо ду первого (старшего) разряда, в третьем - к входу второго разряда,., ;в одиннадцатом - к входу десятого (младшего) разряда.

5

0

Две логические единицы, записанные в третий регистр 11 за счет сдви- га на один разряд вправо каждым тактовым импульсом, начиная с второго (фиг.2ж), обеспечивают прохождение тактовых импульсов, поступающих с i второго выхода генератора 20 (фиг.2г), на вторые входы ячеек коммутации второго коммутатора 9 (на выходе только двух соседних ячеек коммутации коммутатора 9 (фиг.2д). Это -обеспечивает в каждом тактовом интервале, на-- чиная с второго, запись информации только в два соответствующих разряда первого регистра 4 (фиг.2м): во втором тактовом интервале - в первый (старший) и второй разряды, в третьем - во второй и третий разряды,..., в десятом - в девятый и десятый (младший) разряды и в одиннадцатом - только в десятый (младший) разряд регистра. При этом в старший из пары соседних разрядов первого регистра 4

5 всегда записывается логический уровень с выхода первого блока 8 , (фиг.2м), а в младший из пары соседних разрядов всегда записьшается логический нуль. Режим формирования кода управления начинается только при подаче импульса запуска на входы второго 6 и третьего 11 регистров, первого коммутатора 5 и блока 10 элементов ИЛИ. Импульс запуска по длительности равен длительности тактового импульса (фиг.2д), но задержан на 50-100 НС относительно переднего фронта последнего, а после элемента 12 задержки - еще на 50 - 100 не

Q (фиг,2е). Передним фронтом задержанного импульса запуска в первый разряд второго регистра бив первый и второй разряды третьего регистра 11, записывается логическая единица, а в остальные разряда данных регистров - логический нуль, так как второй 6 и третий 11 регистры импульсом запуска, поступающими на их входы выбора режима (W-входы), переведены в режим параллельной записи информации. Одновременно импульсы запуска через блок 10 элементов ИЛИ поступают на входы управления всех ячеек коммутации второго коммутатоg рз. 9, что обеспечивает прохождение импульса установки, сформированного из первого тактового импульса (фиг. 2к), на входы синхронизации всех разрядов первого регистра 4. Передним

0

5

5

0

фронтом импульса установки в старший разряд первого регистра 4 записывается логический нуль, так как информационный вход старшего разряда через первый вход первой ячейки коммутации первого коммутатора 5 подключен к общей шине (логический нуль см. фиг.2л,м). При этом во все остальные разряды первого регистра 4 записывается логическая единица, так как на их информационные входы через первые входы соответствующих ячеек коммутации первого коммутатора 5 поступает логическая единица (импульс запуска) .

Таким образом, в первом тактовом интервале на выходах первого регистра 4 устанавливается код управления кодоуправляемым переключателем 3, при котором устанавливается коэффициент передачи аттенюатора 1, соот- ветствукщий случаю, когда на вход поступает видеосигнал номинального уровня. При этом уровен видеосигнала на выходе меньше опорного напряжения номинального уровня, на выходе первого блока 8 присутствует логическая единица (фиг.2к), которая поступает на вторые входы первого коммутатора 5. Передним фронтом второго тактового импульса (фиг.2в) логические единицы, записанные импульсом запуска во второй 6 и третий 11 регистры, сдвигаются на один разряд вправо, от старшего к младшему (фиг.2ж,и). В результате логическая единица поступает на входы управления только первой и второй ячеек коммутации второго коммутатора 9 пар тактовых импульсов, что обеспечивает прохождение второго (инвертированного) тактового импульса (фиг.2г на выходы только первой и второй (фиг.2з) ячеек коммутации второго коммутатора 9. Следовательно, второй (инвертированный) тактовый импульс поступает на входы синхронизации только двух соседних разрядов первого регистра 4, начиная со старшего (первого). Во втором регистре 6 логическая единица присутствует толь- к6 на его первом выходе (фиг.2и), она поступает на вход управления только первой ячейки коммутации первого коммутатора 5, что обеспечивает йрохождение на выход первой ячейки сигнала, поступакнцего на ее второй вход, т.е. сигнала с выхода первого

0

5

0

блока 8 (фиг.2д). Этот сигнал поступает на информационный вход старшего разряда первого регистра 4. На остальных выходах первого коммутатора 5, а следовательно, и на соответствующих информационных входах первого регистра 4 присутствует логический нуль, так как на первых входах первого коммутатора 5 после чания импульса запуска установлен логический нуль.

Таким образом, второй регистр 6 совместно с первым коммутатором 5 обеспечивает на время второго тактового интервала подключение выхода первого блока 8 к информационному входу старшего (первого) разряд первого регистра 4, а третий регистр 11 совместно с блоком 10 и вторым коммутатором 9 обеспечивает подачу второго (инвертированного) тактового импульса на входы синхронизации двух соседних разрядов первого регистра 4, 5 также начиная со старшего (первого) разряда, т.е. на первый и второй раз- ряды (фиг.2з). Передним фронтом второго (инвертированного) тактового импульса логическая единица с выхода первого блока 8 переписывается в первый (старший) разряд первого регистра 4, а во второй разряд первого регистра 4 записывается уровень логического нуля. Все остальные разряды первого регистра 4 не изменяют своего состояния, так как на их входы синхронизации второй тактовый импульс не поступал. Если после первого тактового импульса уровень видеосигнала на выходе равен или больше опорного

0

5

0

5

0

5

напряжения номинального уровня, то на выходе первого блока 8 устанавливается уровень логического нуля, который передним фронтом второго (инвертированного) тактового импульса переписывается в старший разряд первого регистра 4. Принцип действия с подачей третьего и последующих тактовых импульсов аналогичен работе при подаче второго тактового импульса, т.е. по каждому тактовому импульсу происходит подключение входов синхронизации и информационных входов только двух соседних разрядов первого регистра 4 со сдвигом на один разряд вправо от старшего После записи логического уровня С выхода первого блока 8 в младший разряд первого регистра 4 последний переходит из ре.жийа формирования последовательности кодов в режим хранения кода, при котором на выходе обеспечивается уровень видеосигнала в пределах допус- ковой зоны, Формула изоб ретения

Устройство стабилизации уровня видеосигнала, содержащее последовательно соединенные аттенюатор, первый вход которого является входом устройства стабилизации уровня видеосигнала, и видеоусилитель, выход которого является выходом устройства стабилизации уровня видеосигнала, кодоуправляемый переключатель, выходы которого соединены с вторыми входами аттенюатора, первый регистр, выходы которого соединены с управляющими входами кодоуправляемого переключателя, первьй блок сравнения, первый вход которого соединен с выходом видеоусилителя, селектор синхроимпульсов строк и полей и формирователь стробирующих импульсов, первый и второй входы которого соединен соответственно, с первым и вторым выходами селектора синхроимпульсов строки полей, вход которого объединен с третьим входом формирователя стробирующих импульсов и первым входом аттенюатора, объединенным с первыми входами кодоуправляемого переключателя,, вторые входы которого объединены и соединены с общей шиной, о тличающее ся тем,, что, с Целью повьпиения точности стабилизации путем сокращения времени перестройки коэффициента передачи, в него введены последовательно соединенные первый D-триггер, элемен ИЛИ, элем€:нт И и элемент задержки, второй D-триггер, выход которого соединен с вторым входом элемента ИЛИ, второй и третий блоки сравнения, выходы которых соединены с D-входами первого и второго D-триггеров соответственно, источник опорных напряжений, первый, второй и третий ходы которого соединены соответственно с вторым входом первого блока сравнения, с первым входом второго блока сравнения и с первым входом третьего блока сравнения, второй

5

0

5

0

5

0

вход которого объединен с вторым входом второго блока сравнения и с первым входом первого блока сравнения, генератор тактовых импульсов, вход которого соединен с первым выходом формирователя стробирующих импульсов, второй выход которого соединен с С-входами первого и второго D- триггеров, формирователь импульсов запуска, первый вход которого соединен с первым выходом селектора синхроимпульсов строк и полей, второй вход соединен с первым выходом генератора тактовых импульсов, а выход - с вторым входом элемента И, а также первый коммутатор, выходы которого соединены с D-входами первого регистра, первый вход соединен с общей шиной, вторые входы объединены и соединены с выходом первого блока сравнения, а третьи входы объединены и соединены с выходом элемента И, второй регистр, выходы которого соединены с четвертыми входами первого коммутатора, D-вход нулевого разряда соединен с шиной питания, D-входы разрядов, кроме нулевого, соединены с общей шиной, а С-, V- и W-входы соединены соответственно с первым выходом генератора тактовых импульсов, выходом элемента задержки и выходом элемента И, второй коммутатор, выходы которого соединены с С-входами первого регистра, первые входы соединены с общей шиной, а вторые входы объединены и соединены с вторым выходом генератора тактовых импульсов, блок элементов ИЛИ, выходы которого соединены с третьими входами второго коммутатора, а первые

входы объединены и соединены с выходом элемента.И, а также третий регистр, выходы разрядов которого, кроме нулевого и первого, соединены с вторыми входами блока элементов ИЛИ, D-входы нулевого и первого разрядов соединены с шиной питания, D-входы разрядов, кроме нулевого и первого, соединены с общей шиной, а С-, V- и W-входы объединены соответствен-, но с С, V- и W-входами второго ре- гистра, при этом выход первого разряда третьего регистра соединен с четвертым входом второго коммутатора.

° 1T-bJ5

0 г

-J

fl e

ж

к

л

м

ю

/г г/тМ

Ж.

гг

| Устройство автоматического регулирования уровня видеосигнала | 1975 |

|

SU534885A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-06-30—Публикация

1987-01-12—Подача