1 . 1

Изобретение относится к электро- JCBHSH, а именно, к устройствам при- :|ема избыточных сигнгшов в целом, и |может быть использовано в системах рередачн дискретной информации, в которых для передачи информации при- {меняются избыточные коды большой мощёное ти.

Целью изобретения является распш- прение области применения путем обес- |печения автоматического регулировани |задающего порога.

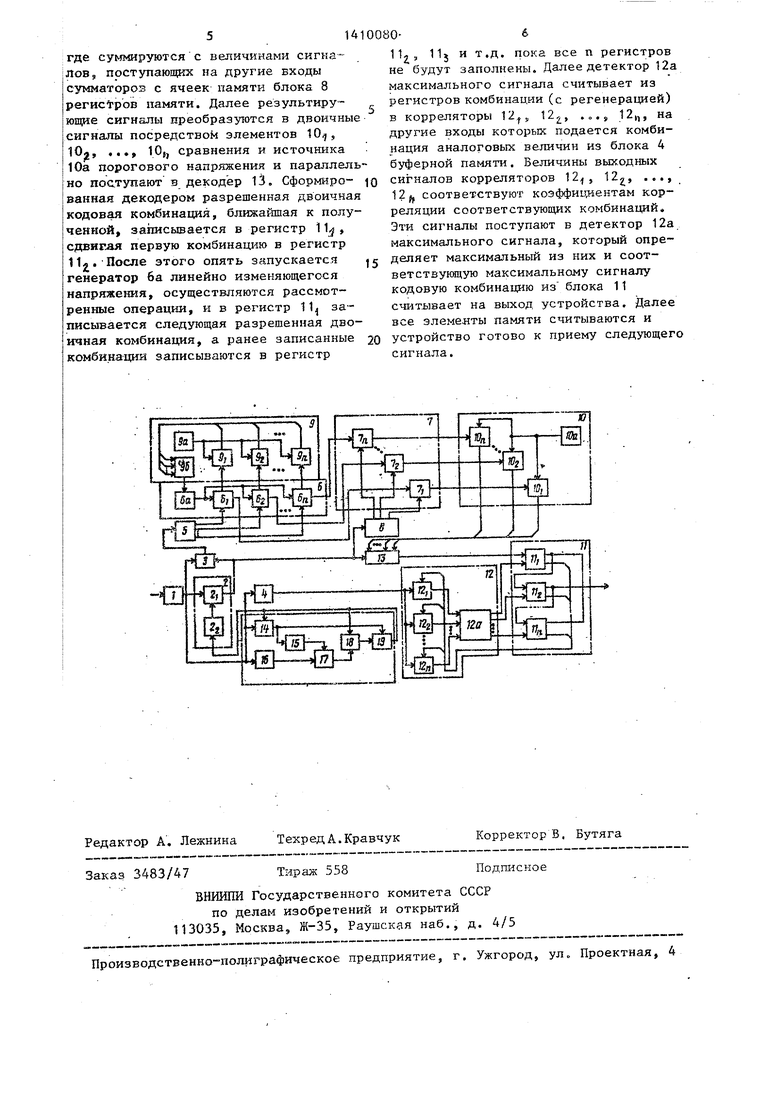

I На чертеже приведена функциональная схема предлагаемого устройства.

Устройство содержит приемник 1,, преобразующий элемент избыточного сигнала в аналоговые величины, например а шлитуду импульсов, первый

|пороговьш селектор 2, состоящий из

I элемента 2 сравн-ения и управляемого

Iисточника Ъ. порогового напряжения,

{величина которого устанавливается

I автоматически в зависимости от уровн

помехи, блок 3 вычитания, в котором

I из величин амплитуд выходных имI пульсов элемента 2 сравнения вычитаIются величины амплитуд его выходных

I импульсовS первый и второй блоки

|4 и 5 буферной памяти, -реализованные

I напримерS в виде дискретно-аналоговы

линий задержки, усилитель 6, состояI щий из п усилителей 6, 6j, ..., 6,

с регулируемыми коэффициентами уси

I ления и регенератора б, линейно из-

I меняющегося напряжения, выходное напI ряженке которого осуществляет синхроI ное изменение коэффициента усиления

усилителей 6, 6

2

6ц, сумматор

40

7, осуществля тций поразрядное сложение колебаний сигналов, поступающих

на его входы и состоящий из п одноразрядных сумматоров (например, операционных усилителей 7 , 7 , ..., 7„ ), второй блок 8 регистров памяти, реат 45 лизует-ый в виде, например, последовательного цифрового регистра, информация с которого считывается параллельно, второй пороговый селектор 9, состоящий из п элементов 9 , 9,, .. ., Q 9, сравнения, источник 9апорогового напряжения ификсатора 96 перехода величины порогового напряжения величиной амплитуды сигнала на выходе одного из усилителей 6 , 6 , . .., 6,, тр-етий по- роговый селектор 10,состоящий из элементов -10/, 10;, ..., 10, сравнения и источника 10а порогового напряжения, первый блок 11 регистров памяти.

состоящий из двоичных регистров 1Ц, 1 12, } llj) блок 12 управления вьщачей информации, состоящий из п-корреляторов 12, 12, .., 12, и детектора 12а максимального сигнала, декодер 13, в котором каждой поступающей на его входы двоичной кодовой комбинации ставится в соответствие ближайшая разрешенная двоичная кодовая комбинация, усилитель 14 с регулируемым коэффициентом усиления, компаратора 15, усилитель 16 с постоянным коэффициентом усиления, 5 управляемый ключ 17, сумматор 18, сравнивающее устройство 19 и блок управления и синхронизации (не показан) .

Сущность работы элементов загслю- чается в следующем.

Введенные элементы реализуют процедуру обучения с выравненными ошибками, которая описывается математическим вьфажением

0

5

V(n+1) V(n) + (n),

|Y(n), V (n)Y(n) A 0; (-Y(n), V(n)Y(n) 0,

5

0

5 Q

и сходимость которой к минимуму вероятности ошибки, доказана.

V(n+1), V(n) - коэффициенты усиления усилителя с регулируемым коэффициентом усиления, выполненного по стандартной схеме; S - шаг, с которым данная процедура сводится к минимуму вероятности ошибки и реализуется, например, коэффициентом усиления усилителя с постоянным коэффициентом усиления, выставляемым вручную или автоматически с зависимости от характера нестационарной помехи в канале связи; Y(n) - образцы канальных сигналов, искаженные помехой и поступающие на вход приемника.

31410080

Устройство работает следующим об- . азом.

па ем ря ро ти от ем вы ще ны ан по эл О об зу ни вы ан в ва ст но

На вход приемника 1 поступает сложный избыточный сигнал. На выходе приемника 1 появляется (последователь- но) совокупность аналоговых сигналов

У.

у) , соответствую

Y.

щих элементам входного сигнала, где п - количество элементарных сигналов в составном избыточном сигнале и количество двоичных символов в комбинации избыточного кода. Каждый аналоговый сигнал подается на вход усилителя 14 с регулируемым коэффициентом усиления, на вход усилителя 16 с постоянным коэффициентом усиления и на первый вход порогового селектора 2. С выхода усилителя 14 с регулируемым коэффициентом усиления усиленные в V раз аналоговые сигналы поступают на компаратор 15, где производится сравнение полученного произведения V(n) (V) с нулем. По результатам сравнения компаратор 13 управляет управляемым ключом 17, разрешая прохождение сигнала .Г„У(п) с выхода усилителя .16 с постоянным коэффициентом усиления либо инверсно, либо неинверсно, т.е. определяет знак произведения S Y(n). Полученный сигнал поступает на второй вход суммтора 18, на первый вход которого поступает си1 нал с выхода сравнивающего устройства 19, который является оцен кой коэффищента усиления (и соответственно пропорционален ему) усилителя 14 с регулируемым коэффициентом усиления на данном шаге. На выходе сумматора 1В в зависимости от знака произведения Sn(Yn) получается разность или сумма V(n)± Sn .Y(n), которая поступает на вход сравнивающего устройства 19, где сравнивается с сигналом, поступающим на его второй вход с выхода усилителя 14 с регулируемым коэффициентом усиления. Напряжение, полученное на выходе сравнивающего устройства 19 в результате сравнения, одновременно регулирует коэффициент усиления усилителя 14 с регулируемым коэффициентом усиления и поступает на второй вход порогового селектора 2, а именно на вход управляемого источника 2 порогового напряжения, которое изменяется любым известным способом, например изменяеся коэффициент усиления усилителя. На вход элемента 2 сравнения посту

0

5

0

5

0

0

45

50

55

пает аналоговый сигнал с выхода приемника 1. На второй вход элемента 2 сравнения поступает пороговое напряжение управляемого источника 2 порогового напряжения, которое автоматически изменяется в зависимости от отношения сигнал/шум на выходе приемника 1 по алгоритму, описанному выше. В элементе 2 сравнения осуществляется сравнение величин входных сигналов. Если величина входного аналогового сигнала меньше величины порогового напряжения, то на выходе элемента сравнения появится сигнал О, в противном случае - 1. Таким образом аналоговый сигнал преобразуется в двоичный. В блоке 3 вьиита- ния из величины двоичного сигнала вычитают величину соответствующего аналогового сигнала. В результате в декодере 13 последовательно записывается кодовая комбинация, соответствующая посимвольному приему входного сигнала.

Декодер в регистр 11 после соот,ветствующих операций записывает (.последовательно) двоичную разрешенную кодовую комбинацию, являющуюся бли- жайшей к двоичной посимвольной. В блоке 8 регистров памяти также последовательно записывается и хранится в нем двоичная .кодовая комбинация

(посимвольного приема. В блок 5 буферной памяти записывается и хранится соЕокупность аналоговых сигналов, полученных с выхода блока 3 вычитания . Из блока 5 памяти эти сигналы параллельно подаются на усилители 6, 62., ..., 6„ с регулируемыми коэффициентами усиления. Б это.время запускается генератор 6а линейно изменяющегося напряжения и коэффициент усиления усилителей увеличивается (начальный коэффициент усиления равен 1). Выходные сигналы усилителей, подаются на элементы 9 , 9 , . .., 9,, сравнения, к другим выходам которых подключен источник 9а порогового напряжения. Как только в каком-нибудь элементе сравнения выходной сигнал усилителя превысит величину порогового напряжения, сразу же срабатывает фиксатор 96 перехода и генератор 6а линейно изменяющегося напряжения выключится. Усиленные сигналы с выхода усилителей 6.J , 62., ..., 6, подаются на выходы соответствующих одноразрядных сумматоров 7, , 1, ..., l,

где суммируются с величинами сигналов, поступающих на другие входы сумматоров с ячеек памяти блока 8 регистров памяти. Далее результирующие сигналы преобразуются в двоичные сигналы посредством элементов 10.}, 10}, 10,j сравнения и источника 10а порогового напряжения и параллельно поступают в декодер 13, Сформиро- ванная декодером разрешенная двоичная кодовая комбинация, ближайшая к полученной, записывается в регистр 11, сдвигая первую комбинацию в регистр 11-, После этого опять запускается генератор 6а линейно изменяющегося напряжения, осуществляются рассмотренные операции, и в регистр 11 за

писывается следующая разрешенная двоичная комбинация, а ранее записанные 20 комбинации записываются в регистр

15

11

2э 11j И Т.д. пока все п регистров не будут заполнены. Далее детектор 12а максимального сигнала считывает из регистров комбинации (с регенерацией)

в корреляторы 12

-г

12

Г) 9

на

другие входы которых подается комбинация аналоговых величин из блока 4 буферной памяти. Величины вых.одных сигналов корреляторов 12, 12j, ..., 12fj соответствуют коэффициентам корреляции соответствующих комбинаций. Эти сигналы поступают в детектор 12а максимального сигнала, который опре- деляет максимальный из них и соответствующую максимальному сигналу кодовую комбинацию из блока 11 считывает на выход устройства. Далее все элементы памяти считываются и устройство готово к приему следующего сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное устройство для приема избыточной информации | 1981 |

|

SU1012310A1 |

| Адаптивное устройство для приема избыточной информации | 1981 |

|

SU1001145A1 |

| Устройство для приема избыточной информации | 1988 |

|

SU1557578A2 |

| Устройство для приема избыточной информации | 1983 |

|

SU1101873A1 |

| Устройство для приема избыточной информации | 1981 |

|

SU978373A1 |

| Устройство для приема избыточнойиНфОРМАции | 1979 |

|

SU824263A1 |

| Устройство для приема и передачи избыточных сигналов | 1981 |

|

SU976466A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1193713A1 |

| Адаптивное устройство для обработки избыточной информации | 1982 |

|

SU1062752A1 |

| Устройство для приема и обработки избыточных сигналов | 1983 |

|

SU1152020A1 |

-га-чз

12

Па

| Бородин Л.Ф | |||

| Введение в теорию помехоустойчивого кодирования | |||

| М.: Советское радио, 1969, с | |||

| Приспособление для уменьшения дымовой тяги паровоза | 1920 |

|

SU270A1 |

| Устройство для приема избыточнойиНфОРМАции | 1979 |

|

SU824263A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-07-15—Публикация

1985-07-01—Подача