Фие.1

Изобретение-относится к автомати- Ле и вычислительной технике, в част- 14ости к устройствам программного уп | авления технологическим оборудова- , может быть использованг для программного управления машинами для гртетрадного шитья книг и является т)гсовершенствованием устройства по 4вт. св. № 1300415.

I ЦеЛь изобретения - расширение ункциональных возможностей устройства путем автоматического формиро- Iания сигнала управления на (Ы-К)-м .

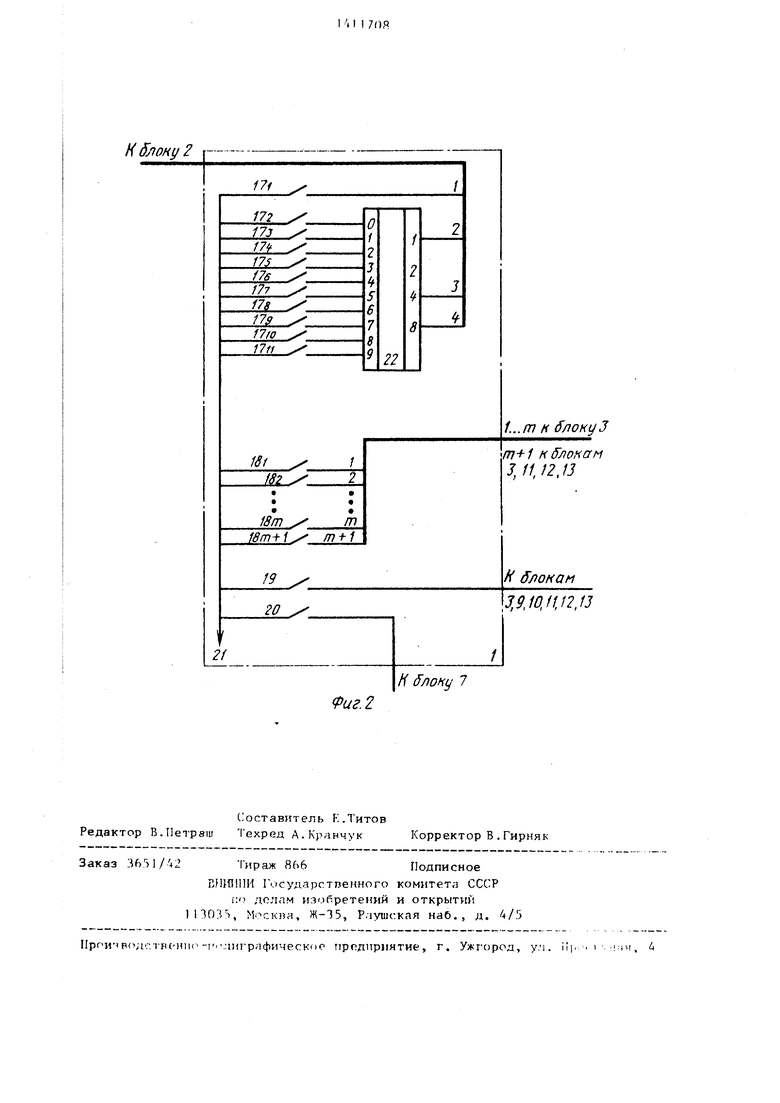

I На фиг.1 представлена функциональная схема устройства дпя циклового грограммного управления; на фиг.2 - схема блока задания программы.

I Устройство содержит блок 1 зада- ь|ия программы, формирователь 2 адре- 4а, первый блок 3 памяти, блок 4 ин- ;икации, блок 5 исполнительных элементов, датчик 6 циклов, первый зле- мент ИЛИ 7, элемент 8 задержки, ком- NyTaTop 9, преобразователи 1.0 кода, второй блок 11 памяти, третья блоки

ll2 памяти, четвертый .блок 13 памяти, элемент И 14, элемент НЕ 15 и второй элемент ИЛИ 16, количество третьих блоков 12 памяти п определяется сле- Р ующим- образом:

п k - 1 ,

г|де k - количество преобразователей : 10 кода.

Блок 1 задания программы содержит г ереключатели 17. устанавливающие но- Цер кинематического цикла, переключа- 11ели 18,...18f, соответствующие ис- Цолнительным элементам, и переключа- ilenb 18fp программирования последне- цикла, переключатель 19 режима работы, переключатель 20 записи информации, шину 21 логической единицы и формирователь 22 кода.

Устройство работает следующим об- plasoM.

Блок 1 задания программы представ- собой наборное поле, при этом г руппы переключателей подключением в шине 2 логической единицы позво- 4яют устанавливать управляющую прог- и режимы работы устройства.

Введены обозначения: N - полное Мсло циклов работы технологического Оборудования; k - целое, меньшее N, ф1сло, постоянное для данного техно- Логического оборудования.

Устройство имеет пка режима: Врод программы и Работа. Режим устанавливается переключателем 19 иа блоке 1,

Соответствующий режиму потгнциал поступает с блока 1 на управляющий вход коммутатора 9, на входы запись - считывание блоков 3 и 11-13 и на вторые входы преобразователей 10.

В режиме Ввод программы переключателями 17 на блоке 1 устана1зливает- ся номер кинематического цикла, для которого вводится программа. Мнформа- 1ЩЯ о номере кинематического цикла

с блока I поступает на установочные входы формироватеЛ Я 2, переводя его в соответствующее состояние. Сигналы с формирователя 2 поступают нл адресные входы блоков 3 и 13 и на первые входы преобразователей 10, При наличии на вторых входах преобразователей 10 потенциала, соответствующего режиму Ввод программы, коду цикла на первых входах преобразователей

10 соответствует следуюшяй код на выходах преобразователей 10:

10 - i - К

i - (К-1)

Юкi - 1

Таким образом, при переводе формирователя 2 в состояние, соответствующее последнему циклу, на адресных входах блоков П-13 присутствует код, соответствующий следующим циклам:

1

12

N - К

N - (К-1)

12, 13

N N

На блоке 1 включаются переключатели 18, соответствующие исполнительным элементам, которые должны срабатывать на данном кинематическом цикле. Информация о состоянии группы переключателей 18 поступает г блока 1 на группу информационных входов блока 3, а потенциал, соответствующий состоянию переключателя 18 trv-n

последнего цикла, поступает также на информационные входы блоков 11-13.

Запись информации в блоки 3 и 11-13 происходит в результате включения переключателя 20 записи информации на блоке 1. При этом сигнал с управляющего выхода блока 1 поступает на вход элемента ИЛИ 7, в результате чего на выходах кoм fyтaтopa 9 ПОЯВЛЯЮТся сигналы, сдвинутые во времени в соответствии с потенциалом, присутствующим на управляющем входе к- ммута- тора 9. Сигнал, появляющийся на первом выходе коммутатора 9, обеспечивает запись информации в блоки 3 и 11-13, а сигнал, появляющийся с задержкой во времени на втором выходе коммутатора 9, производит у величе- ние состояния формирователя 2 на единицу.

Таким образом, при программировании последнего цикла информация о состоянии переключателя ISf, последнего цикла записывается в блоки 3 и 13 по адресу, соответствующему последнему циклу, в блок 11 - по адресу соответствующему (N - К)-му циклу, в блоки I2 - по адресам, соответствующим (N - (K-)...N - 1)-м циклам.

В режиме Работа сигнал с выхода датчика 6, поступая на вход элемента ИЛИ 7, приводит к появлению сигналов на выходах коммутатора 9, сдвинутых во времени в соответствии с потенциалом на управляющем входе коммутатора 9. Сигнал на первом выходе коммутатора 9 появляется с задержкой во времени относительно сигнала на его втором выходе. Сигнал с второго выхода коммутатора 9 производит увеличение состояния формирователя 2 адреса на единицу, а сигнал с первого выхода коммутатора 9 обеспечивает считывание информации из блоков 3 и 11-13. Преобразователи 10 в режиме Работа т.е. при наличии соответствующего потенциала на их вторых входах, функционируют так, что код на их выходах повторяет код на их первых входах. Следовательно, сигнал на выходе блока 1 1 появляется на (N - К)-м цикле. Этот сигнал через элемент И 14 поступает на выход устройства. Поскольку программирование последнего цикла могло быть произведено ранее на N+1...N+K циклах, то в блоке 11 по

адресам, соответствующим N- ( К- I ) . , . циклам, м жет быть записана произвольная информация.

Таким образом, на выходе блока 11 сигнал может появиться на любом из N - (K-1)...N циклов. Однако последовательное считывание сигналов из блоков 12 и 13 через второй элемент ИЛИ 16 и элемент НЕ 15 на второй вход элемента И 14 запрещает прохождение сигнала на этих циклах на выход устройства.

Q 20

J5 Формул,а изобретения

Устройство для циклового программного управления по авт.св . N 1 30041 5 , отличающееся тем, что, с целью расширения функциональных возможностей устройства, в него дополнительно введены преобразователи кода, второй блок памяти, третьи блоки памяти, четвертый блок памяти, элемент И, элемент Е1Е и второй элемент ИЛИ, причем первый выход из группы первых информационных выходов блока задания про грамму: подключен к информационным входам второго блока памяти, третьих блоков и четвертого блока памяти, группа выходов формирователя адреса соединена с группами первых входов преобразователей кбда и группой адресных входов четвертого блока памяти, второй управляющий выход блока задания программы соединен с входами запись - считывание второго блока памяти, третьих блоков памяти, четвертого блока памяти и с вторыми входами преобразователей кода, первый выход коммутатора соединен со стробируюгцими входами второго блока памяти, третьих блоков памяти и четвертого блока памяти, выходы преобразователей кода соединены с адресными входами второго блока памяти и третьих блоков памяти, выход второго блока памяти соединен с первым входом элемента И, выходы третьих блоков памяти соединены с группой первых входов второго элемента ИЛИ, выход четвертого блока памяти соединен с вторым входом второго элемента ИЛИ, выход которого через элемент НЕ соединен с вторым входом элемента И, выход которого является выходом устройства.

Н fnoHy 7

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный регулятор тепловых процессов (его варианты) | 1980 |

|

SU943667A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| Система для программного управления ниткошвейной машиной | 1987 |

|

SU1559329A1 |

| Устройство для программного управления ниткошвейным автоматом | 1988 |

|

SU1533870A1 |

| Устройство для программного регулирования | 1979 |

|

SU930263A2 |

| Устройство для циклового программного управления | 1988 |

|

SU1508193A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Многопрограммный регулятор температуры | 1983 |

|

SU1136123A1 |

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам программного управления технологическим оборудованием, и может быть использовано гипя программного управления машинами для потетрадного пштья книг. Цель изобретения состоит в асширении функциональных возможностей устройства путем автоматического формирования сигнала управления на N - К цикле. Устройство для циклового программного управления содержит блок задания программы 1, формирователь 2 адреса, блоки памяти 3, II, 12, 13, элементы И 14, ИЛИ 7, 16, датчик 6 циклов, блок 4 индикации, блок 5 исполнительных элементов, коммутатор 9, элемент 8 задержки, преобразователи 10 кода. 2 ил. с (Л

Фиг.2

Авторы

Даты

1988-07-23—Публикация

1986-10-20—Подача