(Л

ч|

nU

ko

«w«/

1

ти, генератор 17 импульсов, элемент И 22 и токоограничивающий резистор 23. Контроль цифровых ycTpqttcTB сводится к получению на экране осцилло- . графа одной из во.сьми типов диаграмм и их анализу. Диаграммы на экране осциллографа представляют собой набор цифр, расположенных в углах координатной сетки. Каждая цифра соответствует определенному значению сигналов в контрольных точках исследуемой схемы по отногаению к комбинациям входных или выходных сигналов или внутреннему состоянию схемы. Для получения диаграммы используются два цифро- аналоговых преобразователя (ЦАП), К входам ДАЛ подключаются входные или вькодные сигналы, или сигналы внутреннего состояния исследуемой схемы. Выходы ЦАП подключаются к входам горизонтального и вертикального отклонения луча осциллографа. Для опреде749

.пения значения сигналов в контрольных точках исследуемой схемы используется канал подсчета луча. Выбор конкретных сигналов производится многоразрядным щупом. В устройстве предусмотрен одновременный анализ вось- ми, четырех, трех либо одной точки. В соответствии с этим возможны следу- югцие варианты цифр на экране осциллографа. 00-FF; 0-F; 0-7; 0-1. Для отображения информации с контактов многоразрядного щупа в виде цифр устройство содержит блок постоянной памяти (БПП). В БПП записана информация по управлению подсветкой луча осциллографа и движением луча вблизи узлов координатной сетки„ По характеру отображаемой диаграммы можно судить о правильности работы контролируемой схемы, а по искажению диаграмм производить диагностику неисправностей. 5 ил.5 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор для регистрации результатов контроля | 1988 |

|

SU1608668A1 |

| Логический анализатор | 1982 |

|

SU1111166A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ГИБРИДНЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ | 2012 |

|

RU2493609C1 |

| Устройство для отображения информации на экране осциллографа | 1982 |

|

SU1080195A1 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| Логический анализатор | 1981 |

|

SU1032457A1 |

| Устройство для отображения информации на экране осциллографа | 1985 |

|

SU1282189A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Асинхронное автоматическое устройство для контроля цифровых систем | 1989 |

|

SU1751761A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля цифровых узлов. Целью изобретения является повышение информативности контроля. Логический анализатор содержит два .цифроаналоговых преобразователя 1 и 2, три мультиплексора 3, 4 и 19, два счетчика 7 и 18, два переключателя 9 и 21, два шифратора 10 и 20, блок П отобра:жения, три фильтра 13 - 15 низких частот, блок 16 постоянной памя

Изобретение относится к вычислительной технике и может быть использовано для контроля цифровых устройств.

Цель изобретения - повышение информативности контроля.

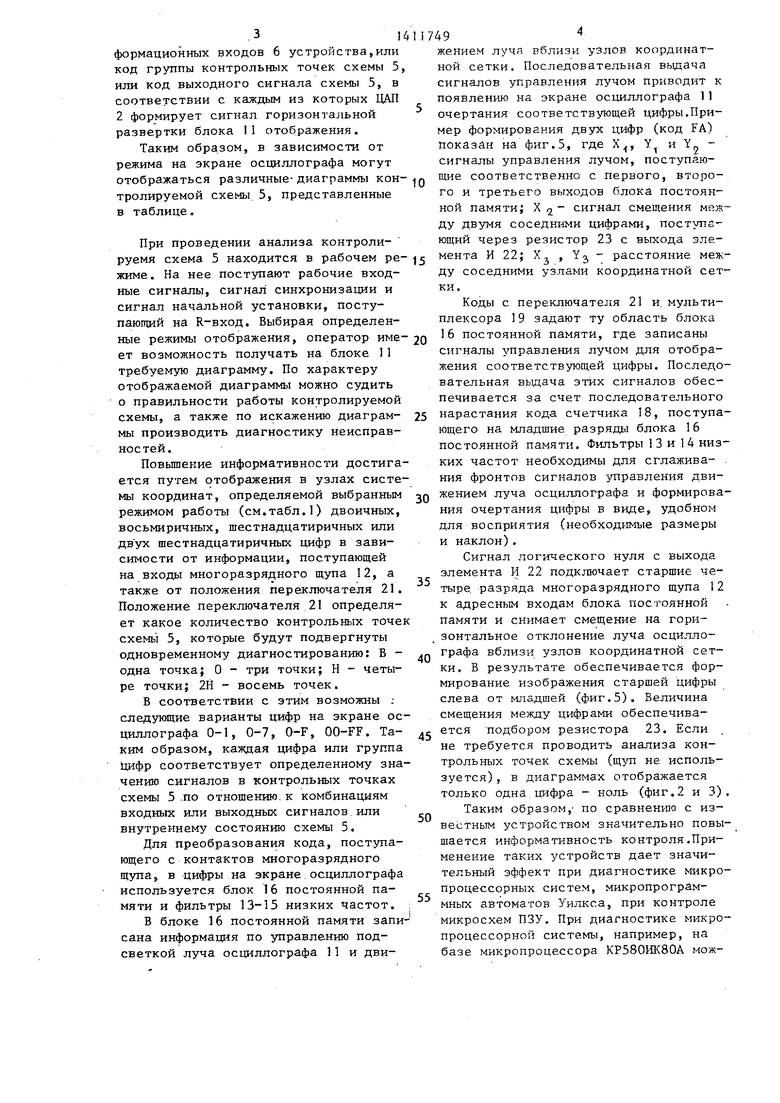

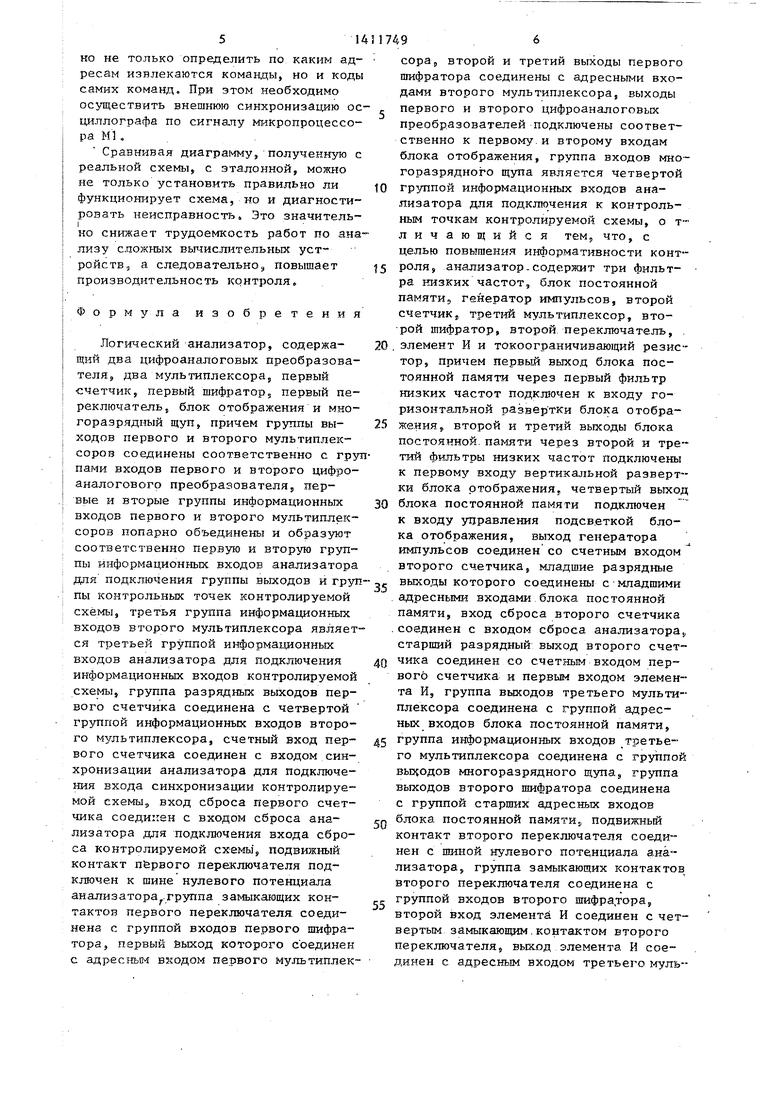

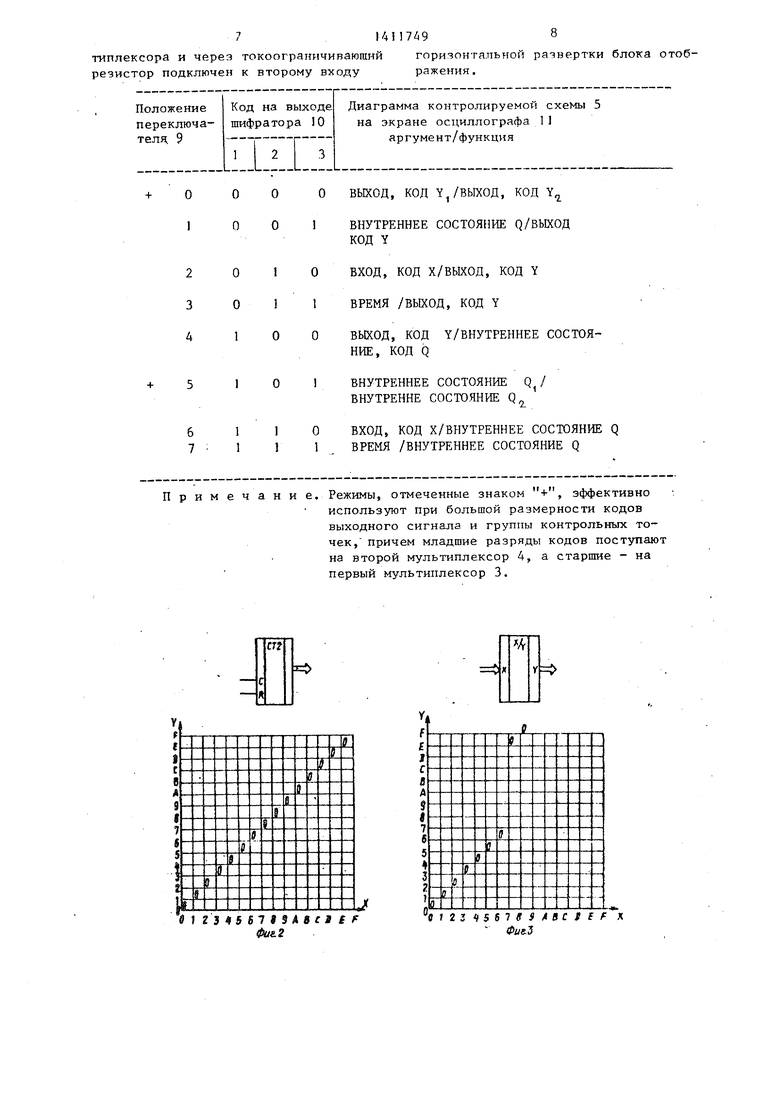

На фиг.1 изображена структурная схема логического анализатора; на фиг.2 - 4 - примеры диаграмм, получаемых с помощью анализатора при контроле некоторых цифровых схем (на фиг, 2 - диаграмма время-выход че i,- тырехразрядного двоичного счетчика; на фиг.З - диаграмма вход-выход комбинационного преобразователя кода 8-4-2-1 в код 2-4-2-1, на фиг.4 - диаграмма вход-выход для автомата Уилкса); на фиг.З - формирование на диаграмме двух шестнадцатиричных цифр (1 байт) вблизи узлов координатной сетки.

Логический анализатор содержит первый 1 и второй 2 цифроаналоговые преобразователи (ЦАП), первый 3 и второй 4 мультиплексоры. Обозначены контролируемая схема .5 и группа 6 информационных выходов анализатора для подключения информационных входов контролируемой схемы. Анализатор содер- жит также первый счетчик 7, вход 8 .сброса, первый переключатель 9, первый шифратор 10, блок 11 отображения8

многоразрядный щуп 12, первый 13, второй 14 и третий 15 фильтры низких частот, блок 16 постоянной памяти, генератор 17 импульсов, второй счетчик 18, третий мультиплексор 19, второй

шифратор 20, второй переключатель 21, элемент И 22 и токоограничивающий резистор 23.

Логический анализатор работает следующим образом.

Режим работы задается переключателем 9,в соответствии с положением которого на выходе шифратора 10 формируется код управления. Мультиплексор 3 пропускает на вход первого ЦАП

(в зависимости от режима) код выходного сигнала или код состояния группы контрольных точек контролируемой схемы 5, в соответствии с кото- рым ЦАП 1 формирует сигнал вертикальной развертки осциллографа Г1, При этом мультиплексор 4 пропускает на вход второго ЦАП 2 код с выхода первого счетчика 7 или код с группы ин

.3

формационных входов 6 устройства,или код группы контрольных точек схемы 5 или код выходного сигнала схемы 5, в соответствии с каждьм из которых ЦАП 2 формирует сигнал горизонтальной развертки блока II отображения.

Таким образом, в зависимости от режима на экране осциллографа могут отображаться различные- диаграммы контролируемой схемы 5, представленные в таблице.

При проведении анализа контроли- руемя схема 5 находится в рабочем режиме. На нее поступают рабочие входные сигналы, сигнал синхронизации и сигнал начальной установки, поступающий на R-вход. Выбирая определенные режимы отображения, оператор имеет возможность получать на блоке )1 требуемую диаграмму. По характеру отображаемой диаграммы можно судить о правильности работы контролируемой схемы, а также по искажению диаграммы производить диагностику неисправностей.

Повышение информативности достигается путем отображения в узлах системы координат, определяемой выбранным режимом работы (см.табл.) двоичных, восьмиричных, шестнадцатиричных или дв ух шестнадцатиричных цифр в зависимости от информации, поступающей на входы многоразрядного щупа 12, а также от положения переключателя 21. Положение переключателя 21 определяет какое количество контрольных точек схемь 5, которые будут подвергнуты одновременному диагностированию: В - одна точка; О - три точки; Н - четыре точки; 2Н - восемь точек.

В соответствии с этим возможны ; следующие варианты цифр на экране осциллографа 0-1, 0-7, 0-F, 00-FF. Таким образом, каждая цифра или группа Цифр соответствует определенному значению сигналов в контрольных точках схемы 5 .по отношению, к комбинациям входных или выходных сигналов или внутреннему состоянию схемы 5.

Для преобразования кода, поступающего с контактов многоразрядного щупа, в цифры на экране осциллографа используется блок 16 постоянной памяти и фильтры 13-15 низких частот.

В блоке 16 постоянной памяти запи сана информация по управлению подсветкой луча осциллографа 11 и дви1749

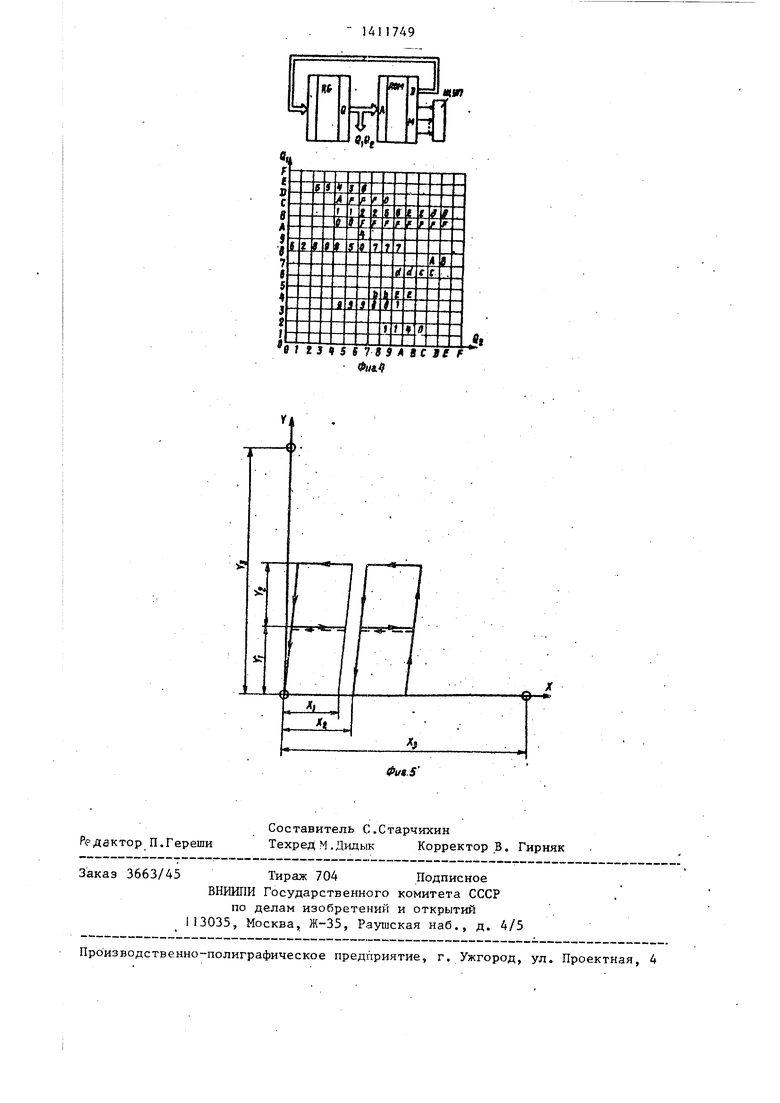

жением луча вблизи узлов координатной сетки. Последовательная выдача сигналов управления лучом приводит к появлению на экране осциллографа 11 очертания соответствующей цифры.Пример формирования двух цифр (код FA) показан на фиг.5, где Х, Y и Y - сигналы управления лучом, поступаю« щие соответственно с первого, второго и третьего выходов блока постоянной памяти; Х сигнал смещения между двумя соседними цифрами, поступающий через резистор 23 с выхода элемента И 22; X,, , Y.J расстояние между соседними узлами координатной сетки.

Коды с переключателя 21 и. мультиплексора 19 задают ту область блока

Q 16 постоянной памяти, где записаны сигналы управления лучом для отображения соответствующей цифры. Последовательная выдача этих сигналов обеспечивается за счет последовательного

5 нарастания кода счетчика 18, поступающего на младшие разряды блока 16 постоянной памяти. Фильтры 13 и 14 низких частот нeoбxoдliмы для сглажива- . НИН фронтов сигналов управления двиQ жением луча осциллографа и формирования очертания цифры в виде, удобном для восприятия (необходимые размеры и наклон).

Сигнал логического нуля с выхода элемента И 22 подключает старшие четыре, разряда многоразрядного щупа {2 к адресным входам блока постоянной памяти и снимает смещение на горизонтальное отклонение луча осцилло5

графа вблизи узлов координатной сетки. В результате обеспечивается формирование изображения старшей цифры слева от младшей (фиг.5). Величина смещения между цифрами обеспечива- ется подбором резистора 23. Если не требуется проводить анализа контрольных точек схемы (щуп не используется) , в диаграммах отображается только одна.цифра - ноль (фиг.2 и 3).

Таким образом,- по сравнению с известным устройством значительно повышается информативность контроля.Применение таких устройств дает значительный эффект при диагностике микропроцессорных систем, микропрограммных автоматов Уилкса, при контроле микросхем ПЗУ. При диагностике микропроцессорной системы, например, на базе микропроцессора КР580Ж80А мож

ко не только определить по каким адресам извлекаются команды, но и коды самих команд. При этом необходимо осуществить внешнюю синхронизацию осциллографа по сигнапу микропроцессора Ml .

Сравнивая диагра1чму, полученгтую с реальной схемы, с эталонной, можно не только установить правильно ли функционирует схема, но и диагностировать неисправность. Это значительно снижает трудоемкость работ по анализу сложных вычислительных устройств, а следователтьноз повышает производительность контроля.

Формула изобретения

Логический анализатор, содержащий два цифроаналоговых преобразователя, два мультиплексора, первый счетчик, первый шифратор, первый переключатель, блок отображения и многоразрядный щуп, причем группы выходов первого и второго мультиплексоров соединены соответственно с группами входов первого и второго цифро- аналогового преобразователя, первые и вторые группы информационных входов первого и второго мультиплексоров попарно объединены и образуют соответственно первую и вторую гр5Ш- пы информационных входов анализатора для подключения группы выходов и группы контрольных точек контролируемой схемы, третья группа информационных входов второго мультиплексора является третьей группой информационных входов анализатора для подключения информационных входов контролируемой схемь, группа разрядных выходов первого счетчика соединена с четвертой группой информационных входов второго мультиплексора, счетный вход первого счетчика соединен с входом синхронизации анализатора для подключения входа синхронизации контролируемой схемы, вход сброса первого счетчика соединен с входом сброса анализатора для подключения входа сброса контролируемой схемы , подвижный контакт пбрвого переключателя подключен к шине нулевого потенциала анализатора.группа замыкающих контактов первого перек.шочателя соединена с группой входов первого шифратора, первый йыход которого соединен с адресньпу вкодом первого мультиплек

to

15

20

25

П7496

сора, второй и третий выходы первого шифратора соединены с адресными входами второго мультиплексора, выходы первого и второго цифроаналоговых преобразователей подключены соответственно к первому.и второму входам блока отображения, группа входов многоразрядного щупа является четвертой группой информационных входов анализатора для подключения к контрольным точкам контролируемой схемы, о т личающийся тем5 что, с целью повышения информативности контроля, анализатор-соде.ржит три фильт- ра низких частот, блок постоянной памятиэ гейератор импульсов, второй счетчик, третий мультиплексор, второй шифратор, второй переключатель, . элемент И и токоограничивающий резистор, причем первый выход блока постоянной памяти через первый фильтр низких частот подкшочен к входу горизонтальной развертки блока отображения, второй и трети.й вьгходы блока постоянной, памяти через второй и третий фильтры низких частот подключены к первому входу вертикальной развертки блока отображения, четвертый выход блока постоянной памяти подключен к входу управления подсветкой блока отображения, выход генератора импульсов соединен со счетным входом второго счетчика, младшие разрядные выходы которого соединены смладшими адресными входами блока постоянной памяти, вход сброса второго счетчика соединен с входом сброса анализатора,, старший разрядный выход второго счетчика соединен со счетным входом первого счетчика и первым входом элемента И, группа выходов третьего мультиплексора соединена с группой адресных входов блока постоянной памяти, группа информационных входов третье-го мультиплексора соединена с группой вьщодов многоразрядного щупа, группа выходов второго шифратора соединена с группой старших адресных входов блока постоянной памятиs подвижный контакт второго переключателя соединен с шиной нулевого потенциала анализатора, группа замыкающих контактов второго переключателя соединена с группой входов второго шифра.тора, второй вход элемента И соединен с чет- вертьм замыкающим.контактом второго переключателя, выход элемента. И соединен с адресным входом третьего муль30

35

40

45

50

55

7141

типлексора и через токоограничиваютий горизонтальной развертки блока отоб- резистор подключен к второму входу ражеиия.

О ВЫХОД, код Y,/выход, код Y

ВНУТРЕННЕЕ СОСТОЯНИЕ Q/ВЫХОД КОД Y

ВХОД, КОД X/ВЫХОД, КОД Y ВРЕМЯ /ВЫХОД, КОД Y

ВЫХОД, КОД Y/ВНУТРЕННЕЕ СОСТОЯНИЕ, КОД Q

ВНУТРЕННЕЕ СОСТОЯНИЕ ВНУТРЕННЕ СОСТОЯНИЕ Q

0ВХОД, КОД X/ВНУТРЕННЕЕ СОСТОЯНИЕ Q

1ВРЕМЯ /ВНУТРЕННЕЕ СОСТОЯНИЕ Q

Примечание, Режимы, отмеченные знакам +, эффективно

используют при большой размерности кодов выходного сигнала и группы контрольных точек, причем младшие разряды кодов поступают на второй мультиплексор А, а старшие - на первый мультиплексор 3.

т

123 561eSABcatf

Фие.2

Ч

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Микропроцессорные системы | |||

| - М.: Энергоиздат, 1981, с.438-441 | |||

| Логический анализатор | 1982 |

|

SU1111166A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-23—Публикация

1986-07-14—Подача