Изобретение относится.к вычислительной технике и может быть использовано для контроля цифровых устройств.

Целью изобретения является повьше ние надежности за счет упрощения анализатора.

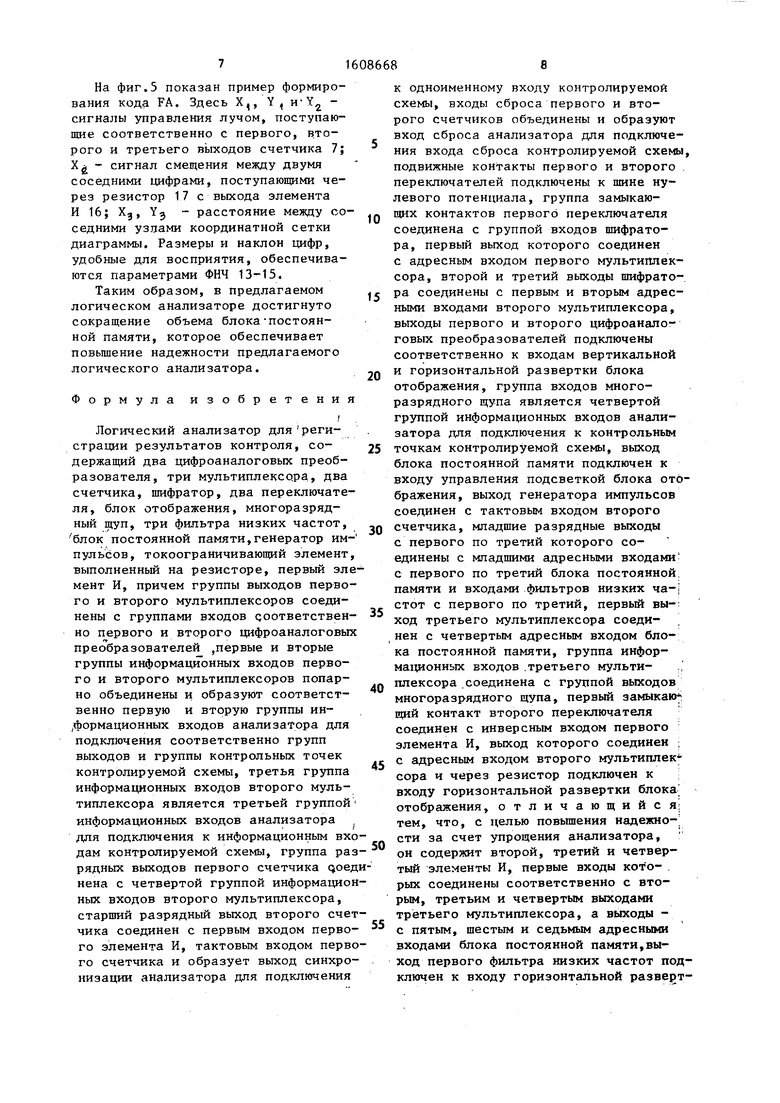

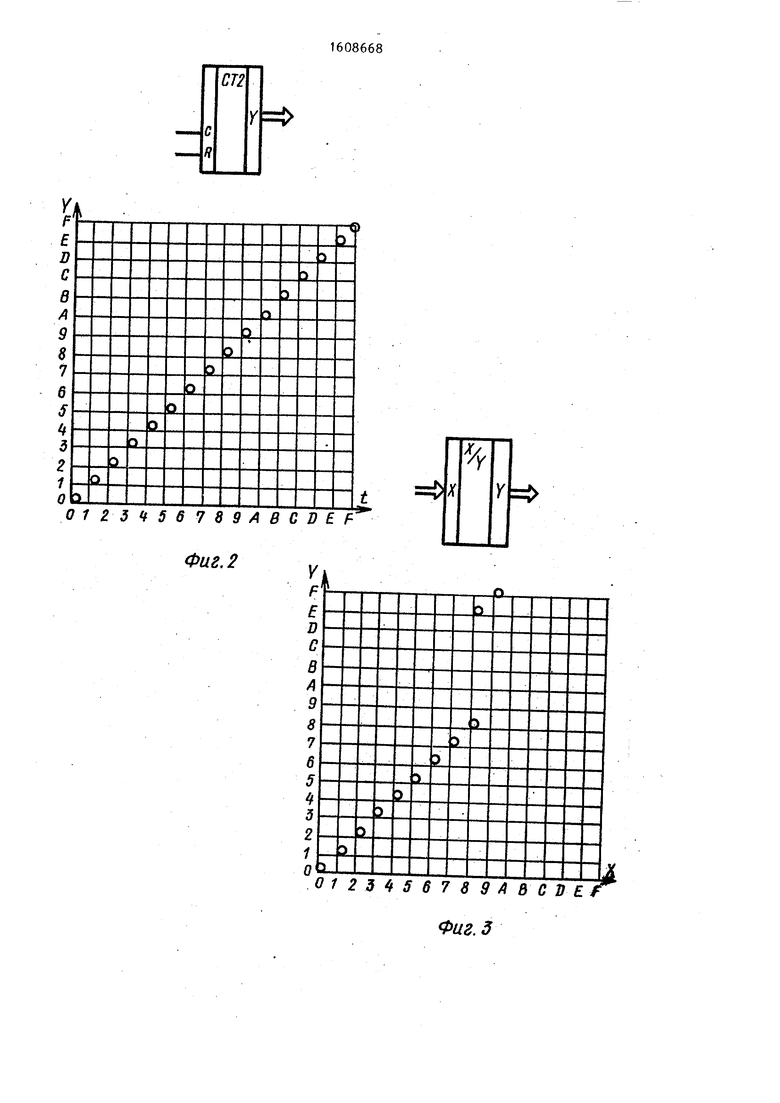

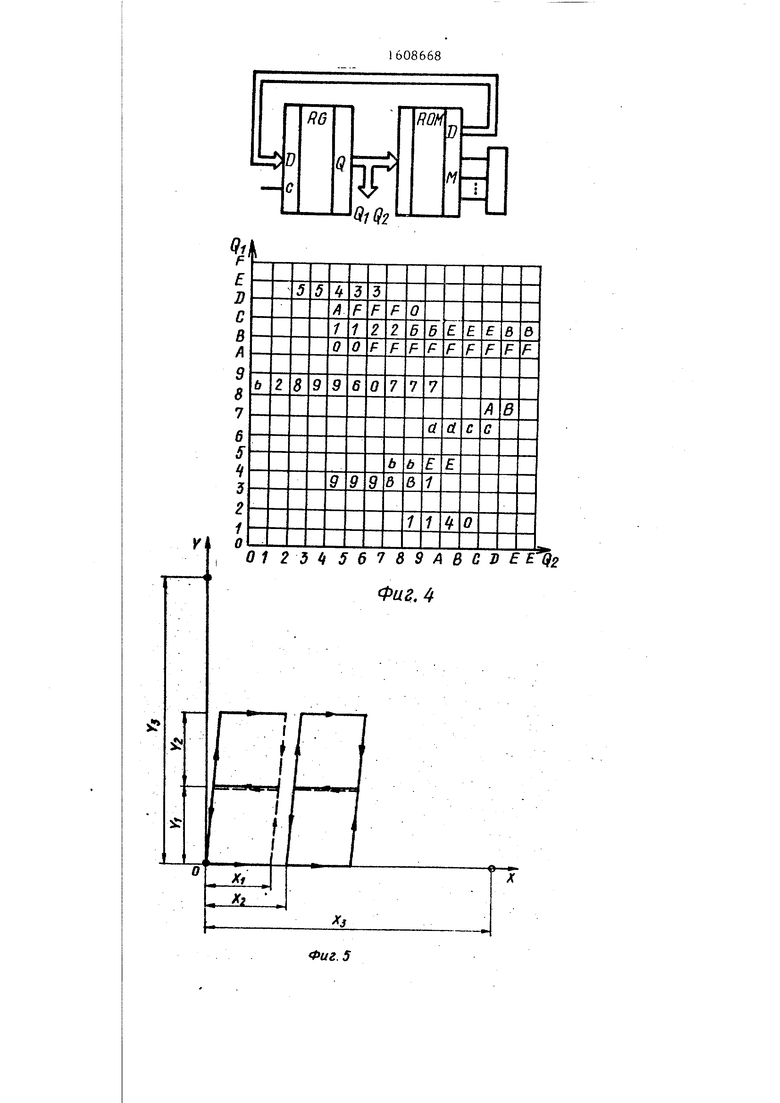

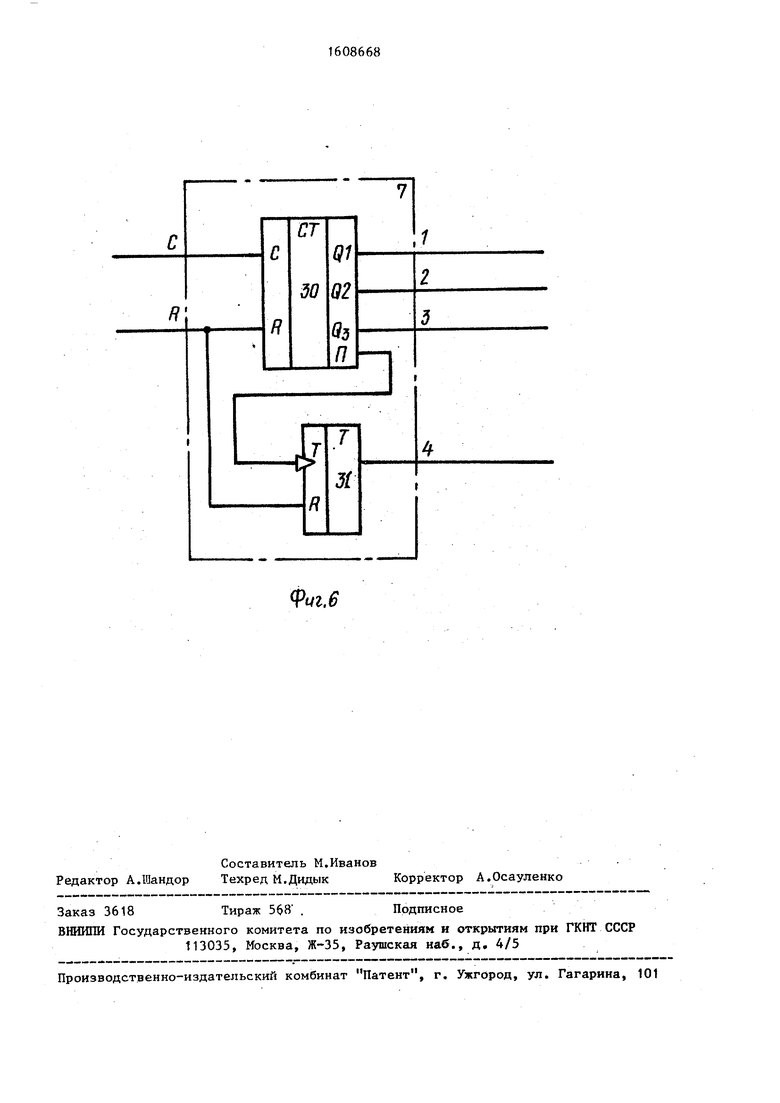

На фиг.1 представлена структурная схема анализатора; на фиг.2 - диаграмма время-выход четырехразрядного двоичного счетчика; на .З - диаграмма вход-выход комбинационного преобразователя кода 8-4-2-1 в код 2-4-2-1; на фиг.4 - диаграмма вы ход-выход для автомата Уилкса; на фиг.5 - формирование на диаграмме двух шестнадцатиричных цифр (1 байт) вблизи узлов координатной сетки; на фиг.6 - схема второго счетчика.

Анализатор содержит первый 1 и второй 2 цифроаналоговые преобразователи, первый 3, второй 4 и третий 5 мультиплексоры, первый 6 и второй 7 счетчики, шифратор 8, первый 9 и второй 10 переключатели, блок 11 постоянной памяти,генератор 12 импульсов, первый 13, второй 14 и третий 15 фильтры низких частот, первый элемент И 16,токоогран.ичиваю- щий элемент, вьтолненньй на резисторе 17, блок 18 отображения, многоразрядный щуп 19, а также контролируемую схему 20.

На фиг.1, показаны первая 21, вторая 22 и третья 23 группы информационных входов, выход 24 синхронизации, вход 25 сброса, элементы И 26 - 28, четвертая группа 29 информационных входов.

Второй счетчик (фиг.6) содержит трехразрядный счетчик 30 в коде Грея и счетный триггер 31,

Все блоки, входящие в логический анализатор, стандартные и могут быть реализованы на микросхемах серии К 155. В качестве блока 18 отображения может быть использован осциллограф, например, С1-83.

Анализатор работает следующим образом.

Он обеспечивает возможность формирования различных диаграмм, характеризующих функционирование контролируемой схемы 20. Тип отображаемой диаграммы (режим работы логич еско- го анализатора) выбирается переключателем 9, в соответствии с положением которого на выходе шифратора 8 форми0

5

0

5

0

5

0

5

0

5

руется код управления режимом. В соответствии с выбранным режимом мультиплексор 3 пропускает на вход циф- роаналогового преобразователя (ЦАП) 1.КОД выходного сигнала или код состояния группы контрольных точек контролируемой схемы 20. При этом мультиплексор 4 пропускает на вход ЦАП 2 код с выхода счетч1Лса 6 или код с группы информационных входов 23 схемы 20, или код группы контрольных точек схемы 20, или код выходного сигнала схемы 20. Выходные сигналы ЦАП 1 и 2 поступают соответственно на входы вертикальной и горизонтальной развертки блока 18 отображения. Это приводит к формированию диаг.раммы на экране блока отображения.

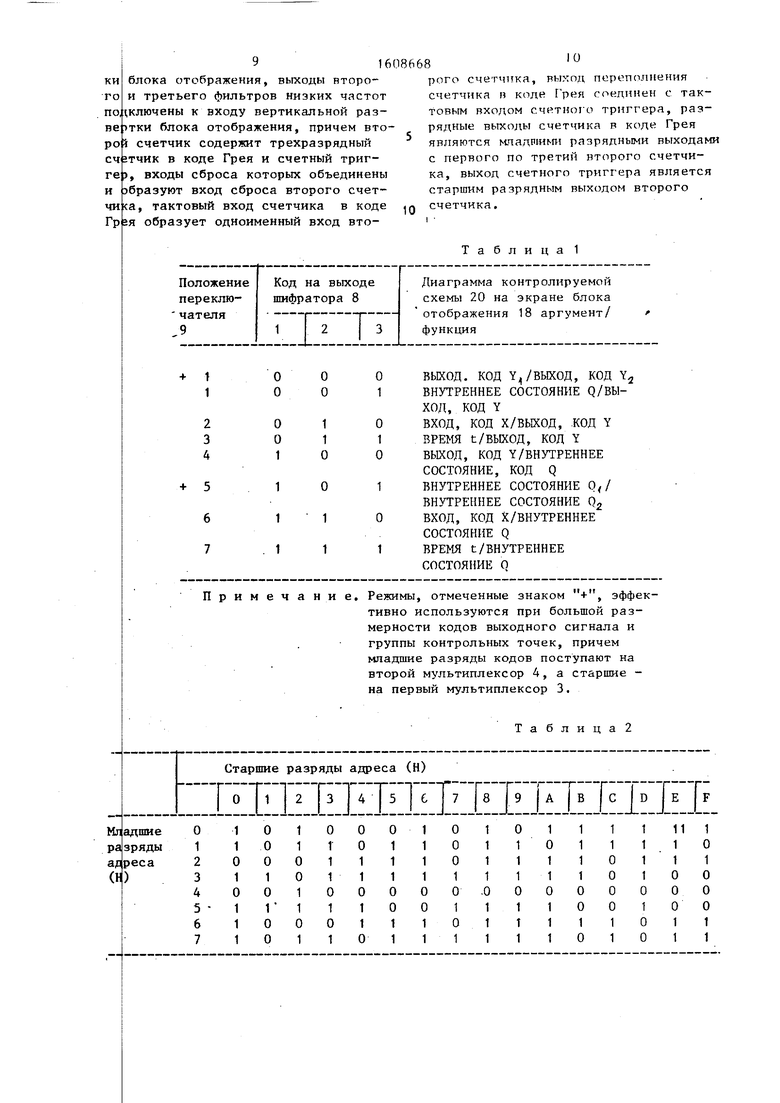

Различные виды диаграмм, получаемые в зависимости от режима работы логического анализатора, представ- лены в табл.1.

При проведении анализа контролируемая схема 20 находится в рабочем режиме На нее поступают рабочие входные сигналы, сигнал синхронизации и сигнал начальной установки. Выбирая определенные режимы отображения, оператор имеет возможность получить с помощью блока 18 требуемую диаграмму. Эти диаграммы дают возможность контролировать последовательность и достоверность генерации внутренних состояний схемы 20, а также ее входных и выходных сигналов. По характеру отображаемой диаграммы можно судить о правильности работы контролируемой схемы, а по искажению диаграммы производить диагностику неисправностей.

Однако для полной характеристики контролируемой схемы необходимо знать значения различных дополнительных сигналов в каждой из точек отображаемой диаграммы. В предлагаемом логи- ; ческом анализаторе обеспечена возможность контроля как одноразрядного, так и многоразрядного дополни- тельного сигнала. Состояние этих сиг-: налов схемы 20 подается в логический анализатор с помощью многоразрядного щупа 19. Положение переключателя 10 определяет режим отображения дополнительного сигнала, т.е. его разрядность. При этом возможно отображение состояния дополнительного сигнала в двоичной форме (одноразрядный дополнительный сигнал), восьмиричной (трехразрядный дополнительный сигнал , шестнадцатиричной (четырехразрядный дополнительный сигнал) и двойной шестнадцатиричной формах (восьмиразрядный дополнительный сигнал). соответствии с этим возможны следующие варианты цифр на экране бло1

0-F, 00-FF.

:а отображения: 0-1, 0-7,

Для

преобразования кода с контактон щупа 19 в цифры на диаграммах исполь;|уются блок 11 постоянной памяти, фильтры 13-15 низких частот СФНЧ) ,

этом TI ционирл Грея,

генератор 12 и счетчик 7. При и младших его разряда функ- ют в соответствии с кодом г выход переполнения третьего

младшего разряда соединен со счетным Входом четвертого разряда, образуе- мого с етным триггером 31. С приходом каздого 16-го импульса генератора 1 Н

чика 7

рому КС

чик 6 I

СОСТОЯ

изменяк1тся сигналы на- входах ЦАП 1

: выходе старшего разряда счет формируется сигнал,по кото- нтролируемая схема 20 и счет- :ереходят в следующее рабочее 1ие. Если в результате этого

и 2, тс ражени ющий у;

электронный луч блока отобпереместится .в соответствуел координатной сетки на диаграмме .

образом, выходные сигналы

с ЦАП 1

и 2 выбирают узлы координатг.

ной сетки, в которых отображается в выбранной форме информация, характеризующа

я состояние дополнительного

сигнала.

Фop иpoвaниe цифры в узле координатной сетки происходит следующим o6pa3ON. Сигналы с мпадших трех разрядов счетчика 7, проходя через фильтры 1315,суммируются с выходными

сигналами соответствующих ЦАП и поступают

ка входы горизонтального и

вертикального отклонения луча блока 18 отображения. Это приводит к тому, что в узле координатной сетки диаграммы электронный луч движется по замкнутому контуру, совпадающему с начертанием цифры 8. Переход счетчика 7

из одного состояния в другое

приводит к перемещению луча по соответствующему участку (сегменту) этого контура. Если этот переход осуществляется при единичном сигнале подсветки луча, то, вследствие сгла86686

живания фронтов сигналов с младших разрядов счетчика 7 фильтрами 13-15, на экране блока 18 отображения возникнет заметный след длиной в один сегмент. Управление подсветкой луча блока 18 отображения в каждом из состояний счетчика 7 дает возможность отображения любой цифры от О до F.

д Это реализуется с помощью одно- разрядного блока 11, в котором записана информация по управлению под- счеткой луча блока 18 отображения. В табл.2 представлено кодирование

IJ блока 11. Каждая клетка этой таблицы соответствует одному из 128 возможных адресов. Строки таблицы соответствуют В возможным состояниям (кодирование в восьмиричной сис20 теме) 3-разрядного кода с младших разрядов счетчика 7, поступающего на младшие разряды адреса. Столбцы таблицы соответствуют 16 возможным состояниям (кодирование в шестнад25 цатиричной системе) 4-разрядного кода,поступающего с мультиплексора 5 на старите разряды адреса.

В целях уменьшения количества 2Q ячеек блока 11 старшие входные линии мультиплексора 5 поступают на адресные входы блока памяти через элементы И 26-28. Управление ими осу- ществляется кодом с переключателя 10.В результате на адресных входах блока 11 памяти, соответствующих тем выходным линиям мультиплексора 5, которые не являются информационными (3 старших линии - контроль одной : - точки, 1 старшая линия - контроль трех точек), устанавливается сигнал логического нуля.

Если одновременно контролируется 8-разрядный дополнительный сигнал д5 схемы 20 (положение 2Н переключателя 10), то в тот момент, когда старший 4-й разряд счетчика 7 установится в единицу, сигнал логического нуля с выхода элемента И 16 подключит стар- 5Q шие четыре разряда многоразрядного щупа 19 через мультиплексор 5 и элементы И 26-28 к адресным входам блока 11. Одновременно, этим же сигналом снимется смещение на горизонтальное j отклонение луча блока 18 отображения вблизи узла координатной сетки диаграммы. В результате обеспечива- . ется формирование старшей цифры 8- разрядного кода слева от младшей. Г

35

На фиг.5 показан пример формирования кода FA, Здесь X,, Y, и Т - сигналы управления лучом, поступающие соответственно с первого, второго и третьего выходов счетчика 7; Х - сигнал смещения между двумя соседними цифрами, поступающими через резистор 17 с выхода элемента И 16; Х, Y - расстояние между оо седними узлами координатной сетки диаграммы. Размеры и наклон цифр, удобные для восприятия, обеспечиваются параметрами ФНЧ 13-15.

Таким образом, в предлагаемом логическом анализаторе достигнуто сокращение объема блока-постоянной памяти, которое обеспечивает повьшение надежности предлагаемого логического анализатора.

Формула изобретения

Логический анализатор для регистрации результатов контроля, со- держащий два цифроаналоговых преобразователя, три мультиплексора, два счетчика, шифратор, два переключателя, блок отображения, многоразрядный П1уп, три фильтра низких частот, блок постоянной памяти,генератор им- пульсов, токоограничивающий элемент, выполненньй на резисторе, первый элемент И, причем группы выходов первого и второго мультиплексоров соединены с группами входов соответствен- но первого и второго цифроаналоговых преобразователей ,первые и вторые группы информационных входов первого и второго мультиплексоров попарно объединены и образуют соответст- венно первую и вторую группы ин- (формационных входов анализатора для подключения соответственно групп выходов и группы контрольных точек контролируемой схемы, третья группа информационных входов второго мультиплексора является третьей группой информационных входов анализатора для подключения к информационным входам контролируемой схемы, группа раз рядных выходов первого счетчика С1оед нена с четвертой группой информационных входов второго мультиплексора, старший разрядный выход второго счетчика соединен с первым входом перво- го элемента И, тактовым входом первого счетчика и образует вьпсод синхронизации анализатора для подклн5чения

5

0

5 - 5 -

5

к одноименному входу контролируемой схемы, входы сброса первого и второго счетчиков объединены и образуют вход сброса анализатора для подключения входа сброса контролируемой схемы, подвижные контакты первого и второго . переключателей подключены к шине нулевого потенциала, группа замыкающих контактов первого переключателя соединена с группой входов шифратора, первый вьпсод которого соединен с адресным входом первого мультиплексора, второй и третий выходы шифратора соединены с первым и вторым адресными входами второго мультиплексора, выходы первого и второго цифроаналоговых преобразователей подключены соответственно к входам вертикальной и горизонтальной развертки блока отображения, группа входов многоразрядного щупа является четвертой группой информационньк входов анализатора для подключения к контрольным точкам контролируемой схемы, выход блока постоянной памяти подключен к входу управления подсветкой блока отображения, выход генератора импульсов соединен с тактовым входом второго счетчика, младшие разрядные выходы с первого по третий которого соединены с мпадшими адресными входами с первого по третий блока постоянной, памяти и входами фильтров низких ча-| стот с первого по третий, первый вы-: ход третьего мультиплексора соединен с четвертым адресным входом блока постоянной памяти, группа инфор- MaiuioHHbix входов .третьего мульти- ., плексора соединена с группой выходов многоразрядного щупа, первый замыкаю щий контакт второго переключателя соединен с инверсным входом первого элемента И, выход которого соединен с адресным входом второго мультиплек - сора и через резистор подключен к входу горизонтальной развертки блока отображения, отличающийся тем, что, с целью повьш1ения надежности за счет упрощения анализатора, он содержит второй, третий и четвертый элементы И, первые входы кот о- рых соединены соответственно с вторым, третьим и четвертым выходаьш третьего мультиплексора, а выходы - с пятым, шестым и седьмым адресными входами блока постоянной памяти,выход первого фильтра низких частот подключен к входу горизонтальной развертблока отображения, выходы нторо- и третьего фильтров низких частот 1ключены к входу вертикальной раз- веЬтки блока отображения, причем вто- poi счетчик содержит трехразрядный

ки го по,

СЧ(

ге и чи Гр

JT4HK в коде Грея и счетный триг- ), входы сброса которых объединены образуют вход сброса второго счет- а, тактовый вход счетчика в коде гя образует одноименный вход вто

рого счетчика, выход переполнения счетчика п коде Грея соединен с тактовым входом счетног о триггера, разрядные выходы счетчика в коде Грея являются кпадшими разрядными выходами с первого по третий второго счетчика, выход счетного Tpvirrepa является старшим разрядным выходом второго счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1986 |

|

SU1411749A1 |

| Логический анализатор | 1982 |

|

SU1111166A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1254489A1 |

| Устройство для формирования видеосигналов | 1985 |

|

SU1317473A1 |

| Цифровой следящий электропривод | 1985 |

|

SU1308982A1 |

| Логический анализатор | 1981 |

|

SU1032457A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

Изобретение относится к вычислительной технике и может использоваться для контроля цифровых устройств. Цель изобретения - повышение надежности анализатора за счет упрощения его схемы. Логический анализатор содержит два цифроаналоговых преобразователя 1, 2 три мультиплексора 3, 4, 5, два счетчика 6, 7, шифратор 8, два переключателя 9, 10, блок постоянной памяти 11, генератор импульсов 12, три фильтра низких частот 13, 14, 15, элемент И 16, резистор 17, блок отображения 18 и многоразрядный щуп 19. Цель изобретения достигается благодаря вводу элементов И 26-28 и выполнению счетчика 7 в виде трехразрядного счетчика в коде Грея, соединенного выходом переполнения с тактовым входом счетного триггера. 6 ил., 2 табл.

t 00 О ВЫХОД. КОД Y /ВЫХОД, КОД Y

1001 ВНУТРЕННЕЕ СОСТОЯНИЕ Q/ВЫХОД, КОД Y

2010 ВХОД, КОД Х/ВЫХОД, -КОД Y

3011 ВРЕМЯ t/ВЫХОД, КОД Y

4100 ВЫХОД, КОД Y/ВНУТРЕННЕЕ

СОСТОЯНИЕ, КОД Q

51 О 1 ВНУТРЕННЕЕ СОСТОЯНИЕ

ВНУТРЕННЕЕ СОСТОЯНИЕ Q

61 1 О ВХОД, КОД Х/ВНУТРЕННЕЕ

СОСТОЯНИЕ Q

СОСТОЯНИЕ Q

Примечание.

Таблица 1

Режимы, отмеченные знаком +, эффективно используются при большой размерности кодов выходного сигнала и группы контрольных точек, причем младшие разряды кодов поступают на второй мультиплексор 4, а старшие - на первый мультиплексор 3.

Таблица2

Фиг. 2

56789 А В С D Е /

Фиг. д

Фиг. 5

(риг.б

| Приспособление для соединения пучка кисти с трубкою или втулкою, служащей для прикрепления ручки | 1915 |

|

SU66A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-11-23—Публикация

1988-04-11—Подача