с группой управляющих входов первого счетчика выход переполнения которого соединен с девятым входом блока управления, четвертая группа выходов которого соединена с группой управляющих входов второго см-етчика , выход которого соединен с десятым входом блока управления | выход блока синхронизации соединен с с янхровходом второго счетчика , первая группа выходов блока переключателей соединена с второй группой информационных входов первого и второго мультиплексоров, с группой информационных входов первого регистра, с группой информационных.входов второго счетчика с группой информационных входов блока регулируемой задержки, второй управляющий вход которого соединен с третьим выходом блока анализа, группа выходов разрядов первого счетчика соединена с третьей группой информационных входов первого мультиплексора, группа управляющих входов которого соединена с группой управляющих входов второго мультиплексора, с второй группой выходов блока переключателей.

2.Анализатор по п,1, о т ли чающийся гем, что блок анализа содержит регистр, группу элементов И,

два элемента ИЛИ, переключатель,причем группа информационных входов блока соединена соответственно с группой единичных входов регистра, соответственно с группой входов первого элемента ИЛИ соответственно с группой информационных входов переключателя, соответственно с первыми входами элементов И группы, вторые входы которых соединены соответственно с выходами регистра, нулевой вход которого соединен с входом сброса блока , первый выход которого соединен с выходом второго элемента ИЛИ входы которого соединены соответственно с выходами элементов И группы, выход первого элемента ИЛИ соединен с управляющим входом переключателя и является вторым выходом блока , третий выход которого соединен с выходом переключателя,

3,Анализатор по п.1, о т л и ч а™ щ и и с я тем, что блок управления

одержит девять переключателей, три лемента ИЛИ, элемент И, триггер ричем первый вход блока соединен с ходом первого переключателя, первый ыход которого является третьим выходом блока, второй выход которого соединен с вторым выходом первого переключателя третий выход которого является первым выходом четвертой группы выходов блока , второй выход четвертой группы выходов которого соединен с прямым выходом первого триггера , с первым входом первого элемента И,второй вход которого соединен с первым входом второго элемента И, с выходом второго перек.пючателя, первый вход которого является синхровходом блока, второй вход которого соединён с первым входом третьего элемента И, второй вход которого соединен с выходом третьего переключателя, вход которого является шестым входомблока, седьмой вход которого соединен с вторым входом второго переключателя, пятый вход блока соедине н с единичным входом первого триггера, с первым входом четвертого переключателя, второй вход которого соединен с выходом второго триггера, единичный вход которог является восьмым входом блока, третий вход которого соединен с нулевым входом первого триггер-а с нулевым входом второго триггеру, с нулевым входом третьего триггера, выход которого .соединен с третьим входом третьего элемента И и является первым выходом блока , четвертый вход третьего элемента И соединен с выходом первого элемента ИЛИ, первый вход которого соединен с четвертым выходом первого переключателя, второй вход первого элемента ИЛИ соединен с выходом пятого переключателя, с входом шестого переключателя и является первым выходом третьей группы выходов блока, второй и третий выходы третьей группы выходов которого соединены соответственно с первым и вт.орым выходами шестого переключателя выходы первого и второго элементов И соединены соответственно с первым и вторым входами пятого переключателя, инверсный выход первого триггера соединен с вторым входом второго элемента И, выход третьего элемента И соединен с первым входом второго элемента ИЛИ с входом седьмого переключателя и является первым выходом первой группы выходов блока, второй выход второй группы выходов которого соединен с выходом седьмого переключателя, первый и второй выходы второй группы выходов блока соединены соответственно с вы ходами восьмого и девятого переключателей, входы которых соединены с выходом второго элемента ИЛИ, второй вход которого является четвертым входом блока, девятый вход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом десятого переключателя, первый вход которого является десятым входом блока, второй вход десятого переключателя соединен, с выходом четвертого переключателя выход третьего элемента ИЛИ соединен с единичным входом третьего триггера.

4. Анализатор по п. 1, о т л и ч а-, ю щ и и тем , что блок регулируемой задерм ки содержит триггер, элемент И, сметчик, причем первый управляющий вход блока соединен с нулевым входом триггера, синхровход которого соединен с вторым управляющим входом блока, выход триггера соединен с первым входом элемента И, второй §ход которого соединен с синхровходом блока , выход которого соединен с выходом переноса счетчика, счетный вход которого соединен с выходом элемента И, группа информационных входов счетчика является группой информационных входов блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1986 |

|

SU1432527A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Логический анализатор | 1987 |

|

SU1476474A1 |

| Устройство для программного управления | 1989 |

|

SU1667005A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для контроля знаний обучаемых | 1989 |

|

SU1679523A1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1702391A1 |

| Устройство для отображения графической информации | 1989 |

|

SU1767520A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1386999A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

1

Изобретение относится к контролю средств цифровой техники .и может быть использовано для контроля И диагностики больших интегральных схем (БИС) и микропроцессорных систем.

Известна система визуального контроля за работой вычислительной машины по гистограмме цифровых данных, содержащая буферный регистр, блок памяти, блок вычисления адресов памяти, блок вычисления компонентов гистограммы , счетчик номера выборки , устройство управления индикацией и блок индикации. Входы регистра являются входами системы, выходы регистра соединены с входами блока вычисления адресов блока памяти, выходы которого подключены к адресным входам блока памяти выходы которого соединены с входами блока вычисления компонентов гистограммы, а также с первыми входами устройства управления индикацией, вторые входы которого подключены к выходам счетчика номера выборки, а выход -к входам блока индикацииС },

Недостаток данной системы - низкая Достоверность контроля сложных цифровых автоматов с большим числом внутренних состояний или/и большим числом выходоЕ,. При построении гистограммы состояний подобных автоматов каждой ячейке блока памяти известной системы (каждому компоненту гистограммы) соответствует не одно состояние, а группа состояний. Поэтому не обнаруживаются

такие неисправности проверяемого автомата, которые приводят к замене некоторых или всех состояний, принадлежа щих одной группе, на одно состояние

этой группы.

Для испытаний с максимальной разрешающей способностью (один бит) необходимо уменьшить диапазон анализи- руемых состояний. Длинные последовагельности приходится просматривать по частям, при этом время испытаний увеличивается- При небольшом числе состояний, закодированных многоразрядными числами , отличающимися в произвольном количестве разрядов различного веса, гистограмма всегда получается с малой разрешающей способностью , что снижает достоверность контроля. Кроме того, для локализации неисправностей слджных автоматов гистограммы состояний обычно нздостаточно. Необходима дополнительная информация, например, в виде таблиц состояний или логических временных

диаграмм. Известная система не позволяет получать такую информацию.

Наиболее близким к предлагаемому по технической сущности является анализатор логического состояния, содержащий блоки аналоговых входных

компараторов, буферный регистр, циф- ровой компаратор, блок регулируемой цифровой задержки блок памяти , блок управления памятью, блок управления

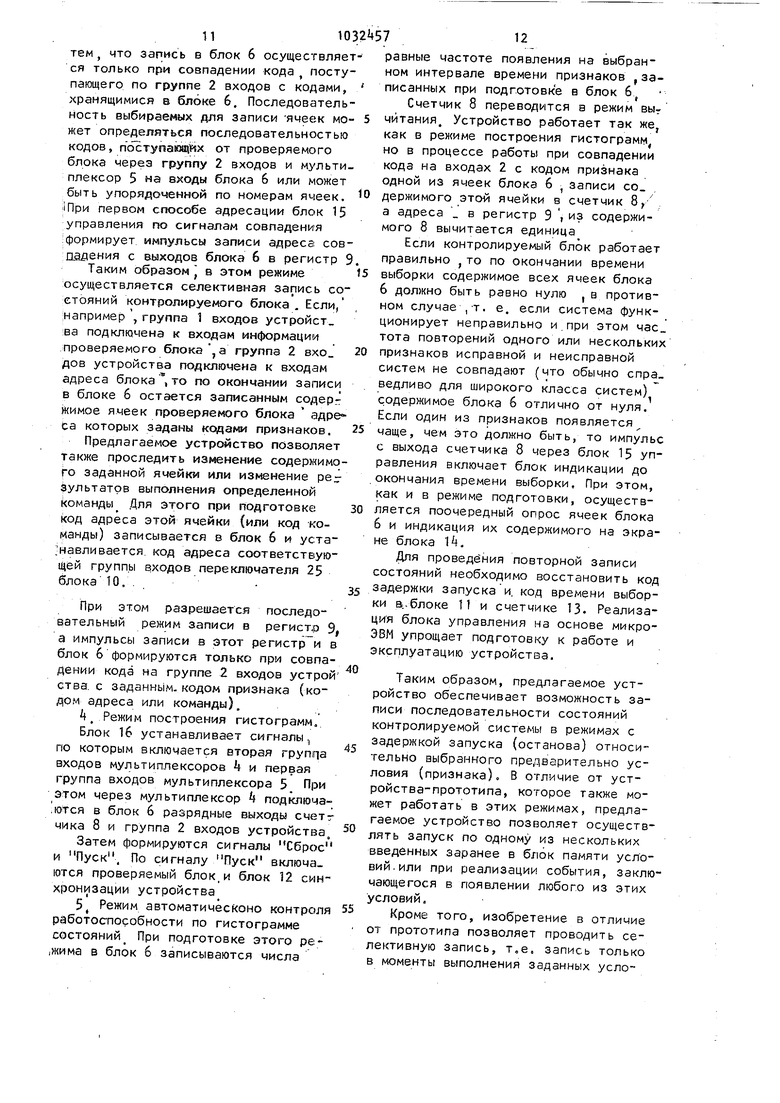

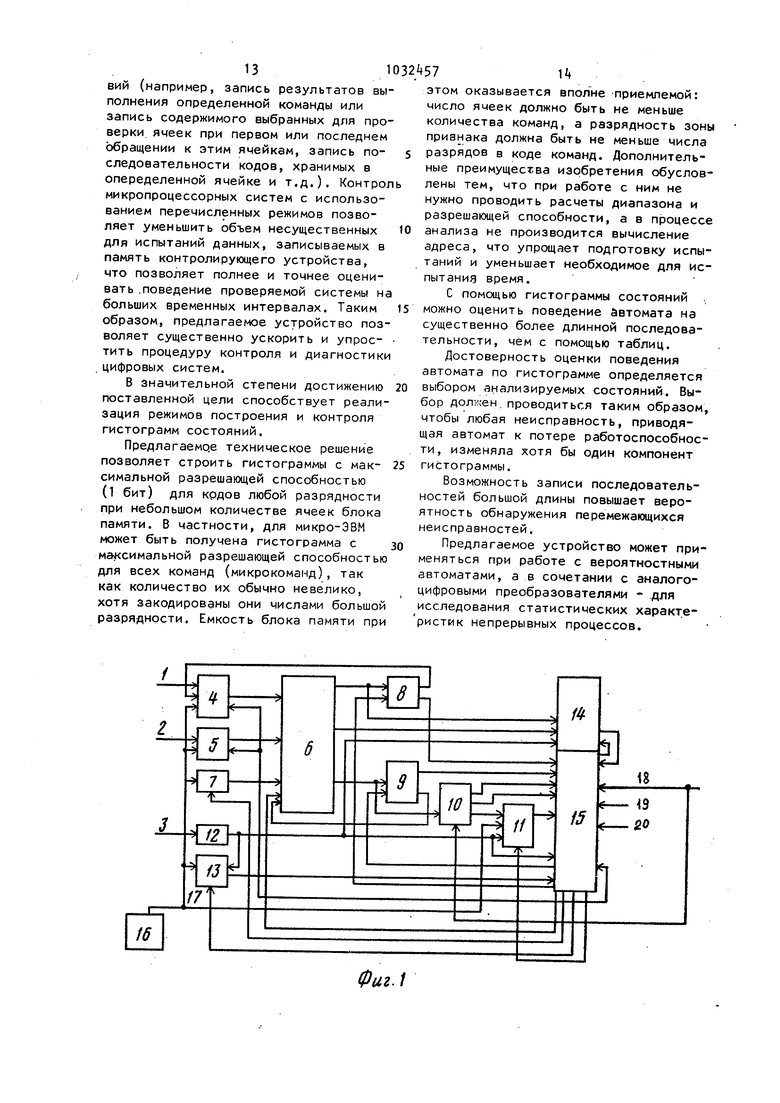

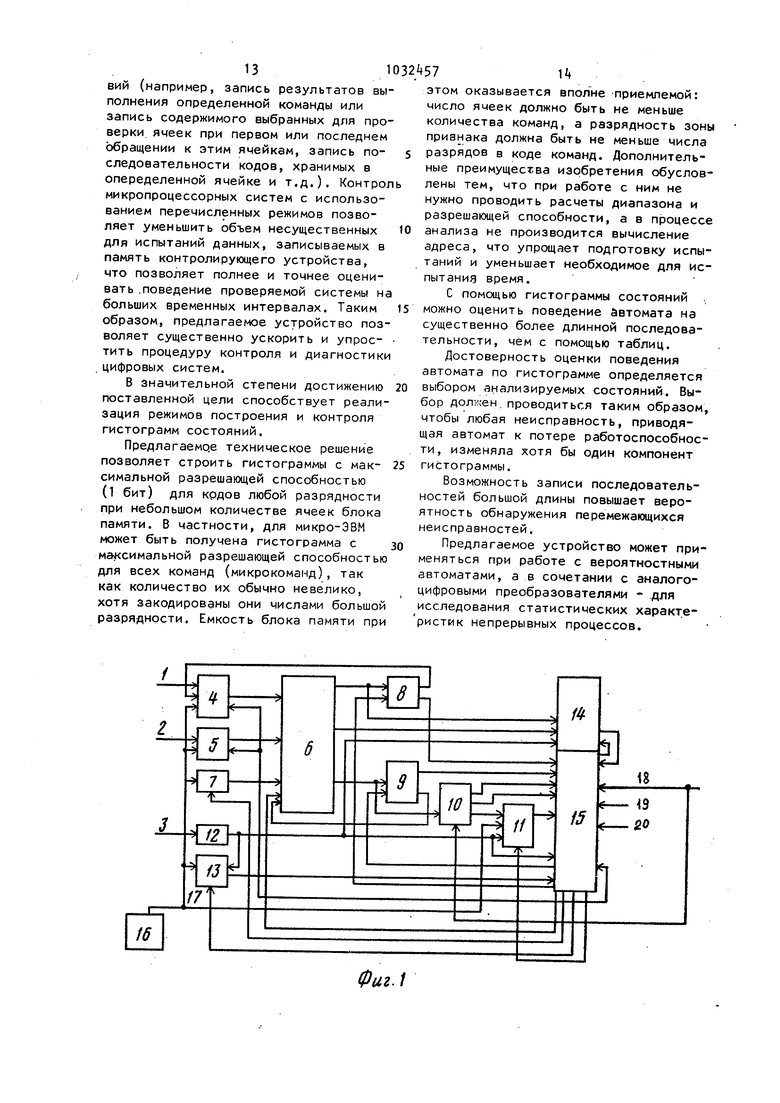

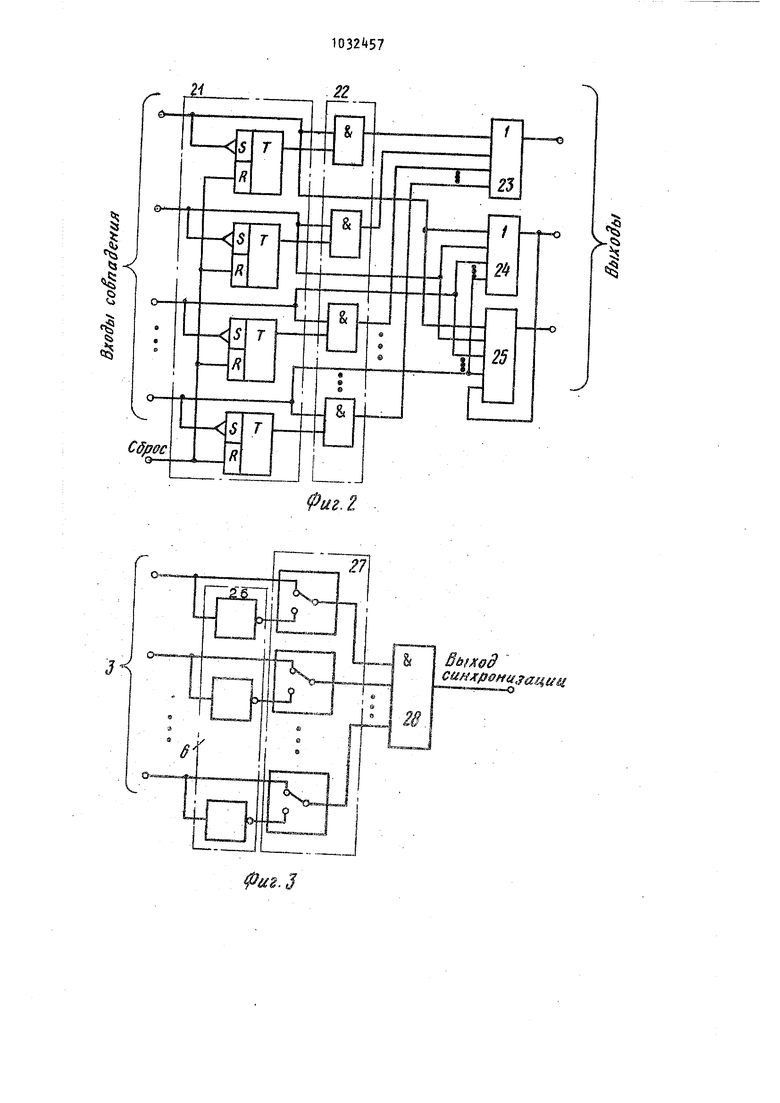

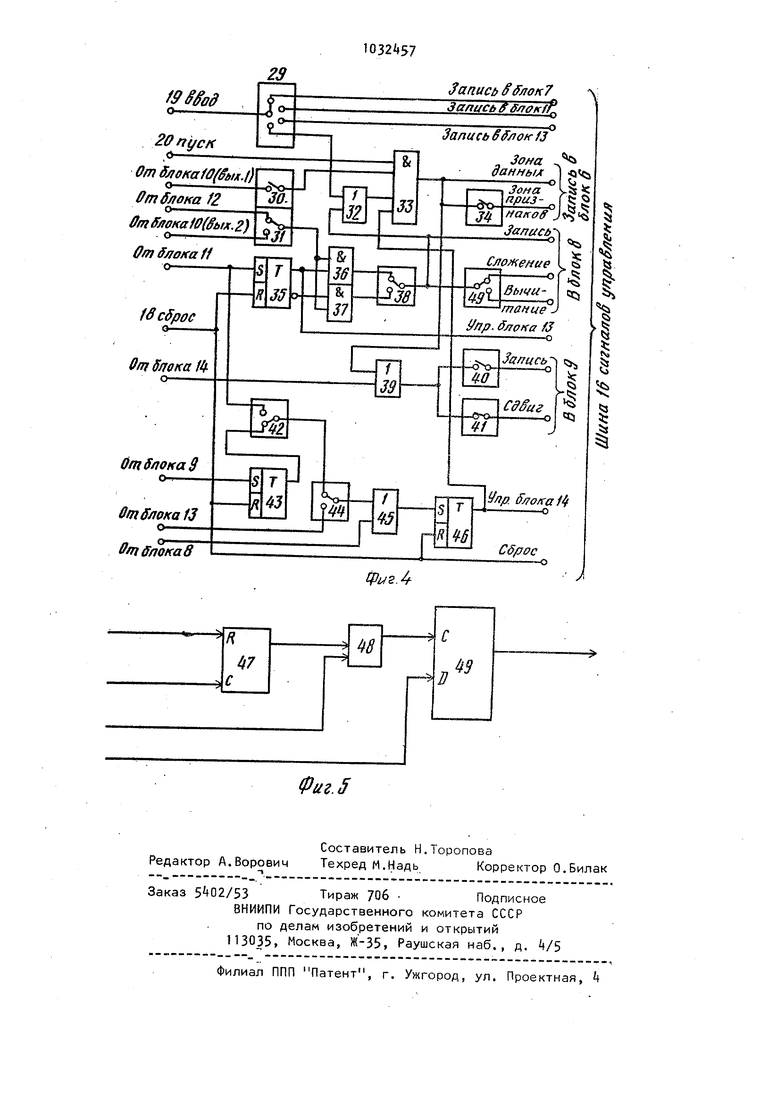

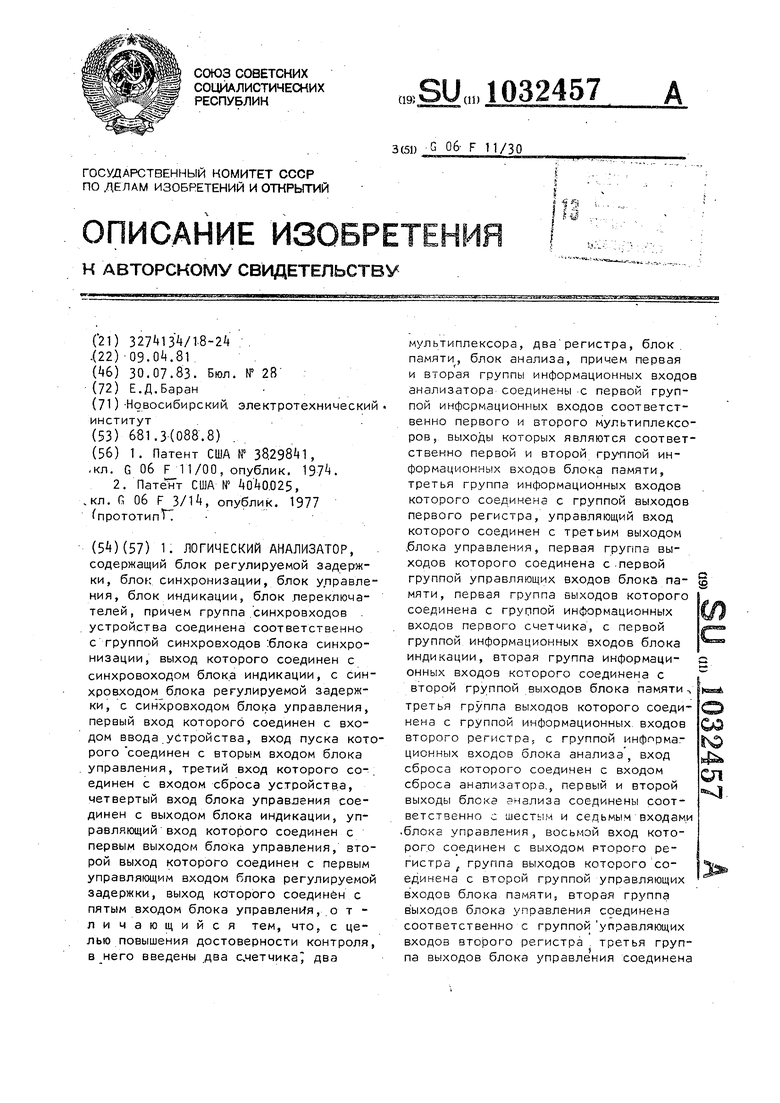

индикацией, цифроаналоговые преобразователи (ЦАП) и устройство отображения. Входы первого блока аналоговых компараторов являются информационными входами устройства, выходы этого бло ка соединены с входами буферного регистра, выходы которого подключены к информационным входам блока памяти. Входы второго блока аналоговых компараторов являются входами условий анализа (признаков) , выходы второго блока компараторов соединены с -входам цифрового компаратора, выход которого соединен с входом управления блока синхронизации. Входы третьего блока аналоговых компараторов являются входами синхронизации выходы этого блока подключены к входам блока синхронизации, выходы которого соединены с синхровходами буферного регистра и блока управления памятью. Выходы блока управления памятью соединены с адресными входами блока памяти и входами управления записью (считыванием в ЗУПВ). Выходы ЗУПВ подключены к входам блока управления индикацией, ыход синхронизации которого соединен с входом блока управления ЗУПВ, а информационные выходы блока управления индикацией соединены с входами ЦАП, Выход первого ЦАП подключаем к .горизонтально отклоняющим, а выход второго ЦАП - к вертикально отклоняющим пластинам устройства отображения 2 Недостатком данного устройства является .низкая достоверность контроля. Оценка поведения таких автоматов требует одновременного анализа весьма длинных последовательностей состояний Длина последовательности, записываемой в память известного устройства, равна количеству ячеек блока памяти. Поэтому испытания сложных автоматов с помощью такого устройства проводят путем поочередной записи и анализа различных небольших участков общей последовательности, многократного изменения режимов записи и восгтановления исходного состояния испытуемого объекта , регистрации промежуточных результатов анализа и т.п., чтотребует значительных затрат времени. Кроме того, огра ничение длины записываемой последовательности затрудняет обнаружение перемежающихся неисправностей, что уменьшает достоверность контроля. Цель изобретения - повышение достоверности контроля. Поставленная цель достигается тем, что в логический анализатор, содержащий блок регулируемой задержки, блок синхронизации, блок управления , блок индикации, блок переключателей, причем группа синхровходов устройства соединена соответственно с группой синхровходов блока синхронизации, выход которого соединен с синхровходом блока индикации, с синхровходом блока регулируемой задержки, с синхровходом блока управления, первый вход которого соединен с входом ввода устройства, вход пуска которого соединен с вторым входом блока управления, третий вход которого соединен с входом сброса устройства, четвертый вход блока управления соединен с выходом блока .индикации, управляющий вход которого соединен с первым выходом блока управления, второй выход которого соединен с первым управляющим входом блока регулируемой задержки, выход которого соединен с пятым входом блока управления , введены Два счетчика, два мультиплексора два регистра, блок памяти блок анализа, причем первая и вторая группы информационных входов устройства соединены с первой группой информационных входов соответственно первого и второго мультиплексо-: ров J выходы которых являются соответственно первой и второй группой информационных входов блока(Памяти, тре- тья группа информационных входов которого соединена с группой выходов первого регистра, управляющий вход которого соединен с третьим выходом блока управления, первая группа выходов кбторого соединена с первой группой управляющих входов блока ламяти, первая .группа выходов, которого соединена с группой информационных входов первого счетчика, с первой группой информационных входов блока индикации , вторая группа информационных входов которого соединена с второй группой выходов памяти, третья группа выходов которого соединена с группой информационных входов второго регистра, с группой информационных входов блока анализа , вход сброса которого соединен с входом сброса устройстве , первый и второй выходы бло(5а анализа соединеьгы соответственно с шестым и седьмым входами блока управления , восьмой вход которого со единен с выходом второго регистра, группа выходов которого соединена с второй группой управляющих входов блока г.амя-ти вторая группа выходов блока управления соединена соответственно с группой управляющих входов второго регистра, третья группа вы ходов блока управления соединена с группой управляющих входов первого счетчика, выход переполнения которого соединен с девятым входом блока управления, четвертая группа выходов которого соединена с группой управляющих входов второго счетчика, выход которого соединен с десятым входом блока .управления, выход блока синхронизации соединен с синхровходом второго счетчика, первая группа выходов блока переключателей соединена с второй группой информаЦИоннных входов первого и второго мультиплексоров , с группой информационных входов первого регистра, с группой информационных входов второго счетчика, с группой информационных входов блока регулиг руемой задернГки, второй управляющий вход которого соединен с третьим выходом блока анализа, группа выходов разрядов первого счетчика соединена с третьей группой информационных входов первого мультиплексора, группа управляющих входов которого соединена с группой управляющих входов второго мультиплексора, с второй группой выходов блока переключателей. Кроме того, блок анализа содержит регистр, группу элементов И, два элемента ИЛИ переключатель, причем груп па информационных входов блока соединена соответственно с группой единич ных входов регистра, соответственно с группой входов первого элемента ИЛИ соответственно с группой информационных входов переключателей соответственно с первыми входами элементов И группы, вторые входьг которых соединены с выходами регистра, нулевой вход которого соединен с входом сброса, блока первый выход которого соединен с выходом второго элемента ИЛИ, входы которого соединены соответственно с выходами элементов И группы, выход первого элемента ИЛИ соединен с управ ляющим входом переключателя и является вторым выходом блока третий выход которого соединен с выходом переключателя . Блок управления содержит девять переключателей три элемента ИЛИ, эле мент И, триггер, причем первый вход блока соединен с входом первого пере.ключателя, первый выход которого является третьим выходом блока, второй выход которого соединен с вторым выходом первого переключателя, третий выход которого является первым выходом четвертой группы выходов блока, второй выход четвертой группы выходов которого соединен с прямым выходом первого триггера, с первым входом первого элемента И, второй вход которого соединен с первым входом второго элемента И, с выходом второго переключателя, первый вход которого является синхровходом блока второй вход которого соединен с первым входом третьего элемента И, второй вход которого соединен с выходом третьего переключателя, вход которого является шестым входом блока, седьмой вход которого соединен с втбрым входом второго переключателя, пятый вход блока соединен с единичным входом первого триггера, с первым входом четвертого переключателя , второй вход которого соединен с выходом второго триггера / единичный вход которого является восьмым входом блока, третий вход которого соединен с нулевым входом первого триггера, с нулевым входом второго три1- гера с нулевым входом третьего три| гера, выход которого соединен с третьим входом третьего элемента И и является первым выходом блока , четвертый вход третьего элемента И соединен с выходом первого элемента ИЛИ, первый вход которого соединен с четвертым выходом первого переключателя, второй вход первого элемента ИЛИ соединен с выходом пятого переключателя с входом шестого переключателя и является первым выходом третьей группы выходов блока ,второй и третий выходы третьей группы выходов которого соеди нены соответственно с первым и вторым выходами шестого переключателя, выходы .первого и второго элементов И соеди-нены соответственно с первым и вторым входами пятого переключателя, ин версный BfcixoA первого триггера соединен с вторым входом второго элемента и выход третьего элемента И соединен с первым входом второго элемента ИЛИ, свходом седьмого переключателя и яв.ляется первым выходом первой группы выходов блока , второй выход второй группы выходов которого соединен с выходом седьмого пере.ключателя, первый и второй выходы второй группы выходов блока соединены соответственно с вы-ходами восьмого и девятого переключателеи f входы которых соединены с выходом второго элемента ИЛИ, второй вход которого является четвертым входом блока, девятый вход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого со(единен с выходом десятого переключа1теля, первый вход кот орого является десятым входом блока второй вход десятого переключателя соединен с вы- 0 ходом четвертого переключателя, выход третьего элемента ИЛИ соединен с еди ничным входом третьего триггера. Блок регулируемой задержки содержит триггер, элемент И, счетчик, при- 15 чем первый управляющий вход блока соединен с нулевым входом триггера, си хрОБХОД которого соединен с вторым управляющим входом блока, выход триг гера соединен с первым входом элемента И, второй вход которого соединен с синхроаходом блока, выход кото рого соединен с выходом переноса сче чика, счетный вход .которого соединен с выходом элемента И, группа информа ционных входов счетцика является груп пой информационных входов блока. На фиг,1 показана структурная схе ма устройства: на фиг,2 - схема блок анализа; на фиг.З - блок синхронизации; на фиг.4 - блок управления на фиг.5 - блок регулируемой задержки. Устройство содержит первую 1, вто рую 2 группы информационных входов устройства 5 группу 3 синхровходов j/стройства мультиплексоры и 5 блок 6 памяти регистр 7, счетчик 8 регистр 9, блок ТО анализа, блок 11 регулируемой задержки, блок 12 синхронизации, счетчик 13. блок И инди кации, блок 15 управления, блок 1б переключателей,группа выходов 17 бло ка управления и-входы устройства: вход 18 сброса, вход 19 ввода, вход 20 пуска. Блок анализа содержит регистр 21 группу 22 элементов И, элементы 23 и 24 ИЛИ и переключатель 25. I Блок синхронизации содержит груп пу 26 элементов НЕ, группу 27 переключателей и элемент И 28, Блок управления содержит переключатели 29-31, элемент ИЛИ 32, элемент И 33J переключатель 3, триггер 35 г элементы И 36 и 37, переключатель 38, элемент ИЛИ 39, переключатели fOk2 триггер , переключатель 4, эле мент ИЛИ 5 триггер 46. 10 78 БЛОК регулируемой задержки содержит триггер k7, элемент И 8, счетчик 9, Устройство позволяет осуществлять сбор данных о поведении контролируемого объекта в следующих режимах: 1. Запись последовательности состояний (выходных сигналов) контролируемого объекта после появления определенного, заданного оператором события с задержкой начала записи на заданное число тактов. 2. Запись последовательности состояний контролируемого объекта, предчествующих появлению определенного события, с задержкой окончания записи на заданное число тактов. 3. Запись состояний только в такте выполнения условия записи (появления определенного события. (Режим селек тивной записи). А. Определение частоты появления предварительно заданных событий на фиксированном временном интервале (построение гистограмм; состоя ний) . 5- Автоматический контроль работоспособности проверяемого объекта по гистограмме состояний. Рассмотрим процесс подготовки устройства к работе. Предварительно подается сигнал Сброс, с помощью которого приводятся в исходное состояние элементы памяти блока 15 управления, счетчика 8, регистра 9, блока 10, блока 11 , счетчика 13 и блока И. Затем по сигналам Ввод блок 15 управления осуществляет запись исходных Данных в блоки устройства. При этом перед каждым сигналом Ввод а блоке управления на выходах 17 устанавливается код, по сигналу Ввод формулируется импульс записи этого кода в соответствующий блок. Таким образом последовательно записываются: код маски в регистр 7, код задержки, запуска (останова) в блок 11, код длительности выборки в счетчик 13. Затем блок у правления записывает в регистр 9 код 0001 адреса первой ячейки блока памяти и через включенные входы мультиплексоров k и 5 записывает установленные предварительно на внутренней информационной шине-выходе 17 соответственно код первого признака и нули при подготовке режимов записи состояний и режима построения гистограмм или код первого повторение этого признака, - при подготовке режима контроля гистограмм. Затем вновь формируется импульс Ввод, код в регистре 9 сдвигается и по адресу 0010 производится запись во вторую ячейку блока памяти и т.д. По заполнении блока памяти устанавливается в 1 триггер 3,-единичный сигнал с выхода которого через переключатели 42, и элемент ИЛИ 45 поступает в блок индикации. Этот сигнал является сигналом окончания подготовки. 1 . Работа устройства в режиме за- писи состояний с запуском по условию и цифровой задержкой заключается в следующем. Блок переключателей устанавливает на шине управления сигналы, по которым открывается первая группа входов мультиплексоров 4 и 5. С помощью переключателей выбирается признак , по которому необходимо осуществить запуск. Устройство подключают к контролируемому блоку следующим образом. Выходы блока, на которых появляются сигналы, характеризующие состояние системы, соединяют с группой 1 входо Выходы блока, на которых появляются сигналы, определяющие условия изменения состояний системы (например, команды или адреса блока памяти), соед няются с группой 2 входов устройства Вход 3 синхронизации подключается к шине тактирующих сигналов. Затем подается сигнал Сброс, с помощью которого устанавливаются в О триггер блока 10 анализа триггеры блока 11 регулируемой задержки и счетчика 13, а также триггеры блока. 15 управления Работа начинается по сигналу Пус которым включается блок 12 синхронизации. Тактовые импульсы, формируемы блоком синхронизации, поступают на соответсгвуше входы блоков 11, 13, 15 , однако не вызывают изменения состояний элементов этих блоков до тех пор, пока на группе входов 2 устрО|3ства не появится код запуска тересующего оператора признака Коды группы 2 входов поступают на входы блока 6, причем при появлении кода запуска на выходе блока б появляется сигнал 1, который через открытую первую группу входов мультиплексора включает блок 11. Поэтому .первым после запуска (т.е. после по10код И 710 явления кода запуска) импульсом в ре гистр 9 записывается код 0001 адреса первой ячейки блока памяти, следующим тактовым импульсом записывается код, поступающий с выходов контролируемого блока через группу 1 входов и открытую первую группу входов мультиплексоров 4 на входы блока 6, Затем блок 16 устанавливает код 0010 адреса второй ячейки блока памяти в зону данных в которой записывается код следующего состояния контролируемого блока и т.д. По окончании записи в последнюю ячейку блока памяти сигнал, переполнения регистра 9 через блок 15 управления включает блок 14 индикации. 2. При работе в режиме 2 (задержки останова по условию) запись в блок 6 начинается сразу после сигнала Пуск, а заканчивается при появлении на группе 2 входов устройства кода останова и отсчета заданной задержки. Для этого в блоке управления формируются си|- налы многократной периодической записи сигналов поступающих от контролируемого блока по входам 1 через мультиплексоры 4 в блок 6, После подачи сигналов Сброс и Пуск тактовые импульсы с выхода блока 12 синхрони- , зации поступают на вход синхронизации регистра 9 По заполнений всех ячеек . блока 6 сигнал 1 с выхода старшего разряда регистра 9 поступает на управляющий вход регистра 9- Поэтому последующими тактовыми импульсами запись состояний с входов 8 блок 6 продолжается и ранее записанные данные заменяются вновь поступившими. При появлении на входах 2 кода совпадающего с кодом, записанным в блоке 6, на вьц. ходе последнего появляется 1, включается блок 11, и после отсчета заданного числа тактов сигнал с выхода блока 11 включает блок 14 индикации и прекращает запись в блок 6, При этом в блоке 6 остаются записанными те состояния контролируемого блока , которые предшествовали появлению кода останова при нулевой задержке останова. Если задержка не равна нулю, но число тактов задержки не превышает количества ячеек блока 6, то в блоке: 6 окажутся зарегистрированными состояния как предшествующие моменту появления кода останова, так и следующие после него. 3. Режим селективной записи состояний отличается от ранее рассмотренных тем что запись в блок 6 осуществляет ся только при совпадении кода, поступающего по группе 2 входов с кодами, хранящимися в блоке 6. Последовательность выбираемых для записи ячеек может определяться последовательностью кодов, постуг а гщйх от проверяемого блока через группу 2 входов и мультиплексор 5 на входы блока 6 или может быть упорядоченной по номерам ячеек. и При первом способе адресации блок 15 управления по сигналам совпадения формирует импульсы записи адреса совпадения с выходов блока 6 в регистр 9 Таким образом J в этом режиме осуществляется селективная запись со стояний контролируемого блока . Если, ;например , группа 1 входов устройст ва подключена к входам информации проверяемого блока ,а группа 2 вхо дов устройства подключена к входам адреса блока , то по окончании записи в блоке б остается Записанным содер.Жимое ячеек проверяемого блока адре са которых заданы кодами признаков. Предлагаемое устройство позволяет также проследить изменение содержимого заданной ячейки или изменение per аультатрв выполнения определенной йоманды Для этого при подготовке код адреса этой ячейки (или код команды) записывается в блок 6 и уста;навливается. код адреса соответствующей группь входов переключателя 25 блока 10. . При этом разрешается последовательный режим записи в регистр 9j а импульсы записи в этот регистр и в блок 6 формируются только при совпадении кода на группе 2 входов устрой ства. с заданным, кодом признака (кодом адреса или команды), , Режим построения гистограмм. Блок 1б устанавливает сигналы, по которым включается вторая группа входов мультиплексоров k и первая группа входов мультиплексора 5 При этом через мультиплексор подклнэча ются в блок 6 разрядные выходы счетт чика 8 и группа 2 входов устройства. Затем формируются сигналы Сброс и Пуск, По сигналу Пуск включаются проверяемый блок,и блок 12 синхронизации устройства 5 Режим автоматическоно контроля работоспособности по гистограмме состояний При подготовке этого ре ,жима в блок 6 записываются числа равные частоте появления на выбранном интервале времени признаков , записанных при подготовке в блок 6 Счетчик 8 переводится а режим выг чйтания. Устройство работает так же, как в режиме построения гистограмм но в процессе работы при совпадении кода на входах 2 с кодом признака одной из ячеек блока 6 , записи содержимого этой ячейки в счетчик 8, а адреса в регистр 9 , из содержимого 8 вычитается единица Если контролируемый блок работает правильно , то по окончании времени выборки содержимое всех ячеек блока 6 должно быть равно нулю , в противном случае , т. е. если система функционирует неправильно и.при этом час тота повторений одного или нескольких признаков исправной и неисправной систем не совпадают (что обычно справедливо для широкого класса систем), содержимое блока 6 отлично от нуля. Если один из признаков появляется чаще, чем это должно быть, то импульс с выхода счетчика 8 через блок 15 управления включает блок индикации до окончания времени выборки. При этом, как и в режиме подготовки, осуществляется поочередный опрос ячеек блока 6 и индикация их содержимого на экране блока Н. Для проведения повторной записи состояний необходимо восстановить код задержки запускаи, код времени выборки в..блоке 11 и счетчике 13. Реализация блока управления на основе микроЭВМ упрощает подготовку к работе и эксплуатацию устройства. Таким образом, предлагаемое устройство обеспечивает возможность записи последовательности состояний контролируемой системы в режимах с задержкой запуска (останова) относительно выбранного предварительно условия (признака), В отличие от устройства-прототипа, которое также может работать в этих режимах, предлагаемое устройство позволяет осуществлять запуск по одному из нескольких введенных заранее в блок памяти условий, или при реализации события, заключающегося в появлении любого из этих условий. Кроме того, изобретение в отличие от прототипа позволяет проводить селективную запись, т.е. запись только в моменты выполнения заданных уелоВИЙ (например, запись результатов выполнения определенной команды или запись содержимого выбранных для проверки, ячеек при первом или последнем обращении к этим ячейкам, запись последовательности кодов, хранимых в опеределенной ячейке и т.д.). Контрол микропроцессорных систем с использованием перечисленных режимов позволяет уменьшить объем несущественных для испытаний данных, записываемых в память контролирующего устройства, что позволяет полнее и точнее оценивать .поведение проверяемой системы на больших временных интервалах. Таким образом, предлагаемое устройство позволяет существенно ускорить и упростить процедуру контроля и диагностики цифровых систем.

В значительной степени достижению поставленной цели способствует реализация режимов построения и контроля гистограмм состояний.

Предлагаемре техническое решение позволяет строить гистограммы с максимальной разрешающей способностью (1 бит) для крдов любой разрядности при небольшом количестве ячеек блока памяти. В частности, для микро-ЭВМ может быть получена гистограмма с максимальной разрешающей способностью для всех команд (микрокоманд), так как количество их обычно невелико, хотя закодированы они числами большой разрядности. Емкость блока памяти при

этом оказывается вполне приемлемой: число ячеек должно быть не меньше количества команд, а разрядность зоны привнака должна быть не меньше числа разрядов в коде команд. Дополнительные преимущества изобретения обусловлены тем, что при работе с ним не нужно проводить расчеты диапазона и разрешающей способности, а в п эоцессе анализа не производится вычисление адреса, что упрощает подготовку испытаний и уменьшает необходимое для испытание время.

С помощью гистограммы состояний можно оценить поведение автомата на существенно более длинной последовательности, чем с помощью таблиц.

Достоверность оценки поведения автомата по гистограмме определяется выбором анализируемых состояний. Выбор . проводиться таким образом, чтобы любая неисправность, приводящая автомат к потере работоспособности, изменяла хотя бы один компонент гистограммы.

Возможность записи последовательностей большой длины повышает вероятность обнаружения перемежающихся неисправностей.

Предлагаемое устройство может применяться при работе с вероятностными автоматами, а в сочетании с аналогоцифровыми преобразователями - .для исследования статистических характеристик непрерывных процессов.

Фиг.1

иг,2

iMTj;

«.

.

3

b-Jp

nuiB III Ilia. jb.uagjag-aS

Urr

i. 3

v

§

cuHJ ftOHu am/ii fdSffod От $локаЮ(мх.1} ffтолока f2 о ffm SaoKatO(ffbix. 2) От блока ff о fScSpoc OmSaoKslit ОтУлокаЗ о От блока 13 O/nffnoKaB За За .4ись лок7 исью

9

S

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для автоматического пуска электрического двигателя трехфазного тока для пожарного насоса | 1929 |

|

SU29841A1 |

| Способ утилизации отработанного щелока из бучильных котлов отбельных фабрик | 1923 |

|

SU197A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

Авторы

Даты

1983-07-30—Публикация

1981-04-09—Подача