Изобретение относится к цифровой вычислительной технике и может быть исполь- зовано для проверки и поиска неисправностей в сложных логических блоках и системах.

Целью изобретения является повышение достоверности контроля и сокращение времени, необходимого для реализации контроля.

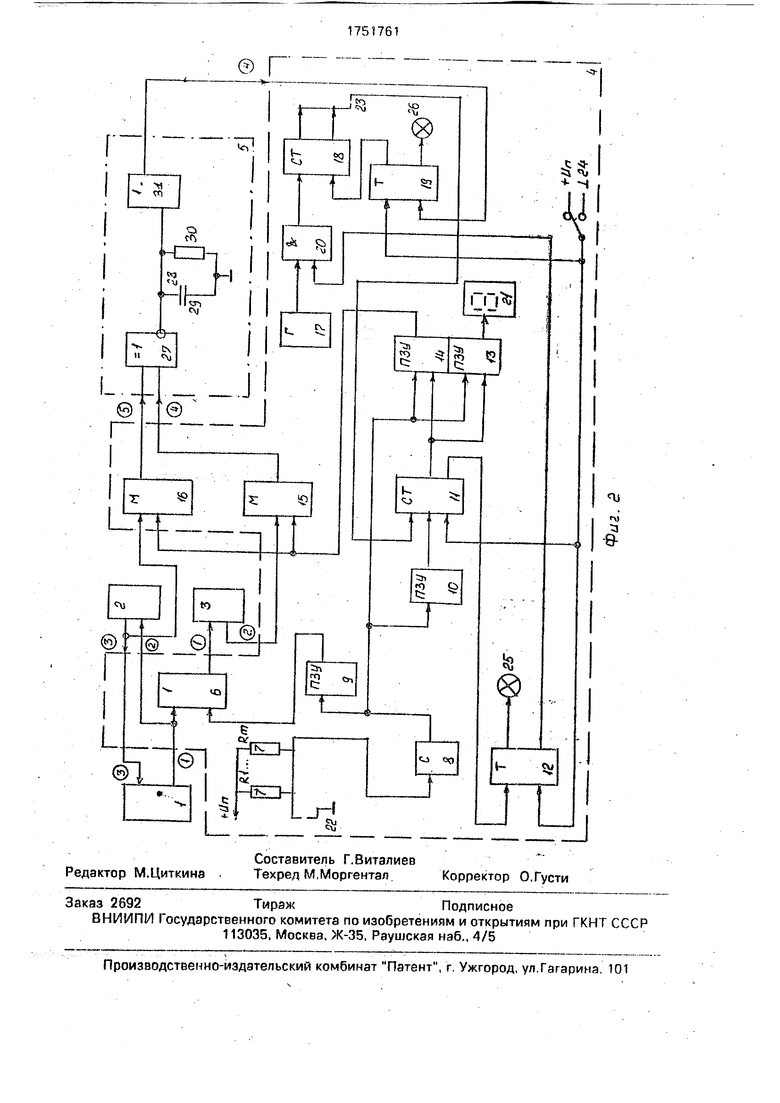

На фиг. 1 представлена структурная схема асинхронного автоматического устройства для контроля цифровых систем; на фиг. 2 - функциональные схемы блока контроля и анализатора перекоса.

На фиг, 1 представлены система 1 обработки данных, эталонный блок 2, контролируемый блок 3 (объект контроля - один из блоков системы 1), блок 4 контроля и анализатор 5 перекоса.

Блок 4 контроля (фиг. 2) содержит п ключей 6, m резисторов (генераторов единичного потенциала) 7, шифратор 8, блоки 9 и 10 постоянной памяти, счетчик 11, триггер 12, блоки 13 и 14 постоянной памяти, п/8 мультиплексоров 15 и 16, генератор 17 импульсов, делитель 18, триггер 19, элемент И 20, группу цифровых индикаторов 21, переключатели 22 и 23, кнопку 24 сброса, индикатор 25 Исправен и индикатор 26 Неисправен. Каждый из п ключей 6 группы имеет три выходных состояния (где п - количество контактов в разъеме для подключения эталонного блока 2 к. системе 1 обработки данных). Переключатель 22 имеет m положений (где m - количество блоков, входящих в систему 1 обработки данных).

Анализатор 5 перекоса (фиг 2) содержит элемент 27 ИСКЛЮЧАЮЩЕЕ ИЛИ, дифференцирующую цепочку 28, включающую резистор 29 и конденсатор 30, и формирователь 31.

Устройство работает следующим образом.

С помощью переключателя 22 устанавливается номер, присвоенный эталонному блоку 2 для данной системы 1 обработки данных. С помощью переключателя 23 устанавливается временной интервал ortl до12, в течение которого происходит изменение всех выходных сигналов контролируемого блока. Система 1 обработки данных переводится в рабочий режим. После нажатия кнопки 24 сброса запускается процесс контроля. При установке переключателя 22 в состояние с заданным номером на соответствующий вход шифратора 8 подается О, а на остальных его входах с помощью резисторов поддерживается потенциал 1. На выходе шифратора 8 формируется двоичное слово, соответствующее выбранному номеру блока. Код этого двоичного слова поступает на адресный вход блока 9, на выходе которого позаписан ной в него таблице формируется n-раэрядное слово. Потенциалы первой группы выходов блока 9 открывают часть ключей б, которые пропускают сигналы, являющиеся входными для контролируемого блока 3, а потенциалы I с другой группы выходов блока 9 закрывают часть ключей б, которые не пропускают соответствующие выходные сигналы.

Код двоичного слова с выхода шифратора 8 поступает также на адресный вход блока 10 и на входы разрешения обращения блоков 13 и 14, На выходе блока 10 формируется двоичное слово, код которого соответствует количеству выходных контактов для данного контролируемого блока 3 С выхода блока 10 код сформированного двоичного слова поступает па установочный вход счетчика 11 и записывается в него нажатием кнопки 24 сброса. Записанное в счетчик 11 двоичное слово с его выхода поступает на адресные входы блоков 13 и 14. На выходе блока 13 по таблице, записанной D него, формируются семиразрядные слова, которые поступают на цифровые индикаторы 21 и высвечивают номер проверяемого контакта в системе обозначений данного разъема. На выходе блока 14 по заданной программе (габлице) форг эируется двоичное слово разрядностью 3 ьп/8. Первые три разряда этого слова поступают на управляющие входы всех мультиплексоров 15 и 16, я остальные разряды кода с выхода блока 14 поступают на два одноименных мультиплексора 15 и 16 (на входы включения микросхем в активное состояние).

Программа (таблица) D блоке 1 записана таким образом, что сигнал с контактов эталонного и контролируемого блоков 2 и 3.

номер которого индицирован с помощью блока 13, через мультиплексоры 15 и 16 подается на соответс гвующий вход анализатора 5 перекоса Если эти выходные сигналы

одинаковы, то на выходе элемента 27 сохраняется потенциал 1 и через время, определяемое положением переключателя 23 счетчик 11 переводится в состояние на единицу меньше предшествующего Код этого

0 нового числа с выхода счетчика 11, поступая на входы блоков 13 и 14, высвечивает номер следующего контакта (с помощью блока 13) и передает соответствующие сигналы выходных контактов эталонного и контролиру5 емого блоков 2 и 3 (с помощью блока 14 и мультиплексоров 15 и 16) на входы анализатора 5 перекоса. На выходе переноса счетчика 11 появляется импульс (после отсчета числа, определяющего количество выход0 ных контактов), который поступает на вход триггера 12. В результате триггер 12 меняет свое состояние, которое отображается индикатором 25 (Исправен). Кроме того, сигнал с второго выхода триггера 12 запрещает

5 прохождение сигнала с выхода генератора 17 чепез элемент I/I 20 на вход делителе 18. Если же обнаруживается несоответствие между сигналами эталонного и контролируемого блоков 2 и 3, то на выходе элемента

0 27 устанавливается потенциал О, а перепад сигнала, продифференцированный цепочкой 28, поступает на вход формирователя 31 С выхода формирователя 31 импульсный сигнал (наличие которого

5 зависит от сдвига входных сигналов знали затора 5 перекоса), поступая на вход сброса (R) триггера 19, переводит его в нулевое состояние и останавливает делитель 18, а следовательно, и счетчик 11. С помощью

0 индикатора26 отображается состояние неисправности контролируемого блока, а также индицируется (элементами 21) номер контакта, на котором обнаружена неисправность,

5 Для контроля другой системы обработки данных достаточно сменить прошивку таблиц в блоках постоянной памяти. Формула изобретения 1. Acnh хронное автоматическое устрой0 ство для контроля цифровых систем, содержащее эталонный блок и анализатор перекоса, отличающееся тем, что, с целью повышения достоверности контроля и сокращения времени, необходимого для

5 реализации контроля, в него введен блок контроля, который включает группу из п ключей (где п - количество контактов в разъеме для подключения эталонного блока по входу и выходу данных), переключатель на m положений (где m - количество блоков,

подлежащих проверке), группу из m генераторов единичного потенциала, шифратор, четыре блока постоянной памяти, счетчик, два триггера, две группы из п/8 мультиплексоров, генератор импульсов, делитель, эле- мент И, переключатель временных интервалов, группу цифровых индикаторов, индикатор Исправен, индикатор Неисправен и кнопку сброса, при этом вход эталонного блока и первые входы всех ключей группы объединены и образуют вход опроса устройства, информационные входы мультиплексоров первой группы являются входом устройства для подключения к выходу объекта контроля, выходы ключей группы являются выходом устройства для подключения входу объекта контроля, первый вывод переключателя на гл положений соединен с шиной нулевого потенциала, а 1-й второй вывод переключателя на m поло- хений (1 i m) подключен к выходу i-ro генератора единичного потенциала и f-му входу шифратора, выход которого соединен с адресными входами первого и второго блоков постоянной памят и и входами разре- шения обращения третьего и четвертого блоков постоянной памяти, выход первого блока постоянной памяти подключен к вторым входам всех ключей группы, адресные входы третьего и четвертого блоков посто- яиной памяти соединена с информационным выходом счетчика, выход третьего блока постоянной памяти подключен к входам цифровых индикаторов группы, выход четвертого блока постоянной памяти соеди- нен с управляющими входами всех мультиплексоров первой и второй групп, вход сброса, тактовый вход и вход останова счетчика подключены соответственно к выходам кнопки сброса, второго блока постоянной памяти и переключателя временных интервалов, вход установки, вход сброса и прямой выход первого триггера соединены соответственно с выходом переноса счетчика, выходом кнопки сброса и входом индикатора Исправен, информационные входы мультиплексоров второй группы подключены к выходу эталонного блока,выходы мультиплексоров первой и второй групп соединены соответственно с первым и вторым информационными входами анализатора перекоса, первый и второй входы и выход элемента И подключены соответственно к выходу генератора импульсов, инверсному выходу первого триггера и тактовому входу делителя, выходы которого соединены с одноименными входами переключателя временных интервалов, а вход установки, вход сброса, прямой и инверсный выходы второго триггера подключены соответственно к выходу анализатора перекоса, выходу кнопки сброса, входу индикатора Неисправен и входу останова делителя,

2. Устройство поп, 1, о т л и ч а ю щ е е- с я тем, что анализатор перекоса содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, дифференцирующую цепочку и формирователь, выход которого является выходом анализатора, первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являтотся первым и вторым информационными входами анализатора, а выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом формирователя и первым выводом дифференцирующей цепочки, второй вывод которой подключен к шине нулевого потенциала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство контроля | 1985 |

|

SU1291931A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для оценки профессиональной пригодности оператора | 1989 |

|

SU1714646A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Устройство для диагностирования логических блоков | 1982 |

|

SU1071978A1 |

Изобретение относится к области вычислительной техники и может быть исполь- зовано для проверки и поиска неисправностей в сложных логических блоках и системах. Целью изобретения является повышение достоверности контроля и сокращение времени, необходимого для реализации контроля. С этой целью в устройство, содержащее эталонный блок и анализатор перекоса, введен блок контроля, который включает группу из п ключей, переключатель на m положений, группу из m генераторов единичного потенциала, шифратор, четыре блока постоянной памяти, счетчик, два триггера, две группы из п/8 мультиплексоров, генератор импульсов, делитель, элемент И, переключатель временных интервалов, группу цифровых индикаторов, индикатор ИСПРАВЕН, индикатор НЕИСПРАВЕН и кнопку сброса 2 ил. (Л

| Устройство стабилизации сильноточного тлеющего разряда | 1974 |

|

SU528709A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 4122995, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1992-07-30—Публикация

1989-10-23—Подача