//

и

1л

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для логической обработки информации | 1984 |

|

SU1262519A1 |

| Устройство для решения систем алгебраических уравнений | 1984 |

|

SU1325507A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Устройство для функционального контроля линейных цифровых блоков | 1988 |

|

SU1631545A1 |

| Устройство решения систем логических уравнений | 2017 |

|

RU2654137C1 |

| Устройство для определения аргумента семейства периодических функций | 1988 |

|

SU1562928A1 |

| Устройство для решения системы линейных алгебраических уравнений | 1986 |

|

SU1405073A1 |

| Устройство для реализации логических функций | 1981 |

|

SU1164724A1 |

| Устройство для исследования графов | 1985 |

|

SU1305720A1 |

| Устройство для раскраски графов | 1985 |

|

SU1283783A1 |

Изобретение относится к вычислительной технике, а именно к устройствам для решения логических уравнений. Цель изобретения - повышение точности устройства за счет получения решения минимальной мощности. Устройство содержит счетчик 3, п групп элементов по m элементов И в каждой, где п - число переменных уравнения; m - разрядность коэффициентов уравнений, операционный блок 5, блок 6 сравнения, триггер 7, элементы НЕ 8 и 9, элемент И 13 и блок 14 памяти. В основе работы устройства лежит формирование лексикографически упорядоченных значений параметров и оценки решения на каждом шаге. 3 ил., 1 табл.

СП) 00

Изобретение относится к вычисли тельной технике, а именно к специали- эированньм устройствам для решения логических уравнений,

Цель изобретения - повышение точности за счет получения решения минимальной мощности.

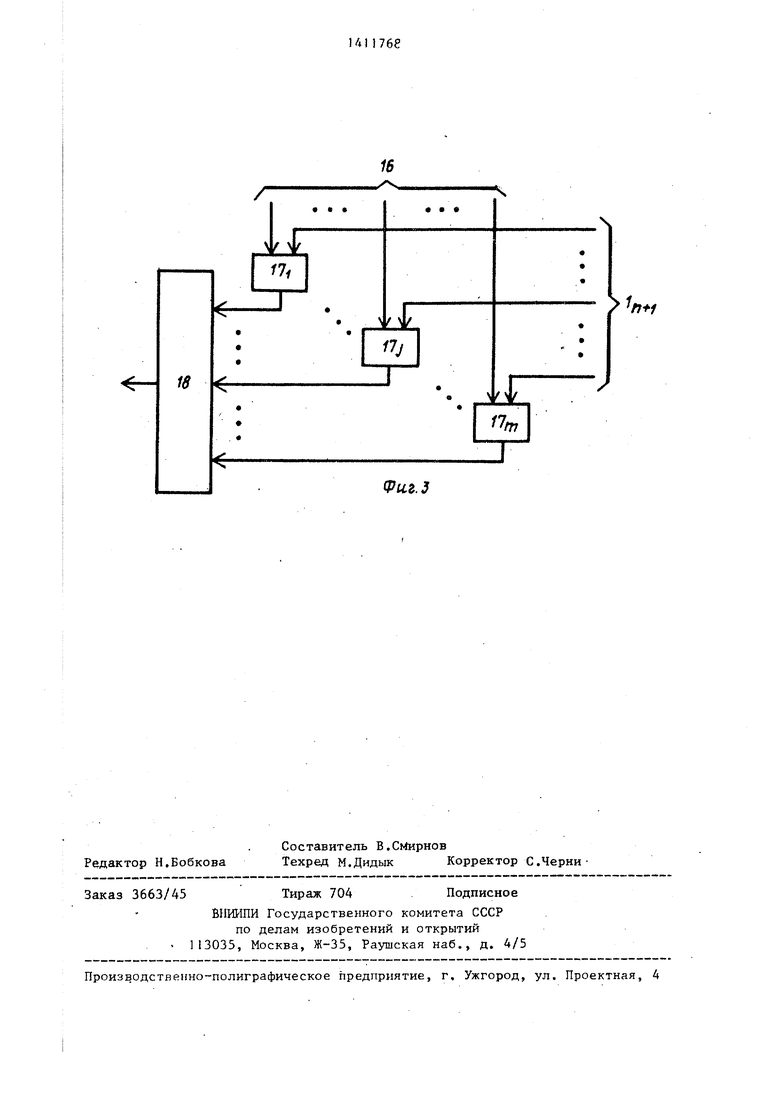

На фиГо представлена схема устройства j на - схема операцион- него блокад на фиг.З - схема блока сравнения,

Устройство содержит входы - 1 коэффициентов -уравнения устройстваj вход If, правой части уравнения уст- ройства, выходы 2 результата устройства j счетчик 3, группы 4 с первой по П--Ю элементов И, операционный блок 55 блок 6 сравнения, триггер 7; первый 8 и второй 9 элементы НЕ, вы- ходы 10 признака отсутствия решения .уравнения ус тройств а выход 1 признака наличия решения уравнения устройства; тактовый вход 12 устройства; элемент И 13, блок 14 памяти. Опера- ционный блок 5 содержит сумматоры 15 по модулю 2, выходы 16 операционного блока.. Блок сравнения содержит элементы РАВНОЗНАЛНОСТЬ 17,™ элемент И 18.

Устройств.о .работает следующим образом.

Устройство предназначено для решения логических уравнений вида

Х. при

:-к,

1 Т

mm

где А. - i-e-га-разрядное двоичное

слово;

п - количество двоичных слов и, соответственно,, количество . переменных; х е 0,1

В - двоичное слово5 соответствующее правой- части уравнения .

Решение уравнения заключается в определении множества х fх,,..«jX минимальной мощности, удовлетворяющего этому условию,

В зависимости от двоичного кода, поступающего с выхода - счетчика 3, с выхода блока 14 памяти вьщаются сигналы 1 в соответствующих позициях, при этом номера позиций фор- мируе.мые для ка ждого состояния счетчика 3, являются лек с 1-жо графически упорядоченными. В таблице приведен пример формирования сочетания .

000 001 010 100

01 101

по

П1

5 20 25 30

5

5

0

из таблицы ви,цно, что вначале фор-. мируются сочетания по одному элемен- тув затем по два, по три и т.д.

На входы 1 1 j подаются соответственно двоичные слова А, ,,., на

вход 1 подается двоичное слово В, (j-й разряд всех двоичных слов, име- ющий вес 2 , подается на j-й вход, . ,,„, j,m) . В исходном состоянии триг- е гер 7 находится в состоянии 1, двоичный счетчик 3 в состоянии Оо,„0. На .выходе блока 14 памяти двоичный код Ооо.ОК На (п+1)-м выходе двоичного счетчика - сигнал О, на выходе элемента НЕ 9 поэтому после подачи тактовых импульсов через элемент И 13-импульсы поступают йа счетный вход двоичного счетчика 3$ меняя его состояние. Значение i-ro выходного разряда блока 14 памяти соответствует значению х . Если х 1, то открывается i-я группа элементов И 4, и на .вход операционного блока 5 поступает двоичное слово , если х 0, то Операционный блок 5 вычисляет выражение

С

х,А.

путем поразрядного сложения ,по модулю 2 соответствующих разрядов, поступающих на его входы двоичных чисел.

Блок 6 сравнения производит поразрядное сравнение чисел С и В. При

на выходе блока 6 сравнения формируется сигнал 1, сбрасывающий триггер 7 в нулевое состояние. При этом закрывается элемент И 13, и импульсы не пиоходят на счетный вход двоичного счетчика 3 и не меняют его состояния.

В процессе решения могут быть два случая.

Решение уравнения существует. При этом на выходе 11 появляется признак наличия решения, и значение разрядов на выходах 2 результата соответствует значениям х,

Решения нет. В этом случае после перебора всех 2 вариантов двоичный счетчик 3 на (n- -I)-M выходе формирует сигнал 1, при этом на выходе 10 появляется признак отсутствия решения, через элемент НЕ 9 на вход элемента И 13 поступает сигнал О, закрывающий поступление импульсов на счетный вход счетчика 3.

Формула изобретения

Устройство для решения логических уравнений, содержащее счетчик, элемент И, первый и второй элементы НЕ, триггер, операционный блок, блок сравнения, п групп по m элементов И, каждая, где п - число переменных уравнения, m - разрядность коэффициентов уравнения, причем j-й вход (З 1,,..т) i-ro (,.... ,п) коэффициента уравнения устройства подклю

5

чен к первому входу j-ro элемента И i-й группы, выход которого подключен к j-му информационному входу i-й группы операционного блока, j-й выход которого подключен к j-му входу первой группы блока сравнения, j-й вход второй группы блока сравнения подключен к j-му входу значения.правой части уравнения устройства, тактовый вход устройства подключен к первому входу элемента И, выход которого подключен к счетному входу счетчика, первый информационный выход которого подключен к выходу признака отсутствия решения устройства и к входу первого элемента НЕ, выход которого подключен к второму входу элемента И, выход блока сравнения подключен к счетному входу триггера, выход которого подключен к выходу признака наличия решения устройства и к входу второго элемента НЕ, выход которого подключен к третьему входу элемента И, отличающееся тем, что, с целью повышения точности за счет получения решения минимальной мощности, оно содержит блок памяти, причем с второго по (п+1)-й ин- Q формационные выходы счетчика подключены соответственно к адресным входам с первого по п-й блока памяти, вход чтения которого подключен к тактовому входу устройства, i-й выход блока памяти подключен к i-му вьпсоду результата решения устройства и к вторым входам m элементов i-й группы.

0

5

35

Н

1т

16

fPil2.2

| Логический процессор | 1977 |

|

SU746531A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для логической обработки информации | 1984 |

|

SU1262519A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-23—Публикация

1986-12-05—Подача