1

10

Изобретение относится к вычислительной технике и может быть использовано при -решенин систем линейных алгебраических уравнений, например, в системах автоматического управления динамическими объектами,

Цель изобретения - повышение точности решения.

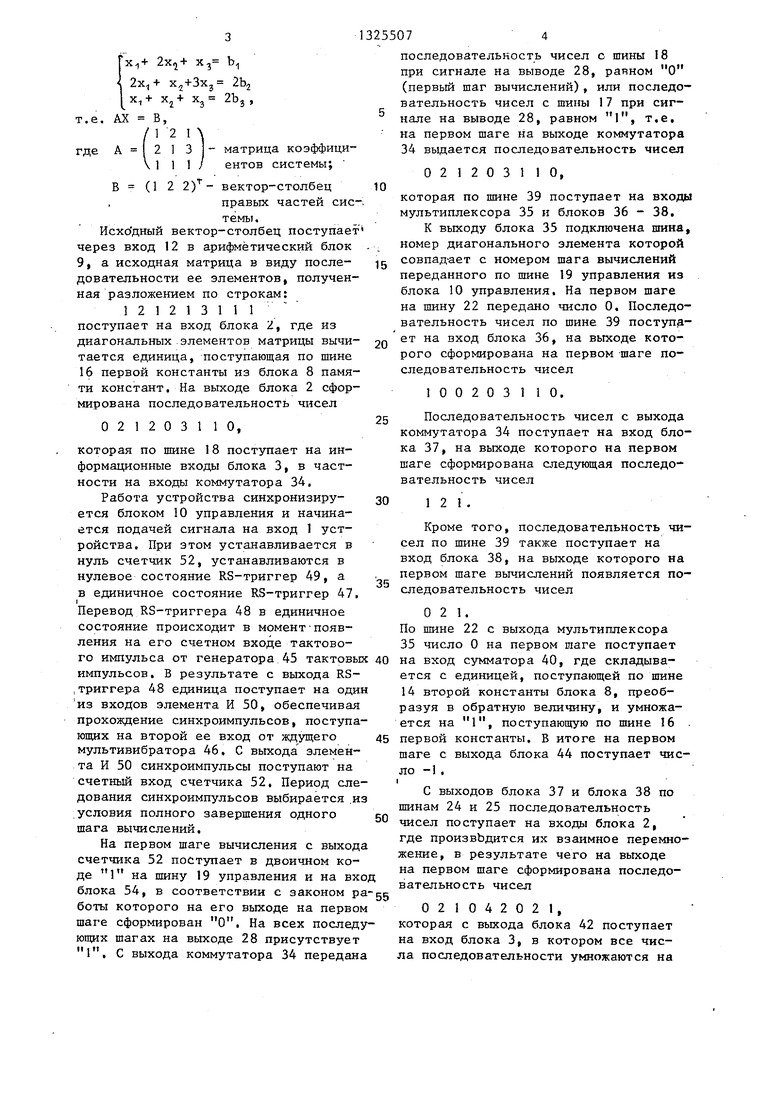

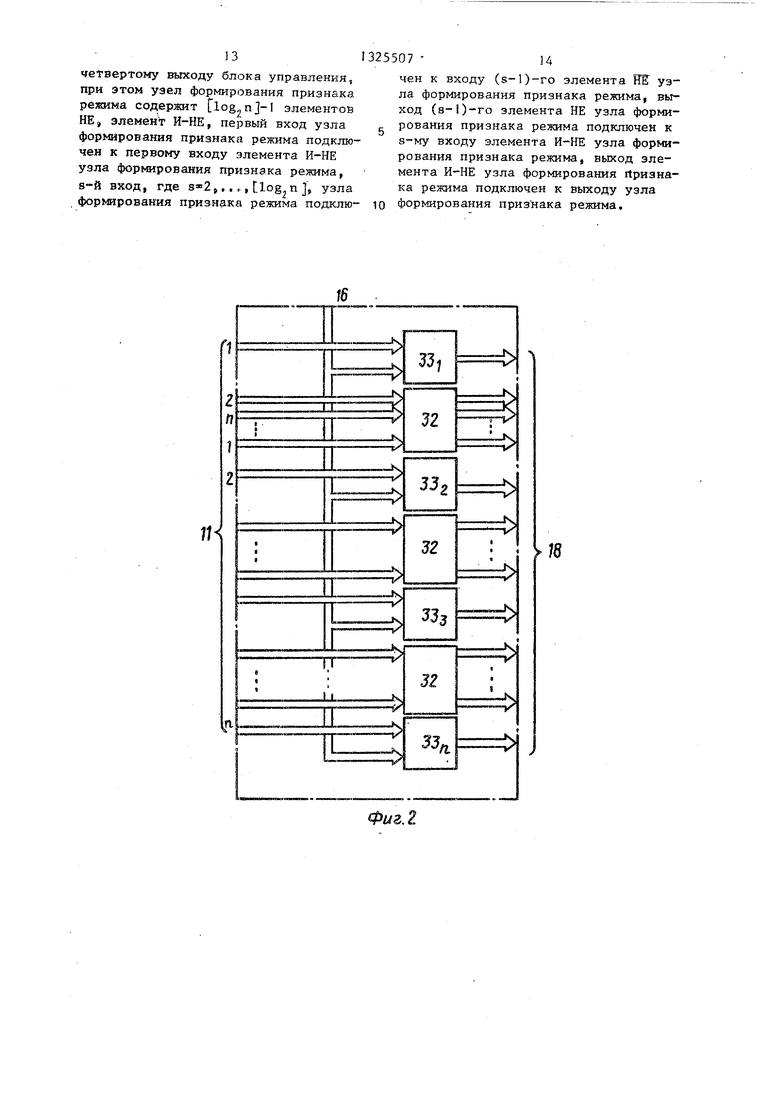

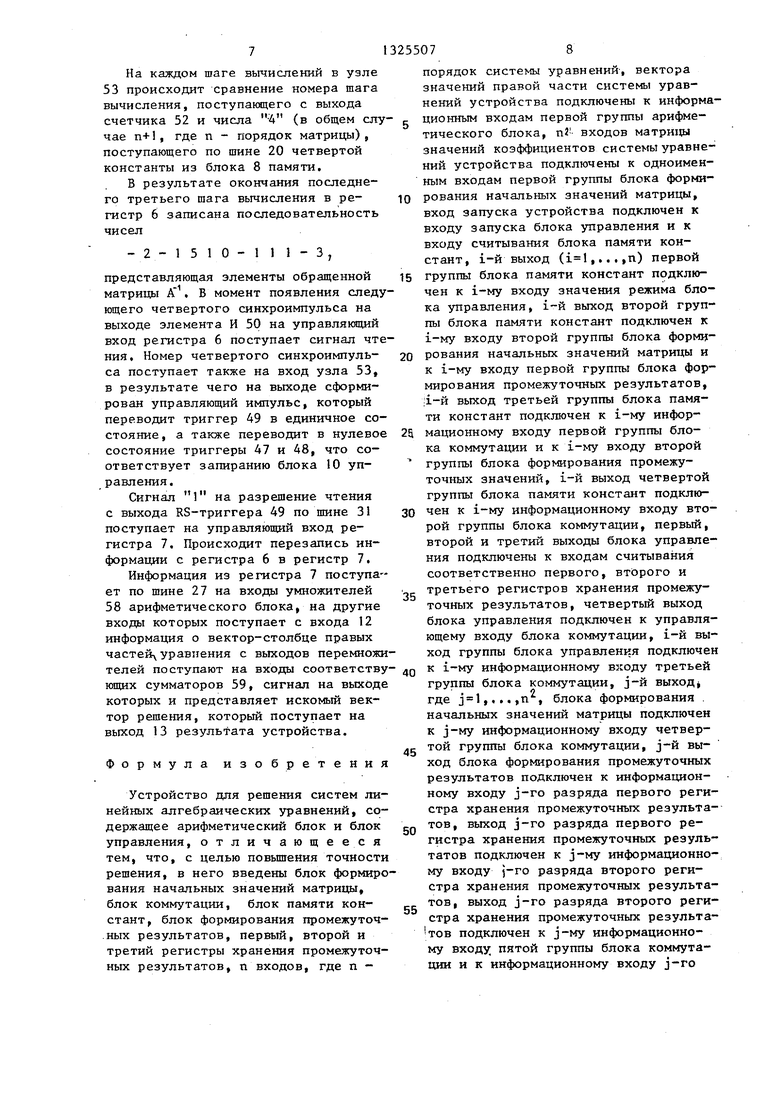

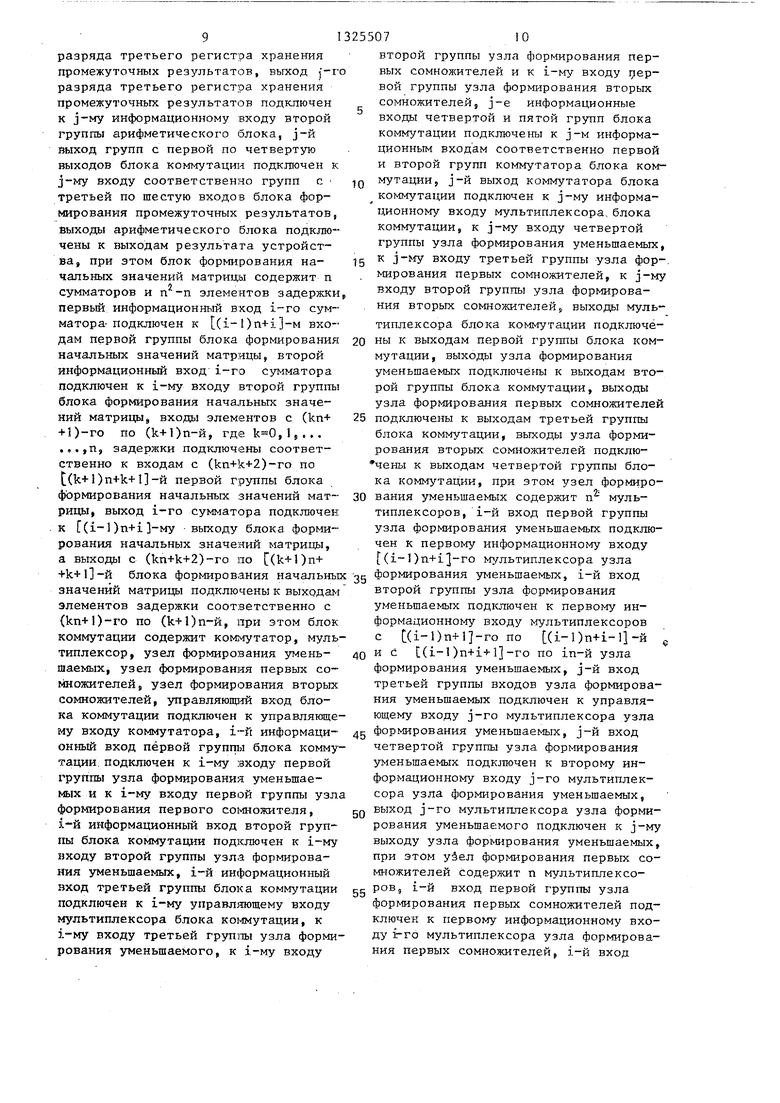

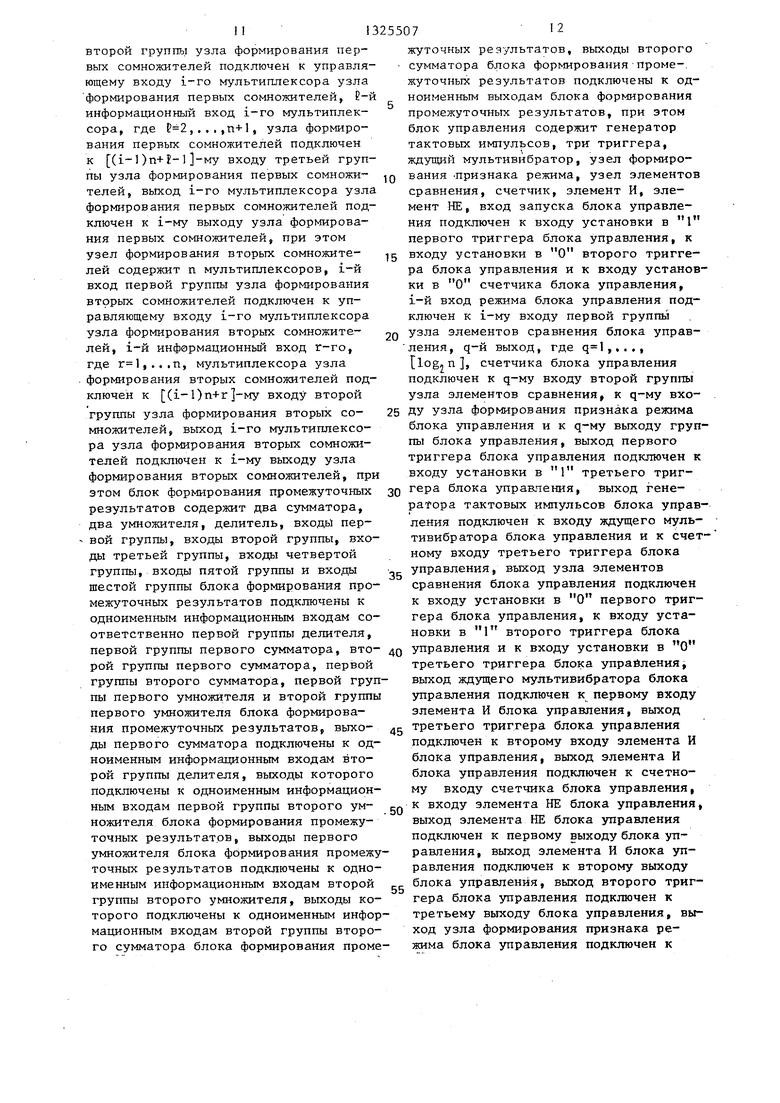

На фиг. 1 представлена структурная схема устройства; на фиг, 2 - блок формирования начальных значений матрицы; на фиг. 3 - блок коммутации; на фиг, 4 - блок формирования промежуточных результатов; на фиг, 5 - 15 блок управления; на фиг, 6 - узел формирования уменьшаемых; на фиг, 7- узел формирования первых сомножителей; на фиг, 8 - узел формирования вторых сомножителей; на фиг, 9 - узел формирования признака режима; на фиг. 10 - арифметический блок; на фиг. 11 - временная диаграмма работы блока управления.

Устройство содержит вход 1 запуска устройства, блок 2 формирования начальньк значений матрицы, блок 3 коммутации, блок 4 формирования прошаемых содержит п/ мультиплексоров 55. Узел 37 формирования первых сомножителей содержит п мультиплексоров 55 о Узел формирования вторых сомножителей содержит п. мультиплексоров 55. Узел 54 формирования признака ре- режима содержит элементов НЕ 565 где Р riog.jn, элемент И-НЕ 57. Арифметический блок 9 содержит умножитель 58 и сумматоры 59,

Устройстззо предназначено для решения системы линейных алгебраических уравнений вида

20

25

АХ В,

где А - матрица коэффициентов размерности пхп, состоящая из элементов a.j (, п., , n);

В - вектор-столбец размерности п, составленный из элементов правых частей Ь ;

X - вектор-столбец решения размерности п, составленный из элементов х- ,

Эта система при det А 7 О имеет для любых правых частей уравнений однозначно определенное решение

межуточных результатов, с первого по

Х(х, , , ., jX,,) , Для отыскания этого - третий рех истры 5-7 хранения промежу- зо вектор-решения воспользуемся обратной точных результатов, блок 8 памяти кон- матрицей А , В этом случае вектор- стант, арифметический блок 9, блок решение -В вычисляется простым 10 управления, вход I1 матрицы значений коэффициентов си:сте 1ы линейных алгебраических уравнений, вход 12 вектора значений правой части системы линейных алгебраических уравнений.

перемножением матриц.

Для отыскания обратной матрицы А 35 реализован гшгоритм обращения матрицы, согласно которому для вычисления матрицы необходимо провести вычисления матриц: А - , ,,, , ...., где А-Е, а Е - единичная матрица и

выход 13 результата устройства, внутренние информационные шины 14-27, выходы 28-31 блока управления.

Блок 2 формирован:ия н ачальных значений содержит элементы 32 задержки и сумматоры , Блок 3 коммута- .ции содержит коммутатор 34, мультиплексор 35, узел 36 формирования уменьшаемых, узел 37 формирования первых сомножителей, узел 38 формирования вторых сомножителей, внутреннюю информационную шину 39. Блок 4 формирования промежуточных результатов содержит два сумматора 40 и 41, два умножителя 42 и 43, делитель 44, Блок 10 управления содерясит генератор 45 тактовых импульсов, ждушдй мультивиб

Устройство на примере решения сисратор 46, с первого по третий тригге- темы линейных алгебраических уравне- ра 47-49, элемент И 50, элемент НЕ 51, ний третьего порядка работает следую- счетчик 52, узел 53 элементов срав- щим образом,

нения, узел 54 формирования признака|

режима. Узел 36 формирования умень- Пусть исходная система имеет вид

10

15

3255072

шаемых содержит п/ мультиплексоров 55. Узел 37 формирования первых сомножителей содержит п мультиплексоров 55 о Узел формирования вторых сомножителей содержит п. мультиплексоров 55. Узел 54 формирования признака ре- режима содержит элементов НЕ 565 где Р riog.jn, элемент И-НЕ 57. Арифметический блок 9 содержит умножитель 58 и сумматоры 59,

Устройстззо предназначено для решения системы линейных алгебраических уравнений вида

АХ В,

где А - матрица коэффициентов размерности пхп, состоящая из элементов a.j (, п., , n);

В - вектор-столбец размерности п, составленный из элементов правых частей Ь ;

X - вектор-столбец решения размерности п, составленный из элементов х- ,

Эта система при det А 7 О имеет для любых правых частей уравнений однозначно определенное решение

Х(х, , , ., jX,,) , Для о вектор-решения воспол матрицей А , В этом с решение -В вычис

перемножением матриц.

Х(х, , , ., jX,,) , Для отыскания этого - вектор-решения воспользуемся обратной матрицей А , В этом случае вектор- решение -В вычисляется простым

Для отыскания обратной матрицы А реализован гшгоритм обращения матрицы, согласно которому для вычисления матрицы необходимо провести вычисления матриц: А - , ,,, , ...., где А-Е, а Е - единичная матрица и

ш

.

1 т.

cf(i

i

. 10.

m j m 3 j

(i, j, in l,n).

Устройство на примере решения сисы линейных алгебраических уравне- третьего порядка работает следую- образом,

х Ь

2х + x,2+3xj 2b2 X, + Xj + X, 2b

3

т.е. AX В,

/1 2 где А I 2 1 3 1 - матрица коэффици 1 1 1 / ентов системы;

В (1 22)- вектор-столбец

правых частей сие

темы.

Исхо дный вектор-столбец поступает через вход 12 в арифметический блок 9, а исходная матрица в виду последовательности ее элементов, полученная разложением по строкам: 121213111 поступает на вход блока Z, где из диагональных элементов матрицы вычитается единица, поступающая по шине 16 первой константы из блока 8 памяти констант. На выходе блока 2 сформирована последовательность чисел

0212031 10,

Последовательность чисел с выхода коммутатора 34 поступает на вход бло ка 37, на выходе которого на первом шаге сформирована следующая последо- вательность чисел

30

которая по шине 18 поступает на информационные входы блока 3, в частности на входы коммутатора 34.

Работа устройства синхронизируется блоком 10 управления и начинается подачей сигнала на вход 1 устройства. При зтом устанавливается в нуль счетчик 52, устанавливаются в нулевое состояние RS-триггер 49, а в единичное состояние RS-триггер 47 Перевод RS-триггера 48 в единичное состояние происходит в момент-появления на его счетном входе тактового импульса от генератора 45 тактовых 40 на вход сумматора 40, где складыва- импульсов. В результате с выхода RS- ется с единицей, поступающей по шине ,триггера 48 единица поступает на один 14 второй константы блока 8, преоб- из входов эленента И 50, обеспечивая разуя в обратную величину, и умножа35

12.

Кроме того, последовательность чи сел по шине 39 также поступает на вход блока 38, на выходе которого на первом шаге вычислений появляется по следовательность чисел

021.

По шине 22 с выхода мультиплексора 35 число О на первом шаге поступает

прохождение синхроимпульсов, поступающих на второй ее вход от ждущего мультивибратора 46. С выхода злемента И 50 синхроимпульсы поступают на счетный вход счетчика 52. Период следования синхроимпульсов выбирается .из .условия полного завершения одного шага вычислений.

На первом шаге вычисления с выхода счетчика 52 поступает в двоичном коде 1 на шину 19 управления и на вход блока 54, в соответствии с законом paботы которого на его выходе на первом шаге сформирован О. На всех последующих шагах на выходе 28 присутствует 1. С выхода коммутатора 34 передана

13255074

последовательность чисел с шины 18 при сигнале на выводе 28, рапном О (первый шаг вычислений), или последовательность чисел с шины 17 при сигнале на выводе 28, равном 1, т.е. на первом шаге на выходе коммутатора 34 выдается последовательность чисел

021203110,

которая по шине 39 поступает на входы мультиплексора 35 и блоков 36 - 38.

К выходу блока 35 подключена шина, номер диагонального злемента которой совпадает с номером шага вычислений переданного по шине 19 управления из блока 10 управления. На первом шаге на шину 22 передано число 0. Последовательность чисел по шине 39 поступд- ет на вход блока 36, на выходе которого сформирована на первом -шаге последовательность чисел

1002031 10.

Последовательность чисел с выхода коммутатора 34 поступает на вход блока 37, на выходе которого на первом шаге сформирована следующая последо- вательность чисел

на вход сумматора 40, где складыва- ется с единицей, поступающей по шине 14 второй константы блока 8, преоб- разуя в обратную величину, и умножа

12.

Кроме того, последовательность чисел по шине 39 также поступает на вход блока 38, на выходе которого на первом шаге вычислений появляется последовательность чисел

021.

По шине 22 с выхода мультиплексора 35 число О на первом шаге поступает

ется на 1, поступающую по шине 16 первой константы. В итоге на первом шаге с выхода блока 44 поступает число -1 . I

С выходов блока 37 и блока 38 по шинам 24 и 25 последовательность чисел поступает на входы блока 2, где произвЬдится их взаимное перемножение, в результате чего на выходе на первом шаге сформирована последовательность чисел

021042021,

которая с выхода блока 42 поступает на вход блока 3, в котором все числа последовательности умножаются на

51325507

исло, поступающее с выхода блока 44,

в э си ти з к х н т в в з г н вы ш

в результате этого на первом шаге с выхода блока 43 выдана последоватепь- ность чисел

0-2-10-4-20-2-1,

которая складывается в соответствии с номерами с последовательностью чисел, поступающей по шине 23, в суьма- торе41, на выходе которого на первом шаге сформирована последовательность чисел

1-2-12-411-1-}.

Данная последовательность чисел с шины 26 поступает на входы регистра 5 хранения промежуточных результатов, который служит для хранения развязки между собой шагов вычи:слений .и устранения эффекта гонок. Во время вы- числения на каком-либо шаге на регистр 5 по выводу 29 поступает управляющий сигнал О с вьххода элемента И 50 блока управления, разрешающий запись информации в данный регистр,

021203110

021203110

100203110

t 2 I

О 2 t

- 1

021042021

021203110 1-2 12-4 1-1-1

Ь2- 10Ш1-1- 2 t - 1

2-41 1 3

-48-22-41-24в то время как по входу 30 на регистр 6 поступает управляющий сигнал 1, разрешающий чтение информации из этого регистра. Период следования синхроимпульсов с выхода ждущего мультивибратора 46 выбирается таким образом, что за время существования низкого перепада напряжения на его выходе полностью завершаются вычисления на данном шаге и запись результата в регистр 5, При появлении высокого по- тешдиала на выходе элемента И 50 на вход регистра 5 поступает 1, а на второй - О, т.е. происходит перезапись информации из первого регистра во второй. При появлении следзтаще- го синхроимпульса вьщается разрешение на чтение результата из регистра 6 и на запись результата следующего шага вычисления в регистр 5, Количество шагов вычислений равно порядку обращаемой матрицы.

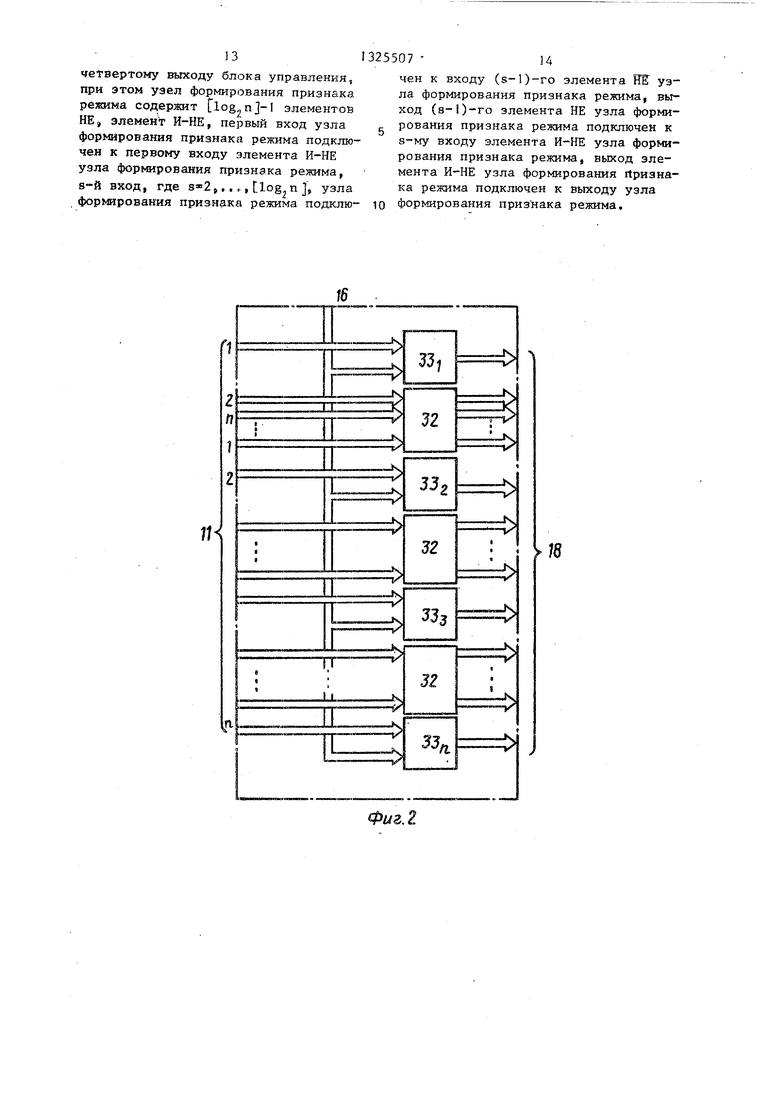

Результаты вычислений на выходах отдельных блоков для каждого шага приведены в таблице.

021203110

5 5 20 I 1 411 4

5 5 20 I 1 4,. , 3 3 З 3 3 з

-2-15Ш-П1-3 -2-1510-111-3 -2-11510-111-3

На каждом шаге вычислений в узле 53 происходит сравнение номера шага вычисления, поступанидего с выхода счетчика 52 и числа Ч (в общем случае п+1, где п - порядок матрицы), поступающего по шине 20 четвертой константы из блока 8 памяти,

В результате окончания последнего третьего шага вычисления в регистр 6 записана последовательность чисел

- 2 - 1 5 1 О - 1 1 1 - 3,

представляющая элементы обращенной матрицы А . В момент появления следующего четвертого синхроимпульса на выходе элемента И 50 на управляющий вход регистра 6 поступает сигнал чтения. Номер четвертого синхроимпульса поступает также на вход узла 53, в результате чего на выходе сформирован управляющий импульс, который переводит триггер 49 в единичное состояние , а также переводит в нулевое состояние триггеры 47 и 48, что соответствует запиранию блока 10 управления.

Сигнал 1 на разрешение чтения с выхода RS-триггера 49 по пшие 31 поступает на управляющий вход регистра 7, Происходит перезапись информации с регистра 6 в регистр 7,

Информация из регистра 7 поступает по шине 27 на входы умножителей 58 арифметического блока, на другие входы которых поступает с входа 12 информация о вектор-столбце правых частей уравнения с выходов перемножителей поступают на входы соответствующих сумматоров 59, сигнал на выходе которых и представляет искомый вектор решения, который поступает на выход 13 результата устройства.

Формула изобретения

Устройство для решения систем линейных алгебраических уравнений, содержащее арифметический блок и блок управления, отличающееся тем, что, с целью повьштения точности решения, в него введены блок формирования начальных значений матрицы, блок коммутации, блок памяти констант, блок формирования промежуточ- .ных результатов, первый, второй и третий регистры хранения промежуточных результатов, п входов, где п

5

0

5

0

5

0

5

0

5

порядок системы уравнений, вектора значений правой части системы уравнений устройства подключены к информационным входам первой группы арифметического блока, nJ- входов матрицы значений коэффициентов системы уравнений устройства подключены к одноименным входам первой группы блока формирования начальных значений матрицы, вход запуска устройства подключен к входу запуска блока управления и к входу считывания блока памяти констант, i-и выход (,,..,п) первой группы блока памяти констант подключен к i-му входу значения режима блока управления, выход второй группы блока памяти констант подключен к i-му входу второй группы блока формирования начальных значений матрицы и к 1-му входу первой группы блока формирования промежуточных результатов, 1-й выход третьей группы блока памяти констант подключен к i-му информационному входу первой группы блока коммутации и к i-му входу второй группы блока формирования промежуточных значений, i-й выход четвертой группы блока памяти констант подключен к i-му информационному входу второй группы блока коммутации, первый, второй и третий выходы блока управления подключены к входам считывания соответственно первого, второго и третьего регистров хранения промежуточных результатов, четвертый выход блока управления подключен к управляющему входу блока коммутации, i-й выход группы блока управления подключен к i-му информационному входу третьей группы блока коммутации, j-й выход где ,,,.,n , блока формирования . начальных значений матрицы подключен к j-му информационному входу четвертой группы блока коммутации, j-й выход блока формирования промежуточных результатов подключен к информационному входу j-ro разряда первого регистра хранения промежуточных результатов, выход j-ro разряда первого регистра хранения промежуточных результатов подключен к j-му информационному входу )-го разряда второго регистра хранения промежуточных результатов, выход j-ro разряда второго регистра хранения промежуточных результа- тов подключен к j-му информационному входу пятой группы блока коммутации и к информационному входу j-ro

разряда третьего регистра хранения промежуточных результатов, выход j-ro разряда третьего регистра хранения промежуточных результатов подключен к информационному входу второй группы арифметического блока, j-й выход групп с первой по четвертую выходов блока коммутации подключен к j-му входу соответственно групп с третьей по шестую входов блока формирования промежуточных результатов, Выходы арифметического блока подключены к выходам результата устройства, при этом блок формирования начальных значений матриад содержит п сумматоров и элементов задержки первый информационный вход i-ro сумматора- подключен к t(i-) входам первой группы блока формирования начальных значений матрицы, второй информационный вход i-ro сумматора подключен к i-му входу второй группы блока формирования нача.пьньпс значений матрицыJ входы элементов с (kn+ +)-го по (k+l)n-й, где ,l,,,. ,,.,п, задержки подключены соответственно к входам с (kn+k+2)-ro по t(k+l) первой группы блока формирования начальных значений матрицы, выход i-ro сумматора подключен к (i-1) выходу блока формирования начальных значений матрицы, а выходы с (kn+k+2)-ro по (k+l)n+

32550710

второй группы узла формирования первых сомножителей и к i-му входу rjep- вой группы узла формирования вторых сомножителей, j-e информационные входы четвертой и пятой групп блока коммутации подключены к j-м информационным входам соответственно первой и второй групп коммутатора блока мутации, j-й выход коммутатора блока коммутации подключен к j-му информационному входу мультиплексора, блока коммутации, к j-му входу четвертой группы узла формирования уменьшаемых,

15 входу третьей группы узла фор-, мирования первых сомножителей, к j-му входу второй группы узла формирования вторых сомножителей 5 выходы мультиплексора блока коммутации подключе20 ны к выходам первой группы блока коммутации, выходы узла формирования уменьшаемых подключены к выходам второй группы блока коммутации, выходы узла формирования первых сомножителей

25 подключены к выходам третьей группы блока коммутации, выходы узла формирования вторых сомножителей подклю- чены к выходам четвертой группы блока коммутации, при этом узел формиро30 вания уменьшаемых содержит п мультиплексоров, i-й вход первой группы узла формирования уменьшаемых подключен к первому информационному входу t(i-l) М}шьтиплексора узла

блока формирования начальных 35 Формирования уменьшаемых, i-й вход значений матрицы подключены к выходам второй группы узла формирования

уменьшаемых подключен к первому информационному входу ьгультиплексоров

Элементов задержки соответственно с (kn+l)-ro по (k+l)n-й, при этом блок коммутации содержит комз 1утатор, мультиплексор, узел формирования уменъ- шаемых, узел формирования первых сомножителей, узел формирования вторых: сомножителей, управляющий вх-од блока коммутации подключен к управляющес (i-I) по (i-l)п+i-ll-й 40 и е C(i-l )n+i-s-1 -го по in-й узла формирования уменьшаемых, j-й вход третьей группы входов узла формирования уменьшаемых подключен к управляющему входу j-ro мультиплексора узла

му входу коммутатора, i-й информаци- 45 Формирования уменьшаемых, j-й вход онный вход первой группы блока комму- четвертой группы узла формирования

к

тации. подключен к i-му входу первой группы узла формирования уменьшаемых и к i-My входу первой группы узла формирования первого сог шожителя, i-й информационный вход второй группы блока коммутации подключен к i-му входу второй группы узла формирования уменьшаемых, i-й информацион1Шй вход третьей группы блока коммутации подключен к i-му управл)те)щему входу мультиплексора блока ко1«1мутации, к 1-му входу третьей грзптш узла формирования уменьшаемого, к i-му входу

ВО

уменьшаемых подключен к второму информационному входу j-ro мультиплексора узла формирования уменьшаемых, выход j-ro мультиплексора узла формирования уменьшаемого подключен к j-му выходу узла формирования уменьшаемых, при этом у5ел формирования первых сомножителей содерлдат п мультиплексо- gg ров, i-й вход первой группы узла

формирования первых сомножителей подключен к первому информационному входу i-ro мультиплексора узла формирования первых сомножителей, i-й вход

с (i-I) по (i-l)п+i-ll-й и е C(i-l )n+i-s-1 -го по in-й узла формирования уменьшаемых, j-й вход третьей группы входов узла формирования уменьшаемых подключен к управляющему входу j-ro мультиплексора узла

к

О

уменьшаемых подключен к второму информационному входу j-ro мультиплексора узла формирования уменьшаемых, выход j-ro мультиплексора узла формирования уменьшаемого подключен к j-му выходу узла формирования уменьшаемых, при этом у5ел формирования первых сомножителей содерлдат п мультиплексо- g ров, i-й вход первой группы узла

формирования первых сомножителей подключен к первому информационному входу i-ro мультиплексора узла формирования первых сомножителей, i-й вход

II1325507 2

второй группы узла формирования пер-жуточных результатов, выходы второго

вых сомножителей подключен к управля- сумматора блока формирования Проме-.

ющему входу i-ro мультиплексора узлажуточных результатов подключены к од формирования первых сомножителей, 2-йпоименным выходам блока формирования

информационный вход i-ro мультиплек-промежуточных результатов, при этом

сора, где ,.,.,n+l, узла формиро-блок управления содержит генератор

вания первых сомножителей подключентактовых импульсов, три триггера,

к (i-l) входу третьей груп-ждущий мультивибратор, узел формиропы узла формирования первых сомножи- Qвания признака режима, узел элементов

телей, выход i-ro мультиплексора узласравнения, счетчик, элемент И, элеформирования первых сомножителей под-мент НЕ, вход запуска блока управлеключен к i-му выходу узла формирова-кия подключен к входу установки в 1

ния первых сомножителей, при этомпервого триггера блока управления, к

узел формирования вторых сомножите- gвходу установки в О второго триггелей содержит п мультиплексоров, i-йра блока управления и к входу установвход первой группы узла формированияки в О счетчика блока управления,

вторых сомножителей подключен к уп-i-й вход режима блока управления подравляющему входу i-ro мультиплексораключен к i-му входу первой группы

узла формирования вторых сомножите- QУзла элементов сравнения блока управ- лей, i-й информационный вход г-го, ления, q-й выход, где ,,.,,

где ,...п, мультиплексора узла log. п, счетчика блока управления

формирования вторых сомножителей под-подключен к q-му входу второй группы

ключен к (i-l) входу второйузла элементов сравнения, к q-му вхо группы узла формирования вторых со- 25ДУ Узла формирования призна;ка режима

множителей, выход i-ro мультиплексо-блока управления и к q-му выходу групра узла формирования вторых сомножи-пы блока управления, выход первого

телей подключен к i-му выходу узлатриггера блока управления подключен к

формирования вторых сомножителей, привходу установки в } третьего тригэтом блок формирования промежуточных ЗО блока управления, выход генерезультатов содержит два сумматора,pafopa тактовых импульсов блока управдва умножителя, делитель, входы пер-ления подключен к входу ждущего муль- вой группы, входы второй группы, вхо-тивибратора блока управления и к счет- ды третьей группы, входы четвертойному входу третьего триггера блока группы, входы пятой группы и входы .,управления, выход узла элементов шестой группы блока формирования про-сравнения блока управления подключен межуточных результатов подключены кк входу установки в О первого триг- одноименным информационным входам со-гера блока управления, к входу уста- ответственно первой группы делителя,новки в 1 второго триггера блока первой группы первого сумматора, вто- доуправления и к входу установки в О рой грзгапы первого сумматора, первойтретьего триггера блока управления, группы второго сумматора, первой груп-выход ждущего мультивибратора блока пы первого умножителя и второй группыуправления подключен к первому входу первого умножителя блока формирова-элемента И блока управления, выход ния промежуточных результатов, выхо- 5третьего триггера блока управления ды первого сзгмматора подключены к од-подключен к второму входу элемента И ноименным информационным входам вто-блока управления, выход элемента И рой группы делителя, выходы которогоблока управления подключен к счетно- подключены к одноименным информацион-му входу счетчика блока управления, ным входам первой группы второго ум- CQк входу элемента НЕ блока управления, ножителя блока формирования промежу-выход элемента НЕ блока управления точных результатов, выходы первогоподключен к первому выходу блока уп- умножителя блока формирования промежу-равления, выход элемента И блока уп- точных результатов подключены к одно-равления подключен к второму выходу именным информационным входам второй сблока управления, выход второго триг- группы второго умножителя, выходы ко-гера блока управления подключен к торого подключены к одноименным инфор-третьему выходу блока управления, вы- мационным входам второй группы второ-ход узла формирования признака ре- го сумматора блока формирования проме-жима блока управления подключен к

13

четвертому выходу блока управления, при этом узел формирования признака режима содержит элементов НЕ, элемент И-НЕ, первый вход узла формирования признака режима подклю чен к первому входу элемента И-НЕ узла формирования признака режима, 8-й вход, где ,,.„,tlogj п J, узла формирования признака режима подклю

1325507 -14

чен к входу (s-l)-ro элемента HF узла формирования признака режима, выход (8-1)-го элемента НЕ узла форми- g рования признака режима подключен к 8-му входу элемента И-НЕ узла формирования признака режима, выход элемента И-НЕ узла формирования Признака режима подключен к выходу узла 10 формирования приз нака режима.

Фиг. 2

Фи.3

1 16

34 в

25.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный процессор | 1985 |

|

SU1354204A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1985 |

|

SU1277128A1 |

| Ассоциативный матричный процессор | 1990 |

|

SU1795467A1 |

| Многоканальный коммутатор | 1988 |

|

SU1538244A1 |

| Система коммутации процессоров | 1984 |

|

SU1242977A1 |

| Устройство для операций над матрицами | 1990 |

|

SU1737461A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для сопряжения многопроцессорной вычислительной системы с внешними устройствами | 1984 |

|

SU1241245A2 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

Изобретение относится к вычислительной технике и может быть использовано автономно или в комплексе с ЦВМ для решения систем линейJT ных алгебраических уравнений. Цель изобретения - увеличение точности решения. Поставленная цель достигается тем, что устройство содержит вход 1 запуска устройства, блок 2 формирования начальных значений матрицы, блок 3 коммутации, блок 4 формирования промежуточных результатов, регистры 5-7 хранения промежуточных результатов, блок 8 памяти констант, арифметический блок 9, блок 10 управления, вход 11 матрицы значений коэффициентов, вход 12 вектора значений правой, части системы уравнений, выход 13 результата устройства. Увеличение тофюсти обеспечивается для случаев, когда элементы матрицы уравнения имеют величины различного порядка. 11 ил. с S (Л оо ю ел СП

И t г Hj,

39 фи,е

391

Фиг.7

3

Z5,

ФигЗ

2

гФ31 55

56

9

55

57

и

Фие.9

9U2.11

Составитель В. Смирнов Редактор Н. Бобкова Техред И.Попович Корректор Т, Колб

I «Illl ИИ I (

Заказ 3112/46 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полигра ческое предприятие, г. Ужгород, ул. Проектная, 4

1325507

27

fPuz. 10

| Устройство для решения системлиНЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU805336A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровое устройство для решения системы линейных уравнений | 1976 |

|

SU624234A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-23—Публикация

1984-11-22—Подача