памяти, выходы которого подключены . к информационным входам блока: фикса ции номеров вычисляемых функций, первая группа выходов которого соединена с входами второго элемента ИЛИ, вторая группа, выходов с первой . группой управляющих входов регистра новых значений выходных сигналов, третья группа выходов . с информаци онными входами второго блока памяти, выходы которого соединены с третьей группой информационных входов операционного блока,, информационный выход которого подключен к информационным входам регистра новых значений выходных сигналов, с первой по одиннадцатую группы выходов блока синхронизации подключены соответственно к второй группе управляющих входов регистра новых значений выходных сигналов и к управляющим входам блока буферных регистров, регистра новых значений входных сигналов, регистров старых значений входных и выходных сигналов регистров измененных состояний входны и выходных сигналов, первого и второго сумматоров по модулю два, блока фиксации номеров вычисляемых функций операционного блока, первый и второй управляющие входы блока синхронизации подключены соответственно к выходам первого и.второго элементов ИЛИ, группа управляющих входов блока синхронизации соединена с группой управляющих выходов операционного блока, причем операционный блок содержи элемент задержки, триггеры, схему сравнения, счетчик, дешифратор, регистр числа инструкций, регистры инструкций, регистры входных выходных и промежуточных переменных, регистр операций, дешифраторы адресов, дешифраторы признаков, группы элементов И, группы элементов ИЛИ, элементы И и ИЛИ, причем первая группа входов схемы сравнения соединена с выходами регистра числа инструкций выходы счетчика - с второй группой входов схемы сравнения и с входами дешифратора, а выход схемы сравне- йия - с первым входом первого элемента И, выход элемента И соединен с прямым установочным входом первого и вторым прямым установочным входом второго триггеров, второй инверсный установочный вход первого триггера через элемент задержки, инверсный установочный вход второго триггера.

первый инверсный установочный вход первого и первьгй прямой установочный вход второго триггеров, вход сброса и счетный вход счетчика, второй вход первого элемента И, первые входы элементов И с первой по четвертую группу, управляющие входы регистров входных и выходных значений соединены с группой управляющих входов операционного блока, выходы первого и второго триггеров соединены с группой управляющих выходов операционног блока, вторые входы элементов И первой группы соединены с выходами регистров инструкций, третьи - с выходом дешифратора, а вьпсоды - с входами элементов ИЛИ первой группы, выходы которых подключены к входам регистра операций, первого и второго дешифраторов адреса, выходы элементов И второй группы соединены с входами регистра входных переменньк, выходы элементов И третьей группы - с входами регистра выходных nepeмеиных, выходы элементов И четвертой группы - с входами регистра промежуточных переменных, вы ходы регистра входных переменных соединены с первыми входами элементов И пятой и шестой групп, выходы регистра выходных переменных соединены с первыми входами: элементов И седьмой и восьмой групп элементов И,. выходы регистра промежуточных переменных соединены с первыми входами элементов И девятой и десятой групп, вторые входы элементов И пятой, седьмой и девятой групп и элементов И шестой, восьмой и десятой групп соединены соответственно с выходами первого и второго дешифраторов адреса, выходы элементов И с пятой по десятую группы соединены соответственно с входами элементов ИЛИ с второй по седьмую группы , первые входы второго, третьего и четвертого элементов И соединены соответственно с выходами первого дешифратора.признака, а вторые входы - с выходами соответственно элементов ИЛИ, второй :четвертой и шестой групп, первые входы пятого, шестого и седьмого элементов И соединены с выходами второго дешифратора признаков, вторые входы соединены с выходами элементов ИЛИ соответственно третьей, пятой, седьмой групп, входы первого элемент ИЛИ соединены с выходами второго.

третьего и четвертого элементов И, прямой и инверсный выходы соединены с первыми входами соответственно восьмого и девятого элементов И, выходы которых соединены с входами второго элемента ИДИ, входьг третьего элемента ИЛИ соединены с выходами пятого, шестого.и седьмого элементов И, прямой и инверсный выходы с первыми входами соответственно десятого и одиннадцатого элементов И, выходы которых соединены с входами четвертого элемента ИЛИ, первый вход пятого элемента ИЛИ соединен с выходом второго элемента ИЛИ, второй вход - с выходом четвертого элемента ИЛИ, выход - с первым входом двенадцатого элемента И, первый вход тринадцатого элемента И соединен с выходом второго элемента ИЛИ, второй вхсд с выходом четверто го элемента ИЛИ, выход тринадцатого 3JieMeHTa И соединен с первым вход

;Четь1рнадцатого элемента И, первый и второй входы шестого элемента ИЛИ со единены с выходами соответственно две-надцатого и четырнадцатого элементовИ, а выход шестого элемента ИЛИ.сов динен с первым входом пятнадцатого элемента И, второй вход которого соединен с группой у прав л яняцих входов операционного блока, прямой и инверс ный выходы первого разряда регистра операций соединены с вторыми входами

соответственно двенадцатого и четыр-. надцатого элементов И, прямой и ин версный выходы второго разряда регист ра операций соединены с вторыми вхо дами восьмого и девятого элементов И прямые выходы третьего и четвертого /.. разрядов регистра операций соединены с входами первого дешифратора призна ка прямой и инверсный выходы пятого, разряда - с вторыми входами соответ ственно десятого и одиннадцатого эле ментов И, прямые выходы шестого и седьмого разрядов с входами второго дешифратора признаков, вторые входы элементов И третьей группы соединены- ., с первой группой информационных входов операционного блока, вторые входы элементов И второй группы - с второй группой информационных входов операционного блока, входы регистра числа инструкций и регистров инструкций -с третьей группой информационных входов . операционного блока, вторые входы элементов И четвертой группы соеди- , нены с выходом дешифратора, третий вход - с выходом шестого элемента

ИЛИ, выход пятнадцатого элемента И соединен с информационньм выходом операционного блока.

2. Устройство по п. I, о т л и ч а ю щ е е .с Я тем, что блок фик сации номеров вычисляемых функций содержит первую и вторую группы триггеров, первую и вторую группы элементов И, группу элементов задержки, элемент ИЛИ, элемент задержки, причем вькод элемента ИЛИ соеднн н с инверсными установочными входами триггеров перарй группы, первые входы первых элементов И первой и второй групп соединены с группой управляющих входов блока, первые входы последуюоовс элемейтов И первой и второй групп соединетл с выхояам предьиущего элемента И первой группы, первый вход последнего элемента И второй группы соединен с выходом последнего элемента И первой группы, вторые входы элементов -И первой и второй групп соединены соответственно с инверсными и прямыми выходами триггеров второй группы прямые выходы триггеров второй группы соединены с первой группой выхо-

дов блока, прямые вькоды триггеров первой группы соединены с второй группой выходов блока, выхЬды элементов И второй группы соединешл с пряюлът установочными входами триггеров первой группы и третьей группой выходов блока, а через группу элементов задержки - с первыми инверсными ус- тановочными входами триггеров второй группы, пряюзк входы триггеров второй группы соединены сияформацион-

аамк входами блока, первый вход элемента ИЛИ через элемент задержки, второй вход злемента ИЛИ, вторые инверсные входы триггеров второй группы соединены с группой управляю щих входов блока., .

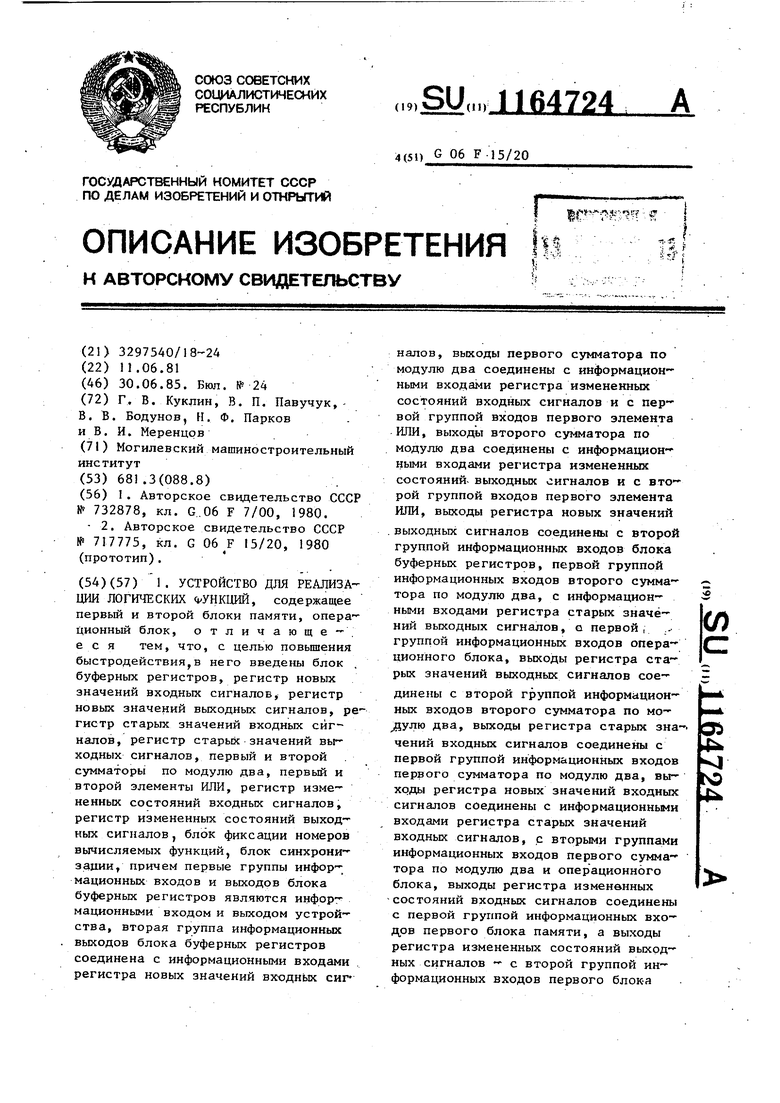

3. Устройство по п. i, отличающееся тем, что блок синхронизации содержит генератор импульсов, триггер, два элемента И, элемент задержки, генератор тактовых импульсов, два инвертора, группу элементов И, причем выход генератора импульсов соединен с первыми входами элементов И, второй вход первого элемента И соединен с прямым I выходом триггера, а выход через элемент задержки - с инверсным установоч ным входом триггера, второй вход второго элемента И соединен с инверсным выходом триггера, а выход - с входом генератора .тактовых импульсов, первый выход генератора тактовых импульсов соединен с первыми входами первого, четвертого, седьмого элементов И группы, торой выход - с первыми вхо дами второго, пятого, восьмого элементов И группы, третий выход с первыми входами третьего, шестого, девятого, десятого элементов И группы, второй вход четвертого элемента И группы соединен с первым управляющим входом блока синхронизации, вторые входы первого, второго, третьего элементов И группы через первый инвертор соединены с первым управляющим входом блока синхронизацииj|,вторые входы с пятого по девятый элементы И группы соединены с вторым управляющим входом блока синхронизации, третьи входы с первого по четвертый элементы И груп пы через второй инвертор соединены с вторыМ управляющим входом блока синхронизации, третьи входы пятого, шестого элементов И- группы и второй вход десятого -элемента И ГРУППЫ соединены с пепвым упоявляюшим входом группы, третьи входы , восьмого, девятого элементов И группы соединены с вторым управляющим входом группы, третий вход десятого элемента И группы соединен с третьим управляющим входом группы, первую группу выходов блока синхронизации образуют выходы первого элемента И и второго элемента И группы, вторую группу выходов выходы первого эле мента И, первого и третьего элементов И группы, третью группу выходов - вьг ходы первого элемента И и второго элемента И группы с четвертой по седь мую группы выходов выходы первого элемента И и четвертого элемента И группы, восьмую и девятую группы выходов -выходы первого элемента И, третьего и четвертого элементов И группы, десятую группу выходев - выходы первого элемента И,пятого и десятого элементов И группы,одиннадцатую группу вьгходов - выходы первого элемента И с пятого по десятый элементы И группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логических функций | 1983 |

|

SU1233160A1 |

| Устройство для реализации логических функций | 1983 |

|

SU1257658A2 |

| Устройство для вычисления систем логических функций | 1982 |

|

SU1269146A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Устройство для реализации логических алгоритмов | 1990 |

|

SU1778763A1 |

| Устройство для построения программируемых цифровых микропроцессорных систем | 2015 |

|

RU2616153C2 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| Мультипрограммное вычислительное устройство | 1990 |

|

SU1777147A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 2001 |

|

RU2207612C2 |

1. УСТРОЙСТВО ДЛЯ РЕАЛИЗАЦИИ ЛОГИЧЕСКИХ (t-YHKLUiE, содержащее первый и второй блоки памяти, операционный блок, отличающее, ее я тем, что, с целью повьппения быстродействия,в него введены блок . буферных регистров, регистр новых значений входных сигналов, регистр новых значений выходных сигналов, регистр старых значений входных сигналов, регистр старых значений вы ходных сигналов, первый и второй сумматоры по модулю два, первый и второй элементы ИЛИ, регистр измененных состояний входных сигналов, регистр измененных состояний выходных сигналов, блок фиксации номеров вычисляемых функций, блок синхронизации, причем первые группы информационных входов и выходов блока буферных регистров являются информационными входом и выходом устройства, вторая группа информационных выходов блока буферных регистров соединена с информационными входами регистра новых значений входных сигналов, выходы первого сумматора по модулю два соединены с информационными входами регистра измененных состояний входных сигналов и с первой группой входов первого элемента ИЛИ, выходы второго сумматора по модулю два соединены с информационными входами регистра измененных состояний, выходных сигналов и с второй группой входов первого элемента ИЛИ, выходы регистра новых значений .выходных сигналов соединены с второй группой информационных входов блока буферных регистров, первой группой информационных входов второго сумматора по модулю два, с информационными входами регистра старых значе(Л ний выходных сигналов, о первой, группой информационных входов операционного блока, выходы регистра старых значений выходных сигналов соединены с второй группой информационных входов второго сумматора по моСП ja,yiim два, выходы регистра старых зна-41 vj чений входных сигналов соединены с первой группой информационных входов ND первого сумматора по модулю два, выходы регистра новых значений входных сигналов соединены с информационньми входами регистра старых значений входных сигналов, с вторыми группами информационных входов первого сумматора по модулю два и операционного блока, выходы регистра измененных состояний входных сигналов соединены с первой группой информационных входов первого блока памяти, а выходы регистра измененных состояний выходных сигналов - с второй группой информационных входов первого блока

1

Изобретение относится к вычислительной технике и автоматике и может быть использовано для управления технологическими процессами, алгоритмы которых описываются логическими функциями, а также для моделирования цифровых устройств с целью их проверки и диагностики.

Известно устройство для реализации логических функций, которое содержит блок управления, блок памяти, блок приема команд, блок .ввода-вывода, таймер, буферный накопитель, маркировочную; память, блок регистровой памяти, операционный блок, блок фиксации результатов, первый и второй упра вляемые блоки инверти рования Q.

Наиболее близким по технической сущности к изобретению является устройству для моделировгшия конеч ньрс автоматов, содержащее два блока памяти, мультиплексор, два счетчика, коммутатор, сумматор по модулю два.

блок сравнения, блок вычисления бу левых функций, дешифратор служебных символов, регистр внутренних пере .менных, элемент задержки, дешифратор внутренних переменньк, регистр функций 2.

Недостатком известных устройств является сравнительно низкое быстродействие, поскольку при формировав НИИ выходных сигналов осуществляет- , ся вычисление всех без исключения функций, описывающих алгоритм работы моделируемого цифрового устройства.

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что в устройство, содержащее первый и второй блоки памяти, операционный блок, введены блок буферных регистров, регистр новых значений входных сигналов, регистр новых значений выходных сигналов, регистр старых зна.чений входныхсигналов, регистр старых значений выходных сигналов, пер3 . вый и второй сумматоры по модулю .Два, первый и второй элементы ИЛИ, регистр измененных состояний входных сигналов, регистр измененных состоя НИИ выходных сигналов, блок фиксации номеров вычисляемых функций, блок синхронизации, причем первые группы информационных входов и выходов блок буферных регистров являются информационными входом и выходом устройства вторая группа информационных выходов блока буферных регистров соединена с информационными входами регистра но вых значений входных сигналов, выхо- ды первого сумматора По модулю два соединены с информационными входами регистра измененных состояний вход ных сигналов и с первой группой входов первого элемента ИЛИ, выходы второго сумматора по модулю два соединены с информационными входами регистра измененных состояний выходных сигналов и с второй группой входов первого элемента ИЛИ, выходы регистра новых значений выходных сигналов соединены с второй группой информационных входов блока буфер ных регистров, первой группой информационных входов второго сумматора по модулю два, с информационными входами регистра старых значений выходных сигналов, с первой группой информационных входов операционного блока, выходы регистра старых зна ений выходных сигналов соединены с второй группой информационных входов второго сумматора по модулю два, выходы регистра старых значений входны сигналов соединены с первой группой информационных входов первого сумма- модулю два, выходы регистра новых значений входных сигналов соединены с информационными входами регистра старых значений входных сигналов, с вторыми группами инфррмационных входов первого сумматора по модулю два и операционного блока, выходы регистра измененных состояний входных .сигналов с-единены с первой группой информационных входов перво- го блока памяти, а выходы регистра измененных состояний выходных сигналов - с второй группой информационных входов первого блока памяти, выходы которого подключены к информа ционным входам блока фиксации номеров вычисляемых.функций, первая груп па выходов которого соединена с вхо- 244 дами второго элемента ИЛИ, вторая группа выходов - с первой группой управляющих входов регистра новых значений выходных сигналов, третья группа выходов - с информационными входами второго блока памяти, выходы которого соединены с третьей группой информационных входов операционного блока, информационный выход которого подключен к информационным входам регистра новых значений выходных сигналов , с первой по одиннадцатую группы выходов блока синхронизации подключены соответственно к второй группе управляющих входов регистра новых значений выходных сигналов и к управляющим входам блока буферных регистров, регистра новых значений входных сигналов, регистров старых значений входных и выходных сигналов, регистров измененных состояний входных и выходных сигналов, первого и второго сумматоров по модулю два, блока фиксации номеров вычисляемых функций, операционного блока, первый и второй управляющие входы блока синхронизации подключены соответственно к выходам первого и второго элементов ИЛИ, группа управляющих входов блока синхронизации соединена с группой уп- равлянщих выходов операционного , причем операционный блок содержит элемент задержки, триггеры,схему сравнения, , дешифратор, регистр числа инструкций, регистры инструкций, регистры входных, выходных и промежуточных переменных, регистр операций, дещифраторы адресов, дешифраторы признаков, группы элементов И, группы элементов ИЛИ, элементы И и ИЛИ, причем первая группа входов-схемы.сравнения соединена с выходами числа инструкций, выходы счетчика - с второй группой входов схемы сравнения и с входами дешифратора, а выход схемы сравнения - с первым входом первого элемента И, выход элемента И соединен с прямым установочным входом первого ц вторым прямым установочным вхоом второго триггеров,второй инверсный установочный вход первого триггера через элемент задержки, инверсный установочный вход второго триггера, первый инверсный установочный вход первого и первый прямой установочный вход iaTOporo триггеров, вход сброса и счетный вход счетчика, второй вход первого элемента И, пер1вые входы элементов И с. первой по четвертую группы, управляющие входы регистров входных и вькодных значений соединены с группой управляющих входов операционного блока, выходы первого и второго триггеров соединены с груп пой управляницих выходов операционно го блока, вторые входы элементов И первой группы соединены с выходами регистров инструкций, третьи с вы ходом дешифратора, а выходы с входами элементов ИЛИ первой группы, выходы которых подключены к входам регистра операций, первого и второго дешифраторов адреса, выходы элемен тов И второй группы соединены с входами регистра входных переменных, выходы элементов И третьей группы с входами регистра выходных переменных, выходы элементов И четвертой группы - с входами регистра промежуточных переменных, выходы регистр входных переменных соединены с первыми входами элементов И пятой и шестой группы, выходы регистра вы ходных переменных соединены с первыми входами элементов И седьмой и восьмой групп, выходы регистра промежуточных переменных соединены с первыми входами элементов И девятой и десятой групп, вторые входы элеме тов И пятой, седьмой и девятой груп и элементов И шестой, восьмой и дес той групп соединены соответственно выходами первого: и второго дешифрат ров адреса, выходы элементов И с пя той по десятую группы соединены соотве ственно с входами элементов ИЛИ с втор по седьмую групп, первые входы второго третьего и четвертого элементов И соед нены соответственно с. выходами перв го дешифратора признака, а вторые входы - с выходами соответственно элементов ИЛИ второй, четвертой и шестой групп, первые входы пятого, шестого и седьмого элементов И соединены с выходами второго дешифратора признаков, вторые входы соединены с выходами элементов ИЛИ соответственно третьей, пятой, седьмой .групп, входы первого элемента ИЛИ соединены с выходами второго, тре- тьего и четвертого элементов И, пря мой и инверсный выходы соединены с первыми входами соответственно вось мого и девятого-элементов И, выходы которых соединены с входами второго 1 4 элемента ИЛИ,входы третьего элемента ИЛИ соединены с выходами пятого, шестого и седьмого элементов И, прямой и инверсный выходы - с первыми вхо- Дами соответственно десятого и одиннадцатого элементов И, выходы кото- . рых соединены с входами четвертого элемента ИЛИ, первый вход пятого элемента ИЛИ соединен с выходом второго элемента ИЛИ, второй вход - с выходом четвертого элемента ИПИ, .выход - с. первым входом двенадцатого элемента И, первый вход тринадцатого элемента И соединен с выходом второго элемента, ИЛИ, второй вход - с выходом четвертого элемента ИЛИ, йыход тринадцатого элемента И соединен с первым входом четырнадцатого элемента И, первый и второй входы шестого элемента ИЛИ соединены с выходами соответственно двенадцатого и четырнадцатого элементов И, а выход шестого элемента ИЛИ соединен с первым входом пятнадцатого элемента И, второй вход которого соединен с группой управляющих входов операционного блока, прямой и инверсный выходы первого разряда регистра операций соединены с вторыми входами соответственно двенадцатого и четырнадцатого элементов И„ прямой и инвер сный выходы второго разреда регистра операций соединены с вторыми входами восьмог.о и девятого элементов И, прямые выходы третьего и четвертого разрядов регистра операций соединены с. входами первого дешифратора признака, прямой и инверсньш выходы пятого разряда - с вторыми входг1ми соответствен.но десятого и одиннадцатого элементов И, прямые выходы шестого и седьмого разрядов с входами второго дешифратора признаков, вторые входы элементов И третьей группы соединены с первой группой информационных входов операционного блока, вторые входы элементов И второй группы - с второй группой информационных входов операционного блока, входы регистра числа инструкций и регистров инструкций с третьей группой информационных входов операционного блока, вторые входы элементов И четвертой группы соединены с выходом дешифратора, третий вход - с выходом шестого элемента ИЛИ, выход пя тнадцатого элемента И соединен с информационным выходом операционного блока. Кроме того, блок фиксации номеров вычисляемых функций содержит первую и вторую группы триггеров, пер, вую и вторую группы элементов И, группу элементов задержки, элемент ИЛИ, элемент задержки, причем выход элемента ИЛИ соединен с инверсными установочными входами триггеров первой группы, ц ервые входы первых эле ментов И первой и второй групп соеди нены с группой управляющих входов блока, первые входы последующих элементов И первой и второй групп сое динены с выходом предьщущёго элемен та И первой группы, первый вход посЛеднего элемента И- второй группы соединен с выходом последнего элемеН та И первой группы, вторые входы элементов И первой и второй групп соединены соответственно с инверсны ми и прямыми выходами триггеров вто рой группы, прямые выходы триггеров второй группы соединены с первой группой выходов блока, прямые выходы триггеров первой группы соединены с второй группой выходов блока, выходы элементов И второй группы соединены с прямыми установочными входами трйг геров первой группы и третьей группой выходов , а через группу элементов задержки ;с первыми инвер ными установочными входами триггеров второй группы, прямые входы триггё ров второй группы соединены с информационными входами блока, первый вхо элемента ИЛИ через элемент задержки, второй вход элемента ИЛИ, вторые инверсные входы триггеров второй груп пы соединены с группой управляющих входов блока. Блок синхронизации содержит геНе ратор импульсов, триггер, два элемен та И, элемент задержки, генератор тактовых импульсов, два инвертора, группу элементов И, причем выход генератора импульсов соединен с первы ми входами элементов И, второй вход первого элемента И соединен с прямым выходом триггера, а выход через эле мент задержки - с инверсным устано вочным входом трИ1 ера, второй вход второго элемента И соединен с инверс ным выходом триггера, а выход с входом генератора тактовых импульсов первый вь1ход генератора тактовых импульсов соединен с первыми входами первого, четвертого, седьмого эле- ментов И группы, второй вьпсод - с первыми входами второго, пятого, восьмого элементов И группы, -третий 24 8 выход с первыми входами третьего, шестого, девятого, десятого элементов И группы, второй вход четвертого элемента И группы соединен с пер- вым управляющим входом блока синхронизации, вторые входы первого, второго, .третьего элементов И группы через первый инвертор соединены с пер вым управляющим входом блока синхронизации, вторые входы с пятого по девятый элементов И группы соединены с вторым управляющим входом блока синхронизации, третьи входы с первого по четвертый элементов И группы через второй инвертор соединены свторым управляющим входом блока синхронизации, третьи входы пятого, шестого элементов И группы и второй вход десятого элемента И группы соединены с первым управляющим входом группы, третьи входы седьмого, восьмого, девятого элементов И группы соединены с вторым управляющим вхо- . дом группы, третий вход десятого элемента И группы соединен с третьим управляющим входом группы, первую группу выходов блока синхронизации образуют выходы первого элемента И и второго элемента И группы, вторую группу выходов - выходы первого эле teHTa И, первого и третьего элемен- т OB и группы, третью группу выходов-- выходы первого элемента И и второго элемента И группы, с четвертой по седьмую группы выходов - выходы перв9го элемента И и четвертого элемента И группы, восьмую и девятую группы выходов - выходы первого элемента И, третьего и четвертого элементов И группы-, десятую группу выходов - выходы первого элемента И, пятого и десятого элементов И группы, одиннадцатую группу выходов - выходы первого элемента И и с пятог.о по.десятый элементов И группы. В устройстве вычисляются только те логические функции, в которые входят переменные, изменившие свои значения по сравнению с предыдущим шагом. Наличие регистров .старых и новых значений входных сигналов и регистров старых и новых значений выходных сигналов, двух блоков поразрядного сложения по модулю два, блока учета изменений входных и выходных сигналов и регистров измененных состояний входных и вы-

ходных сигналов позволяет осуществить обмен информацией с внешней средой, выявить наличие изменений вход ных и (или) выходных сигналовJ сфор мировать признак для обращения к вто рому блоку памяти.

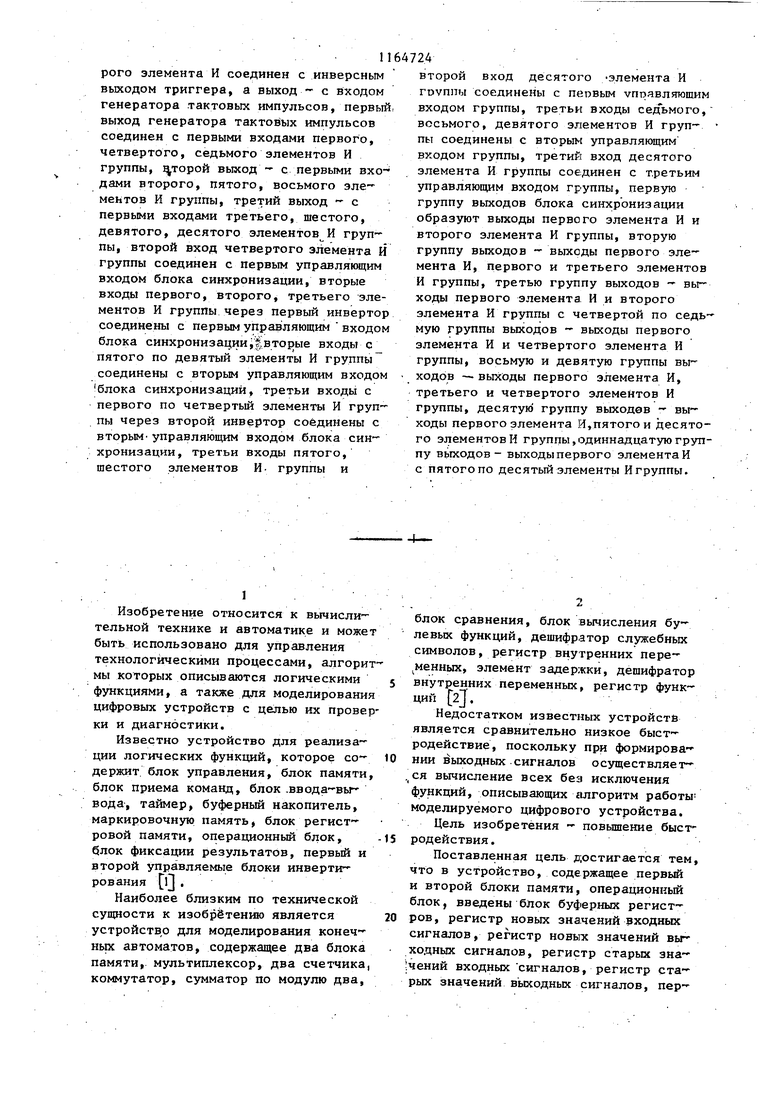

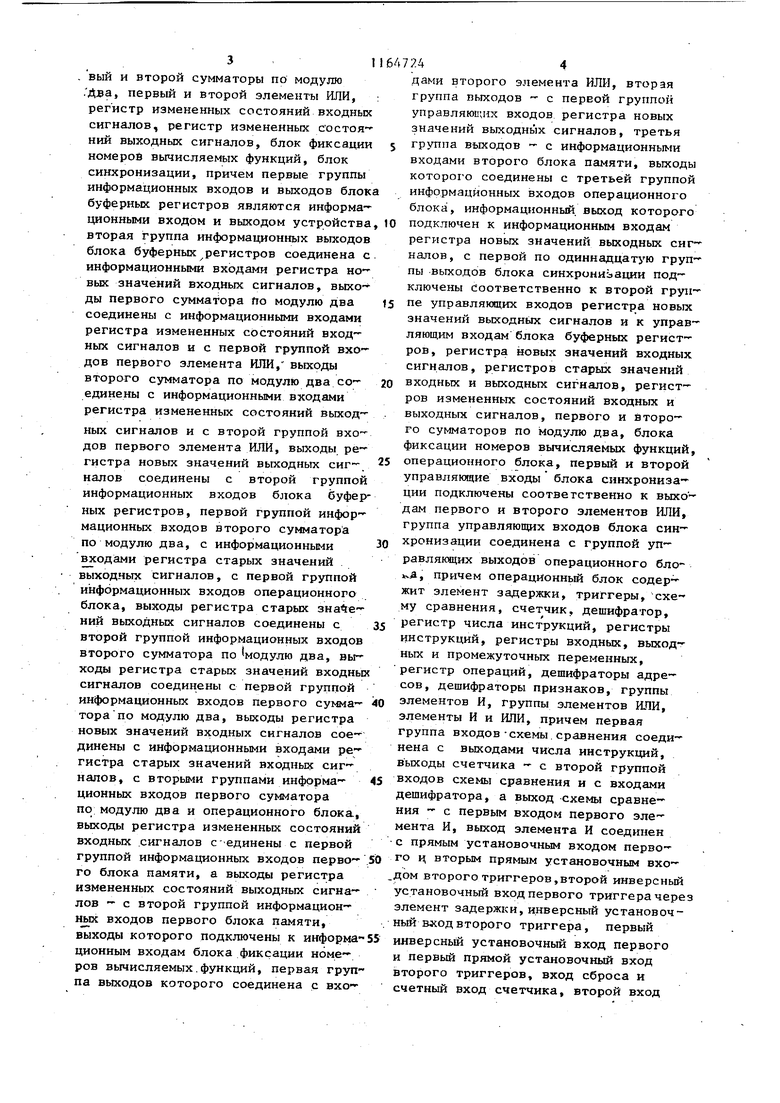

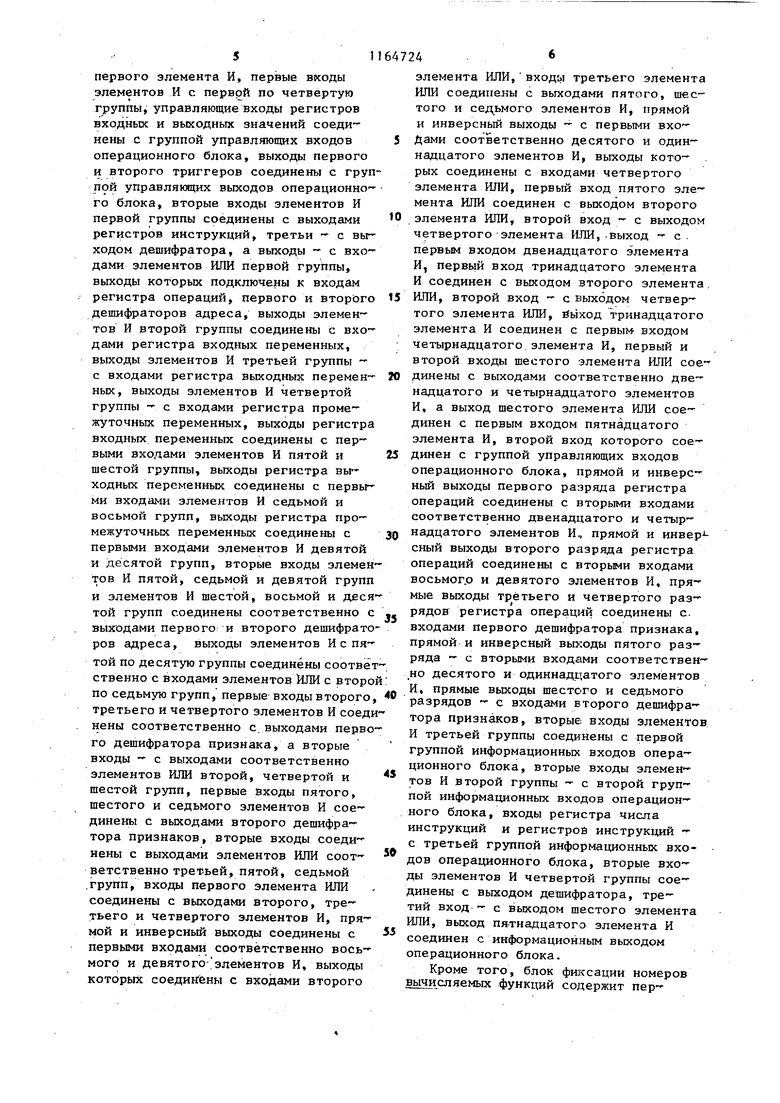

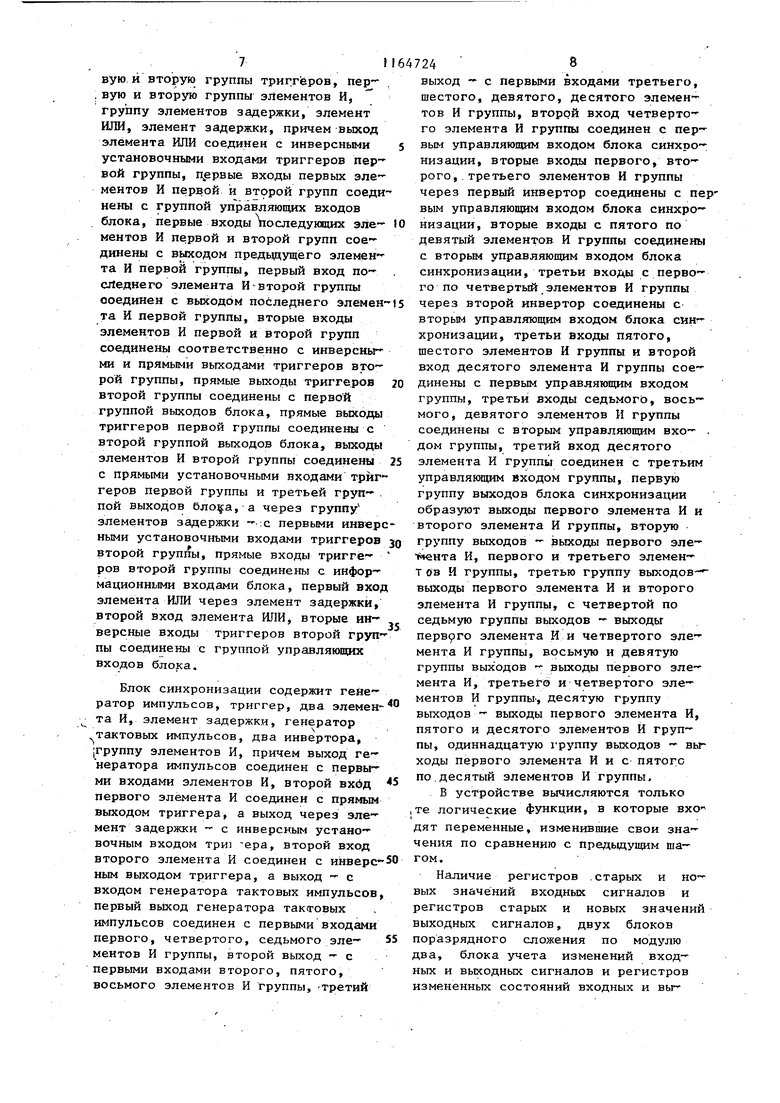

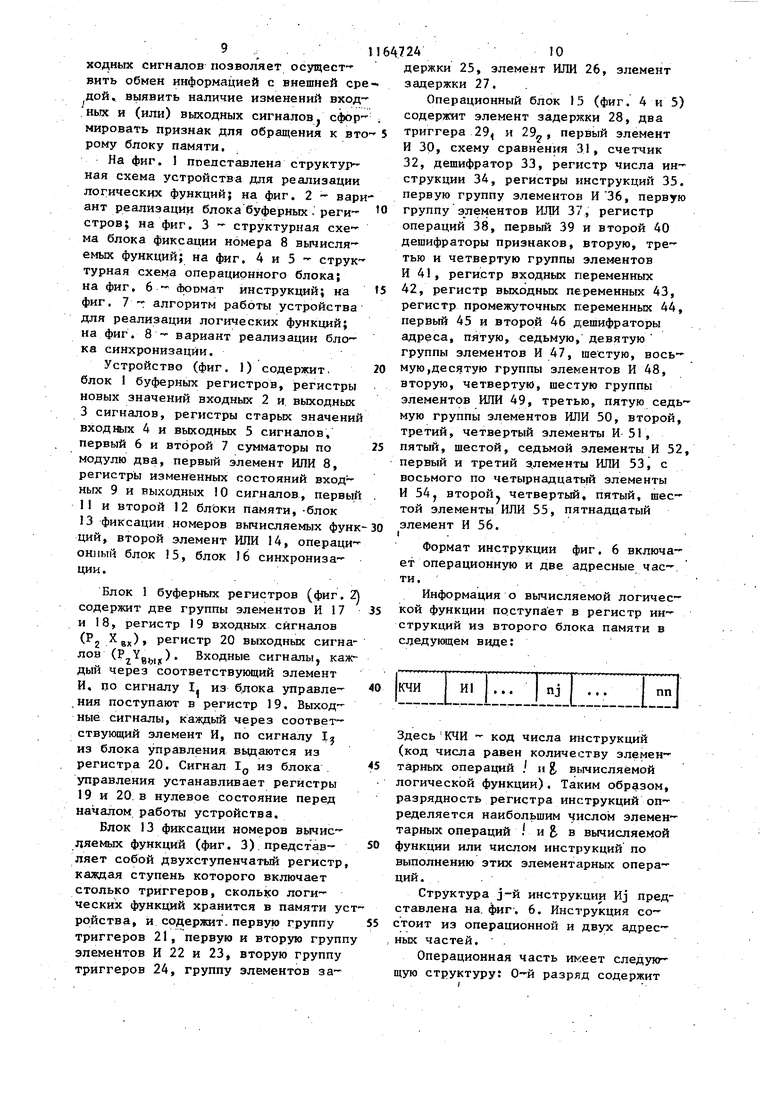

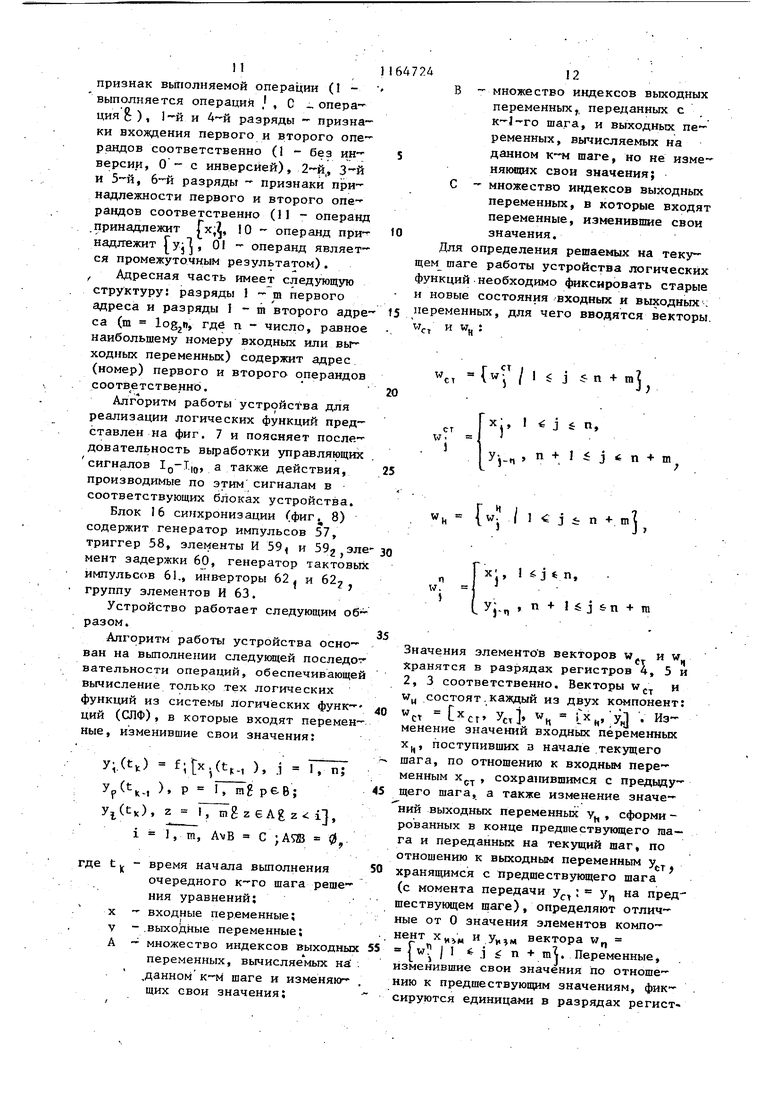

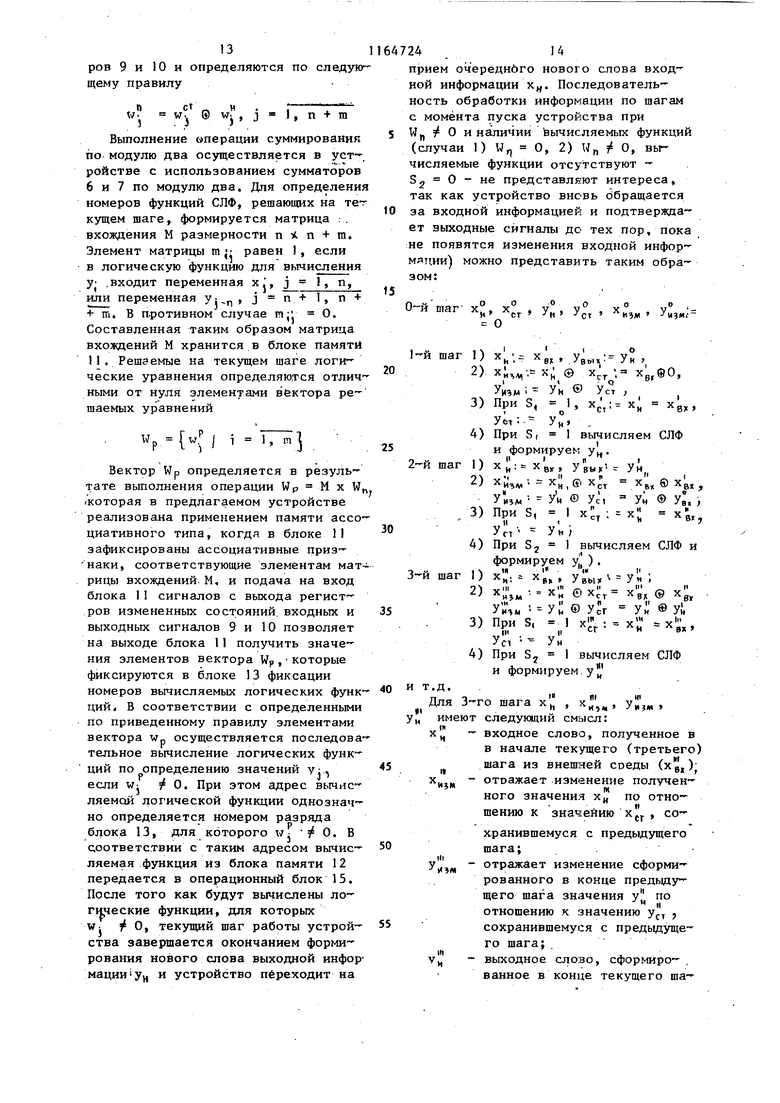

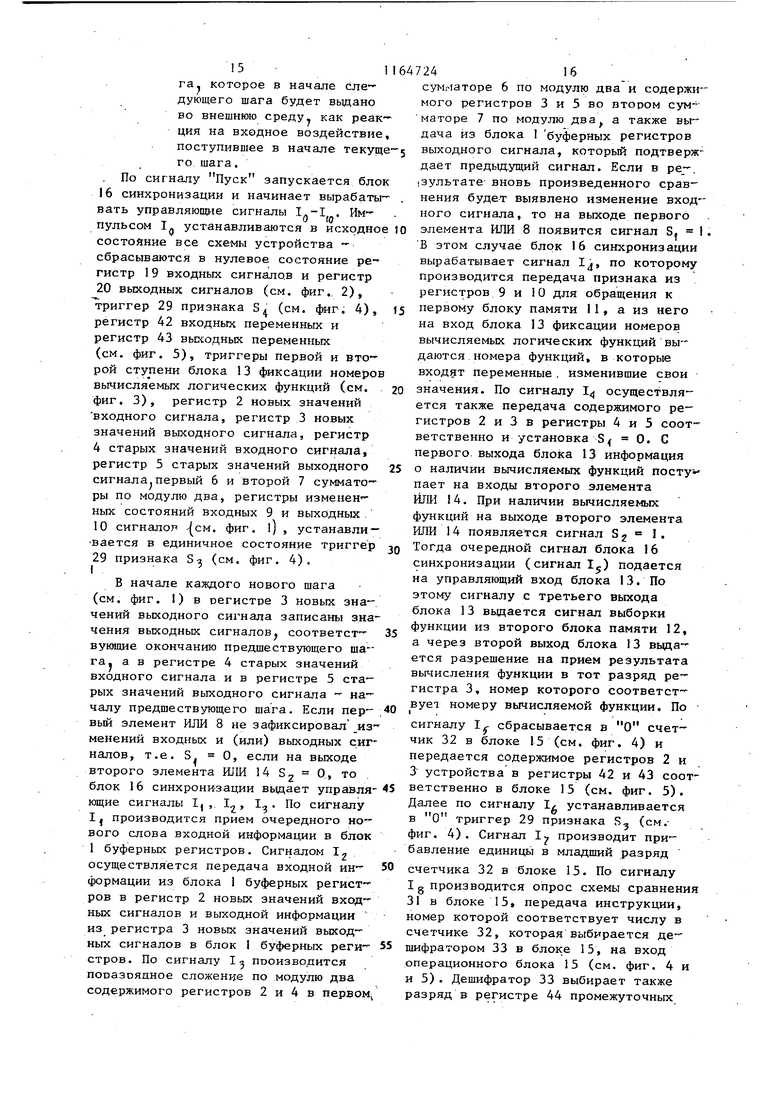

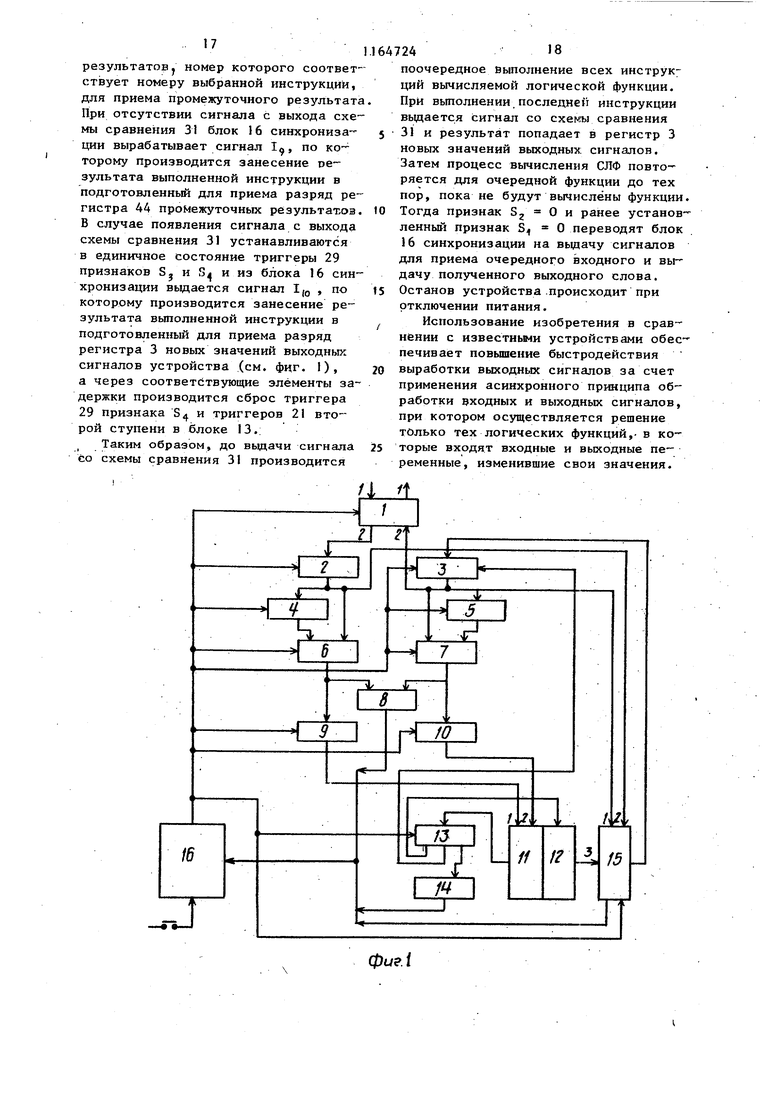

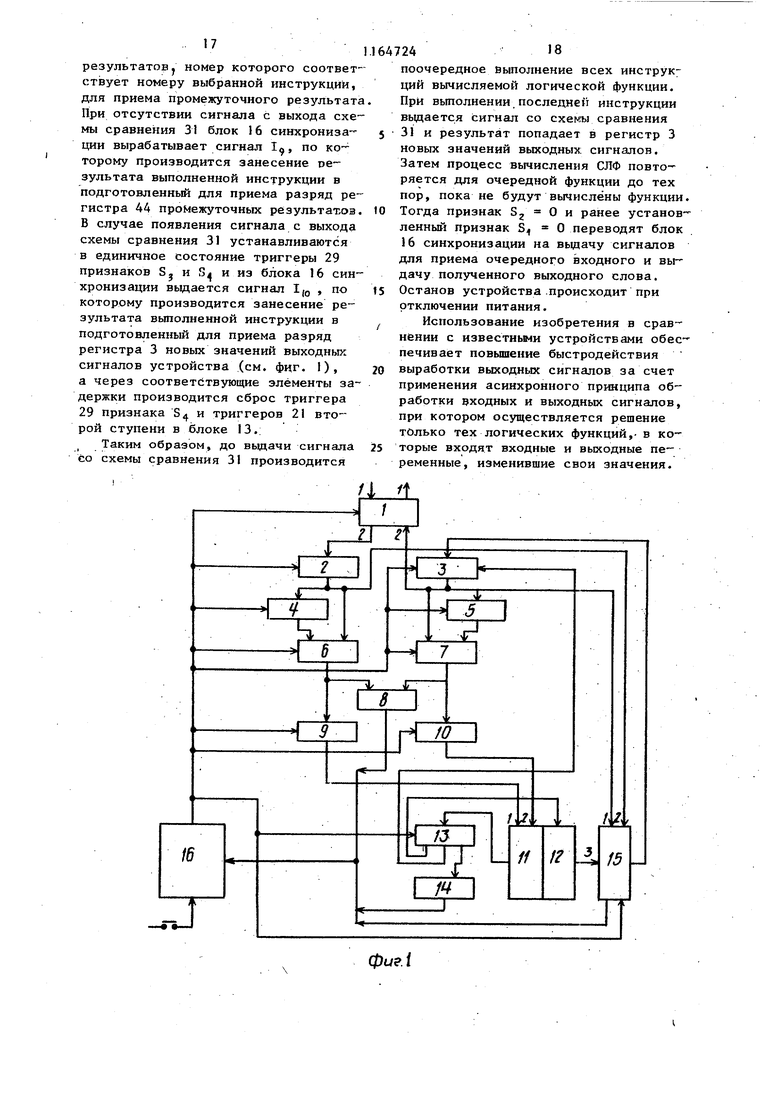

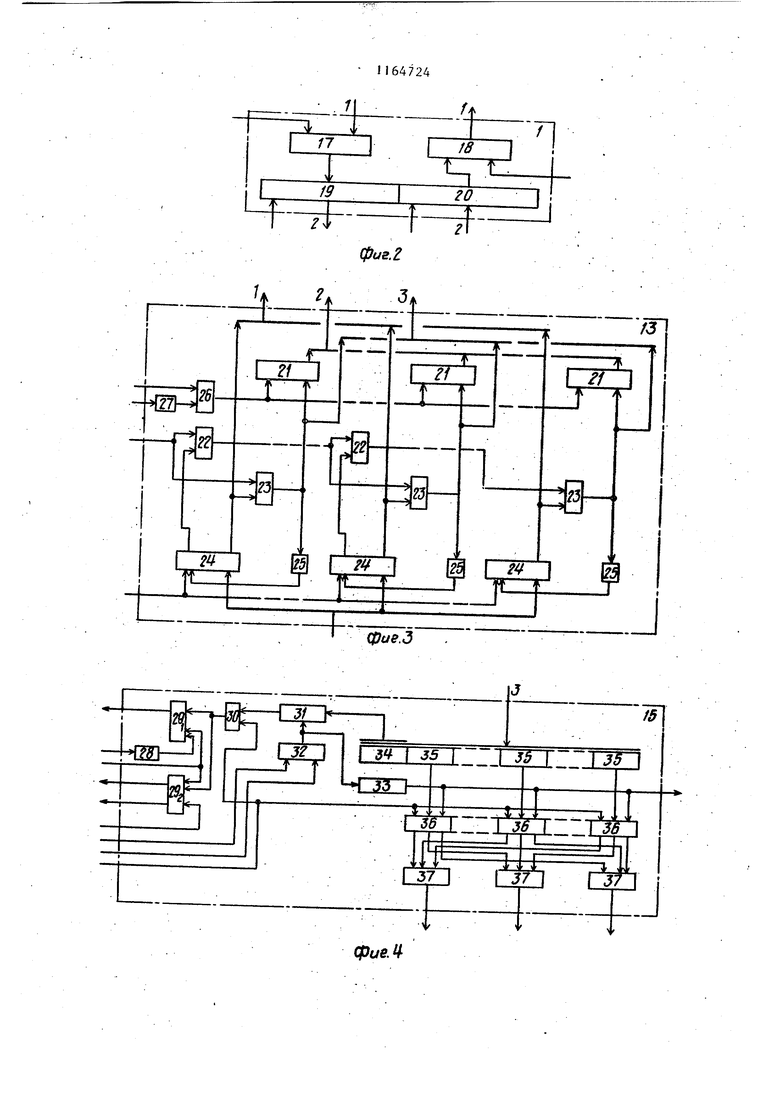

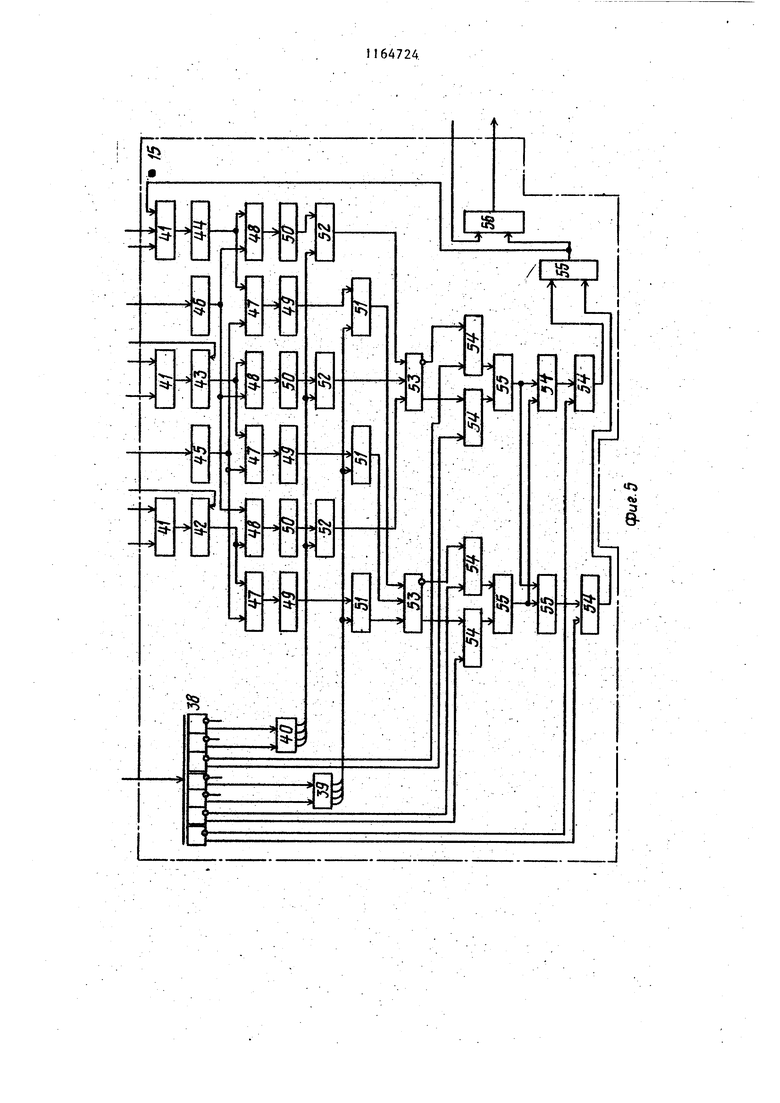

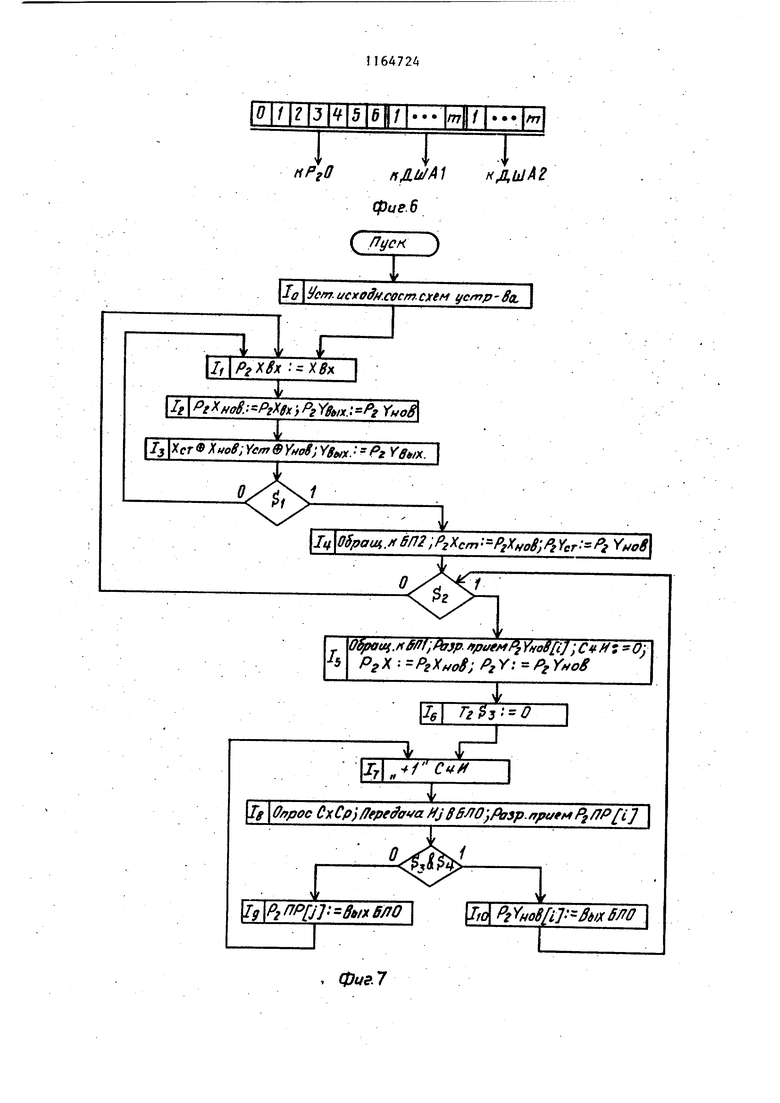

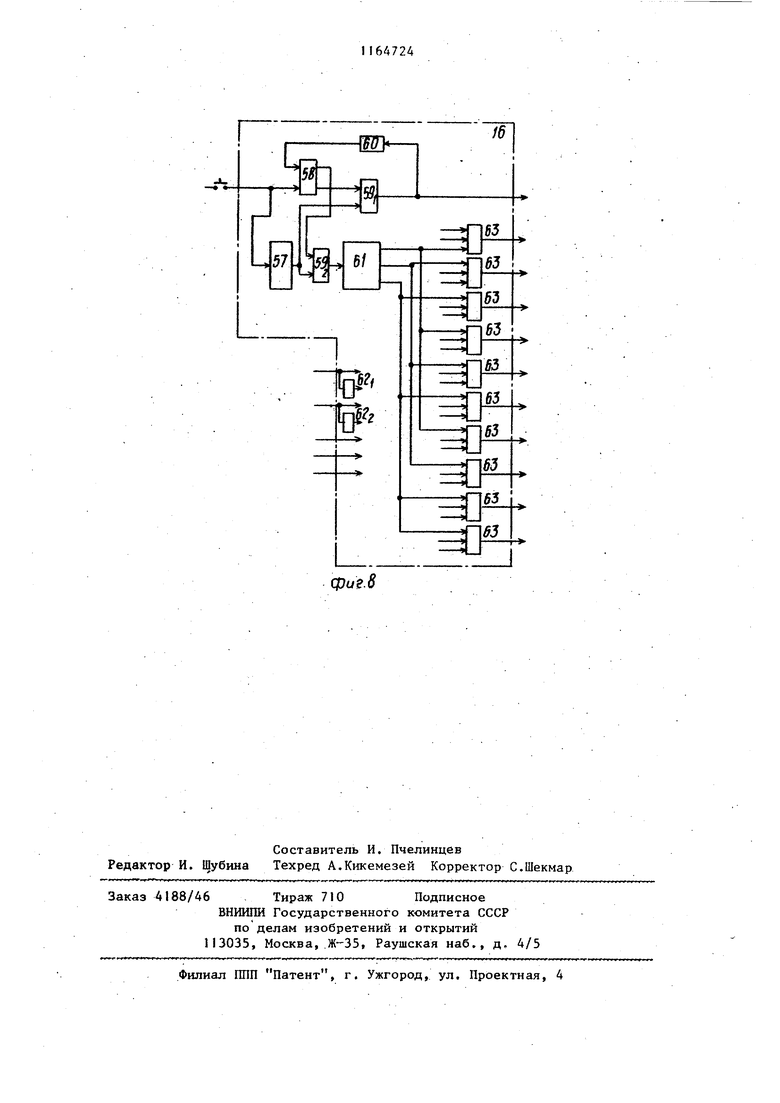

На фиг. 1 пгедставленя структур ная схема устройства для реализации логических функций; на фиг. 2 вариант реализации блока буферных - реги стров; на фиг. 3 структурная схе ма блока фиксации номера 8 вычисля емьк функций; на фиг. 4 и 5 - струк турная схема операционного блока; на фиг. 6 - 4юомат инструкций; на фиг, 7 Г алгоритм работы устройства для реализации логических функций; на фиг. 8 - вариант реализации блока синхронизации.

Устройство (фиг. 1) содержит, блок I буферных регистров, регистры новых значений входных 2 и выходных 3 сигналов, регистры старых значений входи 1х 4 и выходных 5 сигналов, первый 6 и второй 7 сумматоры по модулю два, первый элемент ИЛИ 8, регистры измененных состояний вход ных 9 и выходных 10 сигналов, первый II и второй 12 блоки памяти,-блок 13 фиксации номеров вычисляемых функций, второй элемент ИЛИ 14, операци ониый блок 15, блок 16 синхрониза ции.

Блок 1 буферных регистров (фиг. 2) содержит две группы элементов И 17 и 18, регистр 19 входных сигналов (Pj Xg), регистр 20 выходных сигналов (,,). Входные сигналы, каждый через соответствующий элемент И, по сигналу I. из блока управления поступают в регистр 19. Выход ные сигналы, каждый через соответ ствующий элемент И, по сигналу 1 из блока управления вьщаются из регистра 20. Сигнал Ig из блока управления устанавливает регистры 19 и 20. в нулевое состояние перед началом работы устройства.

Блок 13 фиксации номеров вычис ляемых функций (фиг. 3) представляет собой двухступенчатый регистр, каждая ступень которого включает столько триггеров, сколько логических функций хранится в памяти устройства, и содержит, первую группу триггеров 21, первую и вторую группу элементов И 22 и 23, вторую группу триггеров 24, группу элементов за72410

держки 25, элемент ИЛИ 26, элемент

задержки 27. .

Операционный блок 13 (фиг. 4 и 5) содеряя1т элемент задержки 28, два

триггера 29 и 29„, первый элемент И 30, схему сравнения 31, счетчик 32, дешифратор 33, регистр числа ин струкции 34, регистры инструкций 35. первую группу элементов И 36, первую

группу элементов ИЛИ 37, регистр операций 38, первый 39 и второй 40 дешифраторы признаков, вторую, третью и четвертую группы элементов И 41, регистр входных переменных

42, регистр выходньк переменных 43, регистр промежуточных переменных 44, первый 45 и второй 46 дешифраторы адреса, пятую, седьмую, девятую группы элементов И 47, шестую, восьмую,десятую группы элементов И 48, вторую, четвертую, шестую группы элементов ИЛИ 49, третью, пятую седьмую группы элементов ИЛИ 50, второй, третий, четвертый элементы И 51,

пятьп, шестой, седьмой элементы И 52, первый и третий э,лементы ИЛИ 53, с восьмого по четырнадцать элементы И 54, второйJ четвертый, пятый, шестой элементы ИЛИ 55, пятнадцатый

элемент И 56.

Формат инструкции фиг. 6 включает операционную и две адресные части.

Информация о вычисляемой логичес- кой функции по.ступает в регистр инструкций из второго блока памяти в следующем виде:

I И1 ... nj I ... I 1

кчи

ЗдесьКЧИ - код числа инструкций (код числа равен количеству элементарных операций . и вычисляемой логической функции). Таким образом, разрядность регистра инструкций определяется наибольшим числом элемен тарных операций .и 5- в вычисляемой

функции или числом инструкций по выполнению этих элементарных операций.

Структура j-й инструкции Иj представлена на. фиг. 6. Инструкция состоит из операционной и двух адрес. ных частей. .

Операционная часть Hw;eeT следующую структуру: О-й разряд содержит 11 признак выполняемой операции ( выполняется операция , , С опера ция ), Ни и А-й разряды признаки вхождения первого и второго опе рандов соответственно (1 - без ин версии, О - с инверсией), 2-й, З-й и З-й, 6--Й разряды - признаки принадлежности первого и второго oneрандов соответственно (П - операнд .принадлежит fx,, 10 операнд принадлежит Гу; 01 - операнд является промежуточным результатом). f Адресная часть имеет следующую структуру: разряды - m первого адреса и разряды 1 - m второго адре са (т , где п - число, равное наибольшему номеру входных или выходных переменных) содержит адрес. (номер) первого и второго операндов соответственно. Алгоритм работы устройства для реализации логических функций представлен на фиг, 7 и поясняет последовательность вьфаботки управляющих сигналов IQ-T.|(,, а также действия, производимые по этим сигналам в соответствующих блоках устройства. Блок 16 синхронизации (фиг. 8) содержит генератор импульсов 57, триггер 58, элементы И 59 и 592,эл мент задержки 60, генератор тактовы импульсов 6,, инверторы 62 и 622. группу элементов И 63. Устройство работает следующим об разом. Алгоритм работы устройства основан на выполнении следующей последо вательности операций, обеспечивающе вычисление только тех логических функций из системы логич1еских функ- ций (СЛФ), в которые входят перемен ные, изменившие свои значения: У;.(Ч) ,,., ), л 1, п; Р y(t), Z I, mgzeAgz i}, i 1, m, AvB С ;AOT 0, где t и - время начала выполнения очередного кто шага решения уравнений; X - входные переменные; V -.выходные переменные; А - множество индексов выходны переменных, вычисляемых н .данномк-й шаге и изменяющих свои значения; 2Д В - множество индексов выходных переменных,, переданных с к-1-го шага, и выходных переменных, вы ислнемых на данном к-м шаге, но не изменяющих свои значения; С - множество индексов выходных переменных, в которые входят переменные, изменившие свои значения. Для определения решаемых на текущем шаге работы устройства логических функций необходимо фиксировать старые и новые состояния входных и выходных : переменных, для чего вводятся векторы. Чт И „ : ст TW / 1 j П + mj xj, I j n, y-,-n , n + 1 i j t n + m I w. / 1 j ir n + m n , i w. . y- ,n+ $jfrn + m Значения элементов векторов w и w Хранятся в разрядах регистров 4, 5 и 2, 3 соответственно. Векторы w j состоят .каждый из двух компонент: w, х,, , w 1 и;Ун менение значений входных переменных х, поступивших 3 начале .текущего шага, по отношению к входным переменным Хр. , сохранившимся с предыдущего шага, а также изменение значений выходных переменных у , сформи рованных в конце предшествующего тага и переданных на текущий шаг, по отношению к выходным переменным у,. хранящимся с предшествующего шага (с момента передачи у ; у на предшествующем шаге), определяют отличные от О значения элементов компонент и вектора V7 Гw j п + т. Переменные, изменившие свои значения по отношению к предшествующим значениям, фиксируются единицами в разрядах регист13ров 9 и 10 и определяются по следую щаму правилу 1 , п + m 5 ) J . Выполнение операции суммирования по модулю два осуществляется в уст ройстве с использованием сумматоров 6 и 7 по модулю два. Для определени номеров функций СЛФ, решающих на тет кущем шаге, формируется матрица . . вхождения М размерности п п + га. Элемент матрицы m { равен , если в логическую функцию для вычисления У .входит переменная х , j 1, п, j 1, п + или переменная У: j п + + т. В противном случае т; Составленная таким образом матрица вхождений М хранится в блоке памяти 1.Решаемые на текущем шаге логические уравнения определяются отлич ными от нуля элементами вектора решаемых ур авнений w,P / 1 1, ш Вектор WP определяется в результате выполнения операции Wp М х W (Которая в предлагаемом устройстве реализована применением памяти ассо циативного типа, когда в блоке 11 зафиксированы ассоциативные приз- наки, соответствующие элементам мат рицы вхождений. М, и подача на вход блока I1 сигналов с выхода регистров измененных состояний, входных и выходных сигналов 9 и 10 позволяет на выходе блока 11 получить значения элементов вектора Wp,которые фиксируются в блоке 13 фиксации номеров вычисляемых логических функ ций В соответствии с определенными по приведенному правилу элементами вектора Wp осуществляется последова тельное вычисление логических функций по определению значений у:., если W- О. При этом адрес вычисляемой логической функции однозначно определяется номером разряда блока 13, для которого W; i О. В соответствии с таким адресом вычисляемая функция Из блока памяти 12 передается в операционный блок 15. После того как будут вычислены логические функции, для которых Wi ф О, текущий шаг работы устройства завершается окончанием формирования нового слова выходной инфор мацииу, и устройство переходит на 14 м очереднбго нового слова входинформации х„. Последователь ь обработки информации по шагам мента пуска устройства при О и наличии вычисляемых функций чаи 1) W О, 2) W ф О, выяемые функции отсутствуют о - не представляют интереса, как устройство вновь обращается ходной информацией и подтверждаыходные сигналы до тех пор, пока оявятся изменения входной инфори) можно представить таким обрааг- . х°, у, у , х°, шаг 1) .. х„ , у;,„: у„ , 2) х:,,-.х © х; xg,QO, yi,M - yh ® ; , 3)При S, J, х;,; х; XB,, yet: УН . 4)При S, 1 вычисляем СЛФ и формируем у. шаг 1) , Увь.х Уи,, 2) х;;,; х;;,® Хс% ,, УИЗМ Ум ® Ус1 Уи ® Ув, J 3) При S, 1 х, ; х-; УСТ У) 4) При Sj 1 вычисляем СЛФ и формируем yj, ) . шаг 1) х„., xJ, , Увых У«; 2),--- г- хв, ® х, УизА, - y|i ® Усг Ун ® У, 3)При S, I х , : х , „, сгив Ус1 - Ун 4)При Sj 1 вычисляем СЛФ и формируем, д. . ля 3-го шага х , х;;,, у, , имеют следующий смысл: - входное слово, полученное в в начале текутцего (третьего) шага из внешней соеды (xg, ) .,,.. - отражает изменение получен 1Кного значения х„ по отношению к значению Xjj. , сохранившемуся с предыдущего шага; . - отражает изменение сформированного в конце предыдущего шага значения yj по отношению к значению у , сохранившемуся с предыдущего шага; m. выходное слово, сформированное в конце текущего ша15га, которое в начале еле дующего шага будет вьщано во внешнюю среду, как реак ция на входное воздействие поступившее в начале текущ го шага, . По сигналу Пуск запускается бло 16 синхронизации и начинает вырабаты вать управляющие сигналы п,„- Им пульсом 1- устанавливаются в исходно состояние все схемы устройства сбрасываются в нулевое состояние ре- гистр 19 входных сигналов и регистр 20 выходных сигналов (см. фиг.. 2), -риггер 29 признака S (см. фиг. 4), регистр 42 входных переменных и регистр 43 выходных переменных (см. фиг. 5), триггеры первой и второй ступени блока 13 фиксации номеро вычисляемых логических функций (см. фиг. 3), регистр 2 новых значений входного сигнала, регистр 3 новых значений выходного сигнала, регистр 4 старых значений входного сигнала, регистр 5 старых значений выходного сигнала.первый 6 и второй 7 сумматоры по модулю два, регистры изменен ных состояний входных 9 и выходных . 10 сигналоя -|см. фиг. l , устанавли - вается в единичное состояние триггер 29 признака S (см. фиг. 4). В начале каждого нового шага (см. фиг. I) в регистре 3 новых значений выходного сигнала записаны зна чения выходных сигналов соответст- вуюшие окончанию предшествующего шага, а в регистре 4 старых значений входного сигнала и в регистре 5 старых значений выходного сигнала началу предшествующего шага. Если пер- вый элемент ИЛИ 8 не зафиксировал из менений входных и (или) выходных сиг налов, т.е. S. 0, если на выходе второго элемента ИЛИ 14 82 О., то блок 16 синхронизации выдает управля ющие сигналы I,, 1, 1. По сигналу II производится прием очередного нового слова входной информации в блок 1 буферных регистров. Сигналом 12 осуществляется передача входной ин- формации из блока 1 буферных регистров в регистр 2 новых значений входных сигналов и выходной информации из регистра 3 новых значений выходных сигналов в блок 1 буферных регистров. По сигналу 1 пооизводится пооазоядное сложение по модулю два содержимого регистров 2 и 4 в nepBOM 72416 сумматоре 6 по модулю два и содержи мого регистров 3 и 5 во втором сумматоре 7 по модулю два а также вы дача из блока 1 буферных регистров выходного сигнала, который подтверждает предыдущий сигнал. Если в . зультате- вновь произведенного срав нения будет выявлено изменение входного сигнала, то на выходе первого элемента ИЛИ 8 появится сигнал Sj I. В этом случае блок 16 синхронизации вырабатБ вает сигнал 1д, по которому производится передача признака из регистров 9 и 10 для обращения к первому блоку памяти II, а из него на вход блока 13 фиксации номеров вычисляемых логических функций выдаются номера функций, в которые входят переменные, изменившие свои значения. По сигналу 14 осуществляется также передача содержимого регистров 2 и 3 в регистры 4 и 5 соот ветственно и установка S О. С первого, выхода блока 13 информация о наличии вычисляемых функций посту пает на входы второго элемента ИЛИ 14. При наличии вычисляемых функций на выходе второго элемента ИЛИ 14 появляется сигнал S I. Тогда очередной сигнал блока 16 синхронизации (сигнал I) подается на управляющий вход блока 13. По этому сигналу с третьего выхода блока 13 выдается сигнал выборки функции из второго блока памяти 12, а через второй выход блока 13 выдается разрешение на прием результата вычисления функции в тот разряд регистра 3, номер которого соответствует номеру вычисляемой функции. По сигналу If сбрасывается в О счетчик 32 в блоке 15 (см. фиг. 4) и передается содержимое регистров 2 и 3 устройства в регистры 42 и 43 соответственно в блоке 15 (см. фиг. 5). ,f, ° сигналу 1 устанавливается в О триггер 29 признака S (см.фиг. 4). Сигнал 1 производит прибавление единицы в младший разряд счетчика 32 в блоке 15. По сигналу Ig производится опрос схемы сравнения 31 в блоке 15, передача инструкции, номер которой соответствует числу в счетчике 32, которая выбирается де- шифратором 33 в блоке 15, на вход операционного блока 15 (см, фиг. 4 и и 5) . Дешифратор 33 выбирает также разряд в регистре 44 промежуточных

17

результатовj номер которого соответствует номеру выбранной инструкции, для приема промежуточного результата При отсутствии сигнала с выхода схемы сравнения 31 блок 16 синхронизации вырабатывает сигнал 1, по которому производится занесение результата выполненной инструкции в подготовленный для приема разряд регистра 44 промежуточных результатов. В случае появления сигнала с выхода схемы сравнения 31 устанавливаются в единичное состояние триггеры 29 признаков Sj и 5 и из блока 16 синхронизации выдается сигнал I(Q , по которому производится занесение результата вьтолненной инструкции в подготовленный для приема разряд регистра 3 новых значений выходных сигналов устройства (см. фиг. I), а через соответствующие злёменты задержки производится сброс триггера 29 признака S и триггеров 21 второй ступени в блоке 13.:

Таким образом, до вьщачи сигнала со схемы сравнения 31 производится

248

поочередное выполнение всех инструкций вычисляемой логической функции. При выполнении.последней инструкции вьщается сигнал со схемы сравнения 3 и результат попадает в регистр 3 новых значений вькодных сигналов. Затем процесс вычисления СЛФ повто-ряется для очередной функции до тех пор, пока не будут вычислены функции.

Тогда признак S О и ранее установ ленный признак S О переводят блок 16 синхронизации на вьщачу сигналов для приема очередного входного и вы дачу полученного выходного слова.

Останов устройства .происходит ПРИ отключении питания.

Использование изобретения в сравнении с известньни устройствами обеспечивает повышение быстродействия

выработки выходных сигналов за счет применения асинхронного принципа обработки входных и выходных сигналов, при котором осуществляется решение только тех логических функций,- в которые входят входные и выходные переменные, изменившие свои значения.

/X /t

фиг/

фиг. г

LJL

г

ГЛ

H I

;5

J

фие.д

фиеЛ

«to

|g|/| 3| |5|g|/| H/| «h

I г

t PfOn ,0.11/A1

j/g I i/fm. ucxodff.cocm. cxtM ycmp - Sg,

1

1

-xfa I

Ii Pt Hi S:-P 4it;fi lKt. Уний

i

I /j Xcr P g Увш.

L OSpawj.ffSnZ.PzXcm-Р2 ноВ,РгУст- ов

j |%ygg CxCft)ffepet ff/aMJ8S O)flo3p./fpt/ff4P2nP i

Ig Р2ПР : ВшбЛО

, 7

I

ндшАг

фиг.6

1

Ie 0 I

S

Q .

Pz HoSliT edixS/fff

Авторы

Даты

1985-06-30—Публикация

1981-06-11—Подача