Изобретение относится к вычислительной технике и может быть использовано для функционального контроля двоичных линейных цифровых систем.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности контроля линейных цифровых блоков с произвольным количеством входов и выходов.

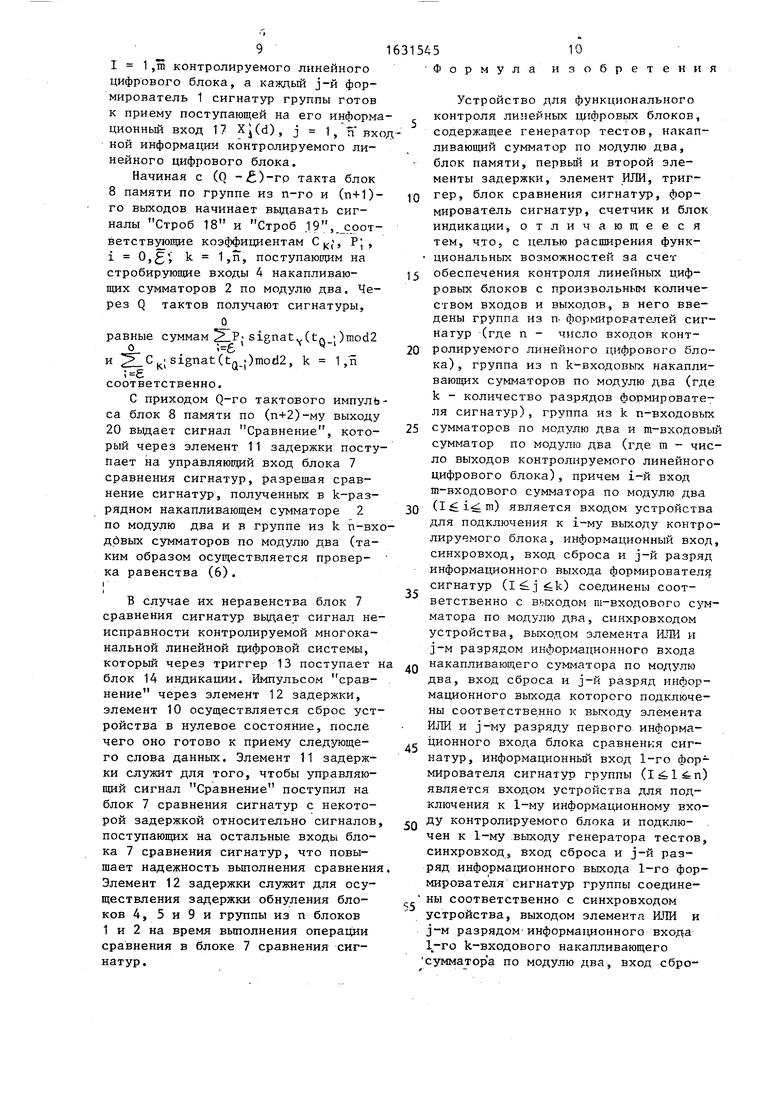

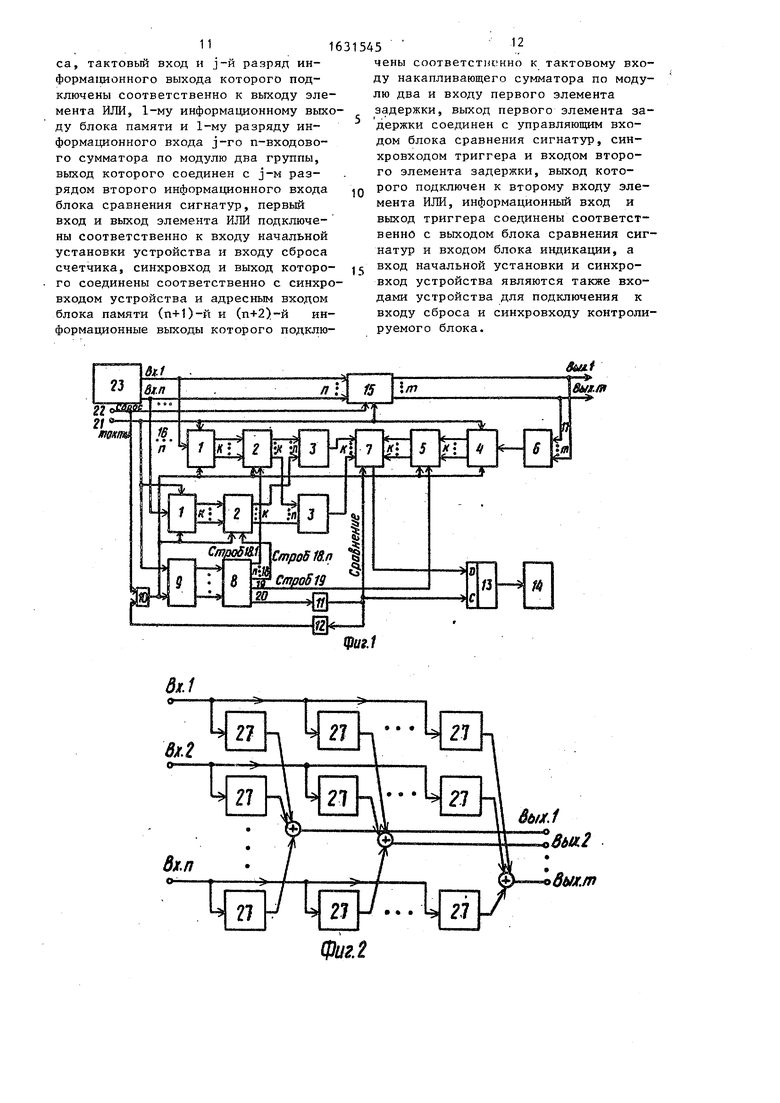

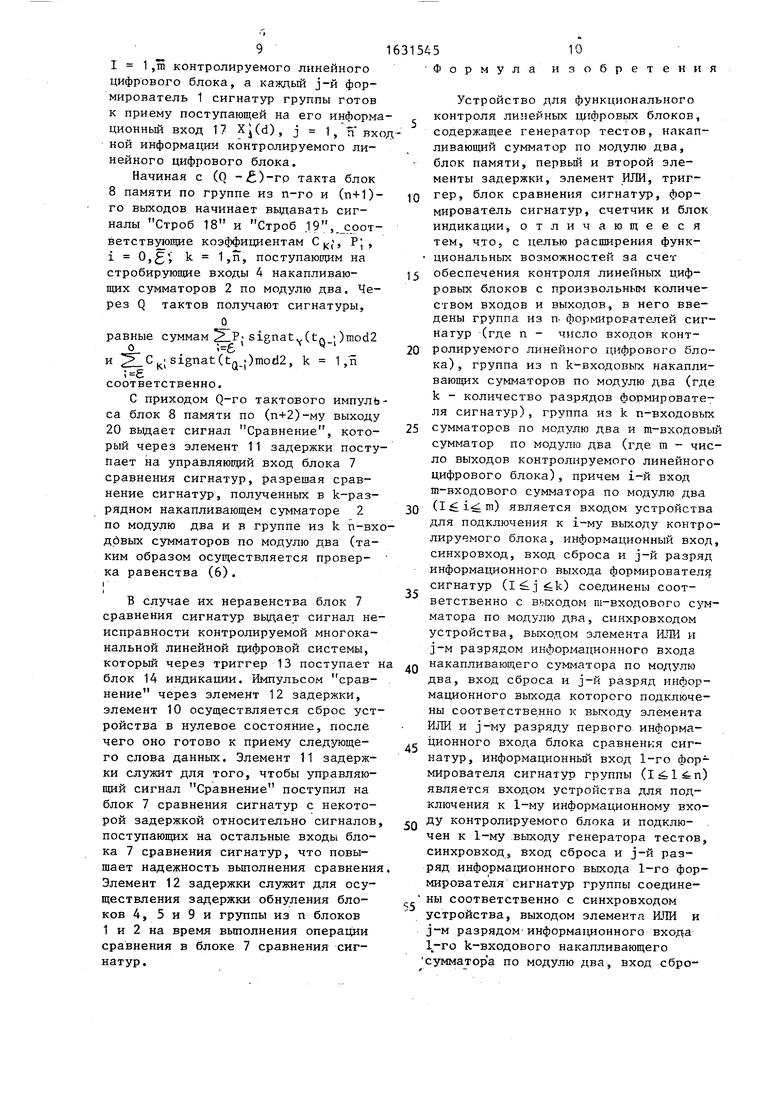

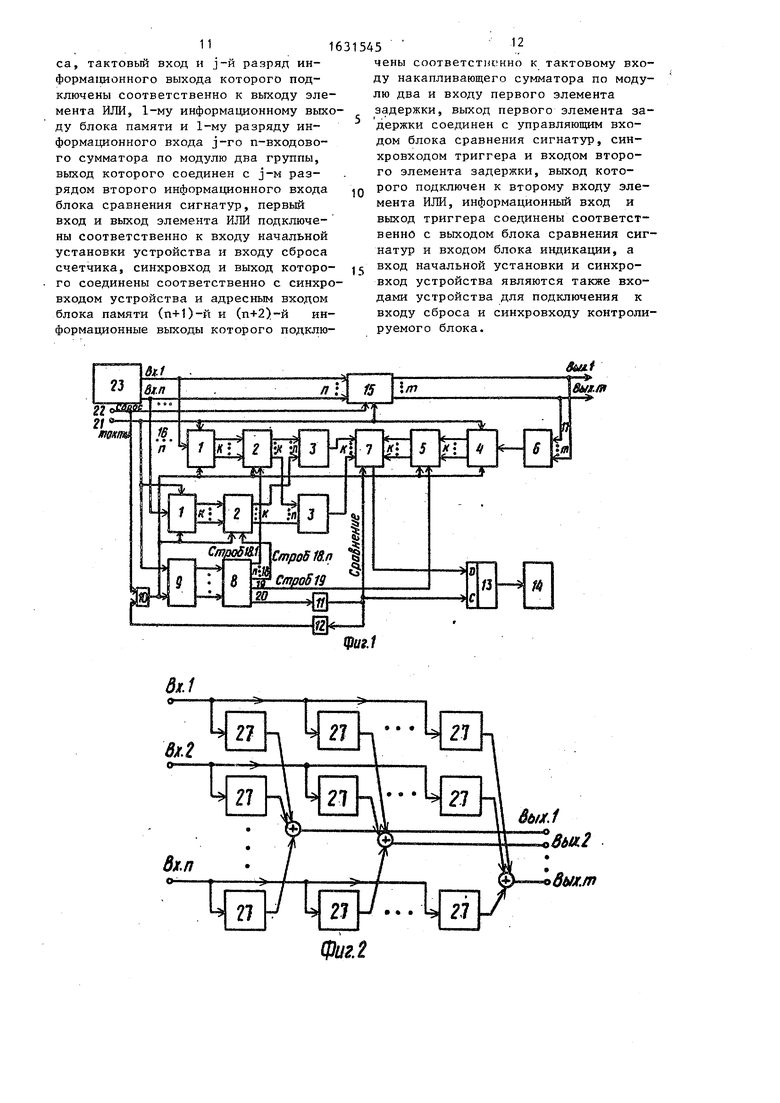

На фиг. 1 представлена структурная схема устройства для функционального контроля линейных цифровых блоков; на фиг. 2 - структурная

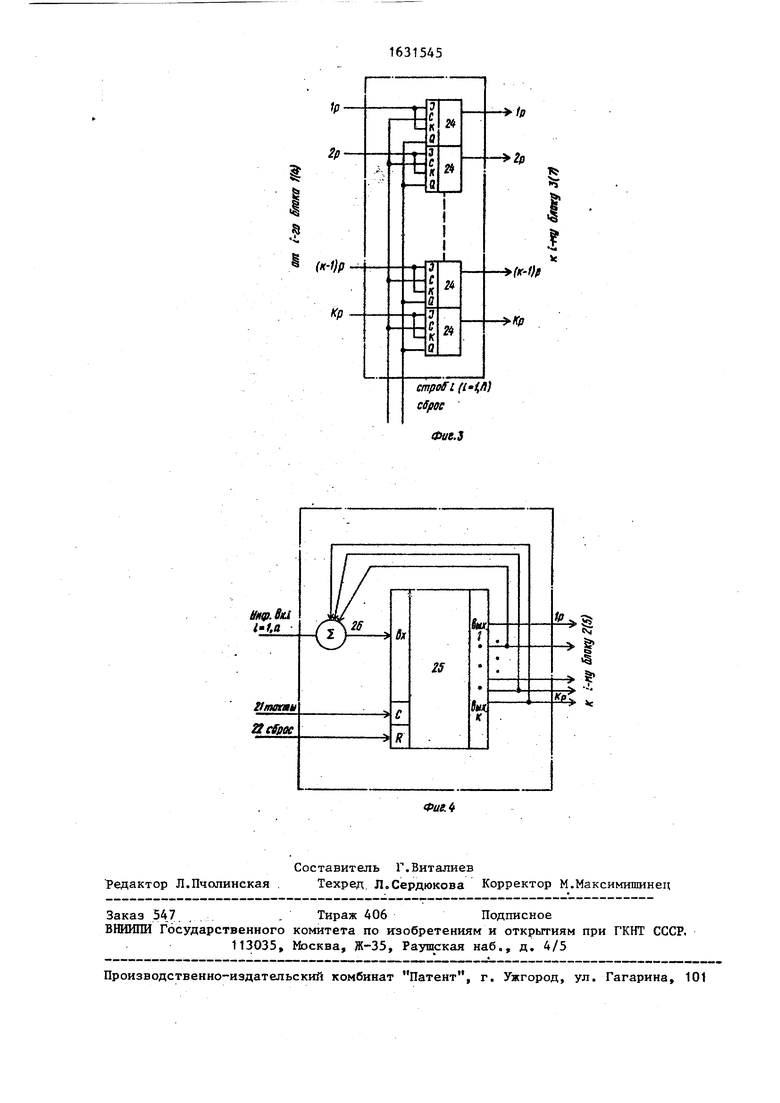

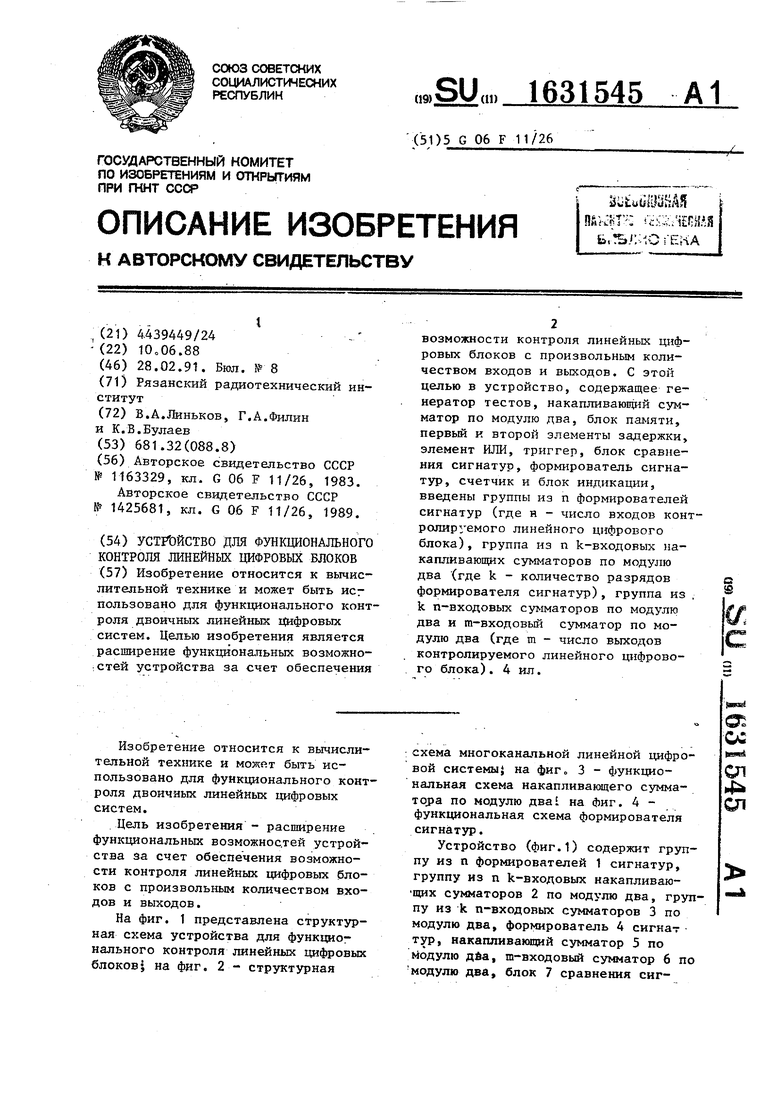

схема многоканальной линейной цифровой системы} на фиг,, 3 - функциональная схема накапливающего сумма- TOjpa по модулю два на фиг. 4 - функциональная схема формирователя сигнатур.

Устройство (фиг.1) содержит группу из п формирователей 1 сигнатур, группу из п k-входовых накапливаю- щих сумматоров 2 по модулю два, группу из k n-входовых сумматоров 3 по модулю два, формирователь 4 сигнат тур, накапливающий сумматор 5 по модулю два, m-входовый сумматор 6 по модулю два, блок 7 сравнения сигсс

1етв4

Сл 4 СЛ

натур, блок 8 памяти, двоичный счетчик 9, элемент ИЛИ 10, первый и второй элементы 11 и 12 задержки, триггер 13 D-типа, блок 14 индикации, объект 15 диагностирования имеет групу из k информационных входов 16 группы из п формирователей 1 сигнатур, группу из тп входов 17 т-входо- вого сумматора 6 по модулю два, труп- пу из п выходов 18, (п+1)-й выход 19 и (п+2)-й выход 20 блока памяти, синхровход 21 и вход 22 сброса контролируемого блока и генератор 23 тестов.

С группы выходов генератора 23 входная информация объекта 15 диагностирования поступает на информационные входы формирователей 1 сигнатур группы, выходы которых подключены соответственно к входам .накапливающих сумматоров 2 по модулю два группы, j-e (j 1, k) выходы сумматоров 2 группы соединены с входами j-ro n-входового сумматора 3 по модулю два группы, выходы которого подключены к входам блока 7 сравнения. Выходная информация объекта диагностирования поступает на т-входо- вый сумматор 6 по модулю два, выход которого соединен с входом формирователя 4 сигнатур. Выходы формирователя 4 сигнатур соединены с входами накапливающего сумматора 5 по модулю два, выходы которого подключены к входу блока 7, выход которого соединен с D-входом триггера 13, выход которого подключен к входу блока 14 индикации. Синхронизирующий вход 21 устройства соединен с син- хроводами объекта 15 диагностирования, группы из п формирователей 1 сигнатур, формирователя 4 сигнатур, группы из п накапливающих сумматоров 2 по модулю два, накапливающего сумматора 5 по модулю два, двоичного счетчика 9. Выход счетчика 9 соединен с адресным входом блока 8 памяти (п+2)-й выход 20 которого через эле- мент 11 задержки соединен со строби- рующим входом блока 7 и с С-входом триггера 13, (п+1)-й выход 19 блока 8-соединен с первым сумматором 5, а группа из п выходов 18 блока 8 соединена с входами соответствующих сумматоров 2 группы. Выход элемента 11 задержки через элемент 12 задержки, подключен к первому входу элемента 10, другой вход которого, а также

5

0

5

,

0

5

вход 22 сброса объекта диагностирования соединен с входами начальной установки формирователей 1 сигнатур группы, формирователя 4 сигнатур, счетчика 9, накапливающего сумматора 5 по модулю два, накапливающих сумматоров 2 по модулю два группы.

Устройство строится по следующему принципу.

Любая многоканальная линейная цифровая система может быть представлена совокупностью отдельных передаточных функций 27 J {| (d) , i 1, n, j - 1,15), показывающих зависимость j-й выходной последовательности от 1-й входной последовательности многоканальной цифровой системы (фиг.2).

Передаточная функция 1-мерной од- ноканальной линейной цифровой системы записывается в виде:

ТГ - fto+fl4d...+ flede .

JW 1 + tf,d...+tfgd

b(d)(1)

a(d)

где #., /5,«efo,i} i оД;

b(d) и a(d) - полиномы степени 1.

Если X(d) многочлен степени k (k n), соответствующий входной информации линейной цифровой системы, а Y(d) - многочлен степени не более k, соответствующий выходной последовательности, то

X(d)j(d) Y(d).(2)

Обозначение через X{(d), i 1,n и Y j (d) , j 1 ,in соответственно выходные и входные последовательности многоканальной линейной цифровой системы, а через Yjj(d) выходные последовательности одноканальных линейных цифровых систем с передаточными функциями J{ (d), многоканальную линейную цифровую систему можно описать системой уравнений:

Y« W + Y2i(d) + ..,+Yni(d)Y,(d); Y,2(d) + Y2i(d) + ...+Ynz(d) Y2(d);

.Y(d) + Y2«W + ...+Ynw(d)

Если (2) известно:

X4(d)J( (d) -t- X4(d) J (d)+.

+ Xn(d)-Jn,(d) Y,(d)i

YM(d).

.+

516315/456

X,(d)J,a(d) + X2(d)J22(d) + ...++ Xn(d)Jnm(d) - Ym(d).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля линейных цифровых систем | 1987 |

|

SU1425681A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1283772A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1718220A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Устройство для контроля логических блоков | 1991 |

|

SU1833879A1 |

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Сигнатурный анализатор | 1983 |

|

SU1223230A1 |

| Сигнатурный анализатор | 1987 |

|

SU1416997A1 |

Изобретение относится к вычислительной технике и может быть исг пользовано для функционального контроля двоичных линейных цифровых систем. Целью изобретения является расширение функциональных возможно- стей устройства за счет обеспечения возможности контроля линейных цифровых блоков с произвольным количеством входов и выходов. С этой целью в устройство, содержащее генератор тестов, накапливающий сумматор по модулю два, блок памяти, первый к второй элементы задержки, элемент ИЛИ, триггер, блок сравнения сигнатур, формирователь сигнатур, счетчик и блок индикации, введены группы из п формирователей сигнатур (где н - число входов контролируемого линейного цифрового блока), группа из п k-входовых накапливающих сумматоров по модулю два (где k - количество разрядов формирователя сигнатур), группа из , k n-входовых сумматоров по модулю два и m-входовый сумматор по модулю два (где m - число выходов контролируемого линейного цифрового блока). 4 ил.

Сложив левые и правые части сис темы уравнений;.

+ jXj,(d)Jh2(d)(d). X«(d)j,(d) + X2(d) j2n,(d) + ...+

X,(d)(J,,(d) + Jta(d) + ...+J4m(d) + Xz(d)(Jw(d) + JM(d) + ...+J2m(d)) + ...+Xn(d)(Jm(d) + Jn2(d) + ...+Jnm(d)) -Y,(d) + Y2(d) + ...+Yh(d).

Представив JH (d) (i 1,n, j . i,ш) в виде (О: .

«,

....$ -т,« i.(d)...W«П -агЩ.си afl7vuy thm

Выражения в скобках приводят к общимзнаменателям

m

я . . (HW. . .+Ь

)т

- I

X,(d)

„ (d) fj ajj(d)+ Ъ12 (d) П a ;; (d) + .. .+b)m(d) fl a ,; (d)

i- Ч

i+

J-.

j4fn

П a,; (d)

тist ™«i

b2r ( aej(dK b22(d) П (d) + ...+b2m(d).n agj (d)

+ XЈ(d) f gj

#

j.-. 2J

1+...

П a2j(d)

т

+ Vd)

ЬЛ(,) + b,2(d :nan;(d) + ...+bnn,(d).n anj(d)

J J

j

m

т

Пап(а) J (

- Y(d) + Ya(d) + ..0+ Ym(d) .Слагаемые левой части приводят к общему знаменателю и домножают на

mw.nmтJZ1Д™

(d)(Ib,;(d)na4:(d))nn a-;(d) + X (dTJ lbftj (d) I j azj (d)) fl fl a- (d) +

fe a s iei1 1 i

m m и т

+ Xn(d)(2:bn;(d) Пви;(«) П rbijCd) (Y,(d) + У) + ...

n v ; J j- J

b1.

(d))

(3)

w m

y П Я a, j(d)- Обозначив Х m n m

CK(d) 2lbk. (d) riak:(d)) П П a;;(d), к- 1, ni.

, j-l. J i p 4

п m j

p(d) ,П П a;:(d)

,-1 J }

-I i

где Cx(d) и P(d) - полиномы степени дены аналитически, выражение (3) мож.п 1 « m Ј , которые могут быть най- j но упростить

Сложив левые и правые части системы уравнений;.

я . . (HW. . .+Ь

)т

J - I

П a ;; (d) + .. .+b)m(d) fl a

i- Ч

i+

J-.

j4fn

П (d) + ...+b2m(d).n agj

#

j.-. 2J

т

:nan;(d) + ...+bnn,(d).n a

j

m

него левую и правую части

(d))

(3)

-,..+ (4)

X,(d)C,(d) + Xu(d)Cz(d) + Рассмотрим многочлен u (d) - U(d)G(d), где G(d) yo + JC, d+...+ Jfede5

U (d) - U(d)(jV +(d+...+ Јde)

Раскроем скобки

U((d) ydU(d)+KitU(d)d+,

+ ygu(d)de.

Так как формирователь сигнатур, используемый для получения сигнатур двоичных последовательностей тоже представляет собой линейную цифрову систему и для него выполняется принцип суперпозиции, то сигнатура последовательности, соответствующей многочлену, равна сумме по модулю два сигнатур последовательностей, членов формулы (4).

Все эти необходимые сигнатуры можно получить на одном сигнатурном регистре по мере поступления информации U(d), фиксируя их коэффициенты У1; полинома, подаваемыми в порядке убывания степеней.

signat(х|а, S 0,Q) + signat(X25, S 0,Q)+...H signat(Xng, S 0,Q)

n

signat(Ys, S 0,Q),

где Y , (d) .

Тогда функционирование устройства для функционального контроля ли- оо

нейкых цифровых блоков передаточными функциям описывается логическим

I

signatt (tQ ;)mod2 + 21 Cg. signata()mod2 + ...+

45

С„; eignat (ta.j)mod2 P

.- .

где signat. , i 1 ,n - состояния i-x

формирователей сигнатур из группы из п формирователей 1 сигнатур;

signatу - состояние формирователя 4 сигнатур.

В общем случае информация в блок 8 памяти вводится следующим образом.

По первым Q - Ј - 1 адресам по всем выходам программируются нули. С (Q Ј)го адреса по Q-й по (п+1)-му выходу 19 и группе из п выходов 20 программируются соответственно коэф50

55

. signatY (tQ.)mod2,

вующая импульсу Сравн пающему на блок 7 о

Устройство работает разом.

Первоначально форми сигнатур и группа из п лей 1 сигнатур, суммат из п сумматоров 2, сче 15 контроля, представл канальную цифровую сис внешнего сброса устана левое исходное состоян го формирователь 4 сиг приему поступающей на онный вход суммы по мо ходных, последовательно

фициенты полиномов P(d) и Cx(d), k 1,п (в порядке убывания1 ст епеней), По Q-му адресу по (п+2)-му выходу 20 программируется единица, соответстm

Xn(d)Cn(d)

Сумматоры 2 и

0

5

0

5

Y;(d)p(d).

5 (фиг.З) представляют собой группу из JK-триггеров 24,

Формирователи 1 и 4 сигнатур (фиг о4) представляют собой сдвиговый регистр 25 с обратными связями и сумматор 23 по модулю два, на котором суммируются по модулю 2 входная двоичная последовательность с разрядами обратной связи сдвигового регистра.

Информационным входом формирователя сигнатур служит один из входов сумматора по модулю два.

Если обозначить сигнатуру последовательности, соответствующую (4), через signat (U, S О, Q), где Q - длина последовательности, а состояние формирователя сигнатуры в момент t, - через signat ( ) , то

signat(Ug, S 0,Q)

О 2L signat( )mod2 ,

Подобные (4) многочлены представляют из себя слагаемые левой части (3) и его правую часть. Поэтому

нейкых цифровых блоков, описываемых передаточными функциями общего вида, описывается логическим уравнением

(5)

signatY (tQ.)mod2,

вующая импульсу Сравнение, поступающему на блок 7 о

Устройство работает следующим образом.

Первоначально формирователь 4 сигнатур и группа из п формирователей 1 сигнатур, сумматор 5 и группа из п сумматоров 2, счетчик 9 и объект 15 контроля, представляющий многоканальную цифровую систему, по цепи внешнего сброса устанавливаются в нулевое исходное состояние. После этого формирователь 4 сигнатур готов к приему поступающей на его информационный вход суммы по модулю два выходных, последовательностей Yj(d),

I 1 ,m контролируемого линейного цифрового блока, а каждый j-й формирователь 1 сигнатур группы готов к приему поступающей на его информационный вход 17 Xj(d), j 15 ff вхоной информации контролируемого линейного цифрового блока.

Начиная с (Q -Ј)-го такта блок 8 памяти по группе из n-го и (п+1)- го выходов начинает выдавать сигналы Строб 18 и Строб .соответствующие коэффициентам CK(, Pj , i 0,Ј j k 1 ,п, поступающим на стробирующие входы 4 накапливающих сумматоров 2 по модулю два. Через Q тактов получают сигнатуры, О

равные суммам 21Р signatv(t(, )mod2 о ч

и lCK;signat()inod2, k 1 ,n

соответственно.

С приходом Q-ro тактового импульса блок 8 памяти по (п+2)-му выходу 20 выдает сигнал Сравнение, который через элемент 11 задержки поступает на управляющий вход блока 7 сравнения сигнатур, разрешая сравнение сигнатур, полученных в k-раз- рядном накапливающем сумматоре 2 по модулю два и в группе из k п-вх ддвых сумматоров по модулю два (таким образом осуществляется проверка равенства (6). i

В случае их неравенства блок 7 сравнения сигнатур выдает сигнал неисправности контролируемой многоканальной линейной цифровой системы, который через триггер 13 поступает блок 14 индикации. Импульсом сравнение через элемент 12 задержки, элемент 10 осуществляется сброс устройства в нулевое состояние, после чего оно готово к приему следующего слова данных. Элемент 11 задержки служит для того, чтобы управляющий сигнал Сравнение поступил на блок 7 сравнения сигнатур с некоторой задержкой относительно сигналов поступающих на остальные входы блока 7 сравнения сигнатур, что повышает надежность выполнения сравнени Элемент 12 задержки служит для осуществления задержки обнуления блоков 4, 5 и 9 и группы из п блоков 1 и 2 на время выполнения операции сравнения в блоке 7 сравнения сигнатур.

5

5

0

5

0

5

0

5

Формула изобретения

Устройство для функционального контроля линейных цифровых блоков, содержащее генератор тестов, накапливающий сумматор по модулю два, блок памяти, первый и второй элементы задержки, элемент ИЛИ, триггер, блок сравнения сигнатур, формирователь сигнатур, счетчик и блок индикации, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения контроля линейных цифровых блоков с произвольным количеством входов и выходов, в него введены группа из п- формирователей сигнатур (где п - число входов контролируемого линейного цифрового блока) , группа из п k-входовых накапливающих сумматоров по модулю два (где k - количество разрядов формирователя сигнатур), группа из k п-входовых сумматоров по модулю два и т-входовый сумматор по модулю два (где m - число выходов контролируемого линейного цифрового блока), причем i-й вход m-входового сумматора по модулю два (1.1 т) является входом устройства для подключения к i-му выходу контролируемого блока, информационный вход, синхровход, вход сброса и j-й разряд информационного выхода формирователя сигнатур () соединены соответственно с выходом m-входового сумматора по модулю два, синхровходом устройства, выходом элемента ИЛИ и j-м разрядом информационного входа накапливающего сумматора по модулю два, вход сброса и j-й разряд информационного выхода которого подключены соответственно к выходу элемента ИЛИ и j-му разряду первого информационного входа блока сравнения сигнатур, информационный вход 1-го формирователя сигнатур группы () является входом устройства для подключения к 1-му информационному входу контролируемого блока и подключен к 1-му выходу генератора тестов, синхровход, вход сброса и j-й разряд информационного выхода 1-го формирователя сигнатур группы соединены соответственно с синхровходом устройства, выходом элемента ИЛИ и j-м разрядом информационного входа 1-го k-входового накапливающего сумматор а по модулю два, вход сброса, тактовый вход и j-й разряд информационного выхода которого подключены соответственно к выходу элемента ИЛИ, 1-му информационному выходу блока памяти и 1-му разряду информационного входа j-ro п-входово- го сумматора по модулю два группы, выход которого соединен с j-м разрядом второго информационного входа блока сравнения сигнатур, первый вход и выход элемента ИЛИ подключены соответственно к входу начальной установки устройства и входу сброса счетчика, синхровход и выход которого соединены соответственно с синхро входом устройства и адресным входом блока памяти (п+1)-й и (п+2)-й информационные выходы которого подклюФиг.1

Фиг. 2

5

чены соответственно к тактовому входу накапливающего сумматора по модулю два и входу первого элемента задержки, выход первого элемента за- держки соединен с управляющим входом блока сравнения сигнатур, син- хровходом триггера и входом второго элемента задержки, выход которого подключен к второму входу элемента ИЛИ, информационный вход и выход триггера соединены соответственно с выходом блока сравнения сигнатур и входом блока индикации, а вход начальной установки и синхровход устройства являются также входами устройства для подключения к входу сброса и синхровходу контролируемого блока.

8ых.т

1р- 2fi

i

(«-f)p Kp

Инф.8я1 l-f.a

§

i

v

| Устройство непрерывного тестового диагностирования линейных цифровых систем | 1983 |

|

SU1163329A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство контроля линейных цифровых систем | 1987 |

|

SU1425681A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-02-28—Публикация

1988-06-10—Подача