19

СП

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования с исправлением ошибок | 1986 |

|

SU1411981A1 |

| Устройство для декодирования с коррекцией ошибок | 1985 |

|

SU1292189A1 |

| Устройство для кодирования | 1985 |

|

SU1275782A1 |

| Устройство для кодирования | 1987 |

|

SU1462494A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Устройство для кодирования | 1987 |

|

SU1496010A2 |

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| Декодер сверточного кода (его варианты) | 1985 |

|

SU1320875A1 |

Изобретение относится к вычислительной технике и связи. Его использование в устройствах обнаружения и исправления ошибок позволяет повысить достоверность декодирования за счет исправления до трех пачек ошибок. Устройство содержит блок 1 задержки, формирователи 2...5 проверочных символов, блок 10 определения ошибочных позиций, блок 11 исправления ошибок, блок 12 управления, элемент И 13 и элемент ИЛИ 15. Благодаря введению формирователей 6, 7 проверочных символов, арифметического блока 8, блока 9 вычисления коэффициентов и элемента И 14 в устройстве обеспечивается решение показательного уравнения третьей степени , лё GF (2m), что и позволяет достичь цели изобретения. 7 з. п. ф-лы, 9 ил.

/7 оОт

18

xj ю

vj

,л

О

ел

Фиг.1

Изобретение относится к вычислительной технике и связи и может быть использо- вано в устройствах обнаружения и исправления до трех пачек ошибок, возникающих при хранении или передаче дискретной информации.

Известно устройство для декодирования с коррекцией ошибок, содержащее блоки данных Д1,...,Дп. каждый из которых имеет 8 бит (байт) плюс два контрольных байта,

Недостатком этого устройства является большое оборудование и излишняя избыточность при обработке 2п-разрядных слов.

Из известных устройств для декодиро- вания с коррекцией ошибок наиболее близким по технической сущности является устройство для декодирования с исправлением ошибок, которое содержит входной сдвиговый регистр; четыре формирователя проверочных символов, блок исправления ошибок, блок управления, два элемента И и элемент ИЛИ.

Недостатком этого устройства является невозможность исправления трех пачек ошибок, что приводит к снижению достоверности при передаче информации.

Целью изобретения является повышение достоверности декодирования за счет исправления до трех пачек ошибок.

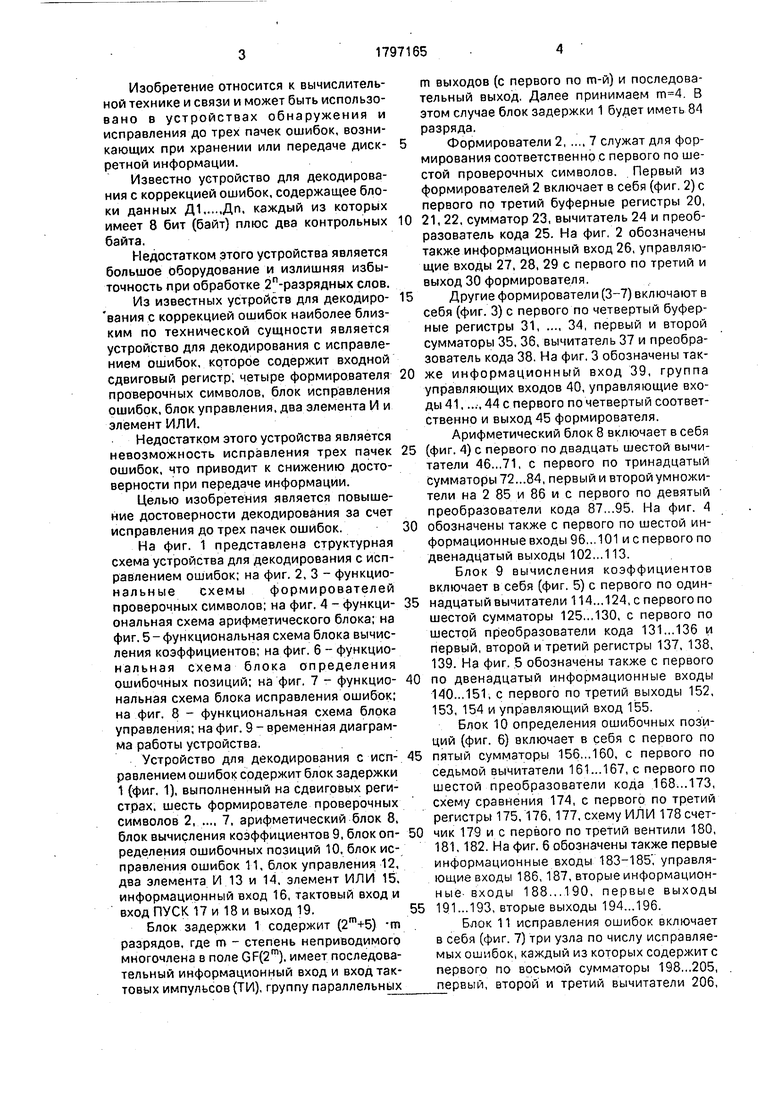

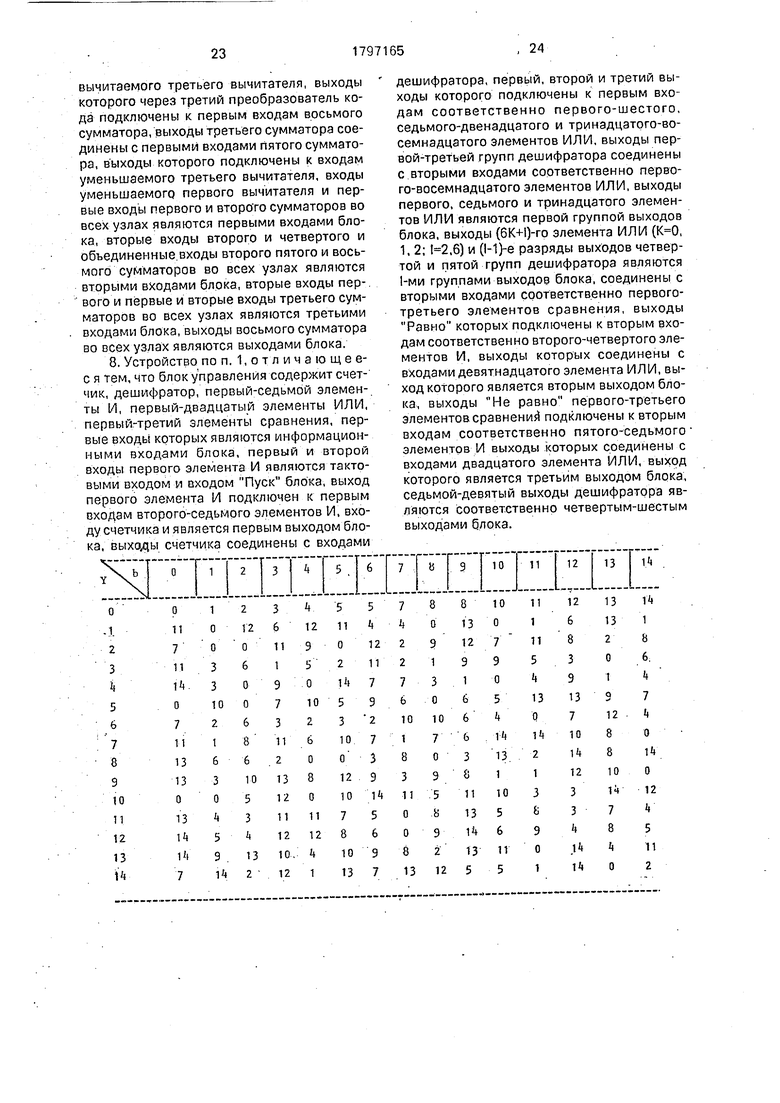

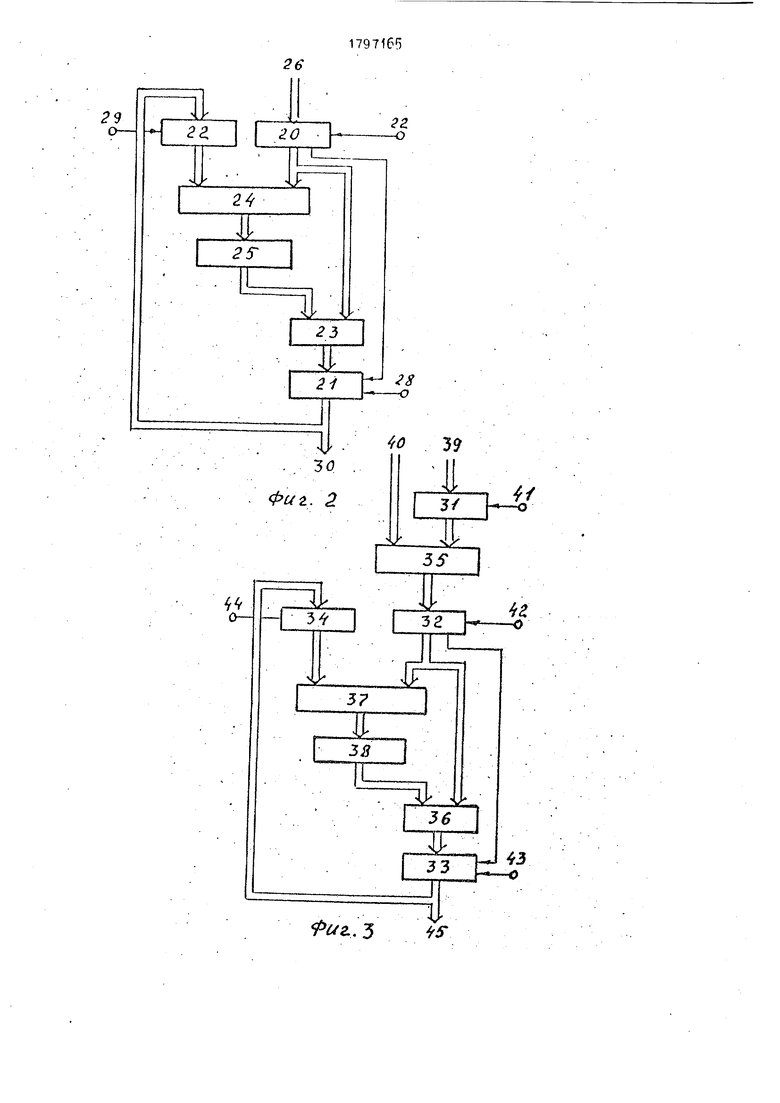

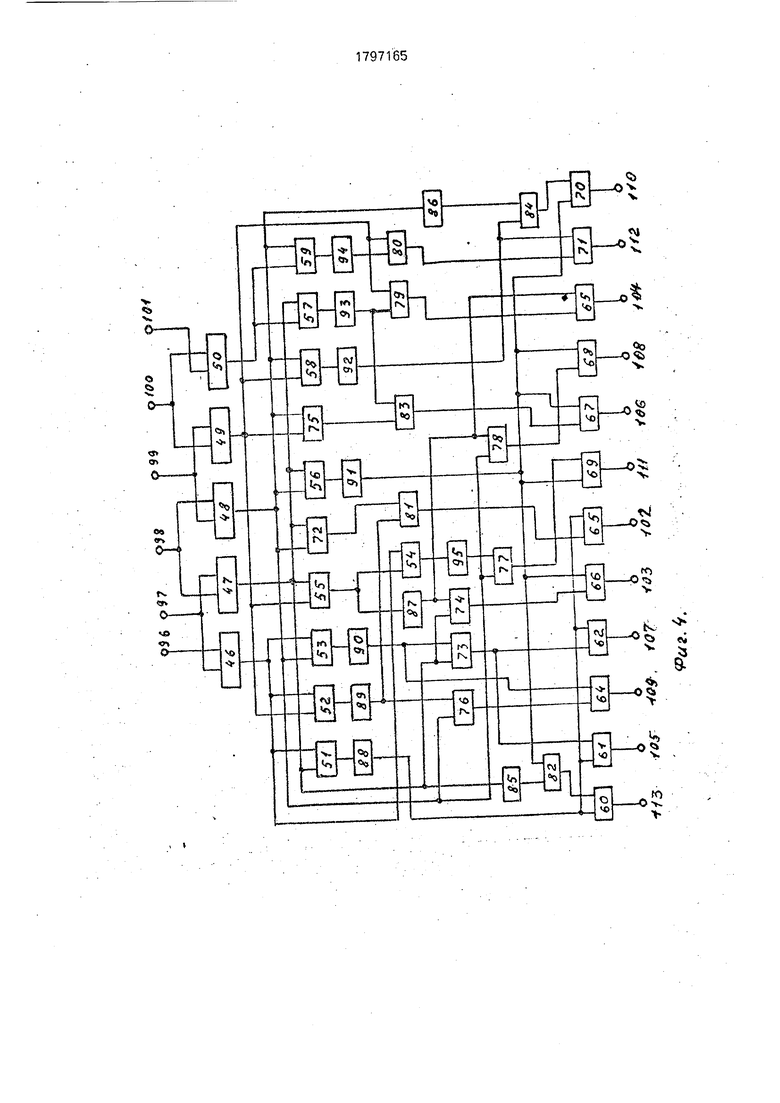

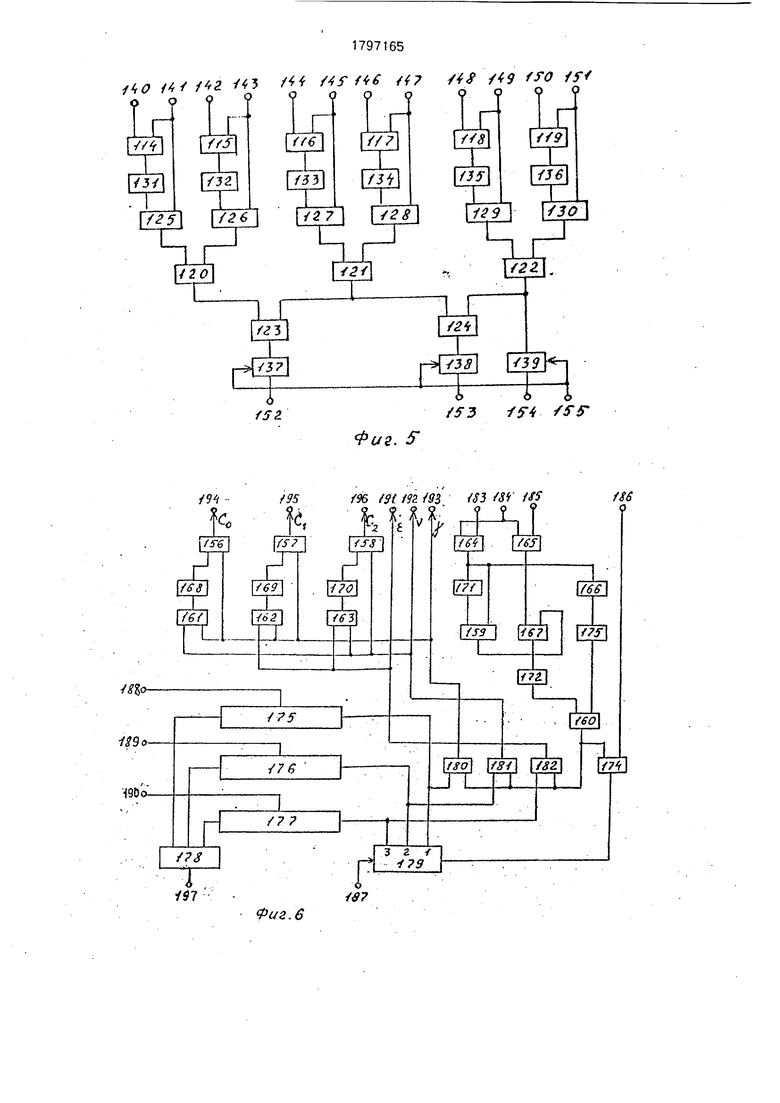

На фиг. 1 представлена структурная схема устройства для декодирования с исправлением ошибок; на фиг. 2,3- функцио- нальные схемы формирователей проверочных символов; на фиг. 4 - функциональная схема арифметического блока; на фиг. 5-функциональная схема блока вычисления коэффициентов; на фиг. 6 - функциональная схема блока определения ошибочных позиций; на фиг. 7 - функциональная схема блока исправления ошибок; на фиг. 8 - функциональная схема блока управления; на фиг. 9 - временная диаграмма работы устройства.

Устройство для декодирования с исправлением ошибок содержит блок задержки 1 (фиг. 1), выполненный на сдвиговых регистрах, шесть формирователе проверочных символов 2, .... 7, арифметический блок 8, блок вычисления коэффициентов 9, блок определения ошибочных позиций 10, блок исправления ошибок 11, блок управления 12, два элемента И 13 и 14, элемент ИЛИ 15. информационный вход 16, тактовый вход и вход ПУСК 17 и 18 и выход 19.

Блок задержки Т содержит (2т+5) -т разрядов, где т - степень неприводимого многочлена в поле GF(2m), имеет последовательный информационный вход и вход тактовых импульсов (ТИ), группу параллельных

m выходов (с первого по m-й) и последовательный выход. Далее принимаем . В этом случае блок задержки 1 будет иметь 84 разряда.

Формирователи 2,.... 7 служат для формирования соответственное первого по шестой проверочных символов. Первый из формирователей 2 включает в себя (фиг, 2) с первого по третий буферные регистры 20,

0 21, 22, сумматор 23, вычитатель 24 и преобразователь кода 25. На фиг, 2 обозначены также информационный вход 26, управляющие входы 27, 28, 29 с первого по третий и выход 30 формирователя.

5 Другие формирователи (3-7) включают в себя (фиг. 3) с первого по четвертый буферные регистры 31, ..., 34, первый и второй сумматоры 35, 36, вычитатель 37 и преобразователь кода 38. На фиг. 3 обозначены так0 же информационный вход 39, группа управляющих входов 40, управляющие входы 41. ...,44 с первого по четвертый соответственно и выход 45 формирователя.

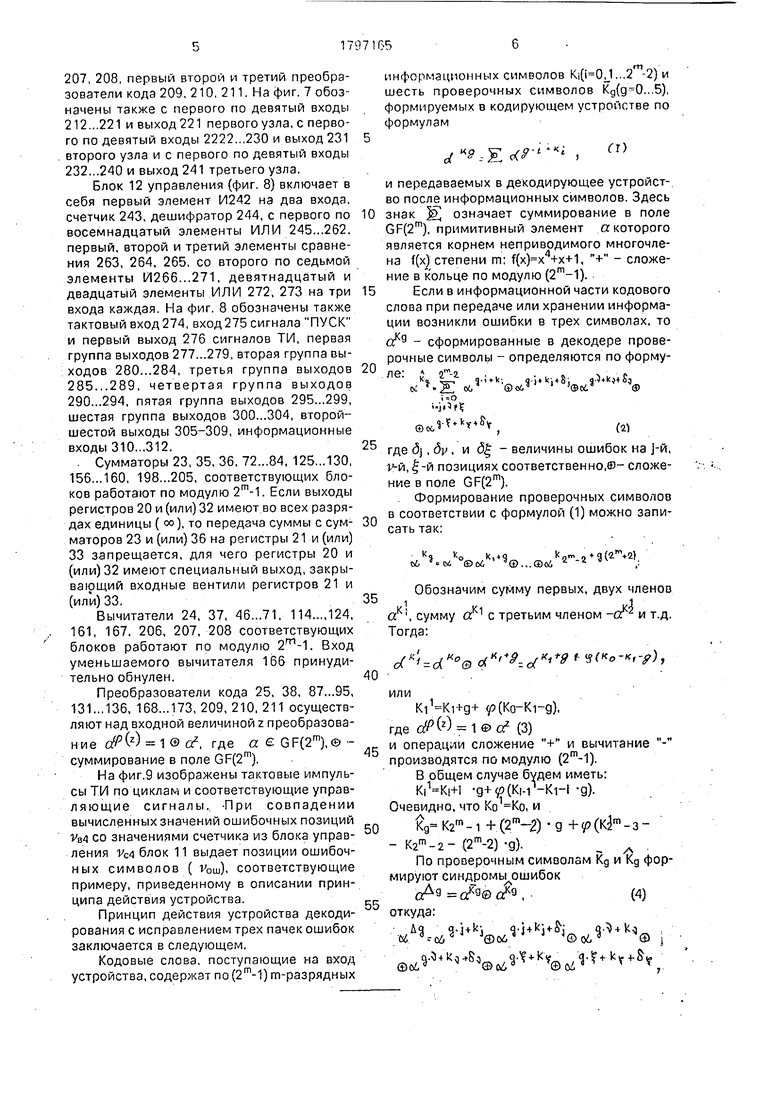

Арифметический блок 8 включает в себя

5 (фиг. 4) с первого по двадцать шестой вычи- татели 46...71, с первого по тринадцатый Сумматоры 72...84, первый и второй умножители на 2 85 и 86 и с первого по девятый преобразователи кода 87,..95. На фиг. 4

0 обозначены также с первого по шестой информационные входы 96..,101 и с первого по двенадцатый выходы 102...113.

Блок 9 вычисления коэффициентов включает в себя (фиг. 5) с первого по один5 надцатый вычитатели 114.„124, с первого по шестой сумматоры 125...130, с первого по шестой преобразователи кода 131... 136 и первый, второй и третий регистры 137, 138, 139. На фиг. 5 обозначены также с первого

0 по двенадцатый информационные входы 140...151, с первого по третий выходы 152, 153, 154 и управляющий вход 155.

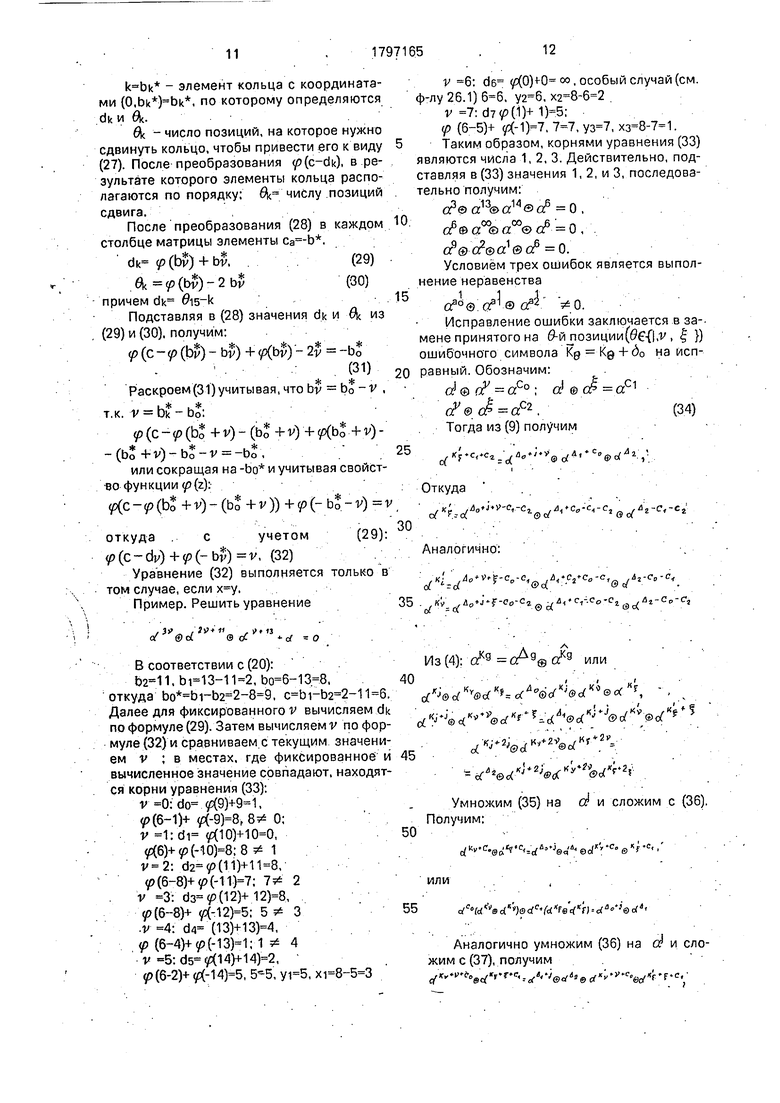

Блок 10 определения ошибочных позиций (фиг. 6) включает в себя с первого по

5 пятый сумматоры 156... 160, с первого по седьмой вычитатели 161... 167, с первого по шестой преобразователи кода 168...173, схему сравнения 174, с первого по третий регистры 175,176, 177, схему ИЛИ 178счет0 чик 179 и с первого по третий вентили 180, 181,182. На фиг. 6 обозначены также первые информационные входы 183-185, управляющие входы 186,187, вторые информационные-входы 188.,.190, первые выходы

5 191.-.193, вторые выходы 194...196.

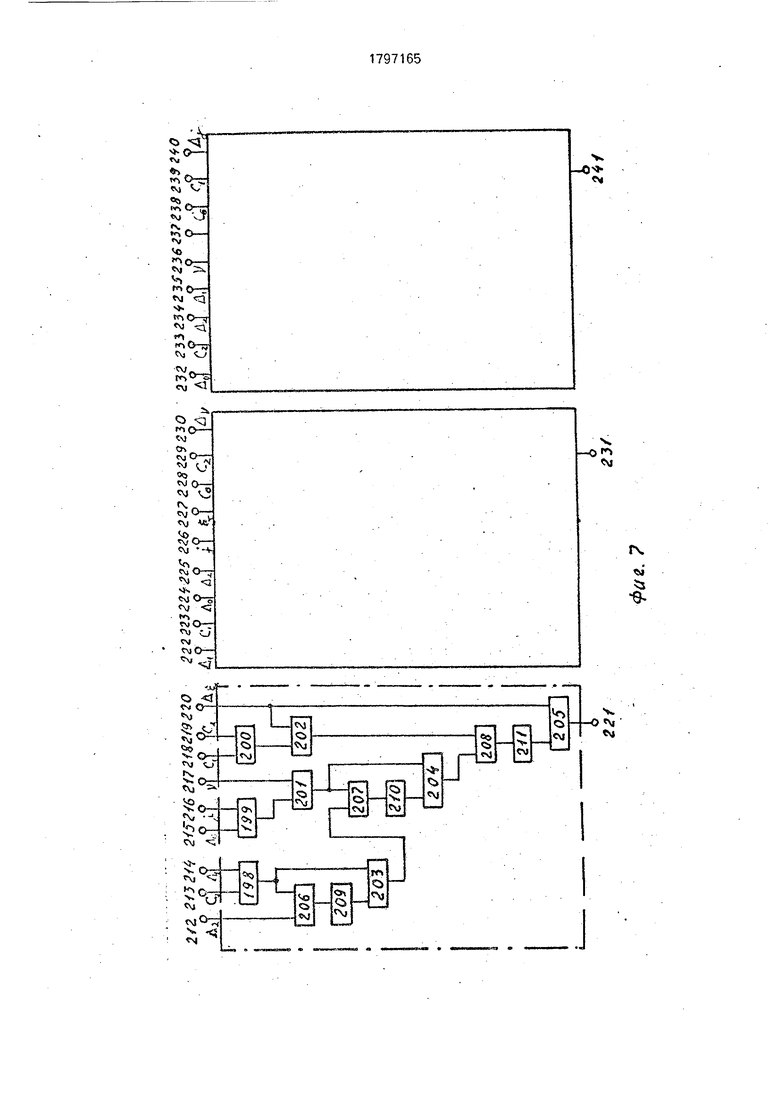

Блок 11 исправления ошибок включает в себя (фиг. 7) три узла по числу исправляемых ошибок, каждый из которых содержит с первого по восьмой сумматоры 198.,.205, первый, второй и третий вычитатели 206,

207, 208, первый второй и третий преобразователи кода 209, 210, 211. На фиг. 7 обозначены также с первого по девятый входы 212...221 и выход 221 первого узла, с первого по девятый входы 2222...230 и выход 231 5 второго узла и с первого по девятый входы 232.,.240 и выход 241 третьего узла.

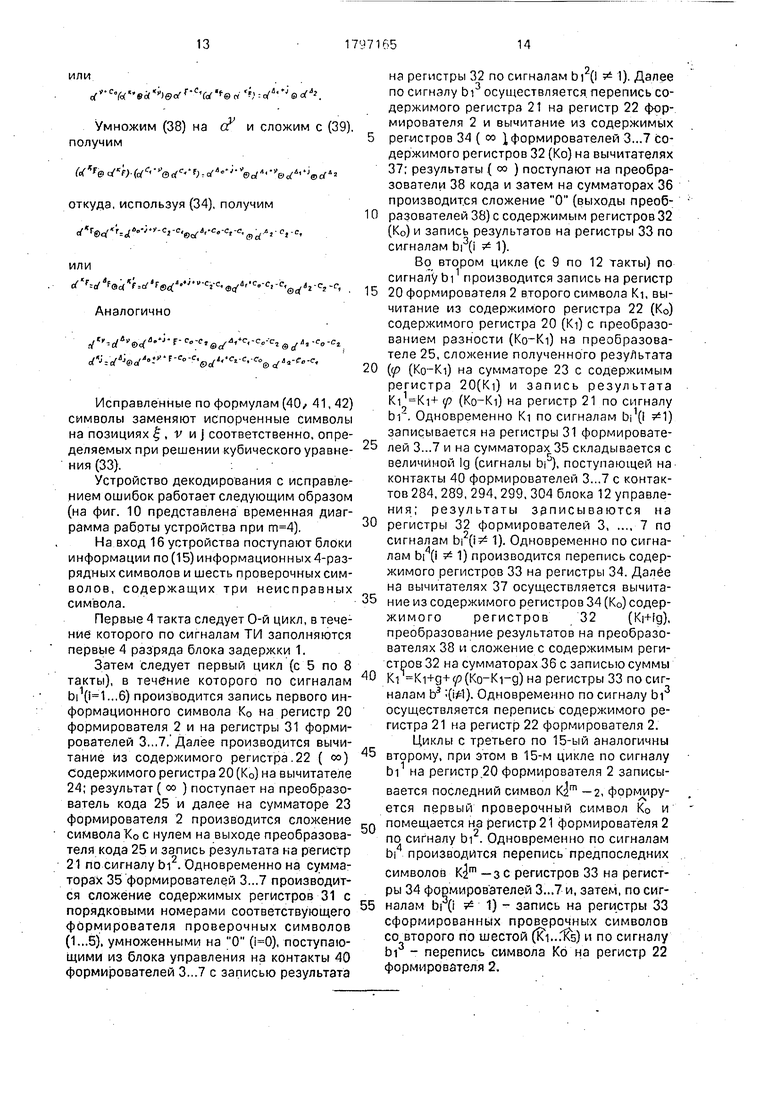

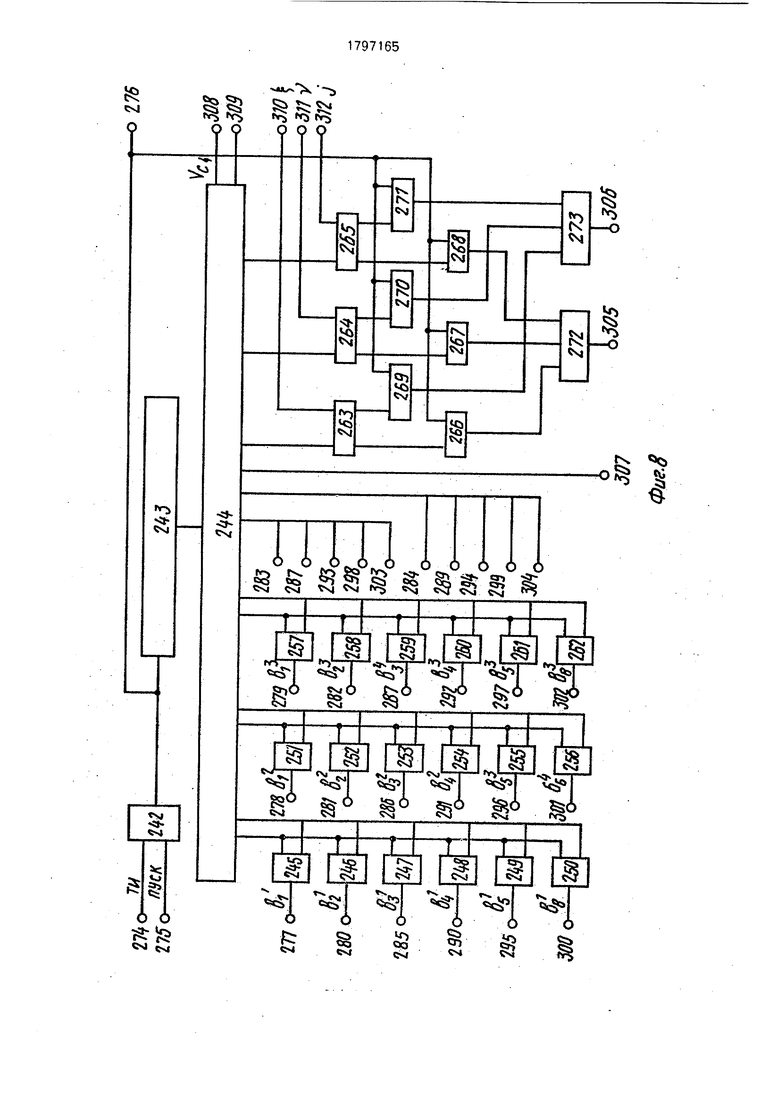

Блок 12 управления (фиг. 8) включает в себя первый элемент И242 на два входа, счетчик 243. дешифратор 244, с первого по 10 восемнадцатый элементы ИЛИ 245...262. первый, второй и третий элементы сравнения 263, 264, 265, со второго по седьмой элементы И266...271. девятнадцатый и двадцатый элементы ИЛИ 272, 273 на три 15 входа каждая. На фиг. 8 обозначены также тактовый вход 274, вход 275 сигнала ПУСК и первый выход 276 сигналов ТИ, первая группа выходов 277...279, вторая группа выходов 280...284, третья группа выходов 20 285...289, четвертая группа выходов 290...294, пятая группа выходов 295...299, шестая группа выходов 300...304, второй- шестой выходы 305-309, информационные входы 310...312.25

. Сумматоры 23, 35, 36, 72...84, 125...130, 156...160, 198...205, соответствующих блоков работают по модулю 2т-1. Если выходы регистров 20 и (или) 32 имеют во всех разрядах единицы (со), то передача суммы с сум- 30 маторов 23 и (или) 36 на регистры 21 и (или) 33 запрещается, для чего регистры 20 и (или) 32 имеют специальный выход, закрывающий входные вентили регистров 21 и (или) 33.35

Вычитатели 24, 37, 46...71, 114...,124. 161, 167. 206, 207, 208 соответствующих блоков работают по модулю 2т-1. Вход уменьшаемого вычитателя 166 принудительно обнулен.40

Преобразователи кода 25, 38, 87...95, 131...136, 168....173, 209, 210, 211 осуществляют над входной величиной z преобразование o(z) 1© о2, где aeGF(2m),© суммирование в поле GF(2m).

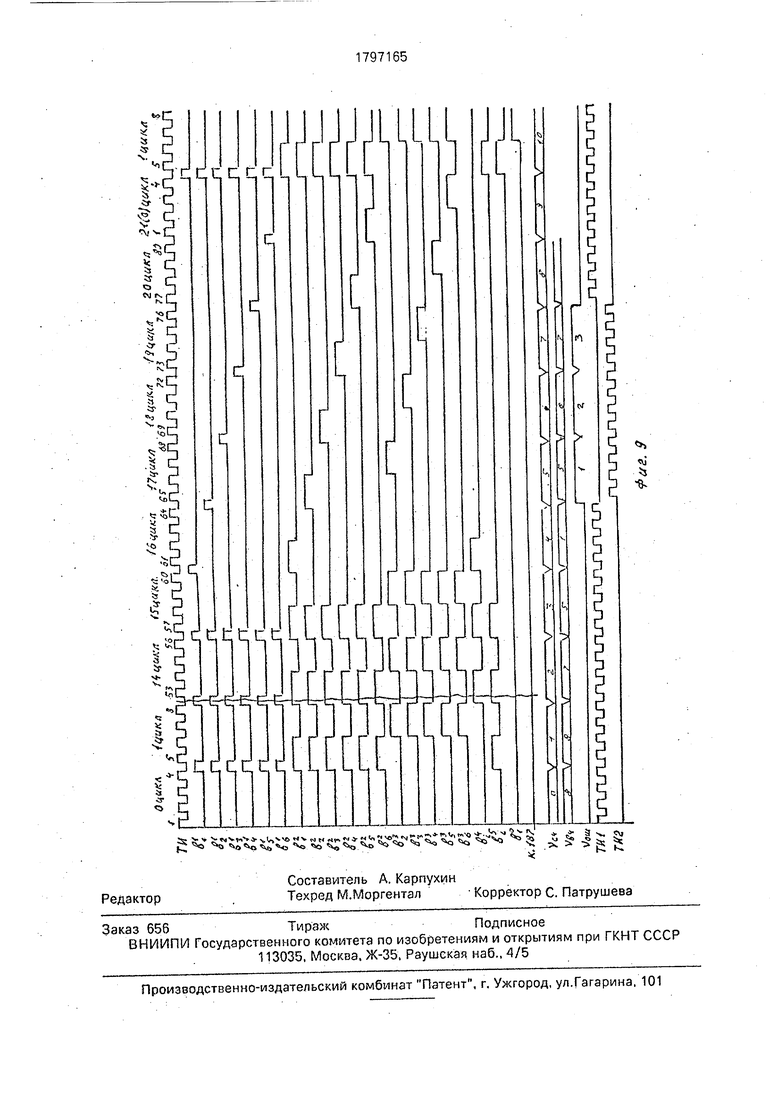

На фиг.9 изображены тактовые импульсы ТИ по циклам и соответствующие управ- ляющие сигналы.. -При совпадении вычисленных значений ошибочных позиций VB4 со значениями счетчика из блока управ- ления VC4 блок 11 выдает позиции ошибоч- ных символов ( УОШ), соответствующие примеру, приведенному в описании принципа действия устройства.р.г

Принцип действия устройства декоди- ° рования с исправлением трех пачек ошибок заключается в следующем.

Кодовые слова, поступающие на вход устройства, содержат по (2т-1) т-разрядных

информационных символов Ki(..,2 -2) и шесть проверочных символов Kg(g-0...5), формируемых в кодирующем устройстве по формулам

ч «;

«)

и передаваемых в декодирующее устройст-. во после информационных символов. Здесь знак }ЁГ означает суммирование в поле GF(2m), примитивный элемент а которого является корнем неприводимого многочлена f(x) степени m: f(x)x4+x+1, + - сложение в кольце по модулю (2т-1).

Если в информационной части кодового слова при передаче или хранении информации возникли ошибки в трех символах, то

- сформированные в декодере проверочные символы - определяются по форму

.Л.2 ),

Ч

Ф

©со

to

где д, dv. и 6% - величины ошибок на j-й, , Ј-й позициях соответственно,®- сложение в поле GF(2m).

. Формирование проверочных символов в соответствии с формулой (1) можно записать так:

...в.

Обозначим сумму первых, двух членов

к

у ,

-с№ и т.д. fKi . f У «°-« -г),

, сумму аК1 с третьим членом Тогда:

или

Ki1 Ki+g+ (Ko-Ki-g),

где af(2) 1©az (3)

и операдии сложение + и вычитание

производятся по модулю (2т-1).

В общем случае будем иметь:

-д+(Ки1-КН -д). Очевидно, что Ко -Ко, и

Кд К2т - 1 + (2т-2) д + р (Klm - з - - К2т-2- (2т-2)-д).л

По проверочным символам Кд и Кд фмируют синдромы ошибок

дД-Э - t .(4)

откуда:

.+M©

или

y kwww-,

где i ,, eeV.Y Тогд

лЧо/ фЛ/ , ,

4 W I W alfll

д. Un oi сб Фоб , .

ь к ; V

Ui Л ©«. g fflcA , L Kj 5jKg+ 5) ky + 5S

oi «об ©oi @oi

Умножим (5) на о и сложим с (6). учим:

:c/ W4wKV@c(%tf1kW

/ aH W J V-t .111)

«& ie«6fc.rt l VWl®«JV K T M1ffltbX)i . . «(Л вй чЛй11).

Умножим (7) на av и сложим с (8), Получим:

rfVj 1 ecfV®o(V;fflc or FW ®rf rf ®rffX

Аналогично:

«. « V aDt -tf KAetf), «4t4i iectVSe ;l} «A4.tfST(«ie.fJ ffl« ),:.

«.©«..

Умножим (9) на о и сложим с (10). Получим: (V Wv fW -e J v®ofJ4« ie.)rfi%

или

y etV «f4 (rf; erfV4f)® V®cf«).©rf ;--o

Обозначим

J+v.+ | aS;(12)

(13) )+ + «а (14) Тогда (11) запишется так:

,

Аналогично

/Al4 af .

1®d

Л -I- ,

& d.

,

,

откуда

cii|+a a Dii24ai

© (si

&1

10

4i

л/.)

C6

2®6i

(Si

ii

Oi

Aa

ИЛИ

Wn © + a 2©c + u .i bo+a ..

M ffiOi fflCi4 4 Лг.+а ..Фй&б + Ь,

Далее из (12) и (13):

oV-w44 4 01 ® 4 4

и

i4niaTtobl+bo .

.Ho @teAqalao6A5, .

откуда:

eb4aU ot&44b to ffltt48 4 o s .0 амй&1®еь4 & i

i fflCi4

и

Vb. ©

Oiiua®OJ,

Аналогично из (12) и (13): 40 © @ &а °4а фйб + ж

1i X 1 . Я

a и

0сбйг+Ь1©№й1

w. й1+

gb +a fflat.4 @e6& tA 4al t(3)(

66

5

Откуда:

Ь 441©0й

Ь 4 + Ь 1

о;

сб «

46

bl+Ь|е йг+ь° 4&1© &44 & . ;

2к й ,°

0

©

йб24ге об

i% + &

Ab2 + b ©oiui + &0 «,

Обозначим ai Ai-Ao, , аз Аз - А , а Ач - Дз, as ДБ - Д},

- :--«-J

Тогда с учетом (3):

(. ) ,, ,), . .tcpca.-aj-

И

об

e64l44 fflOtui e .,

.а чСо -аЛ-чСоц-о,

Аналогично: Раскрывая скобки, получим

. «Р.о.,)Л rf % с « Чо . .

п. „ , . ,5 Из сравнения (18) и (19) вытекают соотношеW661Р(()1 1 -гп1/ 1-л1л

ос

Qt601 а° V(a,-a.)-q(a,-a,)-a,.

. . ния:междуа,иЬ,

« ® ..

. . в/|(а,-01ЬчЧа«-о.-о.)..а ai1 b2+bi, , (20)

. ao1 b2+bi+bo. -ai .

10 Из(19), используя табличную функцию (z)

Тогда ai1 примет вид:(3), получим

ai to° Ca4-°.b4|Ub s a,cnas-Qi)),(-.В,) + ,-у( иЧ(аг-а,)(аг-а,,-а1яйЧ(а,.аг)-ч(а.-а,-а;)-а, vaMi-St-S.-W-tA-Wtt-b-t. .WgjАнэлогично преобразуем Э21. Получим 15

Равенство (21) распадается на три:

, .as(a,cf(a4-a,)-tf(ot-a,)d,A.a1.o,t|(a6-a1))) (v Ьо) °°. о« о« ty i х ч66 ;o,.4to%-aO-c,(Q,..a.)e.(a4-aO-4la,-aOу)(2 V-bl - (V-Ьо)) «, 64 ©W yj(3v-b2-bl-bof(V-bo)Аналогично из (15) определяем ао1. Получим 20 -(2v-bi-bo O -Ь0)))

или, учитывая, что р (р (Ь)) Ь и р (оо) 0. a . D6aiV p((ai ail©ix,a«4tKas-a)-tMa«-0) , получим:

Ч&г-оЛ-Ч(аъ-аг}-г01 ф чка4-аг -ч(а4-оо-2а,V-bo 0. (22)

фо(-2 i -bi-bo-.(v-b0) 0, (23)

Из (12) -v-§; подставляя в (13), пол-25 3 v- b2 bi - (v- Ь0)

учим-(2v-bi-bo(v-b0),))0- (24)

э t t a1 Уравнения (22), (23) и (24) являются уравнеoia° ©ot ©об oi у.ниями первой, второй и третьей степени

„п соответственно.

или, умножая на «/обе части:JU Уравнение (24) преобразуем с учетом

, : . свойства функции р (т): р (z) -f(-z)z. д.,учим

° @rf@o( rf - . b2-v. + so(bt-v+v(bo-v)),

откуда:ос или Ь2-bi-.Ь0 +b0-v + (p

J (bi-bo + b0-v + (bo))0, (25)

, .. . Обозначим ,bi-bo b, -(b2-bi)c.

тогда (25) примет вид Аналогично из (14) получим

40 Ьх+у+ v bx+y+tfy)H. (26)

ae ff&c/Q; ®o()(Ј7 , Формула (26) позволяет представить

.уравнениетретьей тепёни(26) как функцию

откудадвух аргументов и с, т.е. (b. с).

t а -v о ,Составим.таблицу, в которой (b. у)

dC ( ®d . 45образуют замкнутые кольца по модулю 15.

Для удобства далее начало кольца будем

Из (16) и (.17)считать в ячейке с .

Кольцо с началом в ячейке (0.0) обладает .0 0 9® ,свойством

50 откуда Кольца с началом в ячейках (0,5) и (0,10)

Остальные кольца обладают свойством: или. умножая на ,/. 55 c-dk)+ . (28)

где dk - величина, на которую нужно умень- ©rf21 0 .шить содержимое ячейки (bx. у), т.е. с. чтобы

кольцо имело такую же последовательность Представим уравнение (18) в видеэлементов, как и функция c(z);

cr W4rf2W ttV® Je : .

- элемент кольца с координата-v 6: de $0)0 оо, особый случай (см.

ми {0,bk)bk, по которому определяютсяф-лу 26.1) , , .

.dkn ft. . . )+1)5:

Ok - число позиций, на которое нужно f (6-5)+ f(-)l, , , .

сдвинуть кольцо, чтобы привести его к виду5 Таким образом, корнями уравнения (33)

(27). После преобразования p(c-dk), в .ре-, являются числа 1, 2, 3. Действительно, подзультате которого элементы кольца распо-ставляя в (33) значения 1, 2, и 3, последовалагаются по порядку; ф числу .позиций. тельно получим:

сдвига., оРва13© 14© 6 0, После преобразования (28) в каждом 0. JB-,, «XJR ,

-, . СА В С.С (У i A vi/ Сс - и,.

столбце матрицы элементы .q 9 1 fi

ibvY+b (291or©-от©а ®сг 0.

dk p(uv) v, . ( )Условием трех ошибок является выпол j(bv)-2bv ( 30)нение неравенства

причем dk 15-k15 „Т J J- Подставляя в (28) значения dk и Д избГ®.(. JO.

(29) и (30). получим: . : . Исправление ошибки заключается в за-.

. мене принятого на v-w позиции(vЈ,v, Ј })

p(C-p(bv)-bv))-2v -b0ошибочного символа К9 Ке +до на исп: . (31)20 равный. Обозначим:

Раскроем(31)учитывая,чтоbv - , с$®сУ ас°; a ©oЈ aCl

т.к. v ;. . . (34)

(р((Ь +v)-(b +v)(b -+v)- Тогда из (9) получим

-(bЈ+v)-bЈ-v -bo, .25 .. v

или сокращая на-bo и учитывая своист-ч ...

во-функции р(г):. .Откуда

Kc-Kb v)-())+p(, . . .,; ,;.Cf.e.

30 откуда . сучетом (29):

p(c-6v)( (32) .;.... Аналогично:

Уравнение (32) выполняется только в , . . том случае, если .. - . .

Пример. Решить уравнение35. ,к ,а0 г-о0-сг ..со-с, ,

((©ct СУсч

, J) /Jtf+ ff ,13 ОГ©ОС ®of

дЛ .

В соответствии с (20): . Из (4): i/9 или

.bi 13-11 2, , . 40, , , ; откуда bo bi-b2 2-8 9, c bi-b2 2-11 6. rf%rf%cf rfdc ©(/lcj©ofl 0© Kf, -. Далее для фиксированного v вычисляем dk . ,, - л K;.j «j, по формуле (29). Затем вычисляем v по фор- rfVW ®d 9d муле(32) и сравниваем с текущим значени- ,кг.2«.. ем v ; в местах, где фиксированное и 45 ® . ... вычисленное значение совпадают, находят- . V/ i©o( r 2WK ®of 2 ся корни уравнения (33):

v 0:do (9),. Умножим (35) на о1 и сложим с (36).

(6-1))8У8 0; ; Получим:

v 1:di (10),. 50

$6))8;8 5 1c Kl Sc;If c rf s W © :c e if c .

(11),. .

(6-8)+)(-11)7; 7 2или

. v 3: d3(12)+12)8, ..

(р(6-8)+ )5: 5 3 55 a c w rVsc(berfc / o((feV rb c{ 1 ®rf 1

.v 4: d4 (13)+13)4,, .

. (6-4)+9(-13)1; 1 4Аналогично умножим (36) на ct и слоv 5:d5 #14}H4)2, . жим с (37), получим (.б.. ...rf.f..v..rf.;..4.F.c.или

,( r c ( a .

Умножим (38) на о и сложим с (39), получим

fr%c/ b Wc ° ; W4 W W la откуда, используя (34), получим

« -«V .erfVe.-e.-e..-V .

ИЛИ d r a lFerf fkc/ F ..,-cJ-c,ecr,/lr.c,,(grf,2.Cj.c.j

Аналогично

.Vt / l e c J-г-с°;с ©у - - @ ч,-с0-Сг jVztt wW - .- 4.-е.-с,

Исправленные по формулам (40/ 41, 42) символы заменяют испорченные символы на позициях Ј , v и j соответственно, определяемых при решении кубического уравнения (33).. .

Устройство декодирования с исправле - нием ошибок работает следующим образом (на фиг. 10 представлена временная диаграмма работы устройства при ).

На вход 16 устройства поступают блоки информации по (15) информационных 4-разрядных символов и шесть проверочных символов, содержащих три неисправных символа.

Первые 4 такта следует 0-й цикл, в течение которого по сигналам ТИ заполняются первые 4 разряда блока задержки 1.

Затем следует первый цикл (с 5 по 8 такты), в течение которого по сигналам bi1(..,6) производится запись первого информационного символа К0 на регистр 20 формирователя 2 и на регистры 31 формирователей 3...7. Далее производится вычитание из содержимого регистра.22 ( оо) содержимого регистра 20 (К0) на вычитателе 24; результат ( оо ) поступает на преобразователь кода 25 и далее на сумматоре 23 формирователя 2 производится сложение символа Ко с нулем на выходе преобразователя кода 25 и запись результата на регистр 21 по сигналу bt2. Одновременно на сумматорах 35 формирователей 3...7 производится сложение содержимых регистров 31 с порядковыми номерами соответствующего формирователя проверочных символов (1...5), умноженными на О (), поступающими из блока управления на контакты 40 формирователей 3...7 с записью результата

на регистры 32 по сигналам br(l 1). Далее по сигналу bi3 осуществляется перепись содержимого регистра 21 на регистр 22 формирователя 2 и вычитание из содержимых регистров 34 ( со формирователей 3...7 содержимого регистров 32 (Ко) на вычитателях 37; результаты ( оо ) поступают на преобразователи 38 кода и затем на сумматорах 36 производится сложение О (выходы преобразователей 38) с содержимым регистров 32 (К0) и запись результатов на регистры 33 по сигналам bi3(i 1).

Во втором цикле (с 9 по 12 такты) по сигналу bi1 производится запись на регистр

20 формирователя 2 второго символа Ki, вычитание из содержимого регистра 22 (К0) содержимого регистра 20 (Ki) с преобразованием разности () на преобразователе 25, сложение полученного результата

(р () на сумматоре 23 с содержимым регистра 20(Ki) и запись результата Ki Ki+ f () на регистр 21 по сигналу Ьг. Одновременно Ki по сигналам bi1(l М) записывается на регистры 31 формирователей 3...7 и на сумматорах 35 складывается с величиной Ig (сигналы bij), поступающей на контакты 40 формирователей 3...7 с контактов 284, 289, 294, 299, 304 блока 12 управления; результаты записываются на

регистры 32 формирователей 3, ..., 7 по сигналам bi (i 1). Одновременно по сигналам Ь & 1) производится перепись содержимого регистров 33 на регистры 34. Далее на вычитателях 37 осуществляется вычитание из содержимого регистров 34 (К0) содер- жимого регистров 32 (Ki+fg), преобразование результатов на преобразователях 38 и сложение с содержимым регистров 32 на сумматорах 36 с записью суммы

Ki Ki+g+ (p (Ko-Ki-g) на регистры 33 по сигналам Ъ3 :(iЈl). Одновременно по сигналу bi3 осуществляется перепись содержимого регистра 21 на регистр 22 формирователя 2. Циклы с третьего по 15-ый аналогичны

второму, при этом в 15-м цикле по сигналу bi на регистр.20 формирователя 2 записывается последний символ «2т -2, формиру N

ется первый проверочный символ Ко и

помещается на регистр 21 формирователя 2

по сигналу bi2. Одновременно по сигналам

bi4 производится перепись предпоследних

символов -з с регистров 33 на регистры 34 формирователей 3...7 и, затем, по сиг- налам bi (i 1) - запись на регистры 33 сформированных проверочных символов со второго по шестой (.ГК) и по сигналу bi3 - перепись символа Кб на регистр 22 формирователя 2,

В следующем 16-м цикле на регистр 20 формирователя 2 по сигналу bi записывается первый принятый проверочный символ Ко производится формирование первого синдрома ошибки и по сигналу bi2 запись результате ( р (Јо-Ко)) на регистр 21 формирователя 2. Одновременно, по сигналам bi4 производится перепись проверочных символов Ki(i & 1) с.регистров 33 на регистр 34 формирователей 3...7.

В 17-м цикле на регистр 31 формирователя 3 по сигналу Ь2 записывается второй принятый проверочный символ Ki, на сумматоре 35 производится его сложение с нулем () с записью результата Ki на регистр 32 по сигналу b| и затем формирование второго синдром ошибки с записью .результата p(Ki-Ki) на регистр 33 формирователя сигналу Ьа .

Аналогично в циклах с 21 по сигналам bi3(, 4, 5, 6) на регистры 33 формирователей 4, 5, 6, 7 записываются сформированные на них с третьего по шестой синдромы ошибок А... ДБ соответственно.

Сформированные таким образом синдромы ошибок поступают на входы 96...101 арифметического блока 8, с выходов- 104, 109,111,105..106,102,108,107,112,103,110 и 113, которых поступают на входы 140...151 блока 9 вычисления коэффициентов соответственно, где сформированные коэффициенты bo, bi и D2 записываются на регистры 137, 138 и 139 соответственно по сигналу bi , поступающему на вход 155 блока. С выходов регистров 137, 138 и 139 значения коэффициентов bo. bi и b2 поступают на выходы 152, 153 и 154 блока соответственной далее на входы 183,184 и 185 блока 10 определения ошибочных позиций, где по формуле (32) вычисляется Vb4 - номер очередной позиции и сравнивается с vC4, поступающей на входы 186 блока 10 с выходов 308 блока 12 управления.

При равенстве Vb4 и УС4 элемент сравнения 174 выдает импульсы на счетчик 179,

Формула изобретения 1. Устройство для декодирования с исправлением ошибок, содержащее блок задержки, первый вход которого является информационным входом устройства, первые m параллельных выходов подключены к соответствующим информационным входам первого, второго,третьего и четвертого формирователей проверочных символов, а

соответствующий выход которого разрешает выдачу номера позиции неисправного символа с сумматора 160 через соответствующий вентиль 180, 181 или 182 на выходы

193, 192 или 191 блока соответственно и далее на входы 310, 311,312 блока управления 12, и на разрешение записи исправленных в блоке 11 символов на регистры 175, 176 и 177 и на формирование символов со,

С1 и С2, поступающих на выходы 194, 195 и 196 блока соответственно. Исправленные символы последовательно поступают на элемент ИЛИ 178 и далее с контакта 197 - на первый вход элемента И14 устройства,

откуда в сопровождении ТИ2 через элемент ИЛИ15 - на выход 19 устройства.

С входов 310, 311 и 312 блока управления 12 номера Ј , v и j неисправных символов поступают на первые входы элементов

сравнения 263, 264 и 265, на вторые входы которых с дешифратора 244 поступают номера четверок импул ьсов. При совпадении их с номерами позиций элементы сравнения разрешают выдачу ТИ2 через элементы

И269, 270, 271, ИЛИ 272 на выход 305 блока для стробирования исправления символов, а при несравнении разрешают выдачу сигналов ТИ1 через элементы И266, 267, 268 и ИЛИ 273 на выход 306 блока (сигналы ТИ1).

С выходов 306 блока управления сигналы ТИ1 поступают на вторые входы элемента И13 (фиг. 1), а с выходов 305 сигналы ТИ2 поступают на вторые входы элемента И14. Таким образом, применение пятого и

шестого формирователей проверочных символов, арифметического блока, блока вычисления коэффициентов, блока определения ошибочных позиций, решающих совместно показательное уравнение третьей степени в

поле GF(2m), позволяет определить ошибки в трех любых ошибочных символах и с помощью блоков управления, определения ошибочных позиций и блока исправления ошибок исправить их, что повышает надежность канала связи.

последовательный выход подключен к первому входу перв.ого элемента И, выход которого подключен к первому входу элемента ИЛИ. выход которого является выходом устройства, блок управления, тактовый вход и вход Пуск которого являются одновременными входами устройства, первый и второй выходы блока управления подключены соответственно к тактовому входу блока

задержки и второму входу первого элемента И. блок исправления ошибок и блок вычисления ошибочных позиций, отличающийся тем, что, с целью повышения достоверности декодирования за счет исправления до трех пачек ошибок, в устройство введены блок вычисления коэффициентов, арифметический блок, второй элемент И и пятый, шестой формирователипроверочных символов, информационные входы которых подключены к первым m параллельны.м выходам блока задержки, выходы всех формирователей проверочных символов соединены с соответствующими первыми входами блока исп- равления ошибок и входами арифметического блока, выходы которого подключены к информационным входам блока вычисления коэффициентов, выходы которого подключены к первым информационным входам блока определения ошибочных позиций, первые параллельные выходы которого подключены к вторым входам блока исправления ошибок и информационным входам блока управления, вторые выходы блока определения ошибочных позиций соединены с третьими входами блока исправления ошибок, выходы которого подключены к вторым информационным входам блока определения ошибочных позиций, последовательный выход которого подключен к первому входу второго элемента И, третий выход блока управления соединен с вторым входом второго элемента И, выход которого подключен к второму входу элемента ИЛИ, выходы первой-шестой групп выходов блока управления подключены к соответствующим управляющим входам первого-шестого формирователей проверочных символов, четвертый, пятый и шестой выходы подключены соответственно к управляющему входу блока вычисления коэффициентов и первым и второму управляющим входам блока определения ошибочных позиций.

буферного регистра подключены к входам уменьшаемого вычитэтеля, выходы которого через преобразователь кода подключены к вторым входам сумматора, управляющий вход первого буферного регистра, первый управляющий вход второго буферного регистра и управляющий вход третьего буферного регистра являются соответственно первым, вторым и третьим управляющими входами формирователя, второй выход первого буферного регистра подключен к второму управляющему входу второго буферного регистра.

первого вычитателя подключены к входам вычитаемого шестого, седьмого, восьмого и девятого вычитателей, выходы второго вы- .читателя подключены к входам вычитаемого десятого, одиннадцатого вычитателей, к входам уменьшаемого шестого вычитателя и входам первого слагаемого первого, второго и третьего сумматоров и к входам первого умножителя на два, выходы третьего вычитателя подключены к входам уменьшаемого восьмого и одиннадцатого вычитателей, к входам вычитаемого тринадцатого и четырнадцатого вычитателей, к входам первого слагаемого четвертого, пятого, шестого и седьмого сумматоров, к входам второго слагаемого первого сумматора и к входам второго умножителя на два, выходы четвертого вычитателя подключены к входам уменьшаемого седьмого, десятого и тринадцатого вычитателей, к входам первого слагаемого восьмого и девятого сумматоров и к входам второго слагаемого четвертого сумматора, выходы пятого вычитателя подключены к входам уменьшаемого двенадцатого и четырнадцатого вычитателей, выходы десятого вычитателя подключены к входам уменьшаемого девятого вычитателя и к входам первого преобразователя кода, выходы шестого, седьмого, восьмого, одиннадцатого, двенадцатого, тринадцатого и четырнадцатого вычитателей подключены к входам второго, третьего, четвертого, пятого, шестого, седьмого и восьмого преобразователя кода, выходы второго преобразователя кода подключены к входам уменьшаемого пятнадцатого и шестнадцатого вычитателей и к входам вычитаемого семнадцатого и восемнадцатого вычитателей, выходы третьего преобразователя кода подключены к входам второго слагаемого пятого сумматора и первого слагаемого десятого сумматора, выходы четвертого преобразователя кода подключены к входам второго слагаемого второго сумматора и к входам вычитаемого, девятнадцатого вычитателя, выходы первого преобразователя кода подключены к входам второго слагаемого третьего сумматора, к входам второго слагаемого седьмого сумматора и к входам вычитаемого двенадцатого вычитателя, выходы первого сумматора подключены к входам второго слагаемого десятого сумматора, выходы пятого преобразователя кода подключены к входам первого слагаемого одиннадцатого сумматора, к входам вычитаемого двадцать первого, двадцать второго и двадцать третьего вычитателей и к входам уменьшаемого двадцать четвертого и двадцать пятого вычитателей, выходы четвертого сумматора соединены с входами первого слагаемого

двенадцатого сумматора, выходы шестого преобразователя кода подключены к входам первого слагаемого тринадцатого сумматора и к входам вычитаемого двадцать шестого вычитателя, выходы седьмого преобразователя кода подключены к входам второго слагаемого двенадцатого и восьмого сумматоров, выходы восьмого преобразователя кода подключены к входам второго слагаемого девятого сумматора, выходы девятого вычитателя подключены к входам девятого преобразователя кода, выходы которого подключены к входам второго слагаемого шестого сумматора, выходы первого умножителя на два подключены к входам второго слагаемого одиннадцатого сумматора, выходы которого подключены к входам вычитаемого пятнадцатого вычитателя, выходы пятого сумматора подключены к входам уменьшаемого девятнадцатого вычитателя, выходы второго сумматора подключены к входам вычитаемого шестнадцатого вычитателя и к входам уменьшаемого семнадцатого вычитателя, выходы третьего сумматора подключены к входам уменьшаемого двадцать первого вычитателя, выходы шестого сумматора подключены к входам вычитаемого двадцать четвертого вычитателя, выходы десятого сумматора подключены к входам уменьшаемого восемнадцатого вычитателя, выходы двенадцатого сумматора подключены к входам уменьшаемого двадцать второго вычитателя, выходы седьмого сумматора подключены к входам уменьшаемого двадцать третьего вычитателя, выходы восьмого сумматора подключены к входам уменьшаемого двадцатого сумматора, выходы девятого сумматора подключены к входам уменьшаемого двадцать шестого вычитателя, выходы второго умножителя на два подключены к вторым входам тринадцатого сумматора, выходы которого подключены к входам вычитаемого двадцать пятого вычитателя, выходы восемнадцатого, двадцать первого, двадцатого, шестнадцатого, двадцать второго, семнадцатого, двадцать третьего, девятнадцатого, двадцать пятого, двадцать четвертого, двадцать, шестого и пятнадцатого вычитателей являются соответственно - двенадцатыми выходами блока.

j-ro сумматора и являются (2)-ми входами блока, выходы J-ro вычитателя через одноименный преобразователь кода соединены с входами второго слагаемого одноименного сумматора, выходы первого, третьего и пятого сумматоров подключены к входам уменьшаемого седьмого, восьмого и девятого еычитателей соответственно, выходы второго, четвертого шестого сумматоров подключены к входам вычитаемого седьмого, восьмого, девятого вычитателей соответ- ственно, выходы седьмого вычитателя соединены с входами уменьшаемого десятого вычитателя, выходы которого подключены к информационным входам первого регистра, выходы восьмого вычитателя соединены с входами вычитаемого десятого вычитателя и входами уменьшаемого одиннадцатого вычитателя, выходы которого подключены к информационным входам второго регистра, выходы девятого вычитателя соединены с входами вычитаемого одиннадцатого вычитателя и информационными входами третьего регистра, управляющие входы всех регистров объединены и являются управляющим входом блока, выходы первого-третьего регистров являются одноименными выходами блока.

вычитаемого третьего вычитателя, выходы которого через третий преобразователь кода подключены к первым входам восьмого сумматора, выходы третьего сумматора соединены с первыми входами пятого сумматора, выходы которого подключены к входам уменьшаемого третьего вычитателя, входы уменьшаемого первого вычитателя и первые входы первого и второго сумматоров во всех узлах являются первыми входами блока, вторые входы второго и четвертого и объединенные.входы второго пятого и восьмого сумматоров во всех узлах являются вторыми входами блока, вторые входы пер-. вого и первые и вторые входы третьего сумматоров во всех узлах являются третьими входами блока, выходы восьмого сумматора во всех уздах являются выходами блока.

дешифратора, первый, второй и третий выходы которого подключены к первым входам соответственно первого-шестого, седьмого-двенадцатого и тринадцатого-во- семнадцатого элементов ИЛИ, выходы пер- вой-третьей групп дешифратора соединены с вторыми входами соответственно перво- го-восемнадцатого элементов ИЛИ, выходы первого, седьмого и тринадцатого элементов ИЛИ являются первой группой выходов блока, выходы (6К+1)-го элемента ИЛИ (, 1, 2; ,6) и (1-1)-е разряды выходов четвертой и пятой групп дешифратора являются l-ми группами выходов блока, соединены с вторыми входами соответственно первого- третьего элементов сравнения, выходы Равно которых подключены к вторым входам соответственно второго-четвертого элементов И, выходы которых соединены с входами девятнадцатого элемента ИЛИ, выход которого является вторым выходом блока, выходы Не равно первого-третьего элементов сравнения подключены к вторым входам соответственно пятого-седьмого элементов И выходы которых соединены с входами двадцатого элемента ИЛИ, выход которого является третьим выходом блока, седьмой-девятый выходы дешифратора являются соответственно четвертым-шестым выходами блока.

.

&

Г5 XI

S9U6Z.I

ю

СО

г- о гГяеtiteo

oiЈ°№80

9LI о

g-гпф

L0Ј о

sn

081

ш

OSLI °ш

| Патент США № 3629824, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для декодирования с исправлением ошибок | 1986 |

|

SU1411981A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-02-23—Публикация

1990-04-28—Подача