(21)4176158/24-24

(22)06.01.87

(46) 30.07.88. Бюл. № 28

(71)Производственное объединение Краснодарский ЗИП

(72)Г,Б. Виоенский

(53)681.327(088.8)

(56)Авторское свидетельство СССР № 1012230, кл. G 06 F 3/00, 1981.

Авторское свидетельство СССР № 448458, кл. G 06 F 3/00, 1973.

(54)УСТРОЙСТВО ДЛЯ СБОРА И ПРЕДВАРИТЕЛЬНОЙ ОБРАБОТКИ ИНФОРМАЦИИ

(57)Изобретение относится к информационно-измерительной и вычислительной технике. Целью изобретения является ускорение регистрации число- импульсных сигналов. Устройство содержит п входов числоимпульсных сигналов, буферный накопитель, первый, второй и третий счетчики, регистр управления, первый и второй дешифраторы, первый, второй, третий и четвер- тьй элементы ШТИ, генератор импульсов, первый, второй, третий, четвертый и пятый элементы задержки, п буферных триггеров, группу элементов И, элемент И. Применение изобретения высвобождает полезное время процессора и повышает надежность регистрации числоимпульсных сигналов. 2 ил.

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора и предварительной обработки информации | 1981 |

|

SU1012230A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Система передачи и приема сигналов контроля | 1981 |

|

SU999081A1 |

| Устройство для вывода информации | 1983 |

|

SU1124279A1 |

| Устройство управления для доменной памяти | 1988 |

|

SU1566409A1 |

| Устройство регистрации и передачи информации для сосредоточенных объектов | 1977 |

|

SU732959A1 |

| Измеритель временных интервалов | 1983 |

|

SU1155990A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

(Л

с

00

а

Изобретение оти- :.тся к информа- ционно-измерите.гтьнчж и вычислительной технике,

Цель изобретения повышение быстродействия регистра1ши числоимпульс- ньпк сигналов, надежности их регистрации за счет осуществления подсчета числоимпульсных сигналов аппаратурными средствами самого устройства.

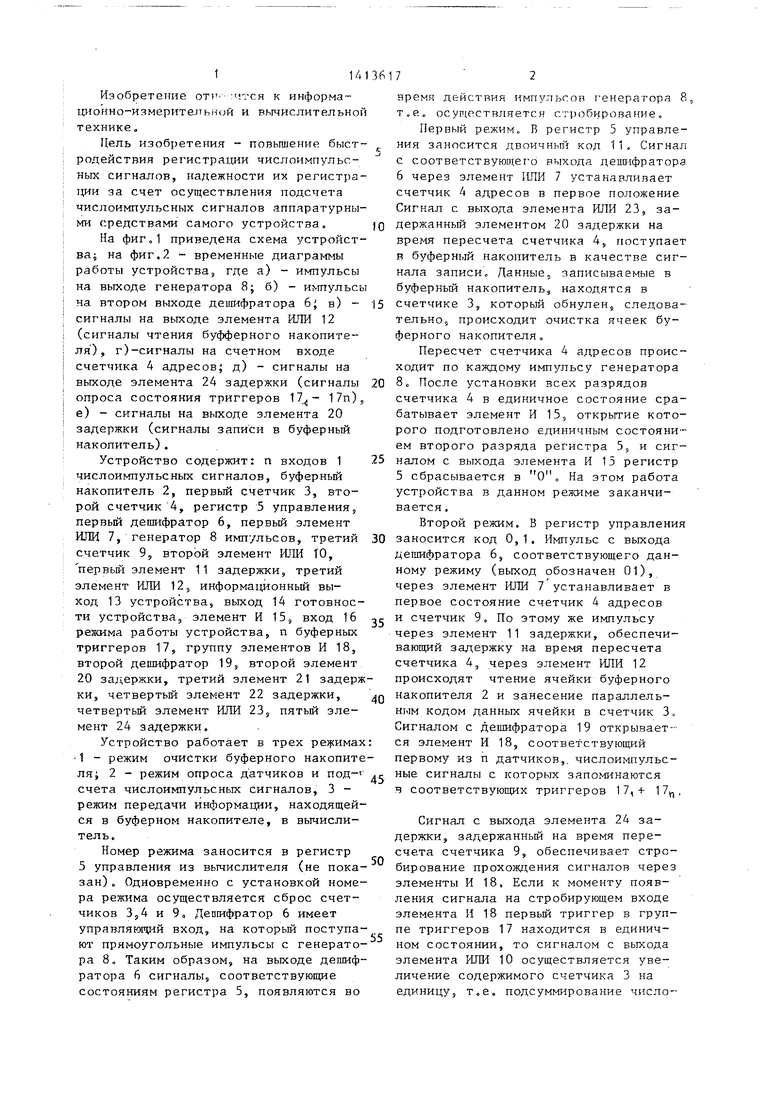

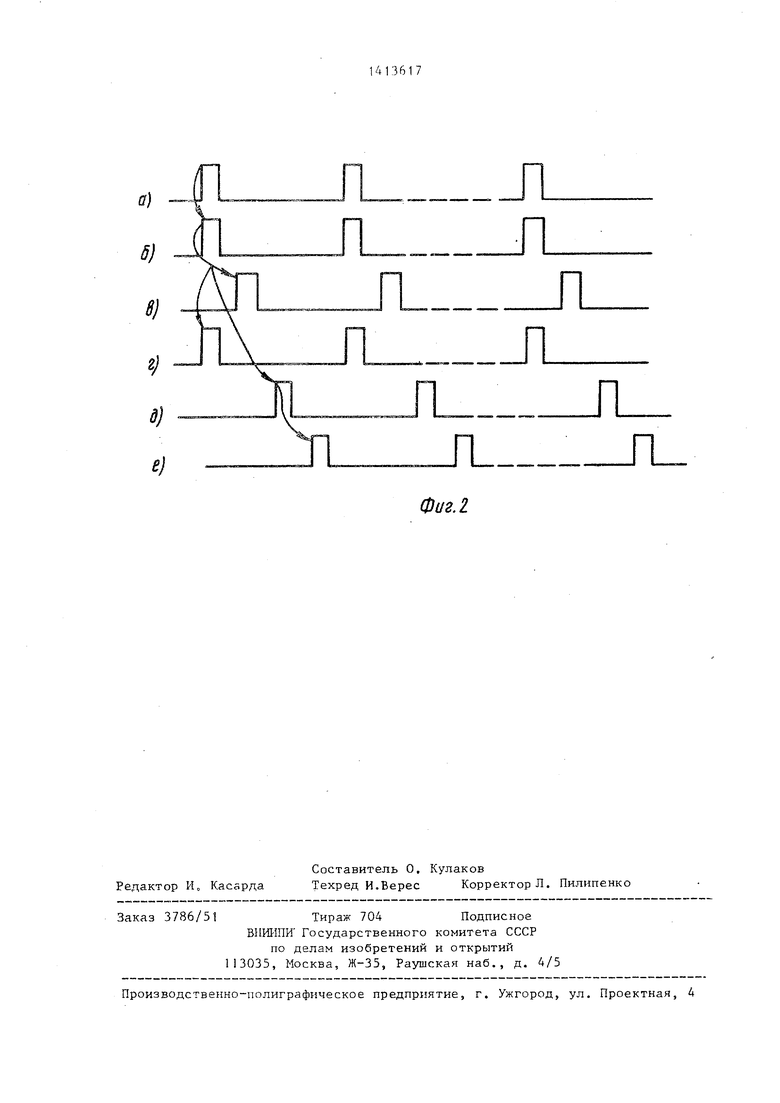

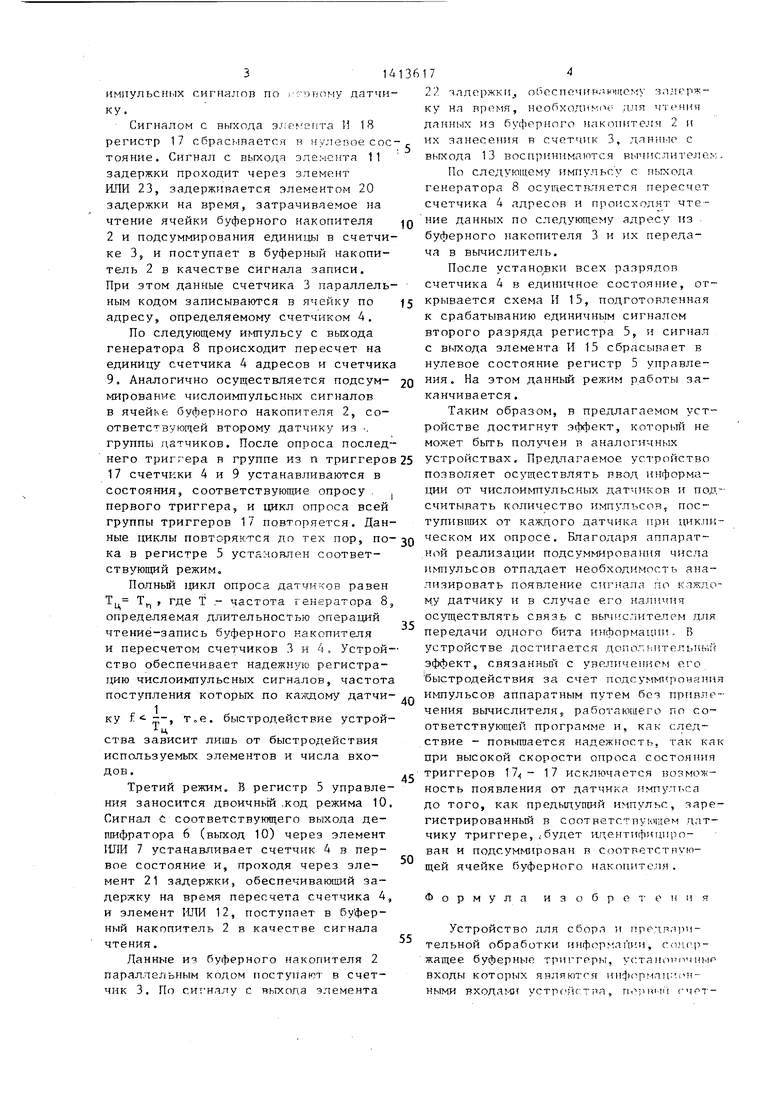

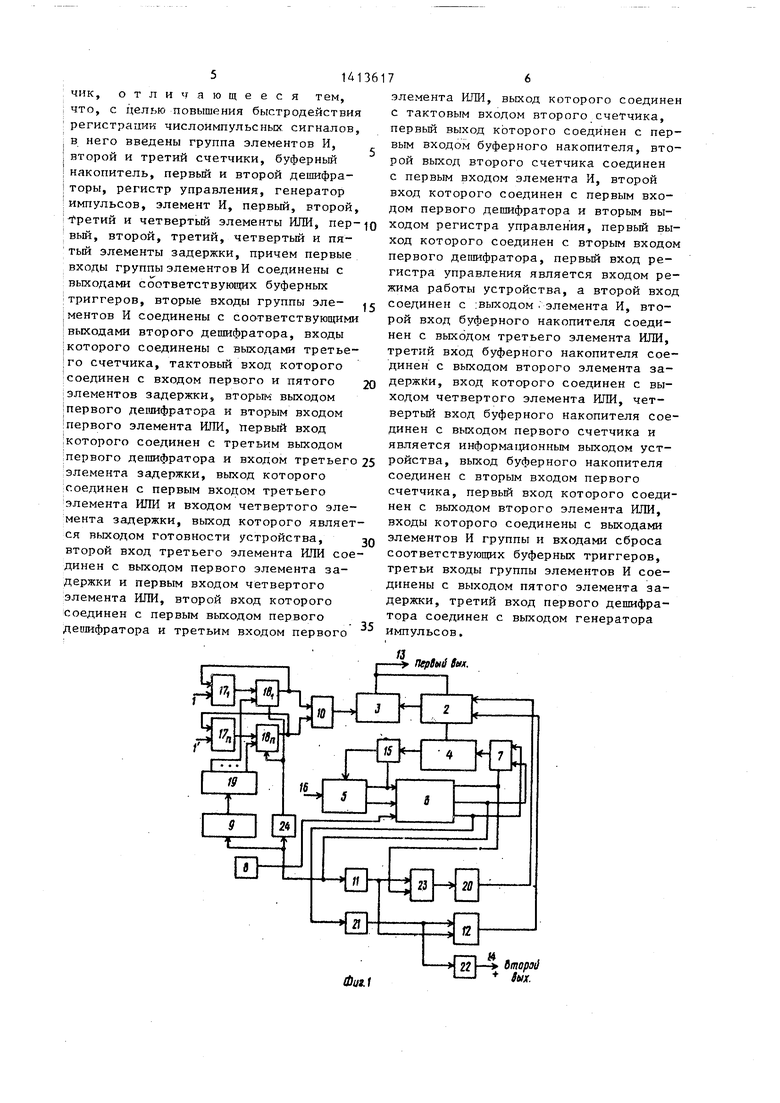

На фиг„1 приведена схема устройства; на фиг.2 - временные диаграммы работы устройства, где а) - импульсы на выходе генератора 8; б) - импульсы на втором выходе дешифратора 6 в) - сигналы на выходе элемента ИЛИ 12 (сигналы чтения буфферного накопителя) , г)-сигналы на счетном входе счетчика 4 адресов; д) - сигналы на выходе элемента 24 задержки (сигналы опроса состояния триггеров 17п)5 е) - сигналы на выходе элемента 20 задержки (сигналы записи в буферньй накопитель).

Устройство содержит: п входов 1 числоимпульсных сигналов, буферньй накопитель 2, первый счетчик 3, второй счетчик 4, регистр 5 управления5 первый дешифратор 6, первьш элемент ИЛИ 7, генератор 8 импульсов, третий счетчик 9, второй элемент Ш Ш ТО, первьм элемент 11 задержки, третий элемент ИЛИ 12, информап онный выход 13 устройства, выход 14 готовности устройства, элемент И 15, вход 16 режима работы устройства, п буферных триггеров 17, группу элементов И 18, второй дешифратор 19, второй элемент 20 задержки, третий элемент 21 задержки, четвертый элемент 22 задержки, четвертый элемент ИЛИ 23, пятьй элемент 24 задержки.

Устройство работает в трех pe)f(имax 1 - режим очистки буферного накопителя; 2 - режим опроса датчиков и счета числоимпульсных сигналов, 3 - режим передачи информации, находящейся в буферном накопителе, в вычислитель .

Номер режима заносится в регистр 5 управления из вычислителя (не показан) „ Одновременно с установкой номера режима осуществляется сброс счетчиков 3,4 и 9, Депифратор 6 имеет управляющий вход, на который поступают прямоугольные импульсы с генератора 8„ Таким образом, на выходе дешифратора 6 сигналы, соответствующие состояниям регистра 5, появляются во

время действия импулыов г-енератора 8. т.е. осуществляется стробирование„ Первый режим, В регистр 5 управления заносится двоичньй код 11 „ Сигнал с соответствующег о рьгеода деш- фратора 6 через элемент ИЛИ 7 устанавливает счетчик 4 адресов в первое положение Сигнал с выхода элемента ИЛИ 23, задержанньй элементом 20 задержки на время пересчета счетчика 4, поступает в буферный накопитель в качестве сигнала записи. Данные, записываемые в буферньш накопитель, находятся в

счетчике 3, который обнулен, следовательно, происходит очистка ячеек буферного накопителя.

Пересчет счетчика 4 адресов происходит по каждому импульсу генератора

счетчика 4 в единичное состояние срабатывает элемент И 15, открытие которого подготовлено единичным состоянием второго разряда регистра 5, и сигналом с выхода элемента И 15 регистр 5 сбрасывается в На этом работа устройства в данном режиме заканчивается .

Второй режим, В регистр управления

заносится код 0,1. Импульс с выхода дешифратора 6, соответствующего данному режиму (выход обозначен 01), через элемент ИЛИ 7 устанавливает в первое состояние счетчик 4 адресов

и счетчик 9, По этому же импульсу через элемент 11 задержки, обеспечивающий задержку на время пересчета счетчика 4, через элемент ИЛИ 12 происходят чтение ячейки буферного

накопителя 2 и занесение параллельным кодом данных ячейки в счетчик 3, Сигналом с дешифратора 19 открывает-ся элемент И 18, соответствующий

первому из п датчиков,, числоимпульсные сигналы с которых запоминаются 3 соответствующих триггеров 17,+ 17,,

Сигнал с выхода элемента 24 задержки, задержанньй на время пересчета счетчика 9, обеспечивает стро- бирование прохождения сигналов через элементы И 18. Если к моменту появления сигнала на стробирующем входе элемента И 18 первьй триггер в группе триггеров 17 находится в единичном состоянии, то сигналом с выхода элемента HTDi 10 осуществляется увеличение содержимого счетчика 3 на единицу, т,е, подсуммирование число

им1тульсных сигналов по i датчику.

Сигналом с выхода И 18 регистр 17 сбрас.вается в нулевое состояние. Сигнал с выхода элемента 11 задержки проходит через элемент ИЛИ 23, задерживается элементом 20 задержки на время, затрачиваемое на чтение ячейки буферного накопителя 2 и подсуммирования единицы в счетчике 3, и поступает в буферный накопитель 2 в качестве сигнала записи. При этом данные счетчика 3 параллельным кодом записываются в ячейку по адресу, определяемоьгу счетчиком 4.

По следующему импульсу с выхода генератора 8 происходит пересчет на единицу счетчика 4 адресов и счетчика 9. Аналогично осуществляется подсум- мирование числоимпульсных сигналов в ячейке буферного накопителя 2, соответствующей второму датчику из -. группы датчиков. После опроса последнего триггера в группе из п триггеров 17 счетчкки 4 и 9 устанавливаются в состояния, соответствующие опросу , первого триггера, и цикл опроса всей группы триггеров 17 повторяется. Данные циклы повторяются до тех пор, пока в регистре 5 установлен соответствующий режим.

Полньй и;икл опроса датчиков равен Тц Т , где Т - частота генератора 8, определяемая длительностью операций чтение-запись буферного накопителя и пересчетом счетчиков 3 и 4 Устройство обеспечивает надежную регистра- }щю числоимпульсных сигналов, частота поступления которых по ка/адому датчику f ;:; т.е. быстродействие устрой цства зависит лишь от быстродействия

используемых элементов и числа входов.

Третий режим. В регистр 5 управления заносится двоичньгй .код режима 10. Сигнал с соответствующего выхода дешифратора 6 (выход 10) через элемент ШМ 7 устанавливает счетчик 4 в первое состояние и, проходя через элемент 21 задержки, обеспечивающий задержку на время пересчета счетчика 4, и элемент ИЛИ 12, поступает в буферный накопитель 2 в качестве сигнала чтения.

Данные из буферного накопителя 2 параллельным кодом поступают в счетчик 3. По сит налу с выхода элемента

чалержк, oбecпeчиF, s.-ijirv

0

5

0

5

0

5

0

5

0

5

ку нл время, необходимое для данных из буферного нпкопителя 2 и их занесения в счетчик 3, дянн1 1е с выхода 13 воспринимаются вычислителем,

По следующему импульсу с пыхода генератора 8 осуществляется пересчет счетчика 4 адресов и происходят чтение данных по следующему адресу из буферного накопителя 3 и их передача в вычислитель.

После устанозки всех разрядов счетчика 4 в единичное состояние, открывается схема И 15, подготовленная к срабатыванию единичным сигналом второго разряда регистра 5, и сигнал с выхода элемента И 15 сбрасывает в нулевое состояние регистр 5 управления. На этом данный режим работы заканчивается .

Таким образом, в предлагаемом устройстве достигнут эффект, который не может быть получен в аналогичных устройствах. Предлагаемое устройство позволяет осуществлять ввод информации от чиcлoи myльcныx и под-- считывать количество и тульсов5 поступивших от каячдого датчика при циклическом их опросе. Благодаря аппаратной peaлизaIJJiи подсуммирования числа иьшульсов отпадает необходимость анализировать появление сигнала по клждо- м,у датчику и в случае его наличия осуществлять связь с вычислителем для передачи одного бита и}тформации. В устройстве достигается дополнительны эффект, связанный с увеличением его быстродействия за счет подсумкиронаиия импульсов аппаратным путем без привлечения вычислителя, работающего по соответствующей программе и, как следствие - повышается надежность, так как при высокой скорости опроса состояния триггеров 17 исключается возможность появления от датчика импулт са до того, как предыдущий импульс, зарегистрированный в соответствующем датчику триггере, ;будет идентифицирован и подсуммирован в соответстпую- щей ячейке буферного накопителя.

Формула изобретения

Устройство для сбора и предрлри- тельной обработки информа1 1ии, c;i.4pp жащее буферные триггеры, устаноипчиые входы которых являются ииформлц: Р(- ными входа -от устро к-.т71а, пернми смет5U1

чик, отличающееся тем, ; что, с целью повышения быстродействия регистрации числоимпульсных сигналов, i в него введены группа элементов И, I второй и третий счетчики, буферный I накопитель, первый и второй дешифра- торы, регистр управления, генератор I импульсов, элемент И, первый, второй, i третий и четвертый элементы ИЛИ, пер- вый, второй, третий, четвертый и пя- тьй элементы задержки, причем первые входы группы элементов И соединены с выходами соответствующих буферных I триггеров, вторые входы группы эле- I ментов И соединены с соответствующими I выходами второго дешифратора, входы которого соединены с выходами третье- I го счетчика, тактовый вход которого Iсоединен с входом первого и пятого iэлементов задержки, вторым выходом I первого дешифратора и вторым входом первого элемента ИЛИ, первый вход iKoToporo соединен с третьим выходом ;первого дешифратора и входом третьего элемента задержки, выход которого соединен с первым входом третьего элемента ИЛИ и входом четвертого элемента задержки, выход которого являет ся выходом готовности устройства, второй вход третьего элемента ИЛИ сое динен с выходом первого элемента задержки и первым входом четвертого элемента ИЛИ, второй вход которого соединен с первым выходом первого дешифратора и третьим входом первого

-

10

15

36176

элемента ИЛИ, выход которого соединен с тактовым входом второго счетчика, первьй выход которого соединен с первым входом буферного накопителя, второй выход второго счетчика соединен с первым входом элемента И, второй вход которого соединен с первым входом первого дешифратора и вторым выходом регистра управления, первьй выход которого соединен с вторым входом первого дешифратора, первый вход регистра управления является входом режима работы устройства, а второй вход соединен с :выходом .элемента И, второй вход буферного накопителя соединен с выходом третьего элемента ИЛИ, третий вход буферного накопителя соединен с выходом второго элемента задержки, вход которого соединен с выходом четвертого элемента ИЛИ, чет- вертьш вход буферного накопителя соединен с выходом первого счетчика и является информационным выходом устройства, выход буферного накопителя соединен с вторым входом первого счетчика, первый вход которого соединен с выходом второго элемента ИЛИ, входы которого соединены с выходами элементов И группы и входами сброса соответствующих буферных триггеров, третьи входы группы элементов И соединены с выходом пятого элемента задержки, третий вход первого дешифратора соединен с выходом генератора импульсов.

20

25

30

35

п

л

п.

л

Фиг. 2

Авторы

Даты

1988-07-30—Публикация

1987-01-06—Подача