Изобретение относится к импульсной технике и может быть использовано при построении асинхронных логических схем и апериодических автоматов.

Цель изобретения - повышение надежности парафазной логической КМОП-схемы путем ее минимизации.

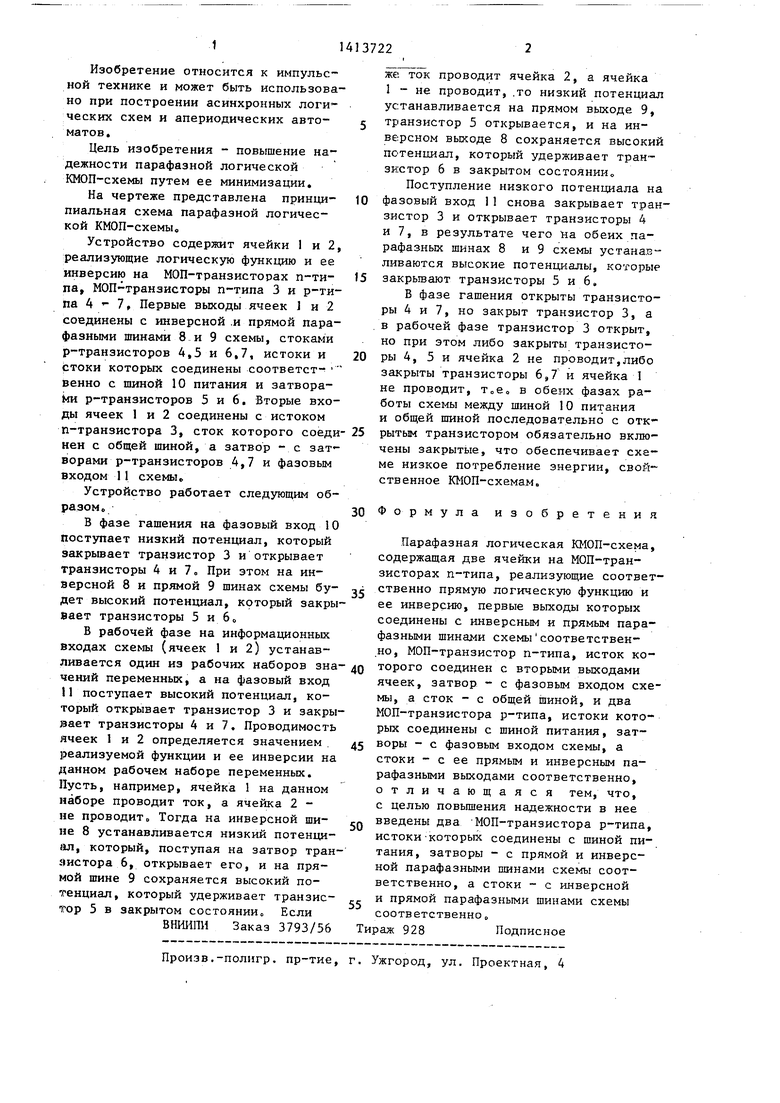

На чертеже представлена принципиальная схема парафазной логической КМОП-схемы,

Устройство содержит ячейки 1 и 2, реализующие логическую функцию и ее инверсию на МОП-транзисторах п-ти- па, МОП-транзисторы п-типа 3 и р-ти- па 4 7, Первые выходы ячеек и 2 соединены с инверсной .и прямой пара- фазными шинами 8 и 9 схемы, стоками р-транзисторов 4,5 и 6,7, истоки и стоки которых соединены соответст- венно с шиной 10 питания и затвора- iw р-транзисторов 5 и 6, Вторые входы ячеек 1 и 2 соединены с истоком п-транзистора 3, сток которого соединен с общей шиной, а затвор - с затворами р-транзисторов 4,7 и фазовым входом 11 схемы.

Устройство работает следующим образом.

В фазе гашения на фазовый вход 10 поступает низкий потенциал, который закрьюает транзистор 3 и открывает транзисторы 4 и 7о При этом на ин- йерсной 8 и прямой 9 шинах схемы будет высокий потенциал, который закрывает транзисторы 5 и 6о

В рабочей фазе на информационных входах схемы (ячеек 1 и 2) устанавливается один из рабочих наборов значений переменных, а на фазовый вход II поступает высокий потенциал, который открывает транзистор 3 и закрывает транзисторы 4 и 7. Проводимость ячеек 1 и 2 определяется значением реализуемой функции и ее инверсии на данном рабочем наборе переменных. Пусть, например, ячейка 1 на данном наборе проводит ток, а ячейка 2 - не проводит. Тогда на инверсной шине 8 устанавливается низкий потенци- &л, который, поступая на затвор транзистора 6, открывает его, и на прямой шине 9 сохраняется высокий потенциал, который удерживает транзистор 5 в закрытом состоянии Если

ВИИ1ШИ Заказ 3793/56

же ток проводит ячейка 2, а ячейка 1 - не проводит, .то низкий потенциал устанавливается на прямом выходе 9,

транзистор 5 открывается, и на инверсном выходе 8 сохраняется высокий потенциал, который удерживает транзистор 6 в закрытом состоянии.

Поступление низкого потенциала на

фазовый вход 1 1 снова закры1вает транзистор 3 и открывает транзисторы 4 и 7, в результате чего на обеих па- рафазных шинах 8 и 9 схемы устанавливаются высокие потенциалы, которые

закрьшают транзисторы 5 и 6,

В фазе гашения открыты транзисторы 4 и 7, но закрыт транзистор 3, а . в рабочей фазе транзистор 3 открыт, но при этом либо закрыты транзисторы 4, 5 и ячейка 2 не проводит,либо закрыты транзисторы 6,7 и ячейка 1 не проводит, т„ео в обеих фазах работы схемы между шиной 10 питания и общей шиной последовательно с открытым транзистором обязательно включены закрытые, что обеспечивает схеме низкое потребление знергии, свой ственное КМОП-схемам

Формула изобретения

Парафазная логическая КМОП-схема, содержащая две ячейки на МОП-транзисторах п-типа, реализующие соответственно прямую логическую функцию и ее инверсию, первые выходы которых соединены с инверсным и прямым пара- фазными шинами схемы соответственно, МОП-транзистор п-типа, исток которого соединен с вторыми выходами ячеек, затвор - с фазовым входом схемы, а сток - с общей шиной, и два МОП-транзистора р-типа, истоки которых соединены с шиной питания, затворы - с фазовым входом схемы, а стоки - с ее прямым и инверсным па- рафазными выходами соответственно, отличающаяся тем, что, с целью повышения надежности в нее

введены два МОП-транзистора р-типа, истоки-которых соединены с шиной питания, затворы - с прямой и инверсной парафазными шинами схемы соответственно, а стоки - с инверсной и прямой парафазными шинами схемы соответственно„ ираж 928 Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Г-ТРИГГЕР | 2007 |

|

RU2371842C2 |

| ЛОГИЧЕСКОЕ КОНВЕЙЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2175811C1 |

| КОМПЛЕМЕНТАРНЫЙ МИКРОЭЛЕКТРОМЕХАНИЧЕСКИЙ ИНВЕРТОР | 2005 |

|

RU2290753C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером | 2019 |

|

RU2725781C1 |

| Устройство для сравнения двух @ -разрядных двоичных чисел | 1988 |

|

SU1594683A1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с нулевым спейсером | 2019 |

|

RU2725780C1 |

| СДВИГОВЫЙ РЕГИСТР (ВАРИАНТЫ) | 2013 |

|

RU2530271C1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| Способ сравнения данных в ячейке ассоциативного запоминающего устройства и модуль сравнения данных в ячейке ассоциативного запоминающего устройства | 2018 |

|

RU2680870C1 |

Изобретение может быть использовано при построении асинхронных .логических схем и апериодических автоматов. Устройство содержит ячейки 1 и 2, реализующие логическую функцию инверсию на МОП-транэисторах (т) п-типа 3 и р-типа 4-7. В рабочей фазе на фазовый вход поступает высокий потенциал, открывающий Т 3 и закрьшакаций Т 4 и 7. Проводимость ячеек 1 и 2 определяется значением реализуемой функции и ее инверсией на данном наборе переменных. При поступлении низкого потенциала на фазовый вход 11 Т 3 закрывается, а Т 4 и 7 открывается. В результате на парафазных шинах 8 и 9 схемы устанавливаются высокие потенциалы, закрывающие Т 5 и 6. В фазе гашения Т 4 и 7 открыты, Т 3 закрыт, а в рабочей фазе Т 3 открыт, но при этом либо закрыты Т 4 и 5 и ячейка 2 не проводит, либо закрыты Т 6 и 7 и ячейка 1 не проводит. Таким образом, между шиной 10 питания и общей шиной последовательно с открытььм Т обязательно включены закрытые Т, что обеспечивает : схеме низкое потребление энергии, свойственное КМОП-схемам, и повышает ее надежность. 1 ил. (Л 42ь ОЭ 1чЭ

Авторы

Даты

1988-07-30—Публикация

1986-11-17—Подача