Гистерезисный триггер (Г-триггер) относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных вычислительных устройств и систем цифровой обработки информации

Известен Г-триггер [1], содержащий (n+1) КМОП инверторов, резистор, МОП транзисторы с каналом р- и n-типа проводимости (в дальнейшем р-транзисторы и n-транзисторы).

Недостаток известного устройства - большое потребление энергии и низкое быстродействие.

Более близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является Г-триггер [2], содержащий (n+1) КМОП инверторов, резистор, транзисторы р- и n-типа.

Недостаток прототипа - низкое быстродействие.

Задача, решаемая в изобретении, заключается в повышении быстродействия.

Это достигается тем, что в Г-триггере, содержащем n входов, КМОП инвертор, логический элемент с инверсией, р-транзистор и n-транзистор, причем вход инвертора подключен к n-му входу триггера, затворы р-транзистора и n-транзистора соединены с выходом логического элемента с инверсией и выходом триггера, введены (n-1) блоков разрешения хранения на выходе триггера низкого уровня и (n-1) блоков разрешения хранения на выходе триггера высокого уровня, входы блоков разрешения обоих типов подключены к соответствующим первым (n-1) входам Г-триггера, выходы блоков разрешения хранения на выходе триггера низкого уровня соединены с истоком р-транзистора, выходы блоков разрешения хранения на выходе триггера высокого уровня соединены с истоком n-транзистора, стоки р- и n-транзисторов подключены к выходу инвертора и входу логического элемента с инверсией.

Предлагаемое устройство удовлетворяет критерию "существенные отличия". Использование КМОП инверторов, логических элементов с инверсией и МОП транзисторов с каналом р- и n-типа проводимости в составе принципиальных схем элементов Г-триггеров известно. Однако использование их в данном случае позволило достичь эффекта, выраженного целью изобретения.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны, устройство может считаться имеющим существенные отличия.

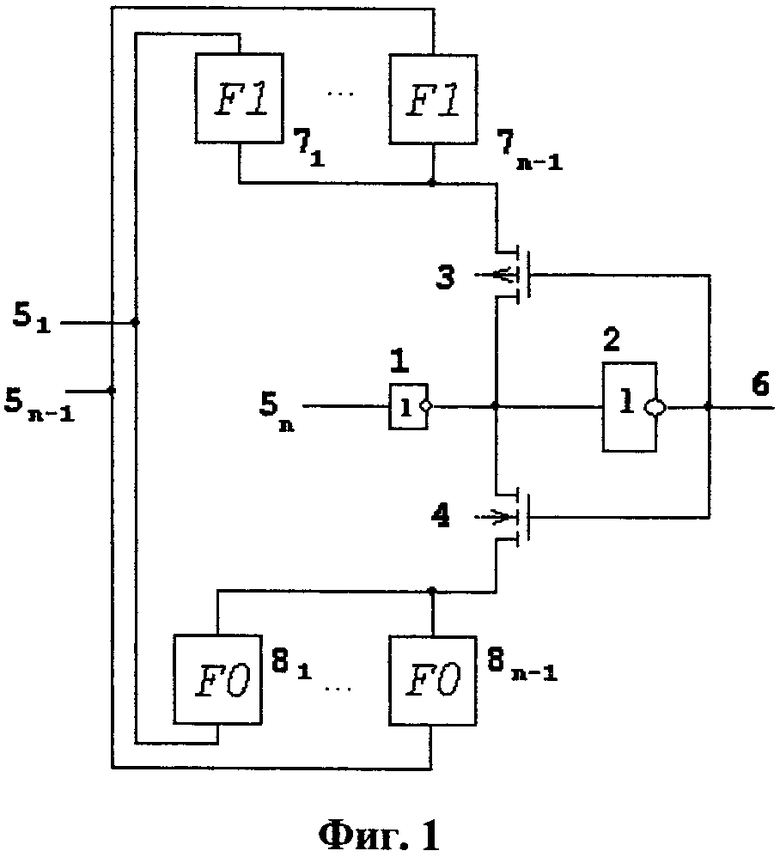

На фиг.1 изображена схема Г-триггера. В простейшем случае логический элемент с инверсией реализуется инвертором.

Схема Г-триггера содержит два инвертора 1-2, р-транзистор 3, n-транзистор 4, n входов 51-5n, выход 6, (n-1) блоков разрешения хранения на выходе триггера низкого уровня 71-7n-1, выполненных на р-транзисторах, и (n-1) блоков разрешения хранения на выходе триггера высокого уровня 81-8n-1, выполненных на n-транзисторах, вход инвертора 1 соединен с n-ым входом триггера 5n, входы блоков разрешения обоих типов подключены к соответствующим первым (n-1) входам Г-триггера 51-5n-1, выходы блоков разрешения хранения на выходе триггера низкого уровня 71-7n-1 соединены с истоком р-транзистора 3, выходы блоков разрешения хранения на выходе триггера высокого уровня 81-8n-1 соединены с истоком n-транзистора 4, стоки р- и n-транзисторов 3 и 4 подключены к выходу инвертора 1 и входу инвертора 2, затворы транзисторов 3 и 4 подключены к выходу инвертора 2 и выходу триггера 6.

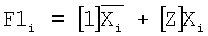

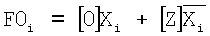

Блоки разрешения хранения на выходе триггера низкого уровня 71-7n-1 (F1) обеспечивают коммутацию истока р-транзистора 3 на шину питания до тех пор, пока хотя бы один из входов Г-триггера 51-5n-1 находится в состояния логического нуля (низкий уровень сигнала). Функция i-го блока описывается логической формулой:

,

,

где Ii - вход блока 5i, i=1…(n-1); Z - состояние высокого импеданса. Формула показывает, что при значении входа Ii=0 на выход F1i блока передается состояние логической "1" (высокий уровень, шина питания), а при Ii=1 выход блока заперт (высокоимпедансное, или третье состояние).

Блоки разрешения хранения на выходе триггера высокого уровня 81-8n-1 (F0) обеспечивают коммутацию истока n-транзистора 4 на общую шину до тех пор, пока хотя бы один из входов Г-триггера 51-5n-1 находится в состояния логической единицы (высокий уровень сигнала). Функция i-го блока описывается логической формулой:

.

.

Формула показывает, что при значении входа Ii=1 на выход F1i блока передается состояние логического "0" (низкий уровень, общая шина), а при Ii=0 выход блока заперт (высокоимпедансное, или третье состояние).

Транзисторы р- и n-типа 3 и 4 выполняют роль ключа, коммутирующего на вход инвертора 2 выходы блоков 71-7n-1 и 81-8n-1 в зависимости от уровня сигнала на выходе 6: при низком уровне на выходе 6 открыт р-транзистор и на вход инвертора 2 поступает сигнал с выходов блоков 71-7n-1; при высоком уровне на выходе 6 открыт n-транзистор и на вход инвертора 2 поступает сигнал с выходов блоков 81-8n-1. Инвертор 1 служит для завершения переключения Г-триггера, когда все входы 51-5n-1 перейдут в одинаковое состояние, противоположное по отношению к предыдущему состоянию.

Если все входы 51-5n-1 находятся в одинаковом состоянии, то лишь одна из групп блоков 71-7n-1 или 81-8n-1 обеспечивает коммутацию соответствующего транзистора к источнику питания или общей шине.

Особенности данной схемы по сравнению с прототипом следующие.

К входу инвертора 2 оказываются подключенными только один инвертор 1 и по одному транзистору р- и n-типа, в то время как в прототипе к этой точке подключена (n-1) пара транзисторов р- и n-типа, создавая большую паразитную емкость за счет диффузионных емкостей областей стоков транзисторов обоих типов, увеличивающую задержку переключения Г-тригтера в обоих направлениях. Действительно, в КМОП схемотехнике задержка переключения элементов обусловлена перезарядом нагрузочных и паразитных емкостей входов, выходов элементов и трассмежсоединений. Поэтому чем меньше перезаряжаемая емкость, тем скорее завершается ее перезаряд и переключение элементов схемы.

Таким образом, предлагаемое устройство обеспечивает меньшую задержку переключения. Цель изобретения достигнута.

Схема работает следующим образом.

Пусть в исходном состоянии на выходе Г-триггера 6 присутствует уровень логического "0". Тогда открыт р-транзистор 3 и, если хотя бы на одном из входов

51-5n-1 задан низкий уровень, вход инвертора 2 через транзистор 3 и соответствующий блок 7i подключается к шине питания, подтверждая низкий уровень на его выходе. Когда все входы 51-5n-1 перейдут в состояние логической "1" (высокий уровень), блоки 71-7n-1, реализованные на КМОП транзисторах р-типа, окажутся закрытыми и вход инвертора 2 будет отключен от шины питания через транзистор 3. Однако, поскольку n-транзистор 4 закрыт по затвору из-за низкого уровня на выходе 6, инвертор 2 переключится в противоположное состояние только после того, как вход 5n также перейдет в состояние логической "1" и выход инвертора 1 переключится в состояние логического "0".

Пусть в исходном состоянии на выходе Г-триггера 6 присутствует уровень логической "1". Тогда открыт n-транзистор 4 и, если хотя бы на одном из входов 51-5n-1 задан высокий уровень, вход инвертора 2 через транзистор 4 и соответствующий блок 7i подключается к общей шине, подтверждая высокий уровень на его выходе. Когда все входы 51-5n-1 перейдут в состояние логического "0" (низкий уровень), блоки 81-8n-1, реализованные на КМОП транзисторах n-типа, окажутся закрытыми и вход инвертора 2 будет отключен от общей шины через транзистор 4. Однако, поскольку р-транзистор 3 в этот момент закрыт по затвору из-за высокого уровня на выходе 6, инвертор 2 переключится в противоположное состояние только после того, как вход 5n также перейдет в состояние логического "0" и выход инвертора 1 переключится в состояние логической "1".

Инвертор 1 реализован таким образом, что в том случае, когда вход 5n переключается в противоположное состояние не самым последним из входов 51-5n, инвертор 1 не способен изменить потенциал точки входа инвертора 2 настолько, чтобы привести к переключению выхода инвертора 2 в противоположное состояние. На практике это достигается разными способами:

1) Подбором размеров транзисторов в составе инвертора 1, блоков 71-7n-1 и 81-8n-1 и транзисторов 3 и 4 (для реализации в составе заказной БИС): транзисторы инвертора 1 должны иметь отношение ширины канала к его длине в m раз меньше, чем аналогичное соотношение для транзисторов противоположного типа 3 и 4 и в блоках 71-7n-1 и 81-8n-1,

2) Заменой одиночных КМОП транзисторов в инверторе на последовательное соединение m транзисторов соответствующего типа с общим затвором (для реализации на основе базовых матричных кристаллов),

3) Использованием резистора между выходом инвертора 1 и узлом схемы, в котором соединяются стоки транзисторов р-типа 3 и n-типа 4 с входом инвертора 2.

Значение коэффициента m в первых двух случаях выбирается в диапазоне 4-8 в зависимости от пороговых напряжений транзисторов и параметров технологии изготовления микросхемы с данным Г-триггером. Номинал резистора в последнем случае выбирается таким, чтобы преждевременное переключение инвертора 1 не приводило к существенному изменению потенциала на входе инвертора 2, достаточному для его переключения в противоположное состояние.

В результате Г-триггер выполняет логическую функцию

G=I1·I2…·In+G·(I1+I2+…+In),

где I1,I2,…,In - входы элемента 51-5n, a G - его выход 6.

В простейшем случае каждый блок 71 реализуется одним р-транзистором, а блок 81 - одним n-транзистором, как показано на фиг.2; р-транзистор 9 подключен истоком к шине питания 10, затвором - к входу блока, а стоком - к его выходу, n-транзистор 11 подключен истоком к общей шине 12, затвором - к входу блока, а стоком - к его выходу. Входами являются инфазные сигналы индикации окончания переходных процессов в элементах индицируемой схемы.

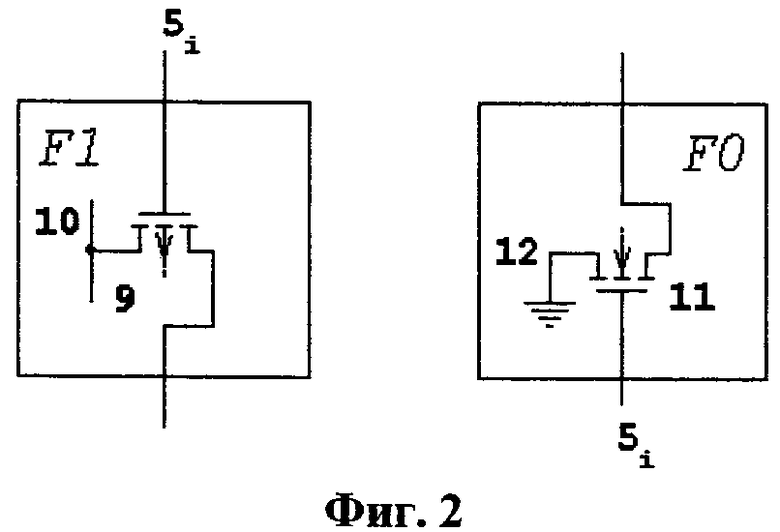

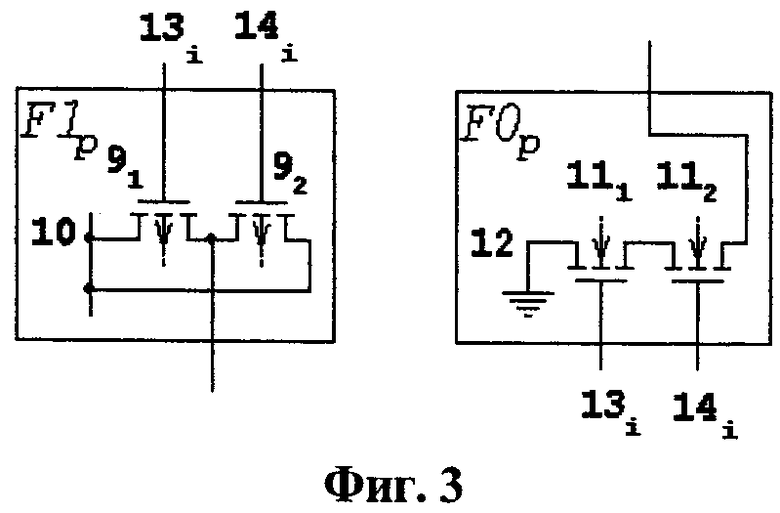

На практике, однако, для индикации окончания процесса переключения самосинхронной схемы используются не только инфазные, но и парафазные сигналы. Каждый парафазный сигнал состоит из двух составляющих: прямой и инверсной. Парафазный сигнал характеризуется двумя состояниями: спейсерным, когда обе его составляющие принимают одинаковое значение, и рабочим, когда значения составляющих противоположно. Спейсерное состояние для каждого парафазного сигнала только одно - "00" (нулевое) или "11" (единичное). Рабочих состояний у каждого парафазного сигнала два: "01" и "10". В процессе работы самосинхронной схемы спейсерное и рабочее состояние парафазного сигнала чередуются, переход из текущего рабочего состояния в следующее может происходить только через спейсерное состояние, что позволяет успешно контролировать с помощью Г-триггера окончание переключения схемы в очередную фазу работы: спейсерную или рабочую.

На фиг.3 представлена реализация блоков разрешения хранения на выходе триггера низкого и высокого уровня для парафазных входов с единичным спейсером. Блок разрешения хранения на выходе триггера низкого уровня содержит два р-транзистора 91 и 92, истоки которых подключены к шине питания 10, стоки - к выходу блока, а затворы - к прямой 13i и инверсной 14i составляющим парафазного входа. Блок разрешения хранения на выходе триггера высокого уровня содержит два n-транзистора 111 и 112, исток транзистора 111 подключен к общей шине 12, его сток - к истоку транзистора 112, а затвор - к прямой составляющей парафазного входа 13i, сток транзистора 112 подключен к выходу блока, а затвор - к инверсной составляющей парафазного входа 14i.

Парафазный вход {13i, 14i} с единичным спейсером может принимать одно из трех состояний: {13i, 14i}={11, 01, 10}. Два последних являются рабочими. Переход из одного рабочего состояния в следующее, даже совпадающее по значению с предыдущим, выполняется только через спейсерное состояние, которое также должно быть проиндицировано на выходе Г-триггера.

В спейсере все парафазные входы Г-триггера находятся в состоянии "11". В этом случае все блоки 71-7n-1 закрыты, а блоки 81-8n-1 - открыты и коммутируют исток n-транзистора 4 с общей шиной. Если при этом и инфазный вход 5n находится в спейсере (состоянии логической "1"), то выход инвертора 2 также будет находиться в состоянии спейсера (логической "1"). В противном случае, если инфазный вход 5n находится в рабочем состоянии (логического "0"), то выход инвертора 2, являющийся выходом Г-триггера 6, будет хранить свое предыдущее значение.

Если все парафазные входы находятся в любом рабочем состоянии, причем i-й и k-й парафазные входы могут находиться в разных рабочих состояниях, то блоки 81-8n-1 закрыты, а блоки 71-7n-1 открыты и коммутируют исток р-транзистора 3 с шиной питания. Если при этом и инфазный вход 5n находится в рабочем состоянии (логического "0"), то выход инвертора 2 также будет находиться в рабочем состоянии (логического "0"). В противном случае, если инфазный вход 5n находится в спейсере (состоянии логической "1"), то выход инвертора 2, являющийся выходом Г-триггера 6, будет хранить свое предыдущее значение.

Таким образом, для переключения выхода Г-триггера 6 в рабочее состояние необходимо и достаточно, чтобы все парафазные входы {13i, 14i}, i=1…(n-1), и инфазный вход 5n находились в рабочем состоянии. И, наоборот, для переключения выхода Г-триггера в спейсер (логическую "1") необходимо и достаточно, чтобы все парафазные входы {13i, 14i}, i=1…(n-1), и инфазный вход 5ц находились в спейсере (логической "1").

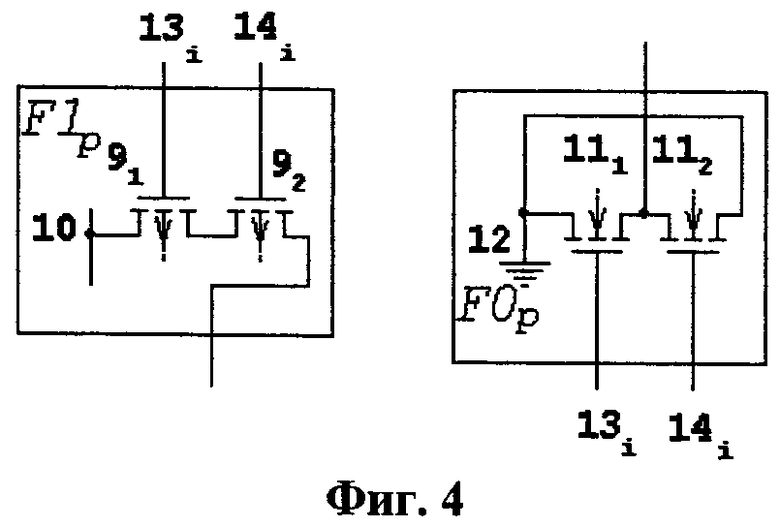

На фиг.4 представлена реализация блоков разрешения хранения на выходе триггера низкого и высокого уровня для парафазных входов с нулевым спейсером. Блок разрешения хранения на выходе триггера низкого уровня содержит два р-транзистора 91 и 92, исток транзистора 91 подключен к шине питания 10, его сток - к истоку транзистора 92, а затвор - к прямой составляющей парафазного входа 13i, сток транзистора 92 подключен к выходу блока, а затвор - к инверсной составляющей парафазного входа 14i. Блок разрешения хранения на выходе триггера высокого уровня содержит два n-транзистора 111 и 112, истоки которых подключены к общей шине 12, стоки - к выходу блока, а затворы - к прямой 13i и инверсной 14i составляющим парафазного входа.

Парафазный вход {13i, 14i} с нулевым спейсером может принимать одно из трех состояний: {13i, 14i}={00, 01, 10}. Два последних являются рабочими. Переход из одного рабочего состояния в следующее, даже совпадающее по значению с предыдущим, выполняется только через спейсерное состояние, которое также должно быть проиндицировано на выходе Г-триггера.

В спейсере все парафазные входы Г-триггера находятся в состоянии "00". В этом случае все блоки 81-8n-1 закрыты, а блоки 71-7n-1 - открыты и коммутируют исток р-транзистора 3 с шиной питания. Если при этом и инфазный вход 5n находится в спейсере (состоянии логического "0"), то выход инвертора 2 также будет находиться в состоянии спейсера (логического "0"). В противном случае, если инфазный вход 5n находится в рабочем состоянии (логической "1"), то выход инвертора 2, являющийся выходом Г-триггера 6, будет хранить свое предыдущее значение.

Если все парафазные входы находятся в любом рабочем состоянии, причем 1-й и k-й парафазные входы могут находиться в разных рабочих состояниях, то блоки 71-7n-1 закрыты, а блоки 81-8n-1 открыты и коммутируют исток n-транзистора 4 с общей шиной. Если при этом и инфазный вход 5n находится в рабочем состоянии (логической "1"), то выход инвертора 2 также будет находиться в рабочем состоянии (логической "1"). В противном случае, если инфазный вход 5n находится в спейсере (состоянии логического "0"), то выход инвертора 2, являющийся выходом Г-триггера 6, будет хранить свое предыдущее значение.

Таким образом, для переключения выхода Г-триггера 6 в рабочее состояние необходимо и достаточно, чтобы все парафазные входы {13i, 14i}, i=1…(n-1), и инфазный вход 5n находились в рабочем состоянии. И наоборот, для переключения выхода Г-триггера в спейсер (логический "0") необходимо и достаточно, чтобы все парафазные входы {13i, 14i}, i=1…(n-1) и инфазный вход 5n находились в спейсере (логическом "0").

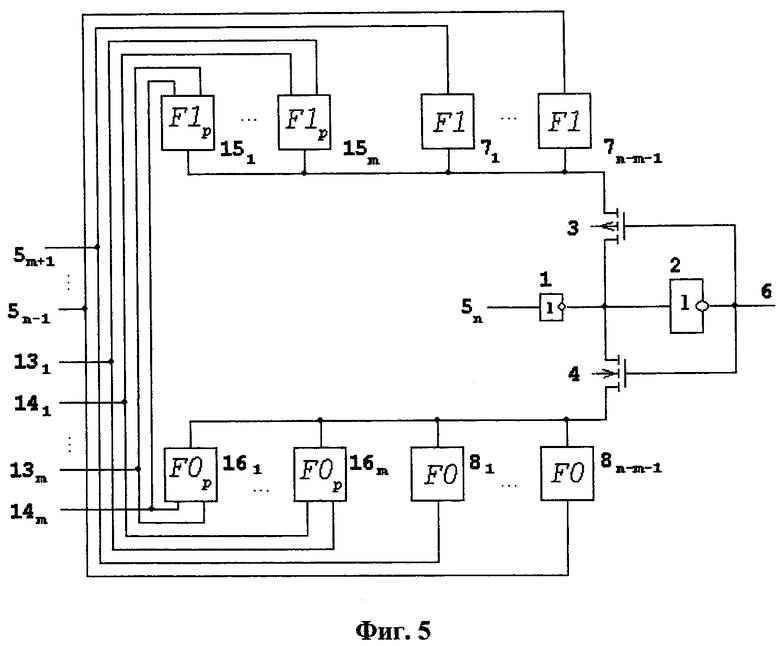

На фиг.5 представлена схема многовходового Г-триггера со смешанным набором входов: первые m входы являются парафазными, а последние (n-m) входы - инфазными. Схема содержит два инвертора 1-2, р-транзистор 3, n-транзистор 4, (n-m) инфазных входов 5m+1-5n, m парафазных входов {131, 141}-{13m, 14m}, выход 6, (n-m-1) блоков разрешения хранения на выходе триггера низкого уровня с инфазным входом 71-7n-m-1, m блоков разрешения хранения на выходе триггера низкого уровня с парафазным входом 151-15m, (n-m-1) блоков разрешения хранения на выходе триггера высокого уровня с инфазным входом 81-8n-m-1, m блоков разрешения хранения на выходе триггера высокого уровня с парафазным входом 161-16m, вход инвертора 1 соединен с инфазным входом триггера 5n, входы блоков 71-7n-m-1 и 81-8n-m-1 подключены к соответствующим (n-m-1) инфазным входам Г-триггера 5m+1-5n-1, входы блоков 151-15m и 161-16m подключены к соответствующим m парафазным входам Г-триггера {131, 141}-{13m, 14m}, выходы блоков разрешения хранения на выходе триггера низкого уровня с инфазным и парафазными входами соединены с истоком р-транзистора 3, выходы блоков разрешения хранения на выходе триггера высокого уровня с инфазным и парафазными входами соединены с истоком n-транзистора 4, стоки р- и n-транзисторов 3 и 4 подключены к выходу инвертора 1 и входу инвертора 2, затворы транзисторов 3 и 4 подключены к выходу инвертора 2 и выходу триггера 6.

Блоки разрешения хранения на выходе Г-триггера низкого и высокого уровней с инфазным и парафазным входами работают в соответствии с описанными выше принципами. Для нормальной работы Г-триггера все парафазные входы Г-триггера должны иметь одинаковое спейсерное состояние.

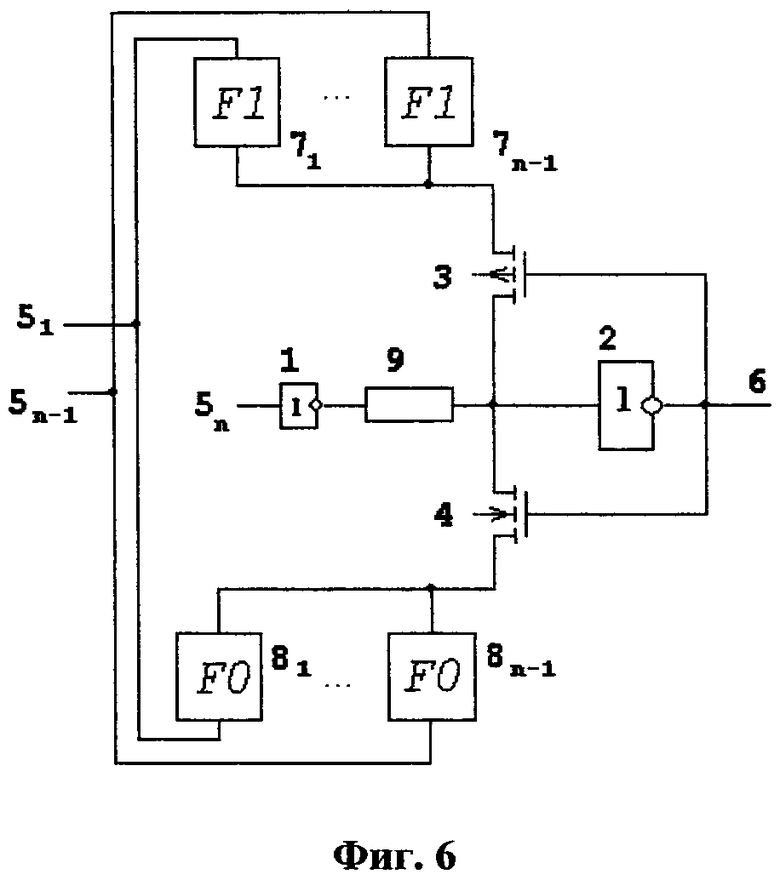

На фиг.6 изображена схема Г-триггера с резистором, подключенным между выходом инвертора и входом логического элемента с инверсией. Использование резистора позволяет реализовывать все транзисторы одного типа с одинаковым соотношением ширины и длины канала.

Однако описанные выше реализации не позволяют устанавливать начальное состояние Г-триггера.

На фиг.7 изображена схема Г-триггера с входом установки нуля на выходе триггера. Отличие ее от схемы на фиг.1 заключается в том, что в логический элемент 2, выполняющий функцию ИЛИ-НЕ, добавлен второй вход, подключенный к входу установки нуля 9.

Для установки нуля необходимо подать на вход установки 9 высокий уровень сигнала.

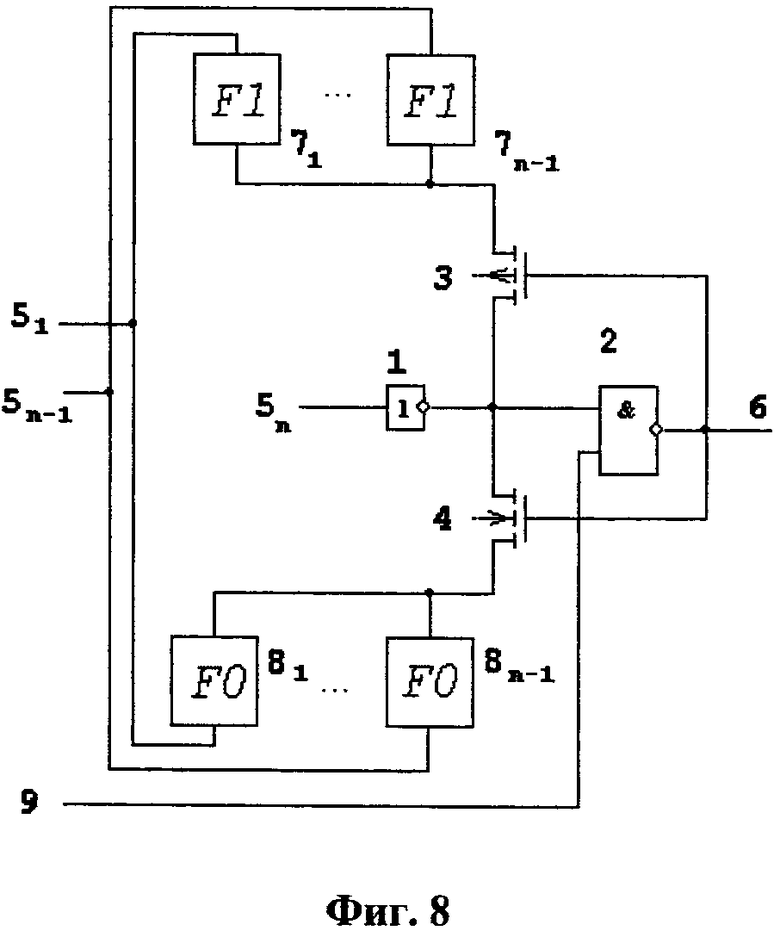

На фиг.8 изображена схема Г-триггера с входом установки единицы на выходе триггера. Отличие ее от схемы на фиг.1 заключается в том, что в логический элемент 2, выполняющий функцию И-НЕ, добавлен второй вход, подключенный к входу установки единицы 9.

Для установки единицы необходимо подать на вход установки 9 низкий уровень сигнала.

Источники

1. А.С. №1474831, Г-триггер / Варшавский В.И., Кондратьев А.Ю., Кравченко Н.М., Цирлин Б.С. Опубл. 23.04.89, БИ №15.

2. А.С. №1562964, Г-триггер / Варшавский В.И., Кравченко Н.М., Мараховский В.Б., Цирлин Б.С. Опубл. 07.05.90, БИ №17.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером | 2019 |

|

RU2725781C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2015 |

|

RU2601145C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2024 |

|

RU2832994C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с нулевым спейсером | 2019 |

|

RU2725780C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653301C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2023 |

|

RU2805759C1 |

| КОМБИНИРОВАННЫЙ Г-ТРИГГЕР С НУЛЕВЫМ СПЕЙСЕРОМ | 2007 |

|

RU2368068C2 |

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

Изобретение относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных вычислительных устройств и систем цифровой обработки информации. Техническим результатом изобретения является повышение быстродействия. Этот результат достигается за счет подключения стоков транзисторов р- и n-типа, управляемых сигналом с выхода Г-триггера, ко входу выходного инвертора и добавления блоков разрешения хранения низкого и высокого уровня на выходе триггера, коммутирующих истоки указанных транзисторов р- и n-типа с шинами питания и общей. Замена выходного инвертора элементом ИЛИ-НЕ или И-НЕ позволяет реализовать установку нуля или единицы соответственно на выходе триггера. 2 н.п. и 5 з.п. ф-лы, 8 ил.

1. Г-триггер, содержащий n входов, КМОП инвертор, логический элемент с инверсией, МОП транзистор с каналом р-типа проводимости (в дальнейшем - р-транзистор) и МОП транзистор с каналом n-типа проводимости (в дальнейшем - n-транзистор), причем вход инвертора подключен к n-му входу триггера, затворы р- и n-транзисторов соединены с выходом логического элемента с инверсией и выходом триггера, отличающийся тем, что в схему введены (n-1) блоков разрешения хранения на выходе триггера низкого уровня и (n-1) блоков разрешения хранения на выходе триггера высокого уровня, входы блоков разрешения обоих типов подключены к соответствующим первым (n-1) входам Г-триггера, выходы блоков разрешения хранения на выходе триггера низкого уровня соединены с истоком р-транзистора, выходы блоков разрешения хранения на выходе триггера высокого уровня соединены с истоком n-транзистора, стоки р- и n-транзисторов подключены к выходу инвертора и входу логического элемента с инверсией.

2. Г-триггер, содержащий n входов, КМОП инвертор, логический элемент с инверсией, р-транзистор и n-транзистор, причем вход инвертора подключен к n-му входу триггера, затворы р- и n-транзисторов соединены с выходом логического элемента с инверсией и выходом триггера, отличающийся тем, что в схему введены резистор, (n-1) блоков разрешения хранения на выходе триггера низкого уровня и (n-1) блоков разрешения хранения на выходе триггера высокого уровня, входы блоков разрешения обоих типов подключены к соответствующим первым (n-1) входам Г-тритгера, выходы блоков разрешения хранения на выходе триггера низкого уровня соединены с истоком р-транзистора, выходы блоков разрешения хранения на выходе триггера высокого уровня соединены с истоком n-транзистора, стоки р- и n-транзисторов подключены к входу логического элемента с инверсией, резистор подключен одним концом к выходу инвертора, а другим концом - к входу логического элемента с инверсией.

3. Г-триггер по п.1 или 2, отличающийся тем, что в схему введен вход установки нуля, в логический элемент с инверсией введен второй вход, подключенный к входу установки нуля триггера, а сам он выполняет логическую функцию ИЛИ-НЕ.

4. Г-триггер по п.1 или 2, отличающийся тем, что в схему введен вход установки единицы, в логический элемент с инверсией введен второй вход, подключенный к входу установки единицы триггера, а сам он выполняет логическую функцию И-НЕ.

5. Г-триггер по п.1, или 2, или 3, или 4, отличающийся тем, что блок разрешения хранения на выходе триггера низкого уровня реализован на одном р-транзисторе, исток которого подключен к шине питания, затвор - к входу блока, а сток - к выходу блока, блок разрешения хранения на выходе триггера высокого уровня реализован на одном n-транзисторе, исток которого подключен к общей шине, затвор - к входу блока, а сток - к выходу блока.

6. Г-триггер по п.1, или 2, или 3, или 4, отличающийся тем, что введены еще m входов, (m=1…(n-1)), дополняющие имеющиеся m входы до парафазного типа с нулевым спейсером, добавлен еще один вход и один р-транзистор в первые m блоки разрешения хранения на выходе триггера низкого уровня, исток первого транзистора подключен к шине питания, сток первого транзистора соединен с истоком второго транзистора, затвор первого транзистора подключен к прямой составляющей парафазного входа блока, сток второго транзистора подключен к выходу блока, а его затвор - к инверсной составляющей парафазного входа блока, добавлен еще один вход и один n-транзистор в первые m блоки разрешения хранения на выходе триггера высокого уровня, истоки обоих n-транзисторов подключены к общей шине, стоки - к выходу блока, а затворы - соответственно к прямой и инверсной составляющим парафазного входа блока.

7. Г-триггер по п.1, или 2, или 3, или 4, отличающийся тем, что введены еще m входов, (m=1…(n-1)), дополняющие имеющиеся m входы до парафазного типа с единичным спейсером, добавлен еще один вход и один р-транзистор в первые m блоки разрешения хранения на выходе триггера низкого уровня, истоки обоих р-транзисторов подключены к шине питания, стоки - к выходу блока, а затворы - соответственно к прямой и инверсной составляющим парафазного входа блока, добавлен еще один вход и один n-транзистор в первые m блоки разрешения хранения на выходе триггера высокого уровня, исток первого транзистора подключен к общей шине, сток первого транзистора соединен с истоком второго транзистора, затвор первого транзистора подключен к прямой составляющей парафазного входа блока, сток второго транзистора подключен к выходу блока, а его затвор - к инверсной составляющей парафазного входа блока.

| Г-триггер | 1987 |

|

SU1562964A1 |

| Г-триггер | 1986 |

|

SU1372597A1 |

| JP 61145924 A, 03.07.1986 | |||

| JP 9270678 A, 14.10.1997. | |||

Авторы

Даты

2009-10-27—Публикация

2007-11-15—Подача