Изобретение относится к области вычислительной техники, в частности к логическим схемам на КМОП-структурах, и может быть использовано при проектировании логических конвейерных устройств на динамических схемах с автоматическим восстановлением исходного состояния на КМОП-структурах.

Известно логическое конвейерное устройство, содержащее комплиментарную логическую схему "домино", включающее множество логических вентилей, управляемых несколькими синхронизирующими сигналами, при этом на входе каждой конвейерной ступени имеются логические динамические элементы, на которые поступают соответствующие синхросигналы, причем фазы синхронизации устроены так, что задний фронт синхронизирующего сигнала, инициирующего фазу предварительного заряда, задержан так, что позволяет периоду вычисления продолжаться во время последующего полупериода, осуществляя тем самым заем времени из следующей конвейерной ступени (см, патент США N 5517136 кл, H 08 К 19/017 от 3.03.95г,).

Однако известное устройство имеет следующие недостатки.

Во-первых, необходимо наличие четырех отдельных синхронизирующих сигналов, что приводит к увеличению фазовых разбросов между сфазированными фронтами синхроимпульсов. Кроме того, конвейер "домино" должен содержать первый вентиль "домино", управляемый первым синхронизирующим сигналом, второй вентиль "домино", управляемый вторым синхронизирующим сигналом и так далее. Минимальное количество вентилей составляет два вентиля на фазу полупериода, Кроме того, требование иметь четыре формирователя синхроимпульсов увеличивает потребляемую мощность и требует дополнительной площади на кристалле.

Следовательно, это решение не дает значительного увеличения тактовой частоты, которое необходимо для высокопроизводительных процессов.

Известно логическое конвейерное устройство, содержащее N последовательно соединенных конвейерных ступеней, каждая из которых состоит из цепи последовательно соединенных динамических КМОП элементов и имеет совокупность логических входов, вход синхронизации и логический выход, каждый динамический КМОП элемент имеет логические входы, входящие в совокупность логических входов соответствующей конвейерной ступени, вход восстановления состояния и логический выход, который у каждого предыдущего динамического КМОП элемента подключен к одному из логических входов последующего за ним динамического КМОП элемента, логический выход последнего динамического КМОП элемента соответствующей конвейерной ступени является логическим выходом этой ступени и соединен с одним ив входов совокупности логических входов последующей за ним конвейерной ступени, а логический выход последней конвейерной ступени является выходом устройства, и шины прямой и обратной фазы импульсов синхронизации. (Журнал полупроводниковых схем Института инженеров по радиотехнике и электронике, т. 33, N 11, стр. 1600 - 1680, ноябрь 1998 г., фиг. 1А и 1Б. ст. Дж. Сильбермана и др.).

Однако наличие входного триггера ведет к потере времени в такте, а из-за разброса фронтов синхроимпульсов и вышеуказанных потерь в такте уменьшается время, необходимое на обработку логических сигналов.

Кроме того, из-за наличия узлов формирования коротких импульсов возникает требование к жесткому выравниванию цепей прохождения сигналов, невозможность заема времени из-за разбросов и неточностей моделирования приводит к необходимости увеличения периода синхроимпульсов и соответственно к снижению быстродействия, а надежность работы может быть гарантирована лишь в узком диапазоне временных интервалов.

Техническим результатом является увеличение быстродействия и надежности функционирования в широком диапазоне временных интервалов.

Дополнительным техническим результатом является расширение области использования устройства за счет применения парафазных логических сигналов управления динамическими элементами.

Достигается это тем, что в логическом конвейерном устройстве, содержащем N последовательно соединенных конвейерных ступеней, каждая из которых состоит из цепи последовательно соединенных динамических КМОП элементов и имеет совокупность логических входов, вход синхронизации и логический выход, каждый динамический КМОП элемент имеет логические входы, входящие в совокупность логических входов соответствующей конвейерной ступени, вход восстановления состояния и логический выход, который у каждого предыдущего динамического КМОП элемента подключен к одному из логических входов последующего за ним динамического КМОП элемента, а логический выход последнего динамического КМОП элемента соответствующей конвейерной ступени является логическим выходом этой ступени и соединен с одним из входов совокупности логических входов последующей за ним конвейерной ступени, а логический выход последней конвейерной ступени является выходом устройства шины высокого и низкого потенциала напряжения и шины прямой и обратной фазы импульсов синхронизации, согласно изобретению вход синхронизации каждой конвейерной ступени подключен к одному из логических входов и ко входу восстановления состояния первого динамического КМОП элемента этой конвейерной ступени, вход восстановления состояния каждого динамического КМОП элемента, кроме первого, подключен к одному из логических входов этого динамического КМОП элемента, который подключен к логическому выходу предыдущего КМОП элемента, причем входы синхронизации нечетных ступеней подключены к шине прямой фазы импульсов синхронизации, а входы синхронизации четных ступеней подключены к шине обратной фазы импульсов синхронизации, кроме того, каждый динамический КМОП элемент содержит входной логический каскад, входы которого являются логическими входами КМОП элемента, выход через выходной инвертор подключен к логическому выходу КМОП элемента, формирователь импульсов сброса, вход запуска которого является входом восстановления состояния КМОП элемента, а вход сброса подключен к выходу выходного инвертора, с которым соединены сток n-МОП транзистора и затвор первого p-МОП транзистора, сток которого соединен со стоком второго p-МОП транзистора и подключен к выходу входного логического каскада, истоки первого и второго p-МОП транзисторов соединены с шиной высокого потенциала напряжения, затвор второго p-МОП транзистора и затвор n-МОП транзистора подключены соответственно к первому и второму выходам формирователя импульсов сброса, причем входной логический каскад выполнен в виде последовательно соединенных n МОП транзисторов, образующих токовую цепь от шины низкого потенциала напряжения питания до выхода входного логического каскада, при этом затворы транзисторов этой цепи являются входами входного логического каскада, кроме того, формирователь импульсов сброса содержит линию задержки, выход которой является первым выходом формирователя и подсоединен через выходной инвертор ко второму выходу формирователя, входной инвертор, вход которого является входом запуска формирователя, а выход подключен к затвору первого n-МОП транзистора, исток которого соединен со стоком второго n-МОП транзистора, затвор которого соединен с затвором p-МОП транзистора и с входом сброса формирователя, при этом сток первого n-МОП транзистора соединен со стоком n-МОП транзистора и со входом линии задержки, а истоки p-МОП транзистора и второго n-МОП транзистора подключены соответственно к шинам высокого и низкого потенциалов напряжения питания, кроме того, согласно изобретению длительность импульсов синхронизации прямой и обратной фазы равна 0,4-0,6 от длительности периода.

Согласно изобретению логические входы динамических КМОП элементов могут быть парафазными, причем каждый динамический КМОП элемент содержит входной логический каскад, парафазные входы которого являются логическими входами КМОП элемента, формирователь импульсов сброса, парафазный вход запуска которого является входом восстановления состояния КМОП элемента, а парафазный вход сброса подключен к выходу соответствующего первого и второго выходного инвертора, с выходом первого из которых соединен сток первого n-МОП транзистора и затвор первого p-МОП транзистора, сток которого соединен со стоком второго p-МОП транзистора и подключен к прямому выходу входного логического каскада, с выходом второго выходного инвертора соединен сток второго n-МОП транзистора и затвор третьего p-МОП транзистора, сток которого соединен со стоком четвертого p-МОП транзистора и подключен к обратному выходу входного логического каскада, истоки p-МОП транзисторов соединены с шиной высокого потенциала напряжения, затворы второго, четвертого p-МОП транзисторов и затворы n-МОП транзисторов подключены соответственно к первому и второму выходам формирователя импульсов сброса, кроме того, формирователь импульсов сброса содержит линию задержки, выход которой является первым выходом формирователя и подсоединен через инвертор ко второму выходу формирователя, элемент "ИЛИ", парафазные входы которого являются входом запуска формирователя, а выход подключен к затвору первого n-МОП транзистора, исток которого соединен со стоками второго и третьего n-МОП транзисторов, затворы которых подключены к парафазному входу сброса формирователя и соединены соответственно с затворами первого и второго p-МОП транзисторов, при этом сток первого n-МОП транзистора соединен со входом линии задержки и со стоком первого p-МОП транзистора, а исток которого соединен со стоком второго p-МОП транзистора, исток которого подключен к шине высокого потенциала, а истоки второго и третьего n-МОП транзисторов подключены к шине низкого потенциала,

Сущность изобретения заключается в том, что выполнение устройства вышеописанным образом с соответствующим подключением входов синхронизации каждой конвейерной ступени к одному из логических входов и ко входу восстановления состояния первого динамического КМОП элемента этой конвейерной ступени и подключение входа восстановления состояния каждого из остальных динамических КМОП элементов к одному из логических входов своего динамического КМОП элемента и к логическому выходу предыдущего КМОП элемента, а также особенности подключения входов синхронизации четных и нечетных ступеней приводят к увеличению быстродействия и надежному функционированию в широком диапазоне временных интервалов.

Использование парафазных логических сигналов управления динамическими элементами позволило реализовать функциональные схемы n-типа сумматоров, дешифраторов и т.п., что расширяет область применения.

Сравнение предложенного устройства с известным аналогом позволяет судить о соответствии критерию "новизна", а отсутствие отличительных признаков в аналогах говорит о соответствии критерию "изобретательский уровень",

Предварительные испытания позволяют утверждать о возможности промышленного использования.

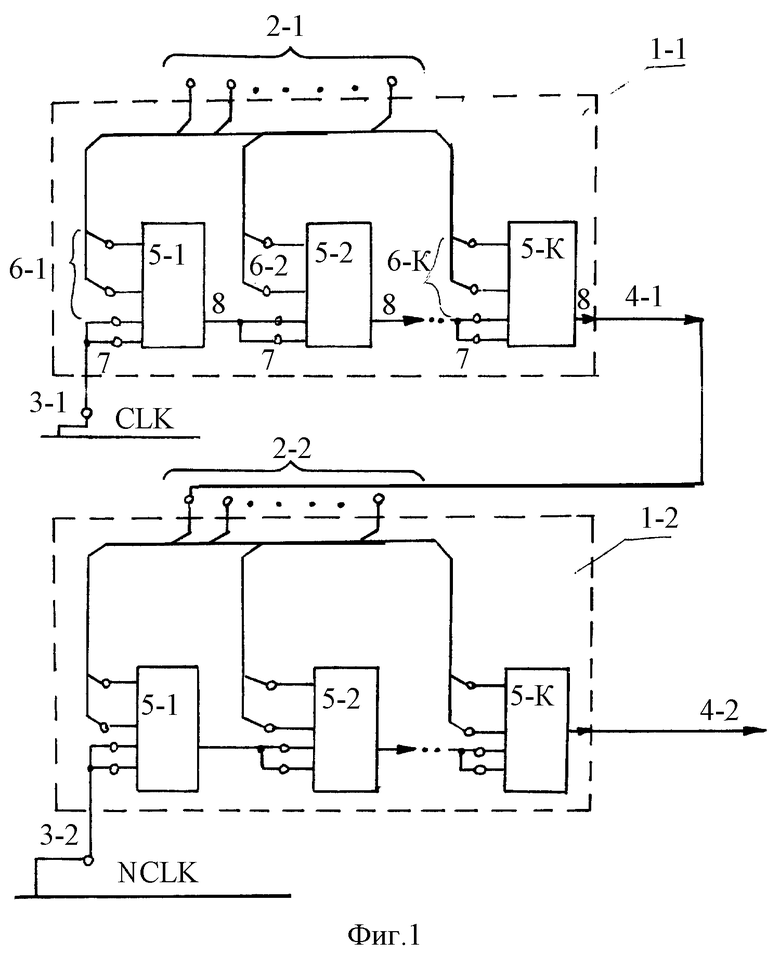

На фиг. 1 представлена принципиальная блок-схема предложенного устройства.

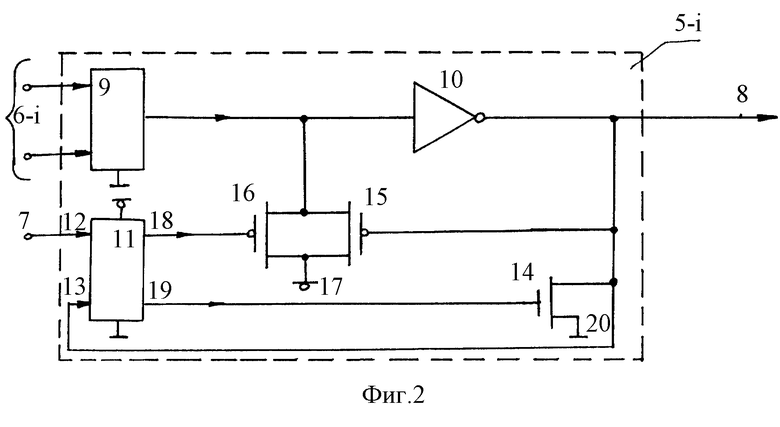

На фиг. 2 - принципиальная электрическая схема первого варианта динамического КМОП элемента,

на фиг. 3 - электрическая схема логического каскада,

на фиг. 4 - электрическая схема формирователя импульсов сброса,

на фиг. 5 - второй вариант динамического КМОП элемента,

на фиг. 6 - второй вариант логического каскада,

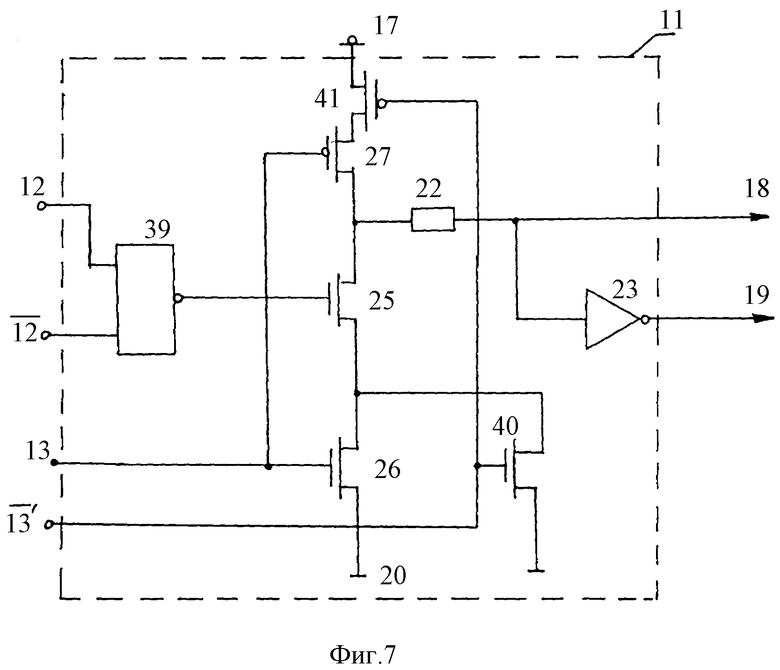

на фиг. 7 - второй вариант формирователя импульсов сброса.

Логическое конвейерное устройство содержит N последовательно соединенных конвейерных ступеней 1-1 и 1-2 (где N=2), каждая из которых имеет совокупность логических входов 2-1 и 2-2, вход 3-1 и 3-2 синхронизации и логический выход 4-1 и 4-2 соответственно и состоит из цепи последовательно соединенных динамических КМОП элементов 5-1...5-К.

Каждый динамических КМОП элемент 5-i имеет логические входы 6-1...6-К, входящие в совокупность логических входов соответствующей конвейерной ступени, вход 7 восстановления состояния и логический выход 8. Логический выход 8 у каждого предыдущего динамического КМОП элемента 5-i подключен к одному из логических входов 6-(i+1) последующего за ним динамического КМОП элемента 5-(i+1), а логический выход 8 последнего динамического КМОП элемента 5-К соответствующей конвейерной ступени 1-i является логическим выходом 4-i этой ступени и соединен с одним из входов совокупности логических входов последующей за ним конвейерной ступени 1-(i+1).

Логический выход 4-N последней конвейерной ступени 1-N является выходом устройства.

Кроме того, устройство содержит шины CLK и NCLK прямой и обратной фазы импульсов синхронизации соответственно, причем к первой из них подключены входы 3-1 синхронизации нечетных ступеней, а ко второй шине - входы 3-2 синхронизации четных ступеней.

Вход 3-i синхронизации каждой конвейерной ступени подключен к одному из логических входов и ко входу восстановления состояния первого динамического KMОП элемента 5-1 этой конвейерной ступени 1-i.

Вход 7 восстановления состояния каждого динамического КМОП элемента (5-2 - 5-К), кроме первого, подключен к одному из логических входов этого динамического КМОП элемента, который подключен к логическому выходу предыдущего КМОП элемента.

Каждый динамический КМОП элемент 5-i (фиг. 2) содержит входной логический каскад 9, входы которого являются логическими входами 6-i КМОП элемента, выход через выходной инвертор 10 подключен к логическому выходу 8 КМОП элемента, и формирователь 11 импульсов сброса, вход 12 запуска которого является входом 7 восстановления состояния КМОП элемента, а вход 13 сброса подключен к выходу выходного инвертора 10. С последним соединены сток n-МОП транзистора 14 и затвор первого p-МОП транзистора 15, сток которого соединен со стоком второго p-МОП транзистора 16 и подключен к выходу входного логического каскада 9.

Истоки первого и второго p-МОП транзисторов 15,16 соединены с шиной 17 высокого потенциала напряжения, затвор второго p-МОП транзистора 16 и затвор n-МОП транзистора 14 подключены соответственно к первому и второму выходам 18 и 19 формирователя 11 импульсов сброса.

К шине 20 низкого потенциала напряжения подключен исток n-МОП транзистора 14 и соответствующие выводы питания входного логического каскада 9 и формирователя 11 импульсов сброса,

Входной логический каскад 9 (фиг. 3) выполнен в виде последовательно соединенных n-МОП транзисторов 21-1...21-М, образующих токовую цепь от шины 20 низкого потенциала напряжения питания до выхода входного логического каскада 9. Затворы транзисторов 21-1...21-М образуют входы 6-1...6-М входного логического каскада.

Формирователь 11 импульсов сброса (фиг. 4) содержит линию задержки 22 (элемент задержки), выход которой является первым выходом 18 формирователя и через выходной инвертор 23 подключен ко второму выходу 19 формирователя. Кроме того, формирователь 11 содержит входной инвертор 24, вход которого является входом 12 запуска формирователя, а выход подключен к затвору первого n-МОП транзистора 25, исток которого соединен со стоком второго n-МОП транзистора 26, затвор которого соединен с затвором p-МОП транзистора 27 и с входом 13 сброса формирователя. Сток первого n-МОП транзистора 25 соединен со стоком p-МОП транзистора 27 и со входом линии задержки 22, а истоки p-МОП транзистора 27 и второго n-МОП транзистора 26 подключены соответственно к шинам 17 и 20.

Вариант динамического КМОП элемента по фиг. 5 помимо входного логического каскада 9, первого выходного инвертора 10, формирователя 11 импульсов сброса, первого n-МОП транзистора 14 и первого и второго p-МОП транзисторов 15 и 16 содержит второй выходной инвертор 28, второй n-МОП транзистор 29, третий и четвертый p-МОП транзисторы 30 и 31 соответственно.

Связи между новыми элементами этого варианта динамического КМОП элемента аналогичны связям первого варианта.

Вариант входного логического каскада 9 по фиг. 6 может быть выполнен в виде трех дифференциальных каскадов на шести n-МОП транзисторах 32-37 и n-МОП транзисторе 38, затвор которого подключен к шине CLK.

Вариант выполнения формирователя 11 импульсов сброса по фиг. 7 содержит линию задержки 22, выход которой является первым выходом 18 формирователя и подсоединен через инвертор 23 ко второму его выходу 19, элемент "ИЛИ" 39, парафазные входы 12 и  которого являются входом запуска формирователя, а выход подключен к затвору первого n-МОП транзистора 25, исток которого соединен со стоками второго и третьего n-МОП транзисторов 26 и 40, затворы которых подключены к парафазному входу 13,

которого являются входом запуска формирователя, а выход подключен к затвору первого n-МОП транзистора 25, исток которого соединен со стоками второго и третьего n-МОП транзисторов 26 и 40, затворы которых подключены к парафазному входу 13,  сброса формирователя и соединены соответственно с затворами первого и второго p-МОП транзисторов 27 и 41.

сброса формирователя и соединены соответственно с затворами первого и второго p-МОП транзисторов 27 и 41.

Сток первого n-МОП транзистора 25 соединен со входом линии задержки 22 и со стоком первого p-МОП транзистора 27, исток которого соединен со стоком второго p-МОП транзистора 41, исток которого подключен к шине 17 высокого потенциала напряжения, а истоки второго и третьего n-МОП транзисторов 26 и 40 подключены к шине 20 низкого потенциала.

Работа устройства.

В архитектуре предлагаемого устройства по фиг, 1 используется синхроимпульс, разделенный на чередующийся нечетный (высокий уровень CLK) и четный (низкий уровень CLK) части полупериода и синхроимпульс инверсной фазы - NСLK.

Положительный фронт прямой фазы CLK совпадает с инверсной фазой NCLK, и наоборот.

Длительность синхроимпульса CLK составляет 0,4-0,6 от длительности периода, поэтому переключения сигнала CLK происходят по существу в то же время, что и переключения сигнала NCLK, так как положительный фронт сигнала CLK совпадает по времени с отрицательным фронтом сигнала NCLK и наоборот.

Когда сигнал CLK имеет низкий уровень, выход входного логического каскада 9 предварительно заряжен до напряжения питания и находится в состоянии "1".

Положительный фронт сигнала CLK инициирует период вычисления. Если входные воздействия на входной логический каскад 9 поданы в соответствии с функцией срабатывания, то его выход будет разряжаться до низкого уровня, который поступает на вход инвертора 10 для переключения логического выхода 8 с низкого уровня на высокий.

Позже сигнал CLK своим отрицательным фронтом заканчивает период вычисления, закрывая транзистор 21-i во входном логическом каскаде 9. Этот фронт сигнала CLK инвертируется на входном инверторе 24 и подается в виде высокого уровня напряжения на затвор первого n-МОП транзистора 25 формирователя 11 импульсов сброса.

Поскольку в это время сигнал с выхода 8 имеет высокий уровень (если все входы входной логики были поданы ранее в соответствии с функцией срабатывания), то второй n-МОП транзистор 26 также будет открыт. Соответственно транзисторы 25 и 26 будут после определенной временной задержки, обусловленной линией задержки 22, переключать выход 18 до низкого уровня, открывая транзистор 16 предварительного заряда и заряжая (увеличивая напряжение) на выходе логического каскада 9. Разряд выхода 18 откроет через инвертор 23 n-МОП транзистор 14, вызывая разряд выхода 8 до низкого уровня, который закроет n-МОП транзистор 26 через вход 13 и откроет p-МОП транзистор 27 для заряда выхода 18 до высокого напряжения, тем самым закрывая транзистор 16.

Таким образом, формирователь 11 импульсов сброса формирует короткий импульс предзаряда для восстановления исходного состояния выхода логического каскада 9.

Первый динамический КМОП элемент 5-1 приведен в исходное состояние, ожидая появление очередного фронта синхросигнала CLK.

Заметим, что если по меньшой мере на один из входов входного логического каскада 9 пришел отрицательный логической уровень, то выход каскада 9 не будет разряжаться и напряжение на выходе 8 останется на низком уровне. В этом случае формирователь 11 импульсов сброса не формирует импульс сброса и тем самым потребляется меньше энергии.

Второй и последующие КМОП элементы 5-2...5-К функционируют аналогично первому элементу 5-1, только на вход 7 восстановления состояния подается сигнал с выхода 8 предыдущего каскада.

Положительный фронт сигнала CLK включает входы первого синхронного каскада - динамического КМОП элемента 5-1 для запуска вычисления по логической конвейерной ступени 1-1.

Если логические сигналы, приходящие на входной логический каскад 9, приводят к образованию цепи разряда предварительно заряженного его выхода к низкому потенциалу, то потенциал соответствующих выходов 8 будет нарастать. Это, в свою очередь, может запустить следующие, находящиеся ниже логические элементы 5-2. ..5-К, и вычисление будет распространяться, формируя макровыходы 4-1.

Если тактовый полупериод вычисления превышает время задержки цепи вентилей данной ступени конвейера, то выходы будут сохранять свои значения до прихода следующего отрицательного фронта CLK. Если время задержки логических вентилей превышает тактовый полупериод вычисления, то выходы 4-1 переключают входы 2-2 следующей по порядку ступени конвейера и данные вычисления распространяются по логической ступени 1-2, формируя на макровыходах 4-2 результирующие импульсы.

Волна сброса начинается от следующего отрицательного фронта синхроимпульса CLK для ступени 1-1 конвейера.

Логическое конвейерное устройство будет функционировать надежно при соблюдении следующих условий.

Во-первых, все входные сигналы на логических входах 6-i для каждого динамического КМОП элемента 5-1 должны иметь общий минимальный временной интервал t мин для правильной работы, что необходимо для обеспечении разряда на выходе входного логического каскада 9 до уровня низкого потенциала.

Выбор линии задержки 22 обеспечивает выполнение вышеуказанного условия.

Максимальный интервал времени, который можно занять в соседних ступенях конвейера

tзаем=T/2-tсдв-tмин,

где T - период,

tсдв - разброс фронтов CLK.

Если заем времени производится только для компенсации потерь, связанных с фазовыми разбросами фронтов синхросигналов tсдв, время задержки отрицательного фронта на выходе входных синхронных каскадов динамических КМОП элементов 5-1 tзад для неконвейерных логических схем равно:

tзад=tподг+tсдв-tвых=tсдв,

т.к. tподг=tвых,

где tподг ≈ tмин,

tвых - время задержки элемента 5-1 по положительному фронту.

В случае tлог = Т без потерь времени цикла для конвейерных устройств с временем обработки данных N тактовых периодов фактическое время для вычисления логики составляет tлог (N•T) с возможностью заема времени между тактовыми полупериодами.

Второе условие заключается в том, что сигнал сброса (восстановления) должен завершиться до прихода очередных данных на входы 6-i.

Логические ступени могут быть сложными с парафазными динамическими сигналами, например, для выполнения функции сумматора.

Работа устройства (фиг. 5,6,7) аналогична вышеописанному, но отличается от него.

Во-первых в начальный момент при отсутствии сигналов управления оба парафазных выхода входного логического каскада 9 предзаряжены к высокому уровню, а оба парафазных выхода 8 - к низкому уровню.

При поступлении парафазных сигналов прямой либо инверторный выходы входного логического каскада 9 разряжаются к низкому уровню напряжения, а соответствующий прямой либо инверторный выходы 8 и  заряжаются к высокому уровню напряжения питания.

заряжаются к высокому уровню напряжения питания.

При этом на затвор транзистора 26 (или 40) подается высокий уровень напряжения, на затвор транзистора 25 поступает низкий уровень напряжения с выхода элемента "ИЛИ" 39, так как на одном из входов элемента "ИЛИ" 39 присутствует высокий уровень напряжения.

Один из пары парафазных сигналов, поступающих на входной логический каскад 9, поступает на входы элемента "ИЛИ" 39.

После окончания полупериода функционирования на парафазные входы входного логического каскада 9 приходят обнуленные сигналы с выхода динамического КМОП элемента 5-1, что вызывает переключение выхода 18 в низкий уровень напряжения, а 19 - в высокий уровень напряжения, тем самым обеспечивая восстановление выходов входного логического каскада 9 в высокий уровень напряжения, а выходов 8 - в низкий уровень.

Такое построение логического конвейерного устройства позволяет реализовывать любое логическое образование: сумматоры, дешифраторы, умножители, делители и т.п., используя вышеописанную динамическую схемотехнику.

Таким образом, в предложенном устройстве достигается поставленный технический результат.

| название | год | авторы | номер документа |

|---|---|---|---|

| БАЗОВЫЙ УСИЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДИФФЕРЕНЦИАЛЬНОЙ ДИНАМИЧЕСКОЙ ЛОГИКИ (ВАРИАНТЫ) | 1999 |

|

RU2154338C1 |

| ДИНАМИЧЕСКИЙ D-ТРИГГЕР | 2018 |

|

RU2679220C1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| УСТРОЙСТВО КОРРЕКЦИИ СКВАЖНОСТИ ВХОДНОГО СИГНАЛА | 2011 |

|

RU2467473C1 |

| Компаратор напряжений | 1989 |

|

SU1688398A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ НАПРЯЖЕНИЯ С УСТРОЙСТВОМ ЗАЩИТЫ ОТ ОТРИЦАТЕЛЬНЫХ ВЫБРОСОВ ПРИ ПОДКЛЮЧЕНИИ ИНДУКТИВНОЙ НАГРУЗКИ | 2011 |

|

RU2483437C1 |

| Г-ТРИГГЕР | 2007 |

|

RU2371842C2 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с нулевым спейсером | 2019 |

|

RU2725780C1 |

| ВЫХОДНОЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ С УСТРОЙСТВОМ ЗАЩИТЫ ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ ДЛЯ КМОП МИКРОСХЕМ | 2013 |

|

RU2540813C1 |

Изобретение относится к вычислительной технике и может использоваться в устройствах обработки данных. Логическое конвейерное устройство содержит N последовательно соединенных динамических КМОП элементов. Вход синхронизации каждой конвейерной ступени подключен к одному из логических входов и ко входу восстановления состояния первого динамического КМОП элемента этой ступени, а вход восстановления состояния каждого КМОП элемента, кроме первого, подключен к одному из логических входов этого элемента, который подключен к логическому выходу предыдущего элемента. Технический результат: повышение быстродействия и надежности функционирования в широком диапазоне временных интервалов. 5 з.п. ф-лы, 7 ил.

6. Логическое конвейерное устройство по п.1, отличающееся тем, что логические входы динамических КМОП элементов являются парафазными.

| US 5517136 A, 14.05.1996 | |||

| Регистр | 1979 |

|

SU822367A1 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

| US 5329176 A, 12.07.1994. | |||

Авторы

Даты

2001-11-10—Публикация

2000-12-29—Подача