14 ПАЗ7

рого элемента И, второй вход которого подключен к третьему входу блока анализа и через второй инвертор к второмуэл не

му Bxoj iy первого элемента И, ньгходы элементов И через элемент Ш1И соединены с выходом блока анализа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования отметок времени | 1982 |

|

SU1112568A1 |

| Устройство для отображения информации | 1983 |

|

SU1124374A1 |

| Устройство для программного управления | 1990 |

|

SU1737411A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ И ОЦЕНКИ ИХ ПЕРИОДА | 1990 |

|

RU2033617C1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство контроля качества датчиков времени | 1986 |

|

SU1422218A1 |

| Многоканальное устройство тестового контроля логических узлов | 1990 |

|

SU1837295A1 |

| Программно-управляемый цифровой фильтр | 1985 |

|

SU1338006A1 |

| Устройство для построения программируемых цифровых микропроцессорных систем | 2020 |

|

RU2726497C1 |

1

Изобретение относится к импульсной технике, предназначено для надежного счета импульсов, формирования отметок времени и сетки частот и является усовершенствованием устройства по авт.св. № 1112568.

Целью изобретения является расширение функциональных возможностей путем обеспечения формирования отметок календарных дат числа, месяца, года.

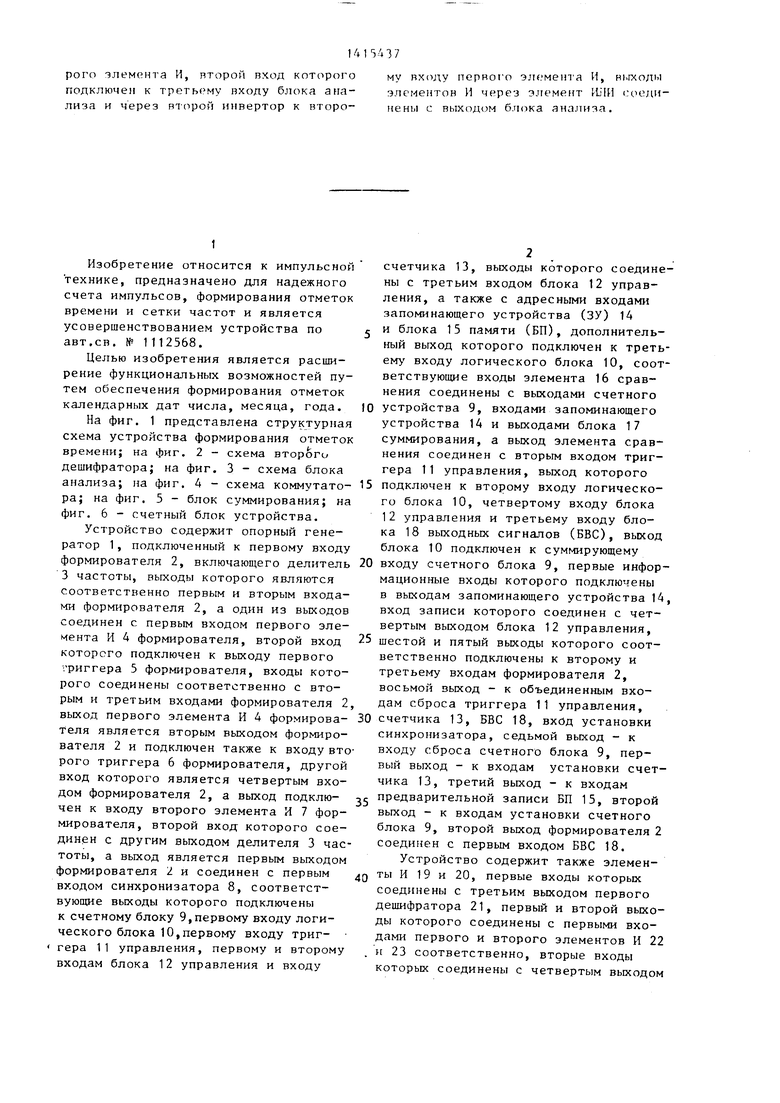

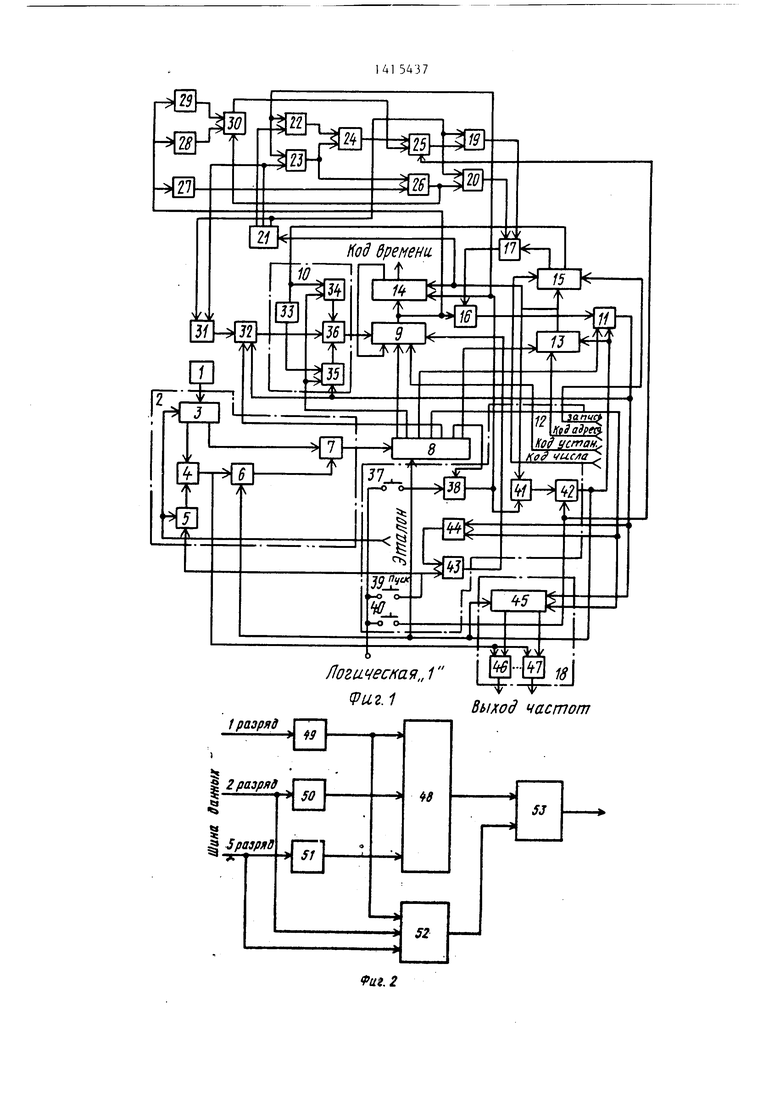

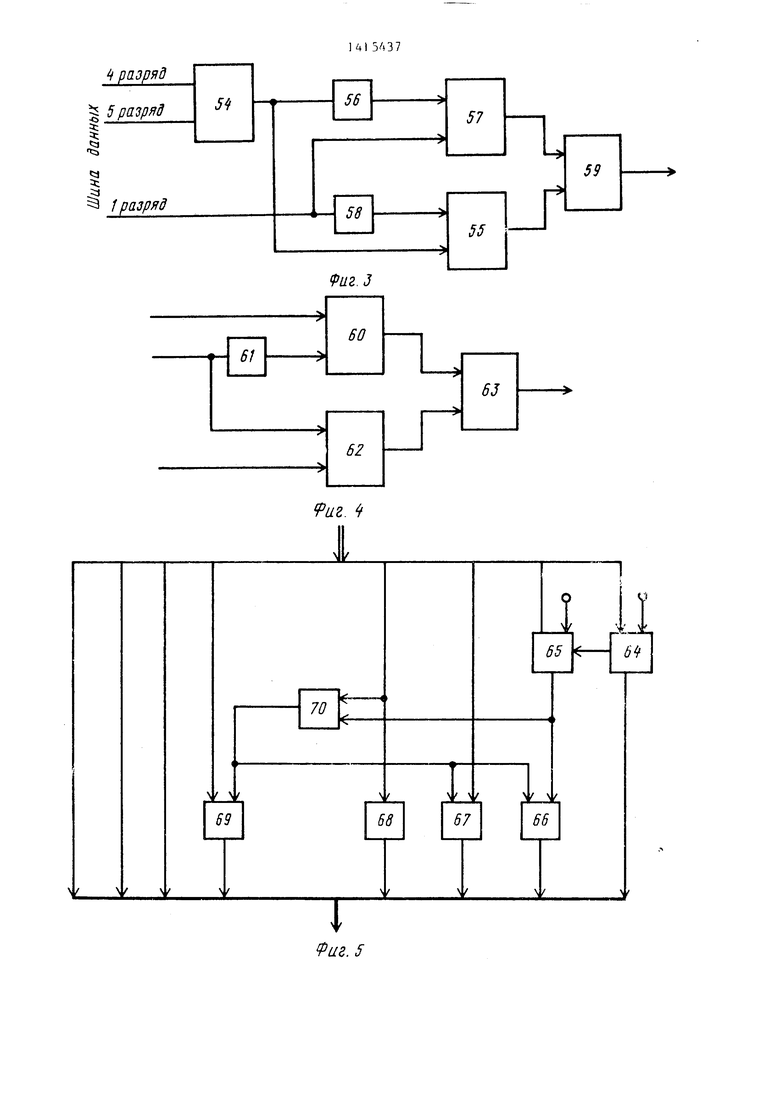

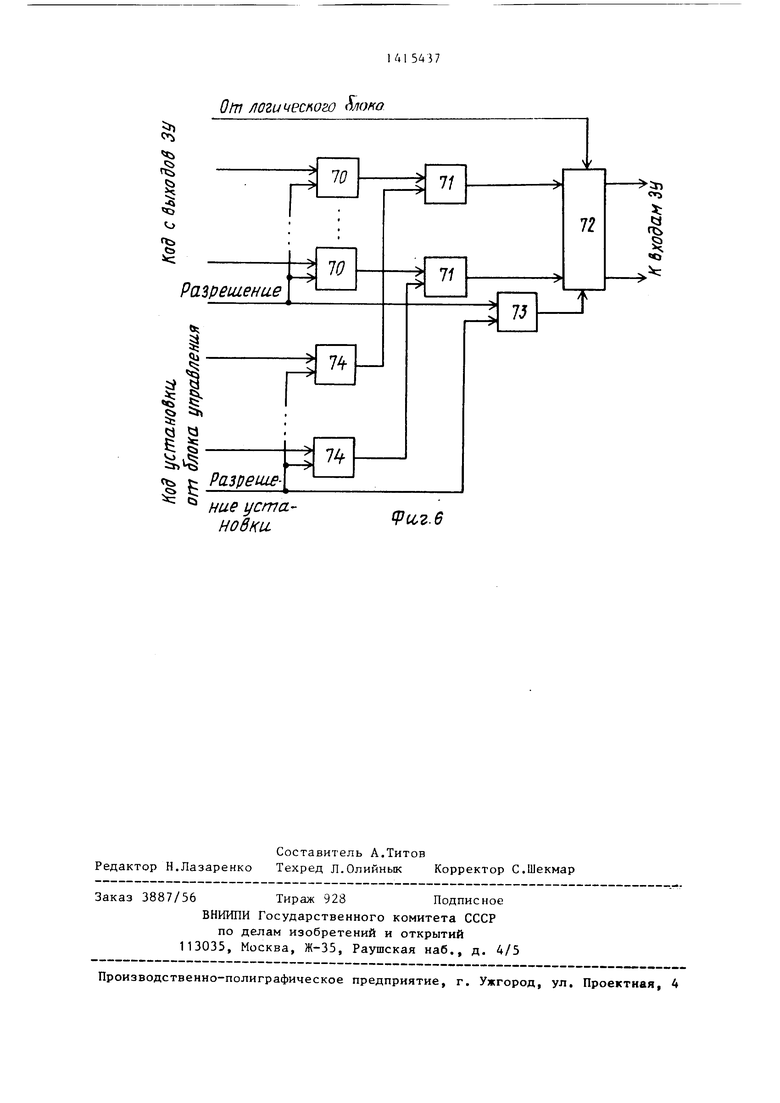

На фиг. 1 представлена структурная схема устройства формирования отметок времени; на фиг. 2 - схема второго дешифратора; на фиг. 3 - схема блока анализа; на фиг. 4 - схема коммутато- ра; на фиг. 5 - блок суммирования; на фиг. 6 - счетный блок устройства.

Устройство содержит опорный генератор 1, подключенный к первому входу формирователя 2, включающего делитель 3 частоты, выходы которого являются соответственно первым и вторым входами формирователя 2, а один из выходов соединен с первым входом первого элемента И 4 формирователя, второй вход которого подключен к выходу первого триггера 5 формирователя, входы которого соединены соответственно с вторым и третьим входами формирователя 2 выход первого элемента И 4 формирова- Теля является вторым выходом формирователя 2 и подключен также к входу второго триггера 6 формирователя, другой вход которого является четвертым входом формирователя 2, а выход подклю- чен к входу второго элемента И 7 формирователя, второй вход которого соединен с другим выходом делителя 3 частоты, а выход является первым выходом формирователя 2 и соединен с первым входом синхронизатора 8, соответствующие выходы которого подключены к счетному блоку 9,первому входу логического блока 10,первому входу триг- гера 11 управления, первому и второму входам блока 12 управления и входу

счетчика 13, выходы которого соединены с третьим входом блока 12 управления, а также с адресными входами запоминающего устройства (ЗУ) 14 и блока 15 памяти (БП), дополнительный выход которого подключен к третьему входу логического блока 10, соответствующие входы элемента 16 сравнения соединены с выходами счетного устройства 9, входами запоминающего устройства 14 и выходами блока 17 суммирования, а выход элемента сравнения соединен с вторым входом триггера 11 управления, выход которого подключен к второму входу логического блока 10, четвертому входу блока 12 управления и третьему входу блока 18 выходных сигналов (ВВС), выход блока 10 подключен к суммирующему входу счетного блока 9, первые информационные входы которого подключены в выходам запоминающего устройства 14 вход записи которого соединен с четвертым выходом блока 12 управления, шестой и пятый выходы которого соответственно подключены к второму и третьему входам формирователя 2, восьмой выход - к объединенным входам сброса триггера 11 управления, счетчика 13, ВВС 18, вход установки синхронизатора, седьмой выход - к входу сброса счетного блока 9, первый выход - к входам установки счетчика 13, третий выход - к входам предварительной записи БП 15, второй выход - к входам установки счетного блока 9, второй выход формирователя 2 соединен с первым входом БВС 18.

Устройство содержит также элементы И 19 и 20, первые входы которых соединены с третьим выходом первого дешифратора 21, первый и второй выходы которого соединены с первыми входами первого и второго элементов И 22 и 23 соответственно, вторые входы которых соединены с четвертым выходом

3I 14

блока 12 управления, а выходы подключены к соответствующим входам элемента 1-Ш11 24, выход которого подключен к входу синхронизации первого триггера 25, ныход которого соединен с вторым входом третьего элемента И 19, т)ыход которого подключен к соответст- иуклдему входу блока 17 суммирования. Выход второго элемента И 23 подключен также к входу синхронизации второго триггера 26, D-вход которого соединен с выходом третьего дешифратора 27 входы которого соединены с соответствующими вьгходами счетного блока 9. Выход триггера 26 соединен с вторым входом четвертого элемента И 20, выход которого соединен с соответствующим входом блока 17 суммирования. Входы блока 28 анализа и второго де- гшфратора 29 подключены к соответствующим выходам счетного блока 9, а цыходы - к второму и первому входам коммутатора 30, вход управления которого соединен с инверсным выходом триггера 26, а выход - с D-входом первого триггера 25.

Второй и третий ныходы первого дешифратора 21 соединены с первым и вторым входами первого элемента МЛИ 31 соответственно,выход которого под- )слючен к первому входу пятого элемента И 32, второй вход которого соединен с пятым вьЕчодом синхронизатора 8, третий вход - с выходом триггера 1 1 управления, i выход - с четвертым .пом логического блока 10.

Логический блок 10 содержит элемент НЕ 38, вход и выход которого подключены соответственно к первым входам первого 34 и второго 35 элементов И логического блока, выходы которых соединены с входами элемента 11ПИ 36 логического блока, при этом третий вход элемента ИЛИ 36 является четвертьь - входом логического блока, .1 его - выходом логического блока, вход элемечта НЕ 33 является третьим входом логического блока, объединенные вторые входы первого 34 и второго 35 элементов И - первым его входом, а третий вход второго элемента И 35 - вторым входом логического блока 10.

Блок 12 управ; ения может быть вы- itb--;, , как показано на п:, 1. Для предварительной записи чисел н запо1 гинаю1цее устройство использованы кнопочный переключатель 37

7

и элемент ИПИ 38, для сбора и установки - пепь из кнопочного переключателя 39 и 40, деишфратора 41, элементов ИЛИ 42 и 43, элемента И 44, для предварительной записи чисел в счетчик и блок памяти - кодовые тины. ВВС 18 состоит из регистра 45 сдвига и выходных вентилей 46 и 47.

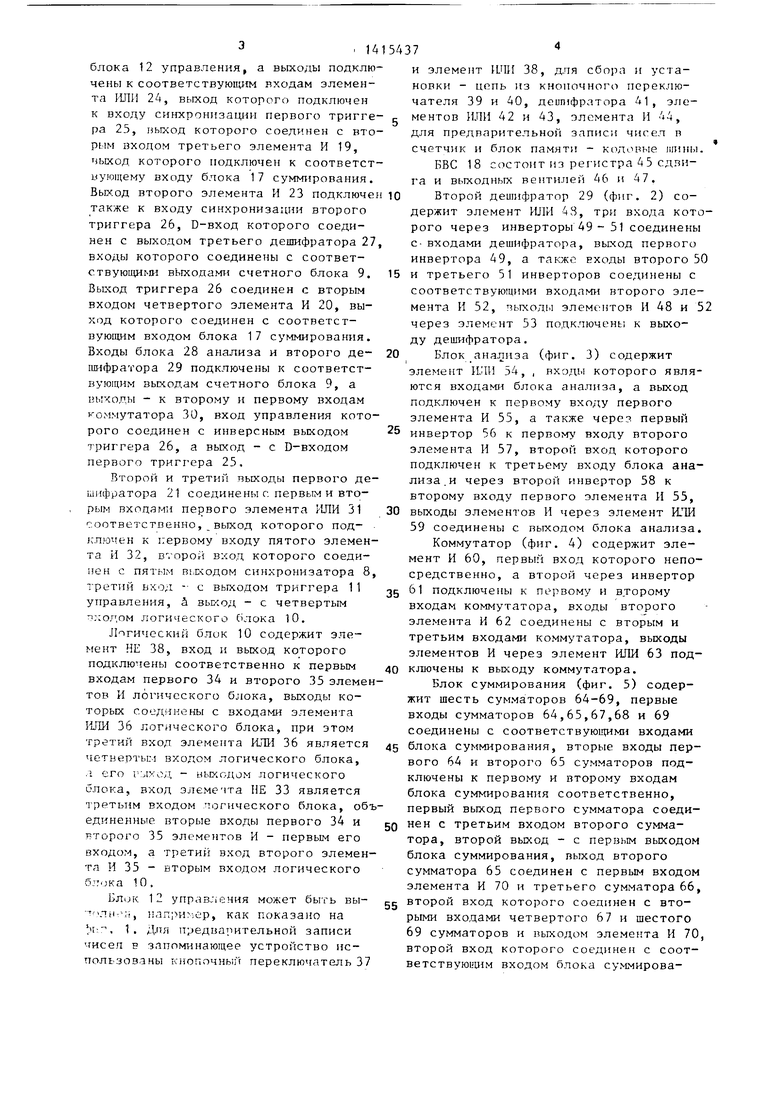

Второй дешифратор 29 (фиг. 2) содержит элемент ИЛИ 48, три входа которого через инверторы 49 - 51 соединены с-входами дешифратора, выход первого инвертора 49, а таь:жс входы второго 50

и третьего 51 инверторов соеди}1ены с соответствующими входами второго элемента И 52, пыходы элементов И 48 и 52 через элемент 53 подключены к выходу дешифратора.

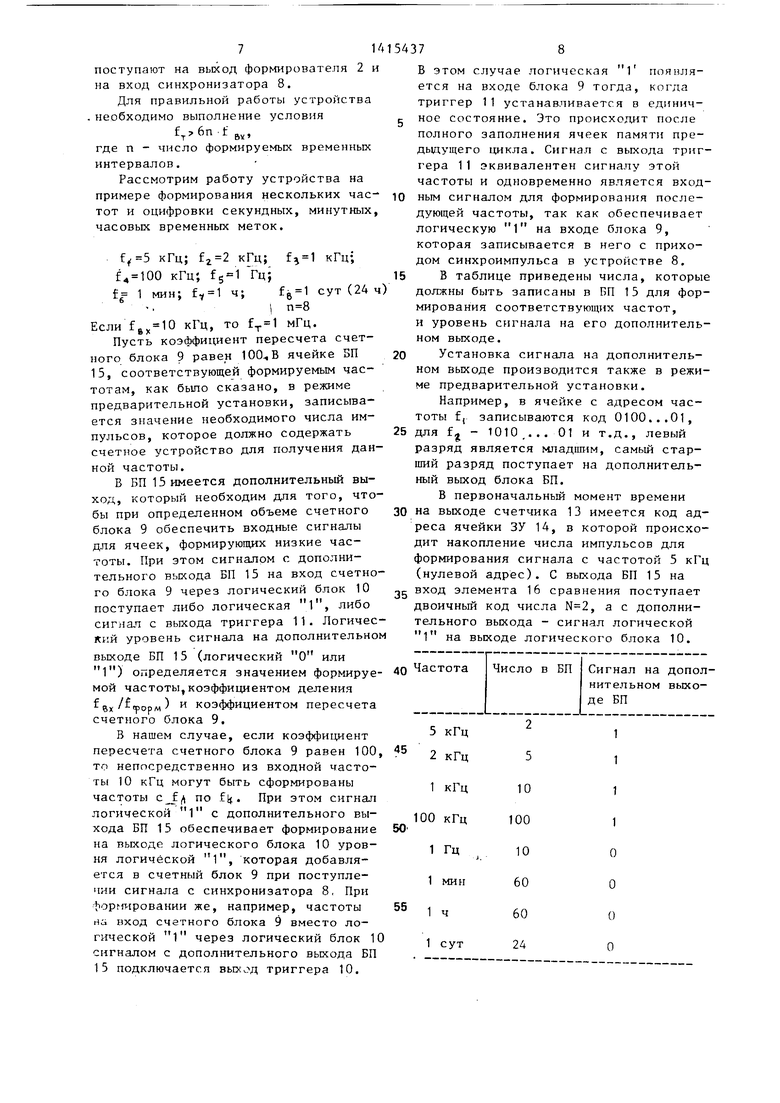

Блок анализа (фиг. 3) содержит

элемент ИЛИ 54, , входы которого являются входами блока анализа, а выход подключен к первому входу первого элемента И 55, а также через первый

инвертор 56 к первом входу второго элемента И 57, второй вход которого подключен к третьему входу блока анализа, и через второй инвертор 58 к второму входу первого элемента И 55,

выходы элементов И через элемент ИЛИ 59 соединены с выходом блока анализа. Коммутатор (фиг. 4) содержит элемент И 60, первый вход которого непосредственно, а второй через инвертор

61 подключены к первому и в.торому входам коммутатора, входы второго элемента И 62 соединены с вторым и третьим входами коммутатора, выходы элементов И через элемент ИЛИ 63 подключены к выходу коммутатора.

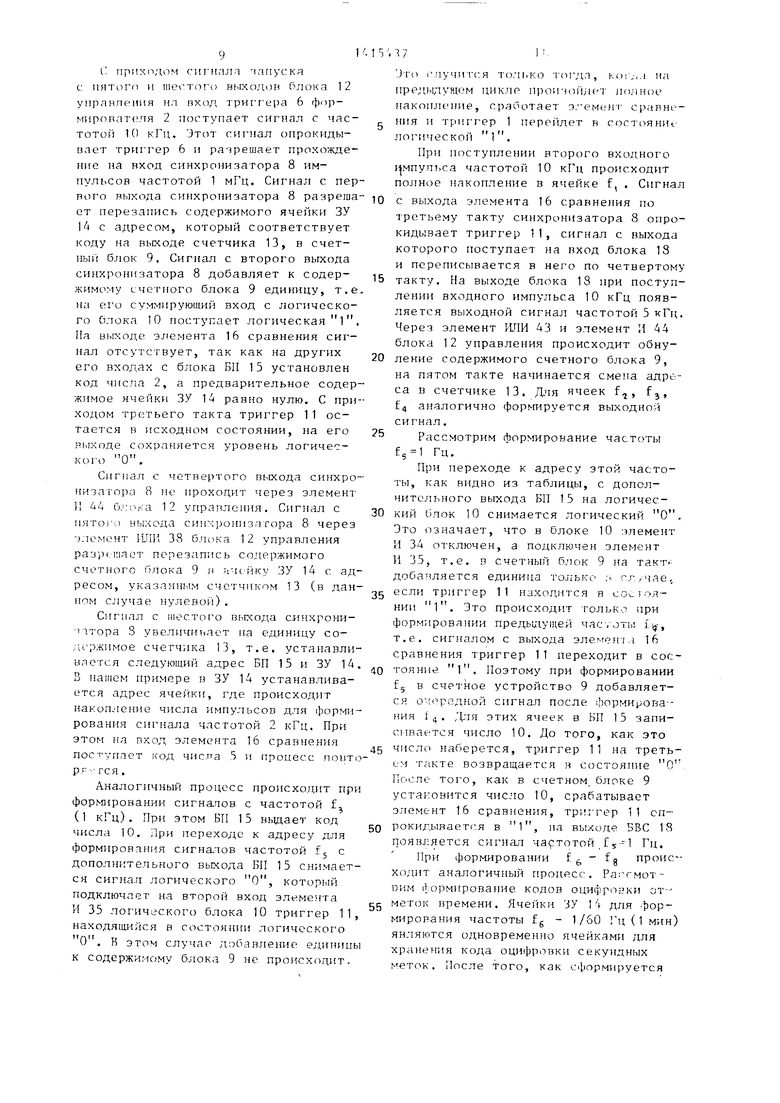

Блок суммирования (фиг. 5) содержит шесть сумматоров 64-69, первые входы сумматоров 64,65,67,68 и 69 соединены с соответствующими входами

блока суммирования, вторые входы первого 64 и второго 65 сумматоров подключены к первому и второму входам блока суммирования соответственно, первый выход первого сумматора соединен с третьим входом второго сумматора, второй выход - с первым выходом блока суммирования, выход второго сумматора 65 соединен с первым входом элемента И 70 и третьего сумматора 66,

второй вход которого соединен с вторыми входами четвертого 67 и шестого 69 сумматоров и выходом элемента И 70, второй вход которого соединен с соот- ветствуюь шм входом блока суммирова

ПИЯ и первым входом пятого сумматора 68, второй вход которого подключен к первому выходу четвертого сумматора 67, третий вход которого подключен к первому выходу третьего сумматора 66, вторые выходы сумматоров 66 и 67 и выходы сумматоров 68 и 69 соединены с соответствующими выходами блока суммирования, восьмой, девятый и десятый входы блока суммирования соединены с шестым, седьмым и восьмым выходами блока суммирования.

Все примеры реализации блоков показаны для случая использования двоич но-десятичиого кода.

Счетный блок 9 (фиг. 6) имеет информационные и установочные входы, которые соединены соответственно с выходами запоминающего устройства и вто

рым выходом блока управления, соответственно каждый разряд выхода ЗУ 14 соединен с соответствующим элементом 71. 1-71.п совпадения, другие входы которых соединены с первым выходом блока синхронизации, а выходы - с входами элементов ИЛИ 72,1-72.п, входы которьк подключены к D-входам счетчика 73 и вход записи которого соединен с выходами элемента liJlH 74. Выход ко- да установки блока управления подключен на входы соответствующих элементов совпадения и через элементы ИЛИ 72.1-72.п на D-входы счетчика, счетный вход которого соединен с выходом логического блока.

Устройство работает следующим образом.

Вначале производится предварительная установка всех элементов устройст ва с помощью блока 12 управления. При нал атии кнопки 40 блока 12 управления обнуляется ВВС 18, счетчик 13, триггер формирователя 2, триггер 11 упт ранления и триггер 25 устанавливаются в состояние О, а триггер 26 - в состояние 1, синхронизатор 8 устанавливается в состояние 0000001. Установка триггера 26 в состояние 1 вызывает установку коммутатора 30 в первое состояние, при котором к выходу коммутатора подключается выход дешифратора 29. Далее производится предварительная установка в ячейки ЗУ 14 текущего значения временных интервалов.

Установка и обнуление производятся следуюпщм образом.

5

5

о

5

0 5 0 5

В счетчик 13 сигналами с первого выхода блока 12 управления устанавливается код адреса ячеек ЗУ 14 для хранения значений часовых интервалов времени. Код может быть набран, например, кнопочными переключателями. С второго вьсхода блока 12 управления на выход установки блока 9 поступает код установки текущего значения часовых интервалов. На вход записи БП 15 с третьего выхода блокц 12 управления подается код числа, определяющего максимальное количество импульсов, которое должно быть накоплено в часовом интервале, т.е. код числа 24, с девятого выхода блока 12 управления на БП 15 подается сигнал записи, который может формироваться вручную, например, от кнопки. С четвертого выхода блока 12 управления через элемент ИЛИ 39 от кнопочного переключателя (КП) 37 поступает сигнал на вход записи ЗУ 14. Содержимое счетного устройства 9 П(реписывается в соответ- ствуюцще ячейки ЗУ 14.

г .. - ,

Далее сигналом с первого выхода

блока 12 управления в счетчике 13 усI

танавливается код адреса ячеек ЗУ 14

для хранения значения минутных интервалов. Аналогично описанному вьш1е в счетном блоке 9 устанавливают код текущего значения минутных интегралов времени, который переписывается в со- ответствующие ячейки ЗУ 14 и код числа 60 в БП 15. Аналогично остальные ячейки ЗУ 14 устанавливают в нулевое состояние, а в БП 15 записываются соответственно коды максимальных чисел, соответствующих данному временному интервалу. После окончания предварительной установки в счетчике 13 остается код адреса ячеек ЗУ 14 для хранения наименьших интервалов времени. Устройство подготовлено к работе. С пятого выхода блока 12 управления подается сигнал Пуск, который устанавливает триггер 5 в состояние О. Как только с шестого выхода блока 12 управления поступает сигнал, привязанный к эталонному, делитель 3 частоты обнуляется, триггер 5 опрокидывается и с выхода элемента И 4 формирователя 2 поступает сигнал с частотой f , который в свою очередь опрокидывает триггер 6, и сигналы с второго выхода делителя 2 частоты частотой f,- через элемент И 7

7I

поступают на выход формирователя 2 и на вход синхронизатора 8.

Для правильной работы устройства необходимо выполнение условия

t а,

где п - число формируемых временных интервалов.

Рассмотрим работу устройства на примере формирования нескольких частот и оцифровки секундных, минутных, часовых временных меток.

кГц; 2 кГц; f 1 кГц; кГц; Гц; f 1 мин; ч;

Ь

fg 1 сут (24 ч)

Если fj,10 кГц, то 1 МГц.

Пусть коэффи1и1ент пересчета счетного блока 9 равен ячейке БП 15, соответствующей формируемым частотам, как было сказано, в режиме предварительной установки, записывается значение необходимого числа импульсов, которое должно содержать счетное устройство для получения данной частоты.

В БП 15 имеется дополнительный выход, который необходим для того, чтобы при определенном объеме счетного блока 9 обеспечить входные сигналы для ячеек, формирующих низкие частоты. При этом сигналом с дополнительного выхода БП 15 на вход счетного блока 9 через логический блок 10 поступает либо логическая 1, либо сигнал с выхода триггера 11. Логический уровень сигнала на дополнительном

выходе БП 15 (логический О или 1) определяется значением формируемой частоты,коэффициентом деления f счетного блока 9.

В нашем случае, если коэффициент пересчета счетного блока 9 равен 100, то непосредственно из входной частоты 10 кГц могут быть сформированы частоты cjE| по f|j. При этом сигнал логической 1 с дополнительного выхода БП 15 обеспечивает формирование на выходе логического блока 10 уровня логической 1, которая добавляется в счетный блок 9 при поступлении сигнала с синхронизатора 8, При форм 1ровании же, например, частоты ria вход счетного блока 9 вместо логической 1 через логический блок 10 сигналом с дополнительного выхода БП 15 подключается выя од триггера 10.

в,(/ тор/ч) и коэффициентом пересчета

78

В этом случае логическая

Г

появляется на входе блока 9 тогда, когда триггер 11 устанавливается в единичHOC состояние. Это происходит после полного заполнения ячеек памяти предыдущего цикла. Сигнал с выхода триггера 11 эквивалентен сигналу этой частоты и одновременно является входным сигналом для формирования последующей частоты, так как обеспечивает логическую 1 на входе блока 9, которая записывается в него с приходом синхроимпульса в устройстве 8.

В таблице приведены числа, которые должны быть записаны в БП 15 для формирования соответствующих частот, и уровень сигнала на его дополнительном выходе.

Установка сигнала на дополнительном выходе производится также в режиме предварительной установки.

Например, в ячейке с адресом частоты f, записываются код 0100...01,

для f - 1010... 01 и т.д., левый разряд является млад1Ш1м, самый стар- щий разряд поступает на дополнительный выход блока БП.

В первоначальный момент времени

на выходе счетчика 13 имеется код адреса ячейки ЗУ 14, в которой происходит накопление числа импульсов для формирования сигнала с частотой 5 кГц (нулевой адрес). С выхода БП 15 на

вход элемента 16 сравнения поступает двоичный код числа , а с дополнительного выхода - сигнал логической 1 на выходе логического блока 10.

5 кГц 2 КГц

1 кГц 100 кГц

1 Гц .

1 мин

1 ч

1 сут

2

5

10 100 10 60 60 24

1

О

о о о

I приходом сигипл-т чапускя с пятого и шем тогч) вьгхоД(И) блока 12 упрлнлеиия нл вхо,п тригг ера 6 формирователя 2 поступает сигнал с частотой 10 кГц. Этот сигнал опрокидывает триггер 6 я раярешает прохождение на вход синхронизатора 8 импульсов частотой 1 мГц. Сигнал с первого выхода синхронизатора 8 разрешает перезапись содержимого ячейки ЗУ 14 с адресом, который соответствует коду на выходе счетчика 13, в счет- Hbii i блок 9. Сигнал с второго выхода синхронизатора 8 добавляет к содержимому счетного блока 9 единицу, т.е }ia его суммирующий вход с логического блока 10 поступает логическая. На выходе элемента 16 сравнения сигнал отсутствует, так как на других его входах с блока БП 15 установлен код числа 2, а предварительное содержимое ячейки ЗУ 14 равно нулю. С приходом третьего такта триггер 11 остается в исходном состоянии, на его иыходе сохраняется уровень логического О.

Сигнал с четвертого синхронизатора 8 не проходит через элемент И 44 б,|;;1ка 12 упрапления. Сигнал с пятого нылода синх1)онизатора 8 через :)ломент 1ШГ 38 блока 12 управления pa3pi. перезапись содержимого счетного блока 9 я ;1чс;йку ЗУ 14 с адресом, указанным счетчиком 13 (в данном случае нулевого .

Сигнал с liiecToi o выхода слнхрони- чттора 8 увеличиг(ает на единиду со- га ржимое счетчика 13, т.е. устанавливается следующий адрес БП 15 и ЗУ 14 В нашем примере в ЗУ 14 устанавливается адрес ячеГ(ки, где происходит накопление числа импульсов для формирования сигнала частотой 2 кГц. При этом на вход элемента 16 сравнения пост упает к од числа 5 и процесс поито рг : гея .

Аналогичный процесс происходит при фop D poвaнии сигналов с частотой f (1 кГц). При этом БП 15 вьщает код числа 10. При переходе к адресу для формирования сигналов частотой fj с дополнительного вькода БП 15 с})имает- ся сигнал логического О, который подключает на второй вход элемента И 35 логического блока 10 триггер 11, находящийся в состоянии логического О. В этом случае добавление единицы к содержимому блока 9 не происходит.

JTO (ГПУЧИТСЯ только тогда, hOi ;,,l на

предыдущем цикле проичо1 1дет полное накопление, сработает эл-емент сралн1;-- ния и тригтер 1 переГшет в состояниь логической 1.

При поступлении второго входного 1 мпулт,са частотой 10 кГц происходит полное накопление в ячейке f, . Сигнал

с выхода элемента 16 сравнения по

третьему такту си1 хронизатора 8 опрокидывает триггер 11, сигнал с выхода которого поступает на вход блока 18 и переписывается в него по четвертому

такту. На выходе блока 18 при поступлении входного импульса 10 кГц появляется выходной сигнал частотой 5 кГц. Через элемент 1-ШИ 43 и элемент И 44 блока 12 управления происходит обнуление содержимого счетного блока 9, на пятом такте начинается смена адреса в счетчике 13. Для ячеек f,, f,, f4 аналогично формируется выходной сигнал.

Рассмотрим формирование частоты

Гц.

При переходе к адресу этой частоты, как видно из таблицы, с дополнительного выхода БП 15 на логический ()лок 10 снимается логический О, Это означает, что в блоке 10 элемент И 34 отключен, а подключен элемент И 35, т.е. в счетный блок 9 на такт добатшяется единица толькс ; ,чае,,

если триггер 11 находится в состоянии 1. Это происходит только при формировании предыдущей час /oTii iij-, т.е. сигналом с выхода элемены 16 сравнения триггер 11 переходит в состояние 1. Поэтому при формировании fj в счетное устройство 9 добавляется о -юредной сигнал после ;)ормирова-- }шя f. Для этих ячеек а БП 15 записывается число 10. До того, как это

число наберется, триггер 11 на третьем такте возвращается и состоягше О После Того, как в счетном, блоке 9 установится число 10, срабатывает элемент 16 сравнения, триггер 11 спрокидывает1:я в 1, на выходе ВВС 18 появляется сигнал частотой , Гц.

При формировании в проис-- ходит аналогичный процесс. Рассмотрим 1т,о1)мирование кодов оцифровки отметок времени. ЯчеГ1ки ЗУ I i для формирования частоты fg - 1/60 Гц (1 мин) являются одновременно ячейками для хранения кода оцифровки секундных меток. После того, как С||)ормируется

частота 1 Гц, триггер 11 переходит в состояние 1. По шестому такту синхронизатора 8 и на этом цикле изменяется содержимое счетчика 13 и в нем устанавливается адрес ячейки для формирования частоты 1/60 Гц. С дополнительного выхода БП 15 снимается логический О, т.е. чере второй управляющий вход логического блока 10 на его выход подключается выход триггера 11.

С приходом первого такта в цикле формирования частоты 1/60 Гц в блоке 9 переписывается состояние ячейки ЗУ 14 (в данном случае оно нулевое) на втором такте происходит добавлени единицы в счетный блок 9, на третьем такте - сброс триггера 11, так как на выходе БП 15 код числа 60, на четвертом такте обнуления не происходит, на пятом такте состояние счетного устройства 100000 переписывается в ячейку ЗУ 14. Код числа секунд далее может сниматься на индикацию или любое другое регистрирующее устройство.

Аналогично формируются коды минутных и часовых меток времени.

Для привязки сигналов сетки выходных частот на выходные вентили 46 и 47 блока 18 подается строб-импульс. Таким образом устройство позволяет сформировать любую сетку частот и код оцифровки текущего времени Для формирования отметок календарных дат, числа, месяца, года в счетчик 13 сигналами с первого выхода блока 12 управления устанавливают код адреса ячеек ЗУ 14 для хранения значений оцифровки лет. Код может быть набран, например, кнопочными переключателями. С второго выхода блока 12 управления на вход установки счетного блока 9 поступает код установки текущего значения лет. С четвертого выхода блока 12 управления через элемент ИЛИ 38 от кнопочного переключателя 37 поступает сигнал на вход записи ЗУ 14. Содержимое счетного блока 9 переписывается в со ответствую1цие ячейки ЗУ 14. Код с блока 13 поступает также на вход дешифратора 21, сигнал с выхода которого после нажатия кнопки 36 через элемент И 22 и элемент ИЛИ 24 поступает на счетный вход триггера 25, D-вход которого соединен с выходом коммутатора 30 и через него с вьсходом дешифратора 29, если текущий i-од lU uncci- косный, то на его выходе нулено; о- тенциал и триггер 25 остается н состоянии О. Если год високосный, то на выходе дешифратора 29 потемциал .ской 1 и триггер 25 переходит в состояние 1.

Далее сигналами с первого выхода блока 12 управления в счетчик 13 устанавливают код адреса ячеек ЗУ 14 для хранения оцифровки значения месяцев .

Аналогично описанному ранее в счет- ном блоке 9 устанавливают код значения текущего месяца, который переписывается в соответствующие ячейки ЗУ 14. При установке адреса месяцев на втором выходе дешифратора 21 по- является сигнал, который при нажатии кнопки 37 через элемент И 23 подается на счетньй вход второго триггера 26. Если устанавливают февраль месяц, то срабатывает дешифратор 27, на выходе появляется сигнал 1 и триггер 26 остается в состоянии 1. Если устанавливают адрес любого другого месяца, то на выходе дещифратора 27 появится логический О и триггер 26 изменяет свое состояние на О. Сигнал с выхода инверсного плеча этого триггера переводит коммутатор во второе положение и к выходу коммутатора подключается схема четности. На выход записи блока 15 памяти с третьего выхода блока 12 управления подается код числа, определяющего максимальное количество импульсов, которое может быть накоплено при оцифровке этих временных интервалов, т.е. код числа 12. С девятого выхода блока 12 управления на БП 15 подается сигнал записи, который может быть сформирован, например, вручную от кнопки.

Аналогично производится установка ячейки 31 для хранения значения суток. При этом в БП 15 записывают код числа 29. Если в месяце 30 дней, на выходе блока 28 анализа будет О, если 31 день - 1. Соответственно триггер 25 устанавливается с состояние О или Г . Таким образом на вы55

ходе элементов И 19 и 20 устанавливаются: 00 - невисокосный год, февраль,

10- високосный год, февраль,

01 - любой год, в месяце 30 дней,

11- любой год, в месяце 31 день.

При усгаи 1вке адреса суток на сум- мат(1р э.пементов И 19 и 20 потупает один из указанных к;1дов, который суммируется с кодом числа 29. Аналогично производится установка в ячейки ЗУ 1 i l для хранения значения часов, минут. При этом в блок памяти записываются числа 24 и 60 соответственно. Остальные ячейки обнуляются, а в блок Г1с1мяти записываются: в ячейки для хранения секундных меток - код числа 60, в ячейки для хранения частот - код значения необходимого числа им- лульс(.в, которое должен содержать счетн1111 блок 9 для получения данной частоты. )тс) зависит от значения вход частоты счетного блока, которая выбирается из условий f,7n-f ,,

-частота с первого выхода де1П5теля 3 частоты;

-частота на входе синхрониза тора 8;

число циклов работы синхронизатора . Ilijcjie С :ч(: нчаиия Г1под1зарительной

где С

bf

п устансяки п счетчике 13 остается код arrp Mja яч /1- К ЗУ 14 для хранения Лцмен1 1П(Х ин 1ч;7)ваиов премени. Устрой .гно к работе.

С, пя Г(.и о Г)Ь:ход.ч Слоь:а 12 управления подае1ся сигнал Пуск, который устаИиШлир. ) S г состояние О. Как чолько с шес 1Ч)Го н --1хода бло- :ч п 12 управления поступает сипкш, риг язанн.:: к эта,г1онному5 делитель 3 :-:стоты обнуляется, триггер 5 спроки- ;|,1;и.;ется и с выхода элемеш а И 4 фор- мир.шателя 12 поступает сигнал частотой fц, который в свою очередь опрокидывает триггер 6, и сигналы с второго вькода делителя 2 частоты частотой f-. через элемент И 7 поступают на выход формирователя 2 и на вход С1П тпчитатора 8.

гтб тта стройства в част формиро в:.;:ип час 1 от, а также оцифровки се- ку1.д, минут, часов рассмотрена ранее и аналогична работе известного уст- ройстна. При 1, аботе устройства вплоть до фор;-пфования часовых отметок Я1ювь введенные элементы не оказывают влияния на работу, поскольку С1ггналы прежде всего поступают на входы введенных дешифраторов 21, 27, 29, а oHii деишфрируют код с выхода счетчика Г: толЬ о при установке и не кода адрегл суток, месяцев, лет. Поэтому

на BXo/tax блока 17 суммирования с выхода элементов И 19 и 20 присутствуют логические О. На вход введеннего элемента ИЛЯ 31 также поступают О. Рассмотрим работу устройства в части вновь введенных блоков, т.е. формирование оцифровки суток, месяцев, лет.

После оцифровки часов сигнал с последнего выхода синхронизатора 8 переводит счетчик 13 в следующее состояние, соответствующее адресу ячеек памяти суток в ЗУ 14. Код со счетчика 13 поступает на адресные входы БП 15 и запоминающего устройства 14, а также на входы дешифраторов 21 и 41. На третьем выходе дешифратора 21 появляется сигнал, который открывает

элементы И 19 и 20 и на их выходе появляются сигналы, соответствующие состоянию триггеров 25 и 26, т.е. установленному в режиме предварительной установки: 00, 10, 01 или

11 в зависимости от года и месяца. Этот код суммируется с кодом числа 29 с БП 15.

Если при формировании кода часов на выходе счетного блока 9 установится код менее чем 24, то элемент 16 сравнения не сработает и триггер 11 останется в том же нулевом состоянии, Поэтому при оцифровке суток счетный вход блока 9 оказывается закрытым; элементы И 32 и 35 - сигналом логи- ческого О с триггера 1 1 , элемент

И 39 - нулем с дополнительного да БП 15. Следовательно, добавление еди.иицы в счетное устройство не происходит.

Если рри формировании кода часов на вьгх1 де счетного блока устройства 9 установится код 24, элемент 16 сравнения срабатывает и триггер 11 управлония устанавливается в состояние 1. В1, счетного блока 9 открыта а а тел,

Код адреса со счетчика 13 поступает на вход дешифратора 21, сигнал

с третьего выхода которого открывает элементы И 19 и 20. На их входах установлены потенщ1алы, соответствующие первоначальной установке, т.е. соответствующие текущему месяцу, году (см. выше). Этот код поступает на вход блока 17 суммирования, где он cyм мpyeтcя с кодом числа 29 и результат поступает на элемент 16 сравнения. При этом по первому такту с

1514

синхронизатора 8 код из ЗУ 14 перецц- сывается в счетньи блок 9, По второму такту через И 35 происходит добавле)1ие единицы в счетный блок 9. По третьему такту, если нет сигнала с элемента 16 сравнения, триггер 11 управления устанавлийается в состояние О. По четвертому такту элеме гг И 44 закрыт, по пятому элемент И 32 закрыт, по шестому происходит запись содержимого счетного устройства 9 и в ЗУ 14, по седьмому такту - смена кода в счетчике 13.

Рассмотрим случай, когда на данном цикле про исходит оцифровка последнего дня текущего месяца, например, в месяце 31 день, т.е. по второму такту в счетном блоке устанавливается код числа 31. Это значит, на выходе эле- ментов И 19 и 20 код 11, на выходе блока суммирования код числа 32. Значит элемент сравнения не срабатывает и код числа 31 переписывается в ЗУ 14 Здесь есть отличие от режима оцифров- ки часов, секунд, минут, где в аналогичной ситуации блок 9 обнуляется по четвертому такту, так как оцифровывается не 60 мин, а 00 мин. В сут- ках же необходимо оцифровать, напри- мер, 31-й день (а не 00 дней).

На следующем цикле оцифровки суток необходимо лерейти от числа 31 к числу 1 (первый день следующего месяца), .Расс:- отрим эту ситуацию. По первому такту код числа 31 лз ЗУ 14 переписывается 13 счетный блок 9, на втором такте добавляется единица и появляется код 32„ Теперь срабатывает элемент 16 сравнения, триггер 11 остается в 1. По четвертому такту через элементы И 44 и РШИ 43 счетный блок 9 обнуляется, но по пятому такту через элемент И 32 добавляется единица. Таким образом в счетном блоке устанавливгегся код числа 1. Триггер 11 остается в состоянии 1. Оцифровка месяцев,, как и при переходе от часов к суткам, меняется после того, как в счетном бло- ке 9 наберется максимальное количество суток в данном месяце, Flo есть некоторое отличие, связанное с тем, как указывалось, что оцифровывается .Л1 ДНИк день месяца. После установ- ки, например, 31-го числа триггер 11 не меняет своего состояния, так как не срабатывает элемемт 16 сравнения. Поэтом: на цикле оцифровки меся1дев

37Ib

К(5д месяца не моцясч ся, т.е. 31, наприхо, яирлря 1)1.

Когда ия слслу|.11це .1 цикле оц.иф1П1р- ки суток устанпв.гщпается кс1Д 01 (цер- вое число), триг гер 11 остается п состоянии 1, как указацо рацее. Это приводит к тому, что цри цергходе к адресу месяцев в счетное устройство добавляется единица и устацавливает- ся код следующего месяца, цапример 01.02.

Рассмотрим подробнее работу в цикле оцифровки месяцев.

По первому такту содержимое из ЗУ 14 пс реписывается н счетный блок 9 По второму такту в него добавляется единица, так как триггер 11 в состоянии 1. По третьему такту, если нет сигна:1а с выхода элемента 16 сравнения,, триггер 11 управления устанавливается в состояние О, По четвертому такту элемент И 44 закрыт, по пя- тому элемент И 32 закрыт, по шестому происходит запись содержимого счетного блока 9 в ЗУ 14. По этому же такту открывается элемент И 23, так как на другой его вход поступает сигнал с второго выхода дешифратора 21 (дешифрируется адрес с выхода счетчика 13). С выхода элемента И 23 сигнал поступает на счетный вход триггера 26 Если на выходе счетного устройства установлен код любого месяца, кроме (5)евраля, то на выходе дешифратора 27 будет сигнал логического О, триггер 26 установится в состояние О, если он бып в состоянии 1, или подтвердится его нулевое состояние. По- тен1Д1ал с его инверсного выхода, т.е. 1, устанавливает коммутатор 30 в п-е состояние, и на его выход проходит сигнал с выхода блока 28 анализа, на вход которого также поступает код с выхода счетного блока 9. Этот блок анализирует порядковый номер месяца. Если в месяце 30 дней, на его выходе будет нуль, если 31 день - единица. Предположим, установлен код месяца, в котором 31 день. Тогда единиц, с выхода коммутатора 30 поступает на D-ВХОД триггера 25, который по шестому такту через схемы 23 ц 25 устанавливается в состояние 1. Тогда на входах элементов И 19 и 20 устанавливается код 11.

Если на счетном блоке 9 кд}; (февраля, то на выходе дешифратора 27 устанавливается единица, триггер 2Ь также

устанавливается в единицу. Нулевой потенциал с его инверсного выхода переводит коммутатор 30 в единичное состояние, т.е. к его выходу подключается выход дешифратора 29, который на следующем цикле анализирует.високосный год или нет. А пока на входах элементов И 19 и 20 установлен код 00.

После того, как будет набрано число месяцев в году, т.е. 12, как и при оцифровке суток элемент 16 сравнения не срабатывает, так как на его вторые входы поступает код числа 13. Так оцифровывается последний месяц в году

На следующем цикле оцифровки месяцев в счетный блок 9 добавляется единица, на выходе элемента сравнения появляется единичный потенциал, а по третьему такту триггер 11 переходит в состояние 1. По четвертому такту через элементы 43 и 44 счетный блок 9 обнуляется, по пятому такту через открытый элемент И 32 в блок 9 добавляется единица, по шестому такту код 01 переписывается в ЗУ 14. Триггер II остается в состоянии 1. По седьмому такту в счетчике 13 устанавливается код адреса ячеек оцифровки лет. Этот код поступает на дешифраторы 21 и 41. С первого выхода дешифратора 21 единичный потенциал открывает элемент И 22. По первому такту синхронизато718

ра 8 содержимое ячеек ЗУ 14 переписывается в счетный блок 9. По второму такту в него добавляется единица. Если с выхода элемента 16 сравнения нет сигнала, триггер 11 устанавливается третьим тактом в О. Четвертый и пятый такты не проходят, так как закрыты элементы 44, 43 и 32. Код с выхода

счетного блока 9 поступает на вход дешифратора 29. Если при оцифровке месяцев установлен февраль, триггер 26 остается в нулевом состоянии, а коммутатор - в единичном, т.е. к его выходу подключается выход дешифратора 29, а если год невисокосный, на его выходе присутствует нуль, если високосный - единица. По шестому такту нуль или единица устанавливаются в

триггере 25. Таким образом, если год високосный, на входах элементов 19 и 20 формируется код 01, если невисокосный - 00. По седьмому такту содер- жимое счетчика 13 увеличивается на

единицу. Это число дешифрируется дешифратором 41. Сигнал с его выхода через элемент 42 поступает на обнуление счетчика 13, триггера 11, блока 18, формирователя 2, установку синхронизатора 8 в состояние 0000001. Устройство переходит в исходное состояние .

Далее весь цикл работы повторяется.

/Логическая„1 Vuz.1

Выход частот

разряд

ч

1 разряд

Раг.З

От логического локо

ние установки

.6

| Устройство для формирования отметок времени | 1982 |

|

SU1112568A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-08-07—Публикация

1985-08-21—Подача