4

о: г

Изобретение относится к вычислительной технике и может быть использовано при построении систем памяти ЭВМ.

Цель изобретения - расширение функциональных возможностей устройства за счет реализации возможности выделения массива требуемого объема путем объединения нескольких свобод- ных массивов суммарным объемом не менее требуемого.

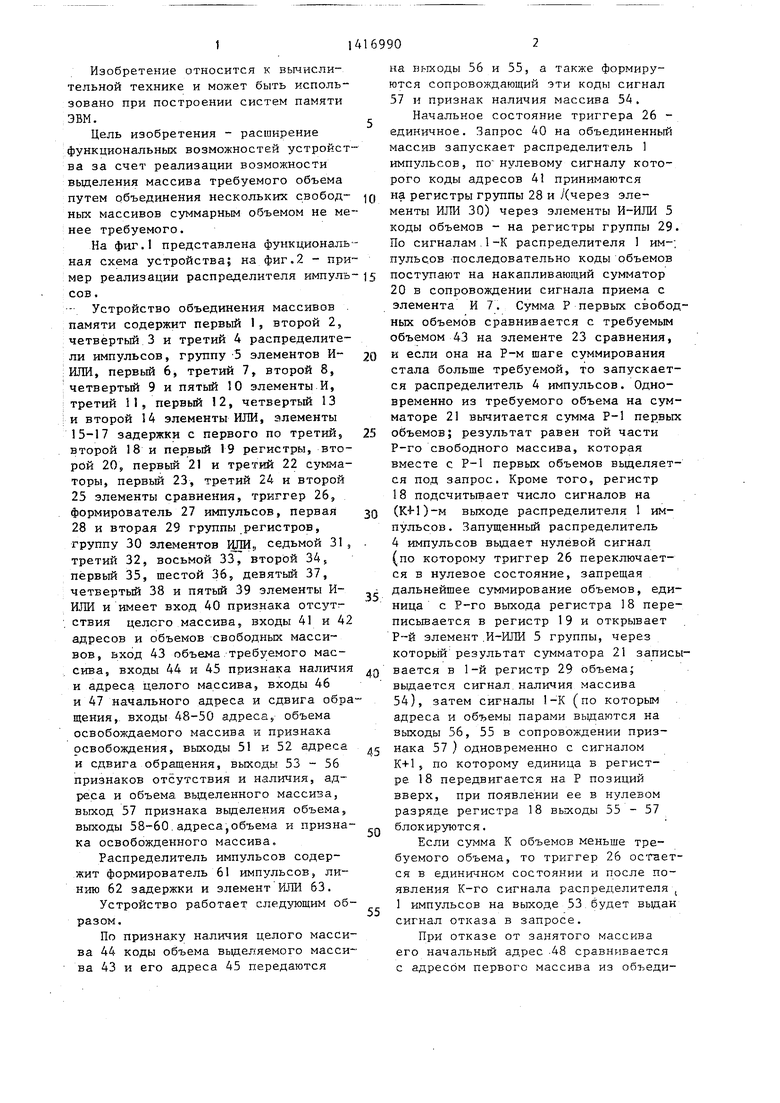

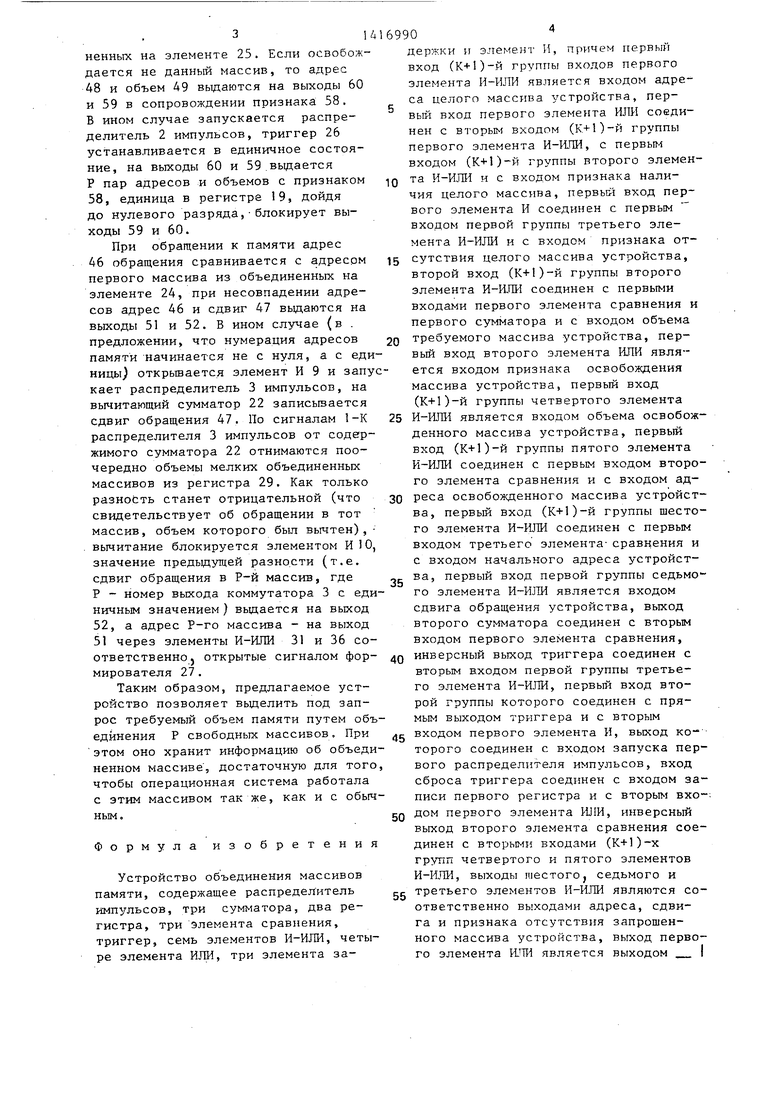

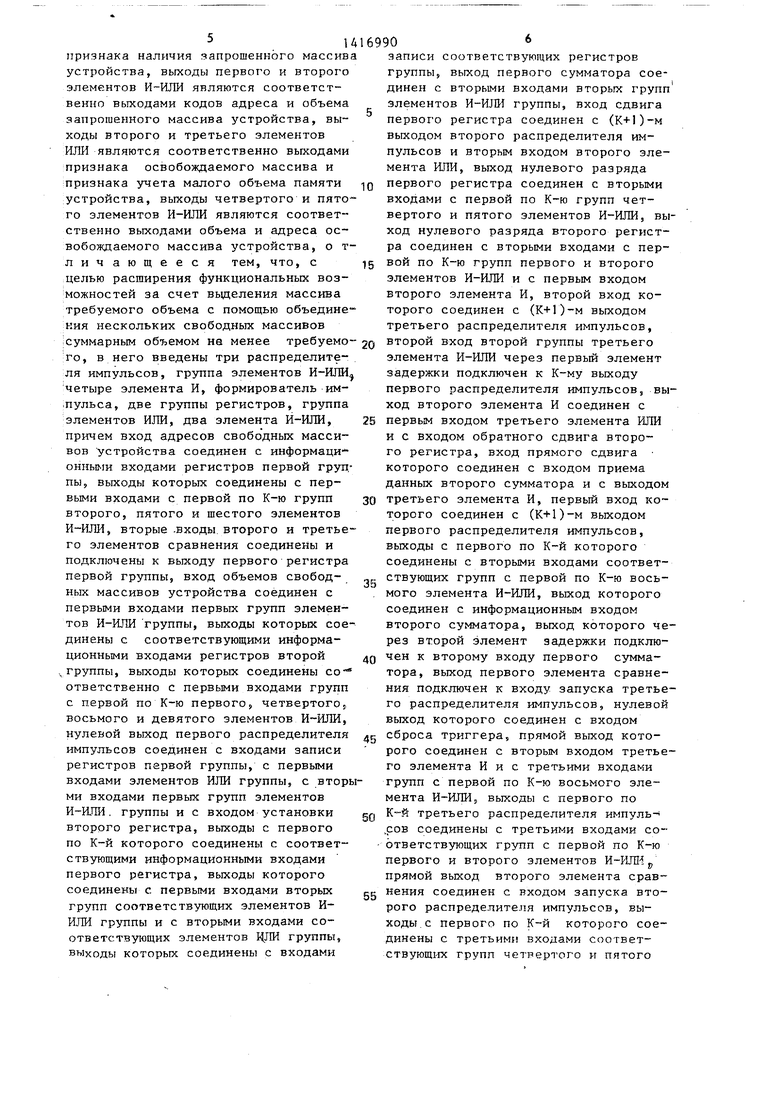

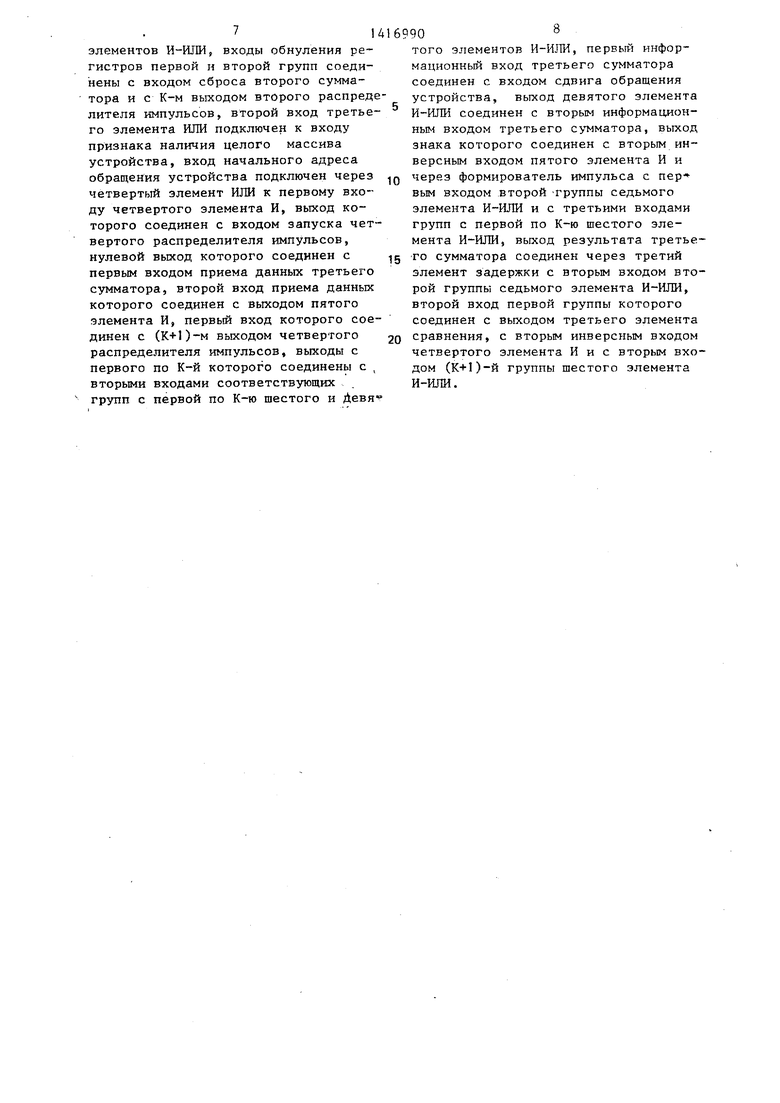

На фиг.1 представлена функциональная схема устройства; на фиг.2 - пример реализации распределителя импуль сов.

- Устройство объединения массивов памяти содержит первый 1, второй 2, четвертый 3 и третий 4 распределители импульсов, группу 5 элементов И- ИЛИ, первый 6, третий 7, второй 8, четвертый 9 и пятый 10 элементы И, третий 11, первый I2, четвертый 13 и второй 14 элементы ИЛИ, элементы 15-17 задержки с первого по третий, второй 18 и первый 19 регистры, второй 20, первый 21 и третий 22 сумматоры, первьй 23, третий 24 и второй 25 элементы сравнения, триггер 26, формирователь 27 импульсов, первая 28 и вторая 29 группы регистров, группу 30 элементов ИЛИ,, седьмой 31 , третий 32, восьмой 33, второй 34, первьш 35, шестой 36, девятый 37, четвертьш 38 и пятый 39 элементы И- ИЛИ и имеет вход 40 признака отсутствия целого массива, входы 41 и 42 адресов и объемов свободных массивов, йход 43 объема требу;емого массива, входы 44 и 45 признака наличия и адреса целого массива, входы 46 и 47 начального адреса и сдвига обращения,, входы 48-50 адреса, объема освобождаемого массива и признака освобождения, выходы 51 и 52 адреса и сдвига обращения, выходы 53 - 56 признаков отсутствия и наличия, адреса и объема выделенного массива, выход 57 признака вьщеления объема, выходы 58-60.адреса,объема и признака освобожденного массива.

Распределитель импульсов содержит формирователь 61 импульсов, линию 62 задержки и элемент ИЛИ 63.

Устройство работает следующим образом.

По признаку наличия целого массива 44 коды объема выделяемого массива 43 и его адреса 45 передаются

Q

5

0 5 о

5

на выходы 56 и 55, а также формируются сопровождающий эти коды сигнал 57 и признак наличия массива 54.

Начальное состояние триггера 26 - единичное. Запрос 40 на объединенный массив запускает распределитель 1 импульсов, ПО нулевому сигналу которого коды адресов 41 принимаются на регистры группы 28 и Дчерез элементы ИЛИ 30) через элементы И-ИЛИ 5 коды объемов - на регистры группы 29. По сигналам , 1-К распределителя 1 им-; пульсов Последовательно коды объемов поступают на накапливающий сумматор 20 в сопровождении сигнала приема с элемента И 7. Сумма Р первых свободных объемов сравнивается с требуемым объемом 43 на элементе 23 сравнения, и если она на Р-м шаге суммирования стала больше требз емой, то запускается распределитель 4 импульсов. Одновременно из требуемого объема на сумматоре 21 вычитается сумма Р-1 первых объемов; результат равен той части Р-го свободного массива, которая вместе с Р-1 первых объемов выделяется под запрос. Кроме того, регистр 18 подсчитьшает число сигналов на (К4-1)-м выходе распределителя 1 импульсов . Запущенный распределитель 4 импульсов вьщает нулевой сигнал (по которому триггер 26 переключается в нулевое состояние, запрещая дальнейшее суммирование объемов, единица с Р-го выхода регистра 18 пере- письшается в регистр 19 и открывает Р-й элемент .И-ШШ 5 группы, через которьм результат сумматора 21 записывается в 1-й регистр 29 объема; выдается сигнал.наличия массива 54), затем сигналы 1-К (по которым адреса и объемы парами вьщаются на выходы 56, 55 в сопровождении признака 57 } одновременно с сигналом К+15 по которому единица в регистре 18 передвигается на Р позиций вверх, при появлении ее в нулевом разряде регистра 18 выходы 55 - 57 блокируются.

Если сумма К объемов меньше требуемого объема, то триггер 26 остается в единичном состоянии и после появления К-го сигнала распределителя 1 импульсов на выходе 53.будет выдан сигнал отказа в запросе.

При отказе от занятого массива его начальный адрес -48 сравнивается с адресом первого массива из объеди3141

енньгх на элементе 25. Если освобожается не данный массив, то адрес 8 и объем 49 выдаются на выходы 60 и 59 в сопровождении признака 58. В ином случае запускается распреелитель 2 импульсов, триггер 26 устанавливается в единичное состояние, на выходы 60 и 59.выдается Р пар адресов и объемов с признаком 58, единица в регистре 19, дойдя до нулевого разряда,блокирует выходы 59 и 60.

При обращении к памяти адрес 46 обращения сравнивается с адресом первого массива из объединенных на элементе 24, при несовпадении адресов адрес 46 и сдвиг 47 вьщаются на выходы 51 и 52. В ином случае (в . предложении, что нумерация адресов памяти начинается не с нуля, а с единицы) открьшается элемент И 9 и запус кает распределитель 3 импульсов, на вычитающий сумматор 22 записьгаается сдвиг обращения 47. По сигналам 1-К распределителя 3 импульсов от содержимого сумматора 22 отнимаются поочередно объемы мелких объединенных массивов из регистра 29. Как только разность станет отрицательной (что свидетельствует об обращении в тот массив, объем которого был вычтен),- вычитание блокируется элементом И 10, значение предьщущей разности (т.е. сдвиг обращения в Р-й массив, где Р - номер выхода коммутатора 3 с единичным значением ) выдается на выход 52, а адрес Р-го массива - на выход 51 через элементы И-ИЛИ 31 и 36 соответственно j открытые сигналом формирователя 27 .

Таким образом, предлагаемое устройство позволяет вьщелить под запрос требуемый объем памяти путем объединения Р свободных массивов. При этом оно хранит информацию об объединенном массиве , достаточную для того, чтобы операционная система работала с этим массивом так же, как и с обычным.

Формула изобретения

Устройство объединения массивов памяти, содержащее распределитель импульсов, три сумматора, два регистра, три элемента сравнения, триггер, семь элементов И-ИЛИ, четыре элемента ИЛИ, три элемента за

90

держки и элемент И, первый вход (К+1)-й группы входов первого элемента И-ИЛИ является входом адреса целого массгша устройства, первый вход первого элемента ШШ соединен с вторым входом (К.+ 1)-й группы первого элемента И-ИГШ, с первьм входом (К+1)-й группы второго элемента И-ИЛИ и с входом признака наличия целого массива, первьы вход первого элемента И соединен с первым входом первой группы третьего элемента И-ИЛИ и с входом признака отсутствия целого массива устройства, второй вход (К+)-й группы второго элемента И-ИЛИ соединен с первыми входами первого элемента сравнения и первого сумматора и с входом объема требуемого массива устройства, пер- вьш вход второго элемента ИЛИ является входом признака освобождения массива устройства, первый вход (К+1)-й группы четвертого элемента

И-ИШi является входом объема освобожденного массива устройства, первый вход (К+О-й группы пятого элемента И-ИЛИ соединен с первым входом второго элемента сравнения и с входом адреса освобожденного массива устройства, первьш вход (К+1)-й группы шестого элемента И-ИЛИ соединен с первым входом третьего элемента-сравнения и с входом начального адреса устройства, первый вход первой группы седьмого элемента И-ИЛИ является входом сдвига обращения устройства, выход второго сумматора соединен с вторым входом первого элемента сравнения,

инверсный выход триггера соединен с вторым входом первой группы третьего элемента И-ИЛИ, первьш вход второй группы которого соединен с прямым выходом триггера и с вторым

входом первого элемента И, выход торого соединен с входом запуска первого распределителя импульсов, вход сброса триггера соединен с входом записи первого регистра и с вторым вхо-;

дом первого элемента ИЛИ, инверсньй выход второго элемента сравнения соединен с вторыми входами (К+)-х групп четвертого и пятого элементов И-ИЛИ, выходы шестогоJ седьмого и третьего элементов И-ИЛИ являются соответственно выходами адреса, сдвига и признака отсутствия запрошенного массива устройства, выход первого элемента ШТИ является выходом I

u

признака наличия запрошенного массива устройства, выходы первого и второго элементов являются соответственно выходами кодов адреса и объема запрошенного массива устройства, выходы второго и третьего элементов ИЛИ являются соответственно выходами признака освобождаемого массива и признака учета малого объема памяти устройства, выходы четвертого и пятого элементов И-ИЛИ являются соответственно выходами объема и адреса освобождаемого массива устройства, о т- личающееся тем, что, с целью расширения функциональных возможностей за счет выделения массива требуемого объема с помощью объединения нескольких свободных массивов суммарным объемом на менее требуемо- го, в него введены три распределителя импульсов, группа элементов И-ИЛИ четыре элемента И, формирователь им- .пульса, две группы регистров, группа элементов ИЛИ, два элемента Й-ИЛИ, причем вход адресов свободных массивов устройства соединен с информаци- онными входами регистров первой груд- пы, выходы которых соединены с первыми входами с первой по К-ю групп второго, пятого и шестого элементов И-ИЛИ, вторые .входы второго и третьего элементов сравнения соединены и подключены к выходу первого регистра первой группы, вход объемов свободных массивов устройства соединен с первыми входами первых групп элементов И-ИЛИ группы, выходы которых соединены с соответствующими информационными входами регистров второй группы, выходы которых соединены ответственно с первыми входами групп с первой по К-ю первого, четвертого;, восьмого и девятого элементов , нулевой вьпсод первого распределителя импульсов соединен с входами записи регистров первой группы, с первыми входами элементов ИЛИ группы, с вторЫ ми входами первых групп элементов И-Ш1И. группы и с входом установки второго регистра, выходы с первого по К-й которого соединены с соответствующими информационными входами первого регистра, выходы которого соединены с первыми входами вторых групп соответствующих элементов И- ИЛИ группы и с вторыми входами соответствующих элементов ЩШ группы, выходы которых соединены с входами

0

5

0

5

6990

записи соответствующих регистров группы, выход первого сумматора соединен с вторыми входами вторых групп элементов И-ШШ группы, вход сдвига первого регистра соединен с (К+1)-м выходом второго распределителя импульсов и вторь М входом второго элемента ИЛИ, выход нулевого разряда первого регистра соединен с вторыми входами с первой по К-ю групп четвертого и пятого элементов И-ИЛИ, выход нулевого разряда второго регистра соединен с вторыми входами с первой по К-ю групп первого и второго элементов И-ИЛИ и с первым входом второго элемента И, второй вход которого соединен с (К+1)-м выходом третьего распределителя импульсов, второй вход второй группы третьего элемента И-ИЛИ через первый элемент задержки подключен к К-му выходу первого распределителя импульсов, выход второго элемента И соединен с первым входом третьего элемента ИЛИ и с входом обратного сдвига второго регистра, вход прямого сдвига которого соединен с входом приема данных второго сумматора и с выходом третьего элемента И, первый вход которого соединен с (К+1)-м выходом первого распределителя импульсов, выходы с первого по К-й которого соединены с вторыми входами соответствующих групп с первой по К-ю восьмого элемента И-ИЛИ, выход которого соединен с информационным входом второго сумматора, выход которого через второй элемент задержки подключен к второму входу первого сумматора, выход первого элемента сравнения подключен к входу запуска третьего распределителя импульсов, нулевой выход которого соединен с входом

g сброса триггера, прямой выход которого соединен с вторым входом третьего элемента И и с третьими входами групп с первой по К-ю восьмого элемента И-ИЛИ, выходы с первого по К-й третьего распределителя импуль- ,сов соединены с третьими входами соответствующих групп с первой по К-ю первого и второго элементов И-ИШ прямой выход второго элемента сравнения соединен с входом запуска второго распределителя импульсов, выходы, с первого по К-й которого соединены с третьими входами соответствующих групп четвертого и пятого

0

0

CI

5

элементов И-ИЛИ входы обнуления регистров первой и второй групп соединены с входом сброса второго сумматора и с К-м выходом второго распределителя импульсов, второй вход третьего элемента ИЛИ подключен к входу признака наличия целого массива устройства, вход начального адреса обращения устройства подключен через четвертый элемент ИЛИ к первому входу четвертого элемента И, выход которого соединен с входом запуска четвертого распределителя импульсов, нулевой выход которого соединен с первым входом приема данных третьего сумматора, второй вход приема данных которого соединен с выходом пятого элемента И, первый вход которого соединен с (К+1)-м выходом четвертого распределителя импульсов, выходы с первого по К-й которого соединены с вторыми входами соответствующих групп с первой по К-ю шестого и Девя

того элементов И-ИЛИ, первьгй информационный вход третьего сумматора соединен с входом сдвига обращения устройства, выход девятого элемента И-ИЛИ соединен с вторым информационным входом третьего сумматора, выход знака которого соединен с вторым инверсным входом пятого элемента И и

через формирователь импульса с пер- вым входом второй Группы седьмого элемента И-ИЛИ и с третьими входами групп с первой по К-ю шестого элемента И-ИЛИ, выход результата третьего сумматора соединен через третий элемент задержки с вторьпи входом второй группы седьмого элемента , второй вход первой группы которого соединен с выходом третьего элемента

сравнения, с вторым инверсным входом четвертого эле.мента И и с вторым входом (К+1)-й группы шестого элемента И-ШШ.

фиг. 1

фиг 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресации памяти | 1986 |

|

SU1328820A1 |

| Устройство для сжатия и восстановления информации | 1983 |

|

SU1149295A1 |

| Устройство для поиска данных | 1988 |

|

SU1564648A1 |

| Устройство сопряжения с блоком памяти | 1986 |

|

SU1416989A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1413656A1 |

| Устройство для управления распределенной вычислительной системой | 1982 |

|

SU1136159A1 |

| Устройство для обнаружения и исправления ошибок | 1985 |

|

SU1368995A1 |

| Устройство управления для доменной памяти | 1987 |

|

SU1499407A1 |

| Устройство для поиска данных | 1989 |

|

SU1658170A2 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

Изобретение относится к вычисли тельной технике и может быть использовано при построении систем памяти ЭВМ. Целыо изобретения является расширение функциональных возможностей устройства за счет реализации возможности выделения массива требуемого объема путем объединения нескольких свободных массивов суммарным объемом не-менее требуемого. Объемы свободных массивов суммируются, пока сумма их не первысит требуемой. Адреса и объемы сложенных массивов запоминаются, фиксируется факт их вьщеления и в качестве адреса ответа вьщается адрес первого массива. При отказе от ресурса памяти фиксируется факт освобождения занятых объемов. 2 ил.

Составитель И.Андреев Редактор А.Огар Техред Л.Сердюкова

Заказ 4066/47

Тираж 704

ВИИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Корректор М.Пожо

Подписное

Авторы

Даты

1988-08-15—Публикация

1986-11-28—Подача