СО Од 00

;0 со

СП

Изобретение относится к вычислительной технике и может быть использовано для обнаруженш и исправления многобитовых пакетов ошибок в процессе приема и передачи информации, поступающей по многим каналам.

Цель изобретения - повьппение достоверности приема и передачи информации за счет устранения пакетов ошибок одновременно в нескольких каналах.

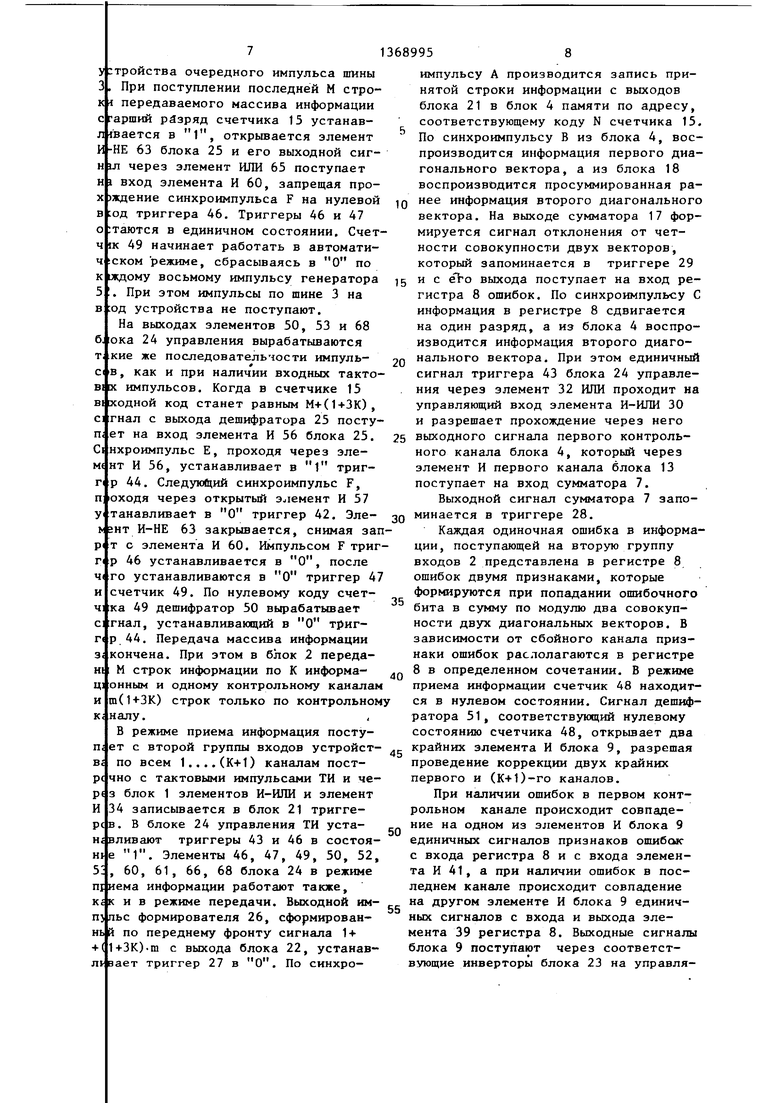

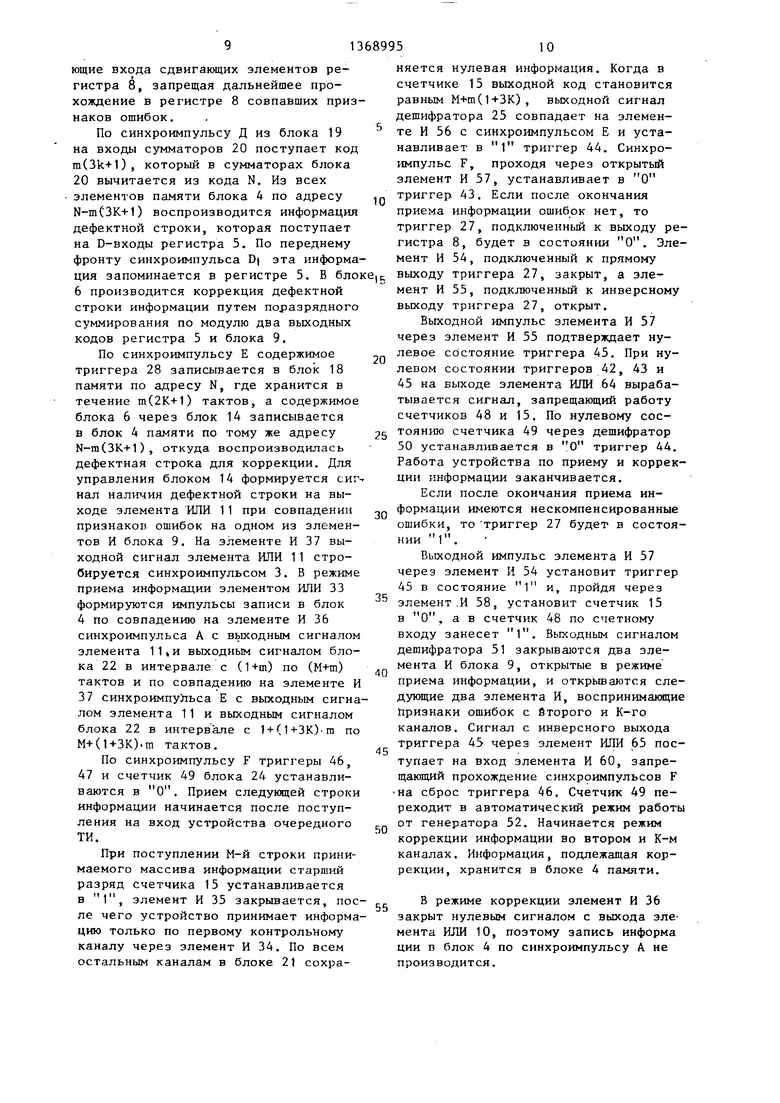

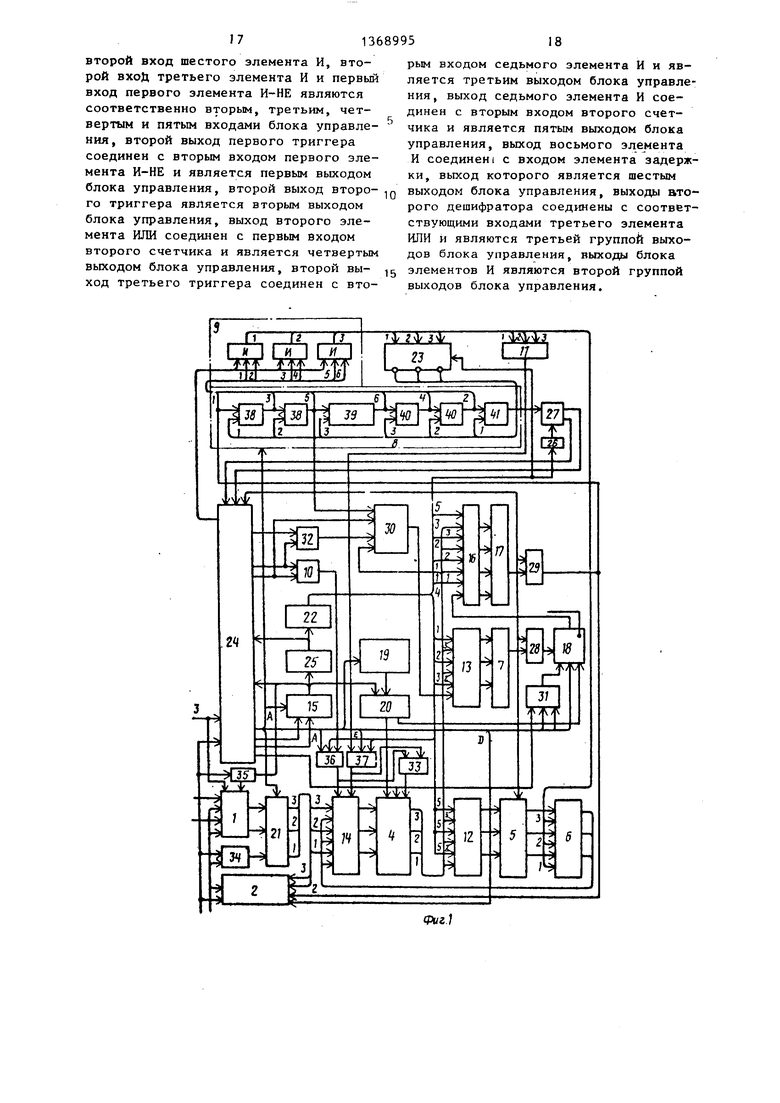

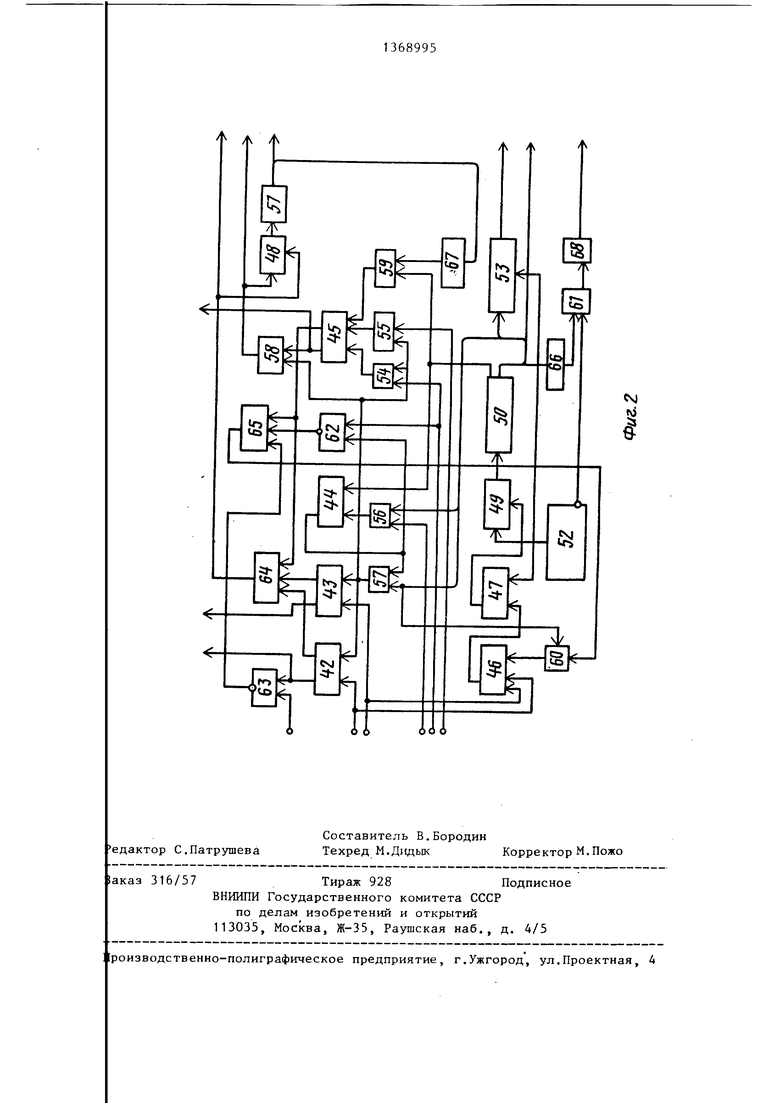

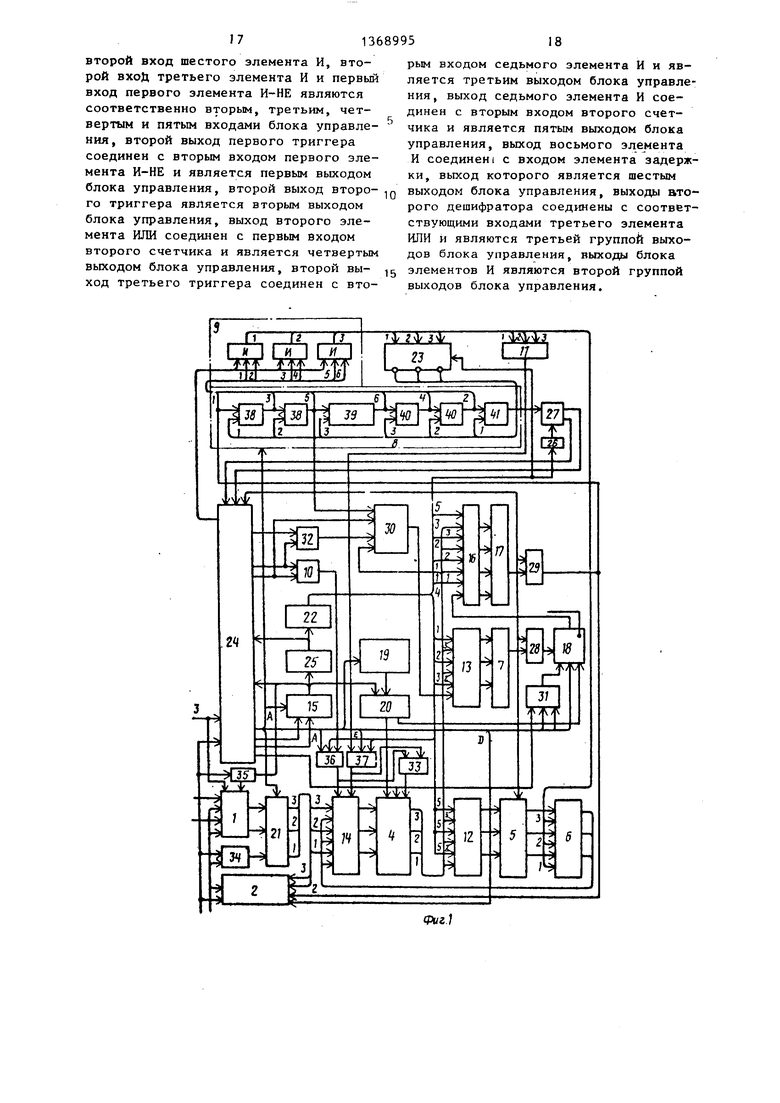

На фиг. 1 приведена функциональная схема устройства на фиг. 2 приведена функциональная схема блока управления.

Устройство (фиг. 1) содержит первый блок 1 элементов И-ИЛЙ, выходы 2 устройства, шину 3 передачи, первы блок 4 оперативной памяти, регистр 5, блок 6 сумматоров по модулю два, первый сумматор 7 по модулю два, регистр 8 ошибок, выполненный с числом пар выходов, равным числу каналов, первый блок 9 элементов И, первый 10 и второй 11 элементы ИЛИ, второй 12 и третий 13 блоки элементов И, второ блок 14 элементов И-ИЛИ, счетчик 15, четвер тый блок 16 элементов И, второй сумматор 17 по модулю два, второй блок 18 оперативной памяти, блок 19 постоянной памяти, блок 20 сумматоров, первой 21 и второй 22 блоки триггеров, блок 23 элементов ИЛИ-НЕ, блок 24 управления, дешифратор 25, формирователь 26, третий триггер 27 (RS-триггер), первый 28 и второй 29 триггеры (D-триггеры), первьй 30 и второй 31 элементы И-ИЛИ, третш 32 и четвертый 33 элементы ИЛИ, первый 34, второй 35, третий 36 и четвертый 37 элементы И.

Регистр 8 ошибок (фиг. 1) содержит первые 38, второй 39, третьи 40 элементы памяти, каждый из которых состоит из последовательно соединенных элементов И и регистра сдвига, и элемент И 41.

Блок 24 управления (фиг. 2) содержит первый 42, второй 43, шестой 44, третий 45, четвертый 46 и пятый 47 триггеры, второй 48 и первый 49 счетчики, первый 50 и второй 51 дешифраторы, генератор 52 импульсов.

блок 53 элементов И, пятый 54, шестой восстанавливаются только те ошибки, 55, третий 56, четвертый 57, седьмой признаки которых не выпадают в ре- 58, второй 59, первый 60 и восьмой 61 элементы И, второй 62 и первый 63 элементы И-НЕ, второй 64, первый 65,

зультате их взаимного наложения. Пр отсутствии ошибок в других каналах искажений информации не происходит.

0

5

5

0

5

0

5

0

третий 66 и четвертый 67 элементы ИЛИ и элемент 68 задержки.

Контроль информации на четность в предложенном устройстве производится совокупностью двух диагональных векторов. При этом адреса контролируемых на четность разрядов соседних каналов первого блока оперативной памяти смещаются блоком сумматоров на m разрядов один относительно другого, что приводит к увеличению расстояния между признаками ошибок одной строки двух соседних каналов до m разрядов. Такое смещение позволяет исключить выпадение признаков ошибок при приеме информации, содержащей дефектный массив из m строк одновременно в любом количестве дефектных каналов при обязательном наличии бездефектного промежутка между дефектными массивами.

В процессе обнаружения ошибок при приеме информации только один из контролируемых на четность разрядов находится в зоне дефектного массива, а остальные находятся в зоне бездефектных участков. Исправление ошибок производится циклично, в каждом из циклов корректируются два крайних канала. Скорректированная в каждом цикле информация записывается в первый блок оперативной памяти. В следующем цикле корректируются следующие два канала и т.д.

Предложенное устройство позволяет исключить одну из следутощлх совокупностей ошибок: любые ошибки в массиве из всех К информационных и .одного контрольного каналов по m строк в каждом; пакеты ошибок длиной (К+1);( л m разрядов по одному из двух крайних каналов при отсутствии ошибок в других каналах; пакеты сшибок длиной 2 m разрядов в К+1/2 каналах, разделенных друг от друга бездефектными каналами.

Защитный промежуток между дефектными массивами должен быть не менее 3(к+1) m строк.

При наличии двух пакетов ошибок в соседних каналах, при длине одного из пакетов, превьш ающего m разрядов.

восстанавливаются только те ошибки, признаки которых не выпадают в ре-

зультате их взаимного наложения. При отсутствии ошибок в других каналах искажений информации не происходит.

Устройство работает в трех режимах: передачи информации в блок 2, приема информации из блока 2 в блок 4 оперативной памяти, коррекции ий- фо змации, хранящейся в блоке 4 оперативной памяти.

В режиме передачи информации по К каналам 2 ... (К+1) построчно поступает на первую группу информационных входов блока 1, на управляющий вход которого и на первый вход блока 24 управления по шине 3 поступают гактовь/е импульсы. Поступающая ин- })ормация построчно через блок 1 поступает либо на выходы устройства, либо для кодирования на блок 14. В блоке 24 управления тактовые импульсы устанавливают триггеры 42 и 46 в состояние 1. По переднему фронту имтриггер 47 ус- 1, снимая запрет с установочного входа счетчика 49, который начинает работать в счетном

пульса генератора 52 танавливается в

ной памяти на входы каждого i-сум- матора блока 20 поступает код

N,

m(i-1)

0

где га - число, на которое смещены разряды соседних каналов диагонального вектора; i - 1, 2, ... () - номер канала.

В каждом i сумматоре блока 20 код . вычитается из текущего выходного

N

кода N счетчика 15. Полученная разность N - N. поступает на адресные входы соответствующих i-элементов 5 блоки 4, на управляющие входы которых с выхода элемента 33 поступает команда воспроизведения. Из блока 4 по заданным адресам N - N . воспроизводится информация первого вектора, которая через блок 16 элементов И поступает в сумматор 17 по модулю два.

Одновременно по синхроимпульсу В из блока 19 на входы соответствующе0

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для ввода информации | 1981 |

|

SU1005019A1 |

| Устройство для вывода графической информации | 1989 |

|

SU1644208A1 |

| Устройство для сопряжения | 1983 |

|

SU1129603A1 |

| Устройство для ввода информации | 1990 |

|

SU1709326A1 |

| Устройство для записи-воспроизведения многоканальной информации | 1984 |

|

SU1190410A1 |

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

| Устройство для многоканальной записи-воспроизведения информации | 1985 |

|

SU1273992A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

режиме по задним фронтам выходных им- 25 ° сумматора блока 20 поступает код

1ульсов генератора 52. В дешифраторе 50 формируется последовательность 13 шести синхроимпульсов А, Б, С, 3, Е, F, длительность каждого из ко- горых равна периоду Т генератора 52. J блоке 53 элементов И формируется юследовательность из трех синхроИм- 1ульсов BI , С,, DI длительностью Т/2. Три этом задние фронты одноименных (например ВиВ,, СиС,, ПиО,) ;инхроимпульсов дешифратора 50 и бло- са 53 совпадают. Сигналом с инверсно- о выхода триггера 42 через элемент 1ПИ 64 снимается запрет с установоч- 1ЫХ входов счетчика 48 и счетчика15.

Синхроимпульсы А поступают на }ход счетчика 15, увеличивая на 1 его 5ЫХОДНОЙ код, который через блок 20 :умматоров поступает на адресные

ходы блока 4 оперативной памяти. При g рядного элемента 39 сдвига, ш-разряд том на другие входы блока 20 сумма- ных К элементов 40 сдвига и элемента

оров с выхода блока 19 постоянной

1амяти поступает нулевой код. По

;инхроимпульсу А, поступающему через

шемент И 36 на управляющий вход блоса 14, строка информации из блока 21

50

И 41. Выходы элементов сдвига регистра 8 попарно подключены к элементам И блока 9, выходы которых подключены к управляющим входам элементов сдвига регистра 8.

триггеров записьшается в блок 4 памя- и по адресу, соответствующему коду ;четчика 15.

По синхроимпульсу В из б/юка 4 юспроизводится информация первого 5иагонального вектора. Для этого по ;инхроимпульсу В из блока 19 постоян0

5

0

т-(2К+1), который в сумматоре блока 20 вычитается из кода N. Из однока- нального блока 18 памяти по адресу N-m(2K+1) воспроизводится просуммированная ранее информация второго вектора, которая также поступает в сумматор 17. На выходе сумматора 17 формируется сигнал отклонения от четности совокупности двух векторов, который по переднему фронту синхроимпульса В,, запоминается в триггере 29 и с его выхода поступает на вход регистра 8 ошибок и на выход устройства.

Регистр 8 ошибок представляет собой последовательный управляемый регистр сдвига, состоящий из К последовательно включенных т-разрядных элементов 38 сдвига, одного (К+1) m раз0

5

И 41. Выходы элементов сдвига регистра 8 попарно подключены к элементам И блока 9, выходы которых подключены к управляющим входам элементов сдвига регистра 8.

По синхроимпульсу С информация в регистре 8 сдвигается на один разряд, а из блока 4 воспроизводится информация второго диагонального век- тора. При этом из блока 19 на входы соответствующих сумматоров блока 20 поступает код

Na, m(K+1-i),

5

который в каждом сумматоре блока 20 вычитаемся из кода N. В результате адреса соседних элементов блока 4

смещаются на m разрядов в другом на

равлении по сравнению с ранее рассмренным формированием разрядов первого вектора. Воспроизведенная информция второго вектора поступает через блок 13 элементов И на информационн входы 2...К сумматора 7 по модулю два. На первый информационный вход сумматора 7 через элемент И-ИЛИ 30, открытый по соответствующему входу единичным сигналом с триггера 42 блка 24, и элемент И блока 13 поступа выходная информация регистра 8 ошибок, смещенная на К строк. На выход сумматора 7 формируется сигнал отклонения от четности второго вектор которьш по переднему фронту синхроимпульса С запоминается в триггере 28.

По синхроимпульсу Е содержимое триггера 28 записывается в блок 18 памяти по адресу N, где хранится в течение т(2К+1) тактов до момента ее воспроизведения в блок 17.

В результате после поступления каждой строки передаваемой информации на выходы 2 устройства поступае информация с 2...(К+1) выходов блок 21 триггеров, а на вход контролььгог канала поступают сигналы с выхода триггера 29, которые представляют сбой дополнение до четности суммы дв диагональных векторов. Блок 9 и тригер 27 в этом режиме не работают.

Для повышения помехоустойчивости устройства в него введены дешифрато 25 и блок 22 триггеров. Из выходных кодовых сигналов счетчика 15 дешифратор 25 формирует две последовательности импульсов. Первая последовательность импульсов дешифратора 2 соответствует следующим кодовым комбинациям счетчика 15:1, 1+т, 1+2т, ..., 1+К-т, 1+(1+2К).т, 1+С1+ЗК) т. Вторая последовательность импульсов дешифратора 25 смещена относительно импульсов первой последовательности на количество строк М массива передваемой информации. Импульсы первой и второй последовательности попарно подаются с выходов дешифратора 25 н установочные входы триггеров блока 22. В результате на выходах блока 2 формируются управляющие сигналы длительностью М строк, смещенные один

5

0

5

относительно другого в соответствии с разностью между кодовыми комбинациями первой (второй) последовательности. При этом первый канал блока 16 и (K-t-l), канал блока 13 открыты для прохождения информационных импульсов на время с 1 по М кодовые комбинации счетчика 15, второй канал блока 16 и К канал блока 13 открыты на время с (1+т) по (М+га) кодовые комбинации счетчика 15 и т.д. Выходные импульсы блока 18 проходят через блок 16 элементов И только в течение с 1+(1+2К)-т по М+т(1+2К) кодовые комбинации счетчика 15, а все входы блока 12 элементов И открыты на время с 1+(1+ЗК) m по ) кода счетчика 15.

Сигналы разрешения операций для блока 4 памяти формируются в блоке 24 с помощью элементов 66, 61, 68. Объединенные элементом ИЛИ 66 выходные синхроимпульсы А...Е дешифратора 50 поступают на один вход элемента И 61, на другой вход которого поступают импульсы с инверсного выхода генератора 52. На выходе элемента И 61 формируются импульсы длительностью Т/2, передние фронты которых совпадают с передними фронтами синхроимпульсов А . ..Е. Элемент 68 задержи- )эает выходные импульсы элемента И 61 на время (20-30) не, необходимое для обеспечения нормальной работы блоков 4 и 18.

Выходные импульсы элемента 68 задержки подаются на вход разрешения блока 4 непосредственно, а на вход разрешения блока 18 через элемент ИИЛИ 31, управляемый синхроимпульсами А и Е. На вход записи блока 18 поступают синхроимпульсы Е с выхода дешифратора 50. В режиме передачи ин- формации на вход записи блока 4 поступают синхроимпульсы А, которые формируются элементами И 36 и ИЛИ 33 по выходному сигналу блока 22 триггеров в интервале с (1+т) по (М+т) входных импульсов шины 3. В конце передачи каждой строки информации синхроимпульс F дешифратора 50 через элемент И 60 устанавливает триггер 46 в О, после чего последовательно устанавливаются в О триггер 47 и счетчик 49. Синхроимпульсом F устанавливаются в О триггеры блока 21. Передача следующей строки информации начинается после поступления на вход

0

5

0

0

5

:тройства очередного импульса шины

При поступлении последней М стро- I передаваемого массива информации арший разряд счетчика 15 устанав10

НЕ 63 блока 25 и его выходной сиг- ш через элемент ИЛИ 65 поступает I вход элемента И 60, запрещая про- ждение синхроимпульса F на нулевой од триггера 46, Триггеры 46 и 47 таются в единичном состоянии, Счет- к 49 начинает работать в автомати- ском режиме, сбрасываясь в О по 1ЖДОМУ восьмому импульсу генератора g

При этом импульсы по шине 3 на од устройства не поступают.

На выходах элементов 50, 53 и 68 ока 24 управления вырабатываются

геается в

11 11

открьгоается элемент

кие же последовательности импульBI к импульсов. Когда в счетчике 15 В1 ходкой код станет равным М+(1+ЗК), гнал с выхода дешифратора 25 постуС1

п; Ci м

ет на вход элемента И 56 блока 25, нхроимпульс Е, проходя через эле- нт И 56, устанавливает в 1 триг- р 44, Следую6(ий синхроимпульс F, оходя через открытый элемент И 57 танавливает в О триггер 42, Эле- 1ФНТ И-НЕ 63 закрывается, снимая зап т с элемента И 60, Импульсом F триг- р 46 устанавливается в О, после го устанавливаются в О триггер 47 счетчик 49, По нулевому коду счет- ка 49 дешифратор 50 вырабатывает гнал, устанавливающий в О триг- р 44, Передача массива информации кончена. При этом в блок 2 передаМ строк информации по К информа- онным и одному контрольному каналам т(1+ЗК) строк только по контрольном налу,

В режиме приема информация посту

ет с второй группы входов устройст- . крайних элемента И блока 9, разрешая

по всем 1,..,(К+1) каналам пост- чно с тактовыми импульсами ТИ и че- 3 блок 1 элементов И-ШШ и элемент И 34 записьшается в блок 21 триггере в, В блоке 24 управления ТИ уста- н вливают триггеры 43 и 46 в состоя- те 1, Элементы 46, 47, 49, 50, 52, 5: , 60, 61, 66, 68 блока 24 в режиме п;иема информации работают также, Кс к и в режиме передачи. Выходной ин- njпьс формирователя 26, сформирован- ньи по переднему фронту сигнала 1+

1+ЗК).т с выхода блока 22, устанав- Л1-эает триггер 27 в О, По синхро50

55

проведение коррекции двух крайних первого и (К+1)-го каналов.

При наличии ошибок в первом контрольном канале происходит совпадение на одном из элементов И блока 9 единичных сигналов признаков ошибок с входа регистра 8 и с входа элемента И 41, а при наличии ошибок в последнем канапе происходит совпадение на другом элементе И блока 9 единичных сигналов с входа и выхода элемента 39 регистра 8, Выходные сигналы блока 9 поступают через соответствующие инверторы блока 23 на управля0

g

0

0

5

5

0

импульсу А производится запись принятой строки информации с выходов блока 21 в блок 4 памяти по адресу, соответствующему коду N счетчика 15. По синхроимпульсу В из блока 4, воспроизводится информация первого диагонального вектора, а из блока 18 воспроизводится просуммированная ранее информация второго диагонального вектора. На выходе сумматора 17 формируется сигнал отклонения от четности совокупности двух векторов, который запоминается в триггере 29 и с ёЪо выхода поступает на вход регистра 8 ошибок. По синхроимпульсу С информация в регистре 8 сдвигается на один разряд, а из блока 4 воспроизводится информация второго диагонального вектора. При этом единичный сигнал триггера 43 блока 24 управления через элемент 32 ИЛИ проходит на управляющий вход элемента И-ИЛИ 30 и разрешает прохождение через него выходного сигнала первого контрольного канала блока 4, который через элемент И первого канала блока 13 поступает на вход сумматора 7,

Выходной сигнал сумматора 7 запоминается в триггере 28,

Каждая одиночная ошибка в информации, поступающей на вторую группу входов 2 представлена в регистре 8 ошибок двумя признаками, которые формируются при попадании ошибочного бита в сумму по модулю два совокупности двух диагональных векторов, В зависимости от сбойного канала признаки ошибок располагаются в регистре 8 в определенном сочетании, В режиме приема информации счетчик 48 находится в нулевом состоянии. Сигнал дешифратора 51, соответствующий нулевому состоянию счетчика 48, открьшает два

0

5

проведение коррекции двух крайних первого и (К+1)-го каналов.

При наличии ошибок в первом контрольном канале происходит совпадение на одном из элементов И блока 9 единичных сигналов признаков ошибок с входа регистра 8 и с входа элемента И 41, а при наличии ошибок в последнем канапе происходит совпадение на другом элементе И блока 9 единичных сигналов с входа и выхода элемента 39 регистра 8, Выходные сигналы блока 9 поступают через соответствующие инверторы блока 23 на управляющие входа сдвигающих элементов регистра 8, запрещая дальнейшее прохождение в регистре 8 совпавших признаков ошибок.

По синхроимпульсу Д из блока 19 на входы сумматоров 20 поступает код m(3k+1), который в сумматорах блока 20 вычитается из кода N. Из всех элементов памяти блока 4 по адресу N-m(3K+1) воспроизводится информация дефектной строки, которая поступает на D-входы регистра 5. По переднему фронту синхроимпульса D) эта информа10

няется нулевая информация. Когда в счетчике 15 выходной код становится равным М+т(1+ЗК), выходной сигнал дешифратора 25 совпадает на элементе И 56 с синхроимпульсом Е и устанавливает в 1 триггер 44. Синхроимпульс F, проходя через открытый элемент И 57, устанавливает в О триггер 43. Если после окончания приема информации ошибок нет, то триггер 27, подключенный к выходу р гистра 8, будет в состоянии О. Эл мент И 54, подключенный к прямому

ция запоминается в регистре 5. В блоке,с выходу триггера 27, закрыт, а эле vJ

мент И 55, подключенный к инверсном выходу триггера 27, открыт.

6 производится коррекция дефектной строки информации путем поразрядного суммирования по модулю два выходных кодов регистра 5 и блока 9.

По синхроимпульсу Е содержимое триггера 28 записывается в блок 18 памяти по адресу N, где хранится в течение т(2К+1) тактов, а содержимое блока 6 через блок 14 записывается в блок 4 памяти по тому же адресу N-m(3K+1), откуда воспроизводилась дефектная строка для коррекции. Для управления блоком 14 формируется сигнал наличия дефектной строки на выходе элемента ИЛИ 11 при совпадении признаков ошибок на одном из элементов И блока 9. На элементе И 37 выходной сигнал элемента ИЛИ 11 стро- бируется синхроимпульсом 3. В режиме приема информации элементом ИЛИ 33 формируются импульсы записи в блок 4 по совпадению на элементе И 36 синхроимпульса А с вькодным сигналом элемента выходным сигналом блока 22 в интервале с (1+т) по (М+т) тактов и по совпадению на элементе И 37 синхроимпу 1ьса Е с выходным сигналом элемента 11 и выходным сигналом блока 22 в интервале с 1+(1+ЗК).га по (1+ЗК) т тактов.

По синхроимпульсу F триггеры 46, 47 и счетчик 49 блока 24 устанавливаются в О. Прием следующей строки информации начинается после поступления на вход устройства очередного ТИ.

При поступлении М-й строки принимаемого массива информации старший разряд счетчика 15 устанавливается в 1, элемент И 35 закрывается, после чего устройство принимает информацию только по первому контрольному каналу через элемент И 34. По всем остальным каналам в блоке 21 сохра

няется нулевая информация. Когда в счетчике 15 выходной код становится равным М+т(1+ЗК), выходной сигнал дешифратора 25 совпадает на элементе И 56 с синхроимпульсом Е и устанавливает в 1 триггер 44. Синхроимпульс F, проходя через открытый элемент И 57, устанавливает в О триггер 43. Если после окончания приема информации ошибок нет, то триггер 27, подключенный к выходу регистра 8, будет в состоянии О. Элемент И 54, подключенный к прямому

мент И 55, подключенный к инверсному выходу триггера 27, открыт.

Выходной импульс элемента И 57 через элемент И 55 подтверждает нулевое сЬстояние триггера 45. При нулевом состоянии триггеров 42, 43 и 45 на выходе элемента ИЛИ 64 вырабатывается сигнал, запрещающий работу счетчиков 48 и 15. По нулевому сос- тоянию счетчика 49 через дешифратор 50 устанавливается в О триггер 44. Работа устройства по приему и коррекции информации заканчивается.

Если после окончания приема информации имеются нескомпенсированные ошибки, то триггер 27 будет в состоянии 1.

Выходной импульс элемента И 57 через элемент И 54 установит триггер 45 в состояние 1 и, пройдя через элемент ,И 58, установит счетчик 15 в О, а в счетчик 48 по счетному входу занесет 1. Выходным сигналом дешифратора 51 закрываются два элемента И блока 9, открытые в режиме приема информации, и открьшаются следующие два элемента И, воспринимающие признаки ошибок с второго и К-го каналов. Сигнал с инверсного выхода триггера 45 через элемент ИЛИ 65 поступает на вход элемента И 60, запрещающий прохождение синхроимпульсов F на сброс триггера 46. Счетчик 49 переходит в автоматический режим работы от генератора 52. Начинается режим коррекции информации во втором и К-м каналах. Информация, подлежащая коррекции, хранится в блоке 4 памяти.

В режиме коррекции элемент И 36 закрыт нулевым сигналом с выхода эле мента ИЛИ 10, поэтому запись информа ции в блок 4 по синхроимпульсу А не производится.

ода элемента И 57 поступает на вхо- ы элементов 54 и 55. В зависимости т состояния триггера 27 триггер 45

По синхроимпульсам В,С, D, Е уст- ойство работает аналогично его ра- оте в режиме воспроизведения. Отли- ие состоит в том, что триггер 43 на- одится в состоянии О, а триггер 5 в состоянии 1 и его выходной игнал через элемент 32 открьшает лемент 30 для прохождения через не- о выходного сигнала первого конт- ольного канала блока 4. Счетчик 49 аботает в режиме коррекции только

автоматическом . Когда в счет- ике 13 выходной код становится рав- ым М+(1+ЗК), синхроимпульс F с вы- 15

10

;

ибо устанавливается в О, прекращая

альнейшую коррекцию информации, либо 2о элемента И, первая группа информациматор по модулю два, регистр ошибок, первые выходы которого соединены с со.ответствующими входами первого блока элементов И, первый и второй элементы ИЛИ, второй и третий блоки элементов И, второй блок элементов И-ИЛИ, счетчик, отличающее- с я тем, что, с целью повышения достоверности устройства, в него введены четвертый блок элементов И, второй сумматор по модулю два, второй блок оперативной памяти, блок постоянной памяти, блок сумматоров, первый и втЭрой блоки триггеров, блок элементов ИЛИ-НЕ, блок управления,-дешиф ратор, формирователь, три триггера, пе.рвый и второй элементы И-ИЛИ, третий и четвертый элементы ИЛИ, четыре

стается в единичном состоянии. Тога импульс F с выхода элемента 57 гроходит через элемент И 58 и увелиивает на 1 код в счетчике 48. Выодные сигналы дешифратора 51 подклю- 25 ны следующие два элемента И блока

счетчик 15 сбрасывается в О. Iачинается следующий цикл коррекции вух крайних из оставшихся нескоррек- тированных каналов.2о

Если после проведения коррекции сЬного или двух -последних каналов триггер 27 останется в состоянии 1, 10 выходной сигнал дешифратора 51

эрез элемент 67 открывает элемент I 59. Сигнал с дешифратора 50, соот- Iетствующий нулевому состоянию счет- ка 49, проходит через элемент И 59 устанавливает триггер 45 в О.

Режим коррекции заканчивается.Еди- iJiMHoe состояние триггера 45 в конце

эррекции перед его окончательной ус- 1ановкой в О свидетельствует о неисправленных ошибок в массиве и{формации. Дальнейшее устранение ошиDK возможно путем повторного проведе- коррекции, начиная с двух крайних

шалов 1 и К+1.

35

40

45

онных входов первого блока элементов И-ИЛИ является первой группой информационных входов устройства, шина записи подключена к первому входу блока управления, выход первого элемента И и выходы первого блока элементов И-ИЛИ соединены с группой входов первого блока триггеров, выходы которого соединены с первой группой информационных входов второго блока элементов И-ИЛИ, вторая группа информационных входов которого подключена к выходам блока сумматоров по модулю два, выходы второго блока элементов И-ИЛИ соединены с соответствующими информационными входами первого блока оперативной памяти, выходы которого соединены с соответствующими первыми информационными входами второго и четвертого блоков элементов И, первый из выходов первого блока оперативной памяти соединен с первым информационным входом первого элемента И-ИЛИ, выход которого и остальные выходы первого блока оперативной памяти соединены с соответствующими информационными входами третьего блока элементов И, выходы третьего блока элементов И через первый сумматор по модулю два соединены с информационным входом первого триггера, выход которого соединен с информационным входом второго блока оперативной памяти, выход которого соединен с вторым информационным входом четвертого блока элементов И, выходы которого через второй сумматор по модулю два соединены с информационньм входом второго триггера, выход которого соеормула изобретения

0

матор по модулю два, регистр ошибок, первые выходы которого соединены с со.ответствующими входами первого блока элементов И, первый и второй элементы ИЛИ, второй и третий блоки элементов И, второй блок элементов И-ИЛИ, счетчик, отличающее- с я тем, что, с целью повышения достоверности устройства, в него введены четвертый блок элементов И, второй сумматор по модулю два, второй блок оперативной памяти, блок постоянной памяти, блок сумматоров, первый и втЭрой блоки триггеров, блок элементов ИЛИ-НЕ, блок управления,-дешифратор, формирователь, три триггера, пе.рвый и второй элементы И-ИЛИ, третий и четвертый элементы ИЛИ, четыре

5

о

5

0

5

0

5

онных входов первого блока элементов И-ИЛИ является первой группой информационных входов устройства, шина записи подключена к первому входу блока управления, выход первого элемента И и выходы первого блока элементов И-ИЛИ соединены с группой входов первого блока триггеров, выходы которого соединены с первой группой информационных входов второго блока элементов И-ИЛИ, вторая группа информационных входов которого подключена к выходам блока сумматоров по модулю два, выходы второго блока элементов И-ИЛИ соединены с соответствующими информационными входами первого блока оперативной памяти, выходы которого соединены с соответствующими первыми информационными входами второго и четвертого блоков элементов И, первый из выходов первого блока оперативной памяти соединен с первым информационным входом первого элемента И-ИЛИ, выход которого и остальные выходы первого блока оперативной памяти соединены с соответствующими информационными входами третьего блока элементов И, выходы третьего блока элементов И через первый сумматор по модулю два соединены с информационным входом первого триггера, выход которого соединен с информационным входом второго блока оперативной памяти, выход которого соединен с вторым информационным входом четвертого блока элементов И, выходы которого через второй сумматор по модулю два соединены с информационньм входом второго триггера, выход которого соединен с информационным входом регистра ошибо к, второй выход регистра ошибок соединен с первым входом третьего триггера, первый и второй выходы которого соединены соответственно с вторым и третьим входами блока управления, первый выход первой группы выходов блока управления соединен с информационным входом счетчика, первым входом третьего элемента И и первым управляющим входом второго элемента И-ИЛИ, второй, третий, четвертый и пятый выходы первой группы выходов блока управления соединены с соответ- ствующими адресными входами блока постоянной памяти, выходы которого соединены с первой группой входов блока сумматоров, первая и вторая группы выходов блока сумматоров соединены с адресными входами соответственно первого и второго блоков оперативной памяти, третий выход первой группы выходов блока управления соединен с синхронизирующим входом регистра оши- бок, четвертый выход первой группы выходов блока управления соединен с первым входом четвертого элемента И, вторым управляющим входом второго элемента И-ИЛИ, входом записи второ- го блока оперативной памяти, пятый выход первой группы выходов блока управления соединен с входом первого блока триггеров, первый выход блока управления соединен с первьм входом первого элемента ИЛИ и вторым входом первого элемента И-ИЛИ, второй и третий выходы блока управления соединены соответственно с объединенными вторым входом первого и первым входом третьего элементов ИЛИ и вторым входом третьего элемента ИЛИ, выходы первого и третьего элементов ИЛИ соединены соответственно с вторым входом третьего элемента И и третьим входом первого элемента И-ИЛИ, четвертый вход которого подключен к третьему выходу регистра ошибок, четвертый и пятый выходы блока управления соединены соответственно с первым и вторым установочными входами счетчика, шестой выход блока управления соединен с входом разрешения первого блока оперативной памяти информационным входом второго элемента И-ИЛИ, выход которого соединен с входом разрешения второго блока оперативной памяти, первый, второй и третий выходы второй группы выходов блока управления

5 Q

5

соединены с вторыми входами соответственно второго триггера, первого триггера и первыми входами регистра, вторые входы регистра подключены к соответствующим выходам второго блока элементов И, третья группа выходов блока управления соединена с соответствующими управляющими входами первого блока элементов И, выходы которого соединены с соответствующими вторыми входами блока сумматоров по модулю два, первыми входами блока элементов ИЛИ-НЕ и входами второго элемента ИЛИ, выходы которого соединены с вторым входом четвертого элемента И, выходы блока элементов ИЛИ- НЕ соединены с соответствующими управляющими входами регистра ошибок, выходы разрядов счетчика соединены с соответствующими входами дешифратора и вторыми входами блока сумматоров , прямой и инверсный выходы старшего разряда счетчика соединены соответственно с четвертым входом блока управления и вторым входом второго элемента И, выход которого соединен с вторым управляющим входом первого блока элементов И-ИЛИ, первый и вторые выходы дешифратора соединены соответсГтвенно с пятым входом блока управления и установочными входами второго блока триггеров, группа выходов второго блока триггеров подключена к группе управляющих входов третьего блока элементов И и к первым управляющим входам четвертого блока элементов И, один выход второго блока триггеров соединен с вторым управляющим входом четвертого блока элементов И, другой выход второго блока триггеров соединен с управляющим вхо- Дом второго блока элементов И и с третьим входом четвертого элемента И, второй группой входов блока элементов ИЛИ-НЕ и через формирователь соединен с вторым входом третьего триггера, первый выход группы выходов второго блока триггеров соединен с третьим входом третьего элемента И, выходы третьего и четвертого элементов И соединены соответственно с объединенными первыми и вторыми управляющими входами второго блока элементов И-ШШ и четвертым входом элемента ИЛИ, выход которого соединен с входом записи первого блока оперативной памяти, объединенные шестой вход блока управления и второй вход

и

ю

Ф

Т

ф

юс

Дс

16

15 ,1368995

рвого элемента И и объединенные орые группы входов первого блока ементов И-ИЛИ и первого элемента являются второй группой информаци- ных входов устройства, шестой вы- д первой группы выходов блока уп- вления, выход второго триггера и гходы первого блока триггеров явля- ся выходами устройства.IQ

2, Устройство по п. 1, о т л и- а ю щ е е с я тем, что регистр :ибок содержит первые блоки памяти, ело которых равно числу информацион- tx каналов, второй блок памяти, тре- ig и блоки памяти, число которых равчислу информационных каналов и емент И, выход каждого первого блопамяти соединен с информационным одом последующего, выход последнего 2о объединенными первым входом четверпервых блоков памяти соединен с формационным входом второго блока мяти, выход которого соединен с ин- рмационным входом первого из тре- их блоков памяти, выход каждого етьего блока памяти соединен с ин- рмационным входом каждого последу- его, выход последнего из третьих оков памяти соединен с первым вхо- м элемента И, выход которого явля- ся первым выходом регистра, инфор- ционный вход первого из первых бло- в памяти является управляющим вхопервый выход первого триггера соединен с первым входом второго элемента ИЛИ, второй вход которого подключен к первому выходу второго триггера, первый выход третьего триггера соединен с объединенньми вторым входом первого и третьим входом второго элементов ИЛИ, выход четвертого триггера соединен с первым входом пятого триггера, выход которого соединен с первым входом первого счетчика, выход которого соединен с входом первого дешифратора, первьп выход первого дешифратора соединен с объединенными первыми входами второго элементу И и шестого триггера, вторые выходы первого дешифратора соединены соответственно с первым входом третьего

25

30

КС

дсм регистра, объединенные управляю-

того и вторым входом первого элементов И, соответствующими первыми входами блока элементов И и входами третьего элемента ИЛИ и являются первой группой выходов блока управления, выходы третьего и четвертого элементов И соединены соответственно с вторым входом шестого триггера и объединенными первыми входами первого и второго триггеров, пятого, шестого и седьмого элементов И, выходы пятого и шестого элементов И соединены соответственно с первым и вторым входами третьего триггера, третий вход которого подключен к выходу второго элемента И, выход шестого триггера соединен с объединенным вторым входом четвертого элемента И и первым входом второго элемента И-НЕ, выход которого соединен с третьим входом первого элемента ИЛИ, первый выход генератора импульсов соединен с объединенными вторыми входами пятого триггера, первого счетчика и блока элементов И, второй выход генератора импульсов соединен с первым входом восьмого элемента И, второй вход которого подключен к выходу третьего элемента ИЛИ, выход первого элемента И соединен с первым входом четвертого триггера, выход второго счетчика соединен с входом второго дешифратора, объединенные вторые входы первого, четвертого триггеров и объединенные второй вход второго, третий вход четвертого триггера являются соответственно первым и шестым входом блока управления, объединенные вторые входы второго элемента И-НЕ и пятого элемента И,

щ м

flf

ПС

Щ1

пг ю

В}

и:

и вход первого из первых блоков па ти и второй вход элемента И, объе- ненные управляющие входы каждого следующего из первых блоков памяти каждого из предыдущих третьих бло- кс|в памяти и объединенные управляю- е входы первого из третьих блоков мяти и второго блока памяти явля- ся соответствующими управляющими одами регистра, выход последнего

первых блоков памяти и выходы пер вь|х и второго и третьих блоков памяТ1

ее Д

КР

Д та

являются соответственно вторым и ответствующими управляющими выхо- ми регистра.

о т л и- блок управ- содержит элементы И-НЕ, триг- г эы, элементы И, элементы ИЛИ, счет- 41 и, дешифраторы, блок элементов И, ге чератор импульсов и элемент задерж-

выход первого элемента И-НЕ сое- 1ен с первым входом первого элеменИЛИ, выход которого соединен с пеЬвым входом первого элемента И,

16

объединенными первым входом четверпервый выход первого триггера соединен с первым входом второго элемента ИЛИ, второй вход которого подключен к первому выходу второго триггера, первый выход третьего триггера соединен с объединенньми вторым входом первого и третьим входом второго элементов ИЛИ, выход четвертого триггера соединен с первым входом пятого триггера, выход которого соединен с первым входом первого счетчика, выход которого соединен с входом первого дешифратора, первьп выход первого дешифратора соединен с объединенными первыми входами второго элементу И и шестого триггера, вторые выходы первого дешифратора соединены соответственно с первым входом третьего

5

0

5

0

g

0

5

того и вторым входом первого элементов И, соответствующими первыми входами блока элементов И и входами третьего элемента ИЛИ и являются первой группой выходов блока управления, выходы третьего и четвертого элементов И соединены соответственно с вторым входом шестого триггера и объединенными первыми входами первого и второго триггеров, пятого, шестого и седьмого элементов И, выходы пятого и шестого элементов И соединены соответственно с первым и вторым входами третьего триггера, третий вход которого подключен к выходу второго элемента И, выход шестого триггера соединен с объединенным вторым входом четвертого элемента И и первым входом второго элемента И-НЕ, выход которого соединен с третьим входом первого элемента ИЛИ, первый выход генератора импульсов соединен с объединенными вторыми входами пятого триггера, первого счетчика и блока элементов И, второй выход генератора импульсов соединен с первым входом восьмого элемента И, второй вход которого подключен к выходу третьего элемента ИЛИ, выход первого элемента И соединен с первым входом четвертого триггера, выход второго счетчика соединен с входом второго дешифратора, объединенные вторые входы первого, четвертого триггеров и объединенные второй вход второго, третий вход четвертого триггера являются соответственно первым и шестым входом блока управления, объединенные вторые входы второго элемента И-НЕ и пятого элемента И,

1713

второй вход шестого элемента И, второй вход третьего элемента И и первый вход первого элемента И-НЕ являются соответственно вторым, третьим, четвертым и пятым входами блока управления, второй выход первого триггера соединен с вторым входом первого элемента И-НЕ и является первым выходом блока управления, второй выход второго триггера является вторым выходом блока управления, выход второго элемента ИЛИ соединен с первым входом второго счетчика и является четвертым выходом блока управления, второй вы- ход третьего триггера соединен с вто

5

8995

с

18

рым входом седьмого элемента И и является третьим выходом блока управления, выход седьмого элемента И соединен с вторым входом второго счетчика и является пятым выходом блока управления, выход восьмого элемента И соединен с входом элемента задерж

выходом блока управления, выходы второго дешифратора соединены с соответствующими входами третьего элемента ИЛИ и являются третьей группой выходов блока управления, выходы блока элементов И являются второй группой выходов блока управления.

C4J

Авторы

Даты

1988-01-23—Публикация

1985-07-17—Подача