Изобретение относится к вычислительной технике и может бъггъ исп-оль- зовано при построении доменных магнитных запоминающих устройств.

Цель изобрете шя - уменьшение энергопотребления за счет подюпоче- ния только необходимых в текущий момент блоков паьити.

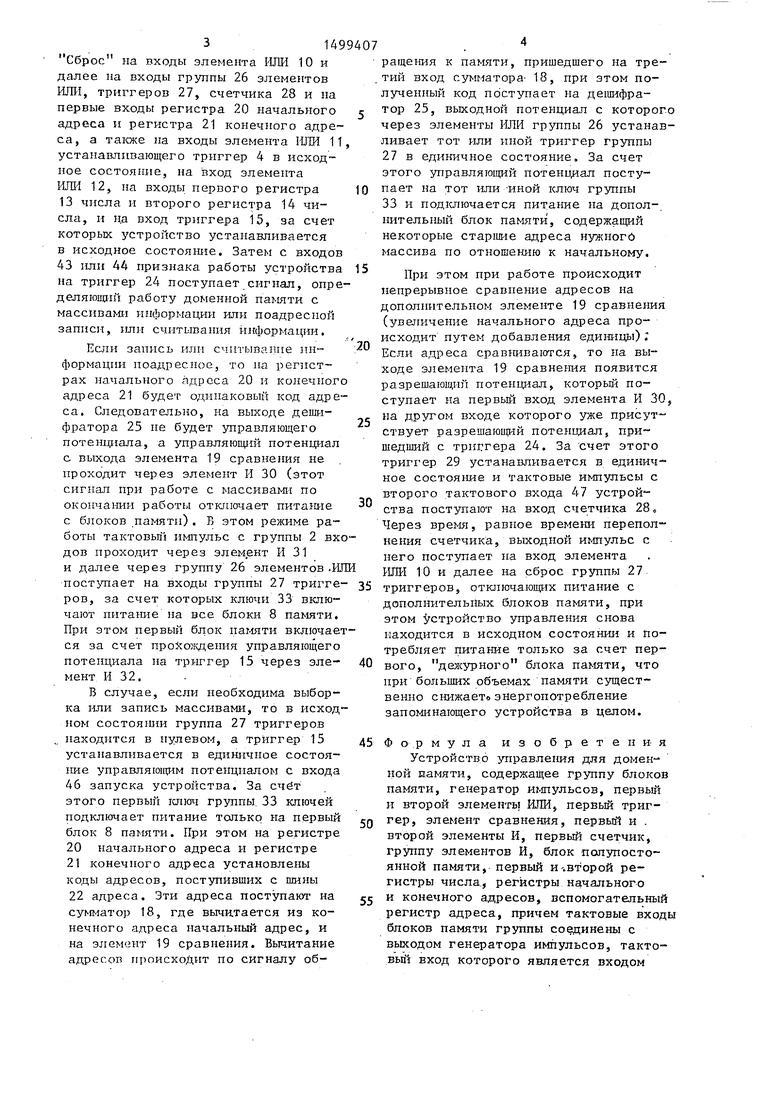

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - алгоритм функционирования устройства.

Устройство (фиг. 1) содержит генератор 1, г руппу 2 управляющих входов, первый элемент И 3, первьй триггер 4, второй элемент И 5, первьй элемент 6 сравнения, третий элемент ИЛИ 7, группу 8 блоков памяти, группу 9 элементов И, четвертый элемент ИЛИ 10, первьй 11 и второй 12 элементы ИЛИ, первый 13 и второй 14 регистры числа, третий триггер 15, вспомогательный регистр 16 адреса, первьй счетчик 17, сумматор 18, второй элемент 19

сравнения, регистры начального 20 и конечного 21 адресов, rpjmny 22 адресных входов устройства, блок 23 полупостоянной памяти, второй триггер 24, дешифратор 25, группу 26 элементов ИЛИ, группу 27 триггеров, второй счетчик 28, четвертьй триггер 29, третий 30, четвертый 31 и пятый 32 элементы И, группу 33 ключей, шестой элемент И 34, вход 35 числа устройства, входы синхроимпульса 36, считывания 37, сброса 38, управляклций 39, следукщего адреса 40, начала такта 41, записи 42, признака работы с массивом 43, признака поадресней работы 44, первый тактовый 45, запуска 46, второй тактов1ый 47, обращения 48, конечного адреса 49, начального адреса 50, адресньй 51. .

Устройство работает следующим образом.

Перед началом работы с входа 38 сброса устройства подается сигнал

(Л

:D

3149

Сброс на входы элемента ИЛИ 10 и далее на входы группы 26 элементов ИЛИ, триггеров 27, счетчика 28 и на первые входы регистра 20 начального адреса и регистра 21 конечного адреса, а тазсже на входы элемента ШШ 11 устанааливающего триггер 4 в исходное состояние, на вход элемента ИЛИ 12, на входы первого регистра

13 числа и второго регистра 14 числа, и н.а вход триггера 15, за счет которых устройство устанавливается в исходное состояние. Затем с входов 43 или 44 признака работы устройства на триггер 24 поступает сигнал, опре- деляюпцп работу доменной памяти с массивами информации или лоадреспой записи, или считывания информации.

Если запись или с штывание ин- формадии поадреснее, то на регистрах начального адреса 20 и ко}1ечного адреса 21 будет одинаковый код адреса. Следовательно, на выходе дешифратора 25 не будет управляющего потенциала, а управляющий потенциал с выхода элемента 19 сравнения не проходит через элемент И 30 (этот сигнал при работе с массивам по окончании работы отключает питашш с блоков памяти), В этом режиме работы тактовьп импульс с группы 2 входов проходит через элемент И 31 и далее через группу 26 элементов .l-ffl поступает на входы группы 27 тригге- ров, за счет которых ключи 33 включают питаете на все блоки 8 памяти. При этом первый блок наг-шти включается за счет проХолодения управляющего потенциала на триггер 15 через эле- мент И 32.

В случае, если необходима выборка или запись массивами, то в исход™ ном состояшш группа 27 триггеров находится в нулевом, а триггер 15

устанавливается в единичное состояние управляюищм потенциалом с входа 46 запуска устройства. За счёт этого первый ключ группы. 33 ключей подключает питание только на первый блок 8 памяти. При этом на регистре

20начального адреса и регистре

21конечного адреса установлены коды адресов, поступивших с шины

22адреса. Эти адреса поступают на сумматор 18, где вычнтается из конечного адреса начальный адрес, и

на элемент 19 сравнения. Вычитание адресов происходит по сигналу обращения к памяти, пришедшего на третий вход сумматора- 18, при этом полученный код поступает на тор 25, выходной потенциал с которог через элементы ИЛИ группы 26 устанавливает тот или иной триггер группы 27 в единичное состояние. За счет этого управляющий потенциал поступает на тот или -иной ключ группы 33 и под1а 1ючается питание на допол-. нительный блок памяти , содержащий некоторые старшие адреса нужногй массива по отношению к начальному,

При этом при работе происходит непрерывное сравнение адресов на дополнительном элементе 19 сравнения (уве гичение начального адреса происходит путем добавления единицы)Г Если адреса сравшгеаются, то на выходе элемента 19 сравнения появится разрешающий потенциал, который поступает на первый вход элемента И 30 на другом входе которого уже присутствует разрешающий потенциал, при™ шедший с триггера 24. За счет этого триггер 29 устанавливается в единичное состояние и тактовые импульсы с второго тактового входа 47 устрой ства поступают на вход счетчика 28, Через время, равное времени переполнения счетчика, выходной импульс с него поступает на вход элемента ИЛИ 10 и далее на сброс группы 27 триггеров, отключающих питание с дополнительных блоков памяти, при этом гстройство управления снова находится в исходном состоянии и Потребляет питание только за счет первого, дехсурного блока памяти, что при больших объемах памяти существенно снижает энергопотребление запоминающего устройства в целом.

Формула изобретения Устройство управления для доменной памяти, содержащее группу блоко памяти, генератор шлтульсов, первый и второй элементы ШШ, первый триггер, элемент сравнения, первый и . второй элементы И, первый счетчик, группу элементов И, блок полупостоянной памяти, первый и- второй регистры числа, регистры начального и конегшого адресов, вспомогательный регистр адреса, причем тактовые вход блоков памяти группы соединены с выходом генератора импульсов, такто- вьй вход которого является входом

cинxpoи myльca устройства, первьш вход первого элемента И является входом считывания устройства, второй вход первого элемента И соединен с выходом первого триггера и с первым входом второго элемента И, второй вход которого соединен с третьим входом первого элемента И и с выходом первого элемента сравнения, первый вход которого соединен с выходом регистра начального адреса, второй вход первого элемента сравнения соединен с выходом вспомогательного регистра адреса, вход сброса которого соединен с первыми входами первого и второго элементов ИЛИ, с входами., сброса первого и второго регистров числа и вспомогательного регистра адреса и с входом сброса устройства, информационные входы регистров конечного и начального адресов являются соответственно входами конечного и начального адресов устройства, ад- ресньй вход блока папупостоянной памяти является адресным входом устройства, управлякиций вход блока полу- постоянной памяти соединен с управ- ляюпщми входами блоков памяти группы и с управляющим входом устройства, вход следующего адреса устройства соединен с тактовым входом регистра начального адреса, вход начала такта устройства соединен с вторым входом первого элемента ИЛИ, выход которого соединен с входом сброса первого триггера, вход установки которого соединен с выходом блока полупостоянной памяти и со счетным входом первого счетчика, вход сброса которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с выходом переполнения первого счетчика и с входом записи вспомогательного регистра адреса, выход первого элемента И соединен с входом записи второго регистра числа, разряды информационного входа которого соединены с выходами соответствующих эле

99407

числа

10

15

20

информационный вход которого является входом числа устройства, отлича ющееся тем, что, с целью уменьшения энергопотребления за счет подключения только необходимых в текущий момент блоков памяти, в него введены третий и четвертый элементы ИЛИ, элементы И с третьего по шестой, второй элемент сравнения, триггеры с второго по четвертый, группа элементов ИЛИ, группа триггеров, группа зспючей, второй счетчик, дешифратор и сумматор, пер- вый вход которого соединен с выходом регистра начального адреса и с первым входом второго элемента сравне- 1шя, второй вход которого соединен с йыходом регистра конечного адреса и с-вторым входом сумматора, выход второго элемента сравнения соединен с первым входом третьего элемента И, второй вход которого соединен с прямым выходом второго триггера, входы сброса и установки которого являются соответственно входами признаков работы с массивом и поадрес- ной работы устройства, инверсный выход второго триггера соединен с первым входом четвертого элемента И, второй вход которого является первым тактовым входом устройства, выход четвертого элемента И соединен с первым входом пятого элемента И и с nepBbiMii входами элементов ИЛИ группы, второй вход пятого элемента И является входом запуска устройства, выход пятого элемента И соединён с входом установки третьего триггера, вход сброса которого соединен с входом сброса устройства, вторые входы элементов 1ШИ группы соединены с соответствукщиьш выходами дешифратора, вход которого сое- . динен с выходом сумматора, выход

третьего элемента И соединен с входом установки четвертого триггера, вход сброса которого соединен с входами сброса регистров начального и конеч25

30

35

40

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1363229A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Медианный фильтр | 1988 |

|

SU1562902A1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Устройство для определения текущей медианы | 1985 |

|

SU1322314A1 |

| Устройство для медианной фильтрации двумерных массивов | 1987 |

|

SU1524067A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ И ОЦЕНКИ ИХ ПЕРИОДА | 1990 |

|

RU2033617C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении магнитных доменных запоминающих устройств. Целью изобретения является уменьшение энергопотребления за счет подключения только необходимых в текущий момент блоков памяти. Устройство позволяет определять, в каких конкретно блоках памяти физически расположен массив, начальный и конечный адреса которого заданы, и подключать источник питания только к этим блокам. 2 ил.

ментов И группы, первые входы которых п ного адресов, второго счетчика, тригсоединены с третьим входом второго элемента И и с входом записи устройства, выход второго регистра числа соединен с четвертым входом второго элемента И, выход которого соединен с управляющим входом генератора импульсов, вторые входы элементов И группы соединены с соответствующими разрядами выхода первого регистра

55

геров группы и с выходом третьего элемента ИЛИ, первьй вход которого соединен с входом сброса устройства, второй вход третьего элемента ИЛИ соединен с выходом второго счетчика, счетньп вход которого соединен с выходом пятого элемента И, первый и второй входы которого соединены соответственно с выходом четвертого триг5

геров группы и с выходом третьего элемента ИЛИ, первьй вход которого соединен с входом сброса устройства, второй вход третьего элемента ИЛИ соединен с выходом второго счетчика, счетньп вход которого соединен с выходом пятого элемента И, первый и второй входы которого соединены соответственно с выходом четвертого триггера и с вторым тактовым входом устройства, выходы элементов ШШ группы соединены с входами установки соответствугшцих триггеров группы, выходы которых через клкпш группы с второго по К-й (К - число ключей в группе) соединены с входами обра- щеиия блоков памяти группы с второго по К-й, вход обращения первого -блока

.памяти группы соединен через первый КЛЮЧ группы с выходом третьего триггера, выходы блоков памяти группы соединены с соответствующими входа- ми четвертого эл.емента ИЛИ, выход которого соединен с четвертым входом первого элемента ИЛИ, третий вход сумматора является входом обращения устройства..

Г Начало j

Опр дмени pejffUMS с HaccugoH иаи fgi

/ Запись начального адреса, 7 / инеющеев if од ) . /

/Запись почечного адреса, / именя еей код т (Am) /

1 fafoma (, текущим аЗресонМ

увеличение tnsKyuieto адреса на 1. i-i-n

Включение питания на к-й. o/tOK памяти

&ка1 чение питания на п-и f/ioK памяти

noS pfCHt U fiafffn f I

ЧКонец

)

Фиг.2

| Запоминающее устройство | 1974 |

|

SU519761A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1053161A1 |

Авторы

Даты

1989-08-07—Публикация

1987-08-03—Подача