00 оь ел

О5

корреляционных кодов комбинационными сумматорами, а также за счет уменынения временных затрат внешнего устройства, работающего совместно с устройством, на программирование последнего. Коды слов вы борочной комбинации с выходов регистров 3 ноступают на адресные входы блоков памяти 4 и считывают на их выходы корреляционные числа, равные числу информационных позиций, на которых данное слово выборочной комбинации совпадает с соответствующим словом эталона. Решение об обнаружении комбинации принимается пороговым элементом 7, если сумма корреляционных чисел не меньше порога. В случае составной комбинации, образованной из частичных комбинаций, случайно выбираемых из алфавитов комбинаций известного вида, обнаружение осуш.ествляется путем считы- из блока памяти 4 результатов сравнения по методу максимального правдоподобия слов выборочной комбинации эталонам соответствующих алфавитов частичных комбинаций. Из внешнего устройства загружаются в блок 5 только эталоны и маски алфавитов частичных комбинаций, используя которые программатор 11 формирует таблицы корреляционных кодов и загружает их в блоки па.мяти 4. 1 з.п. ф-лы, ,5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1984 |

|

SU1156110A1 |

| Устройство для приема информации | 1983 |

|

SU1088051A1 |

| Выделитель составной комбинации двоичных сигналов | 1984 |

|

SU1223411A1 |

| Обнаружитель комбинации двоичных сигналов | 1985 |

|

SU1506463A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство классификации N-разрядных двоичных комбинаций | 1982 |

|

SU1089576A1 |

| Логическое запоминающее устройство | 1981 |

|

SU1014036A1 |

| Устройство приема двоичных сигналов | 1984 |

|

SU1197116A1 |

| Логическое запоминающее устройство | 1983 |

|

SU1140172A1 |

Изобретение относится к технике связи и может использоваться в устройства.х обработки дискретны.х сообщений для обнаружения составной комбинации при неиз- вестно.м моменте ее нрихода в потоке двоичных сигналов и образованной из частичных комбинаций, случайно выбираемых из алфавитов комбинаций известного вида. Цель изобретения - повышение быстродействия устройства. Устройство содержит ко.ммутаторы 1, 2, регистры сдвига 3.1...3.L , блоки памяти 4.1...4.L, 5. сумматор 6, пороговый элемент 7, регистр 8 D-триггеры 9, 10. программатор 11, счетчик 12, элемент НЕ 13, элемент И 14, входы 15, 16, выходы 17 - 22 програ.мматора 1 I, входы устройства: информационный 23, тактовые 24-28, управляющие 29, 30, входы данных 31, 32, выход 33 устройства. Программатор 11 содержит счетчик, группу элементов сравнения, группу элементов И, первый, второй, третий и четвертый элементы И, су.мматор 41, блок ера- .внения, регистры, D-триггеры, элементы З.Л- ПРЕТ, элементы И-НЕ, распределители. Сумматор 6 содержит сумматоры. Быстродействие устройства повышается за счет получения корреляционных кодов одновременно для всех слов выборочной комбинации с помощью табличных корреляторов, реализованных на основе блоков памяти, параллельно-последовательного суммирования «5 (Л

Изобретение относится к связи и может использоваться в устройствах обработки дискретных сообщений для обнаружения составной комбинации при неизвестпо.м .моменте ее прихода в потоке двоичных сигналов и образованной из частичных ко.мбинаций. случайно выбираемых из алфавитов комбинаций известного вида.

Це;1ью изобретения является повышение быстродействия устройства.

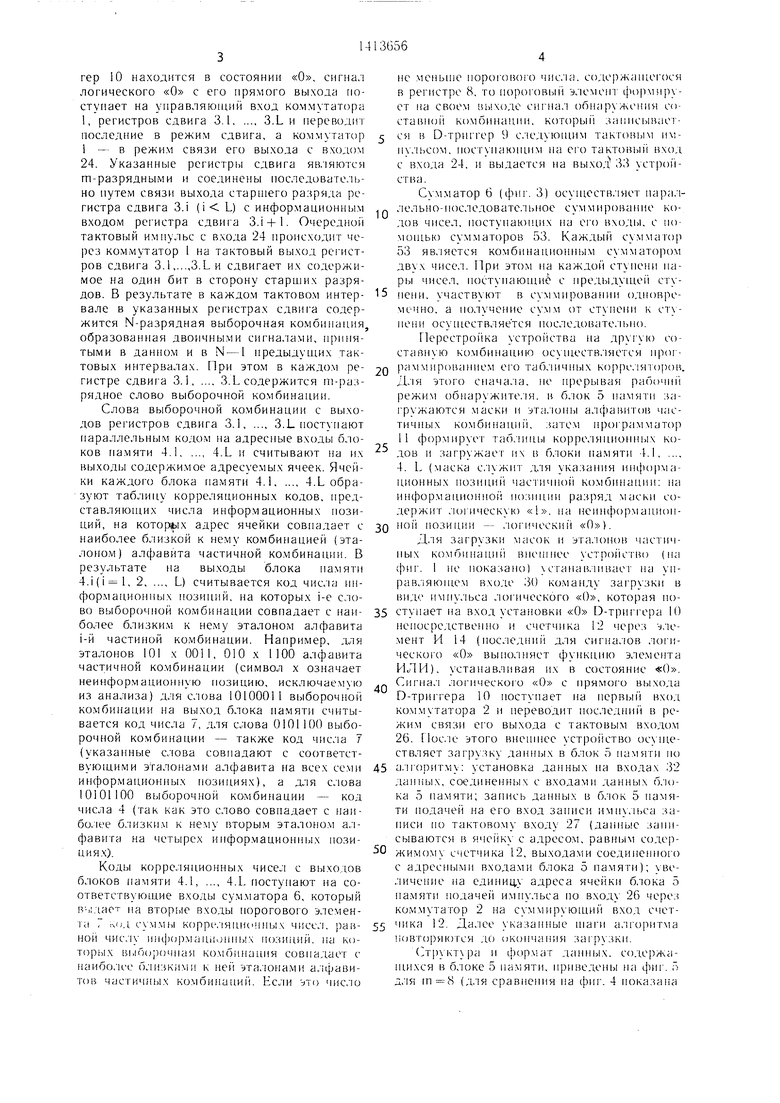

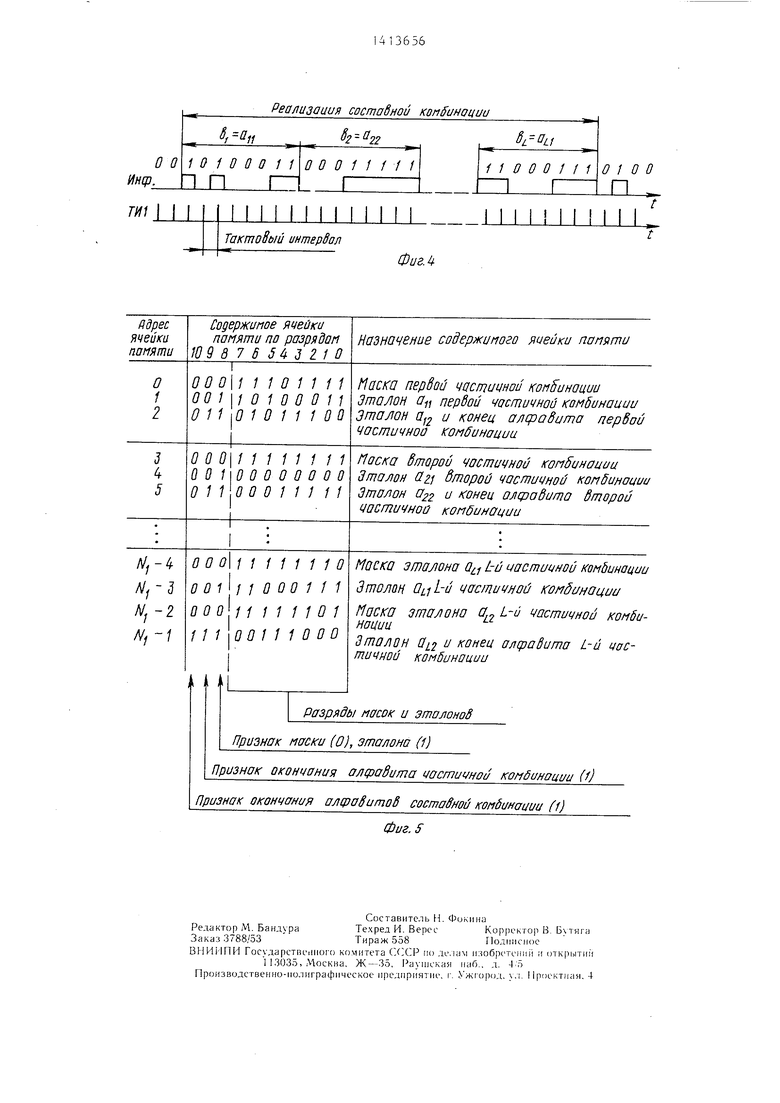

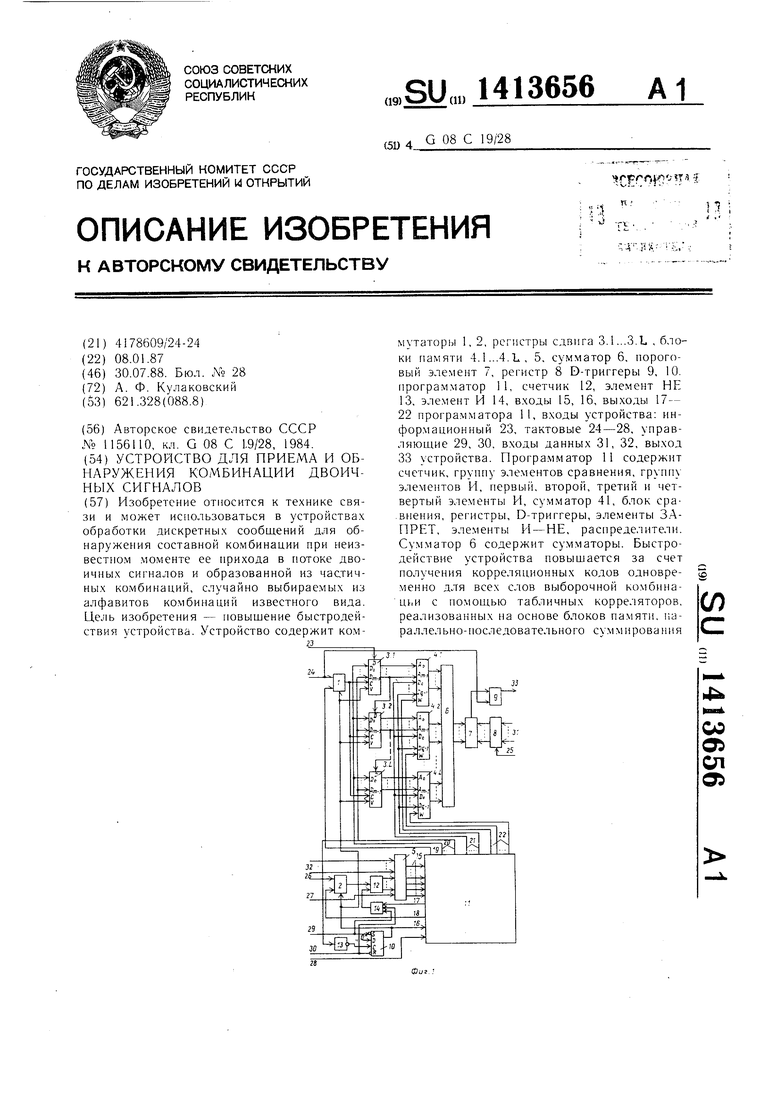

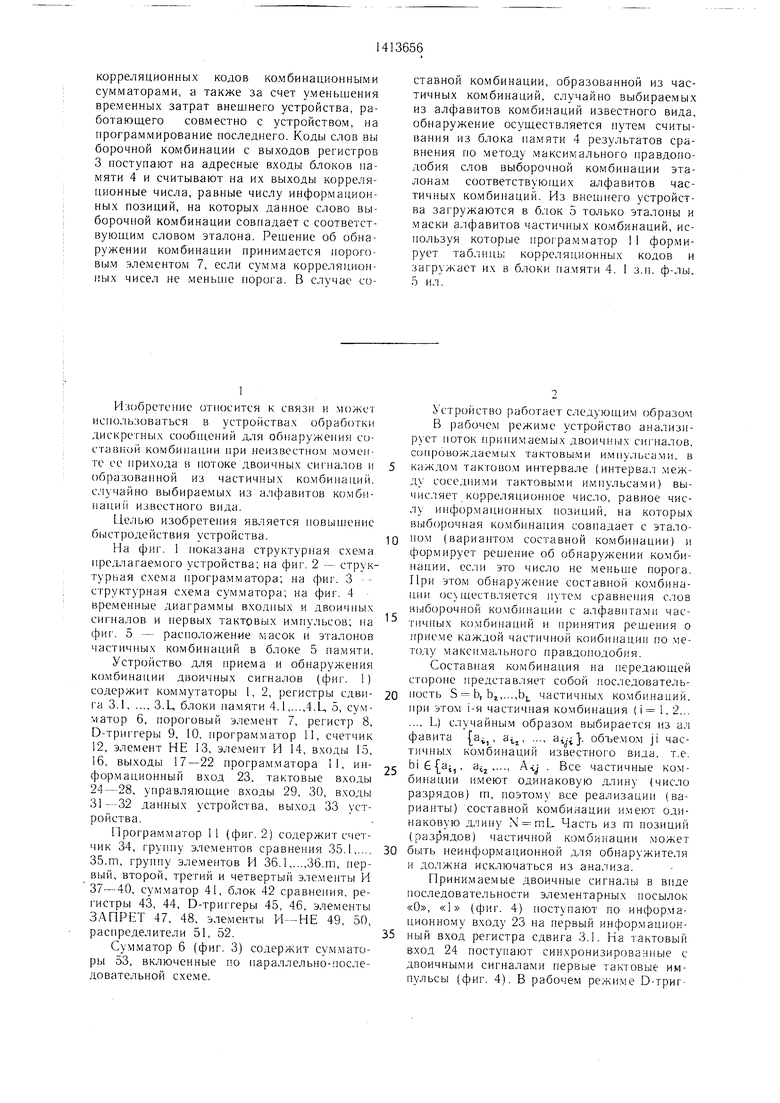

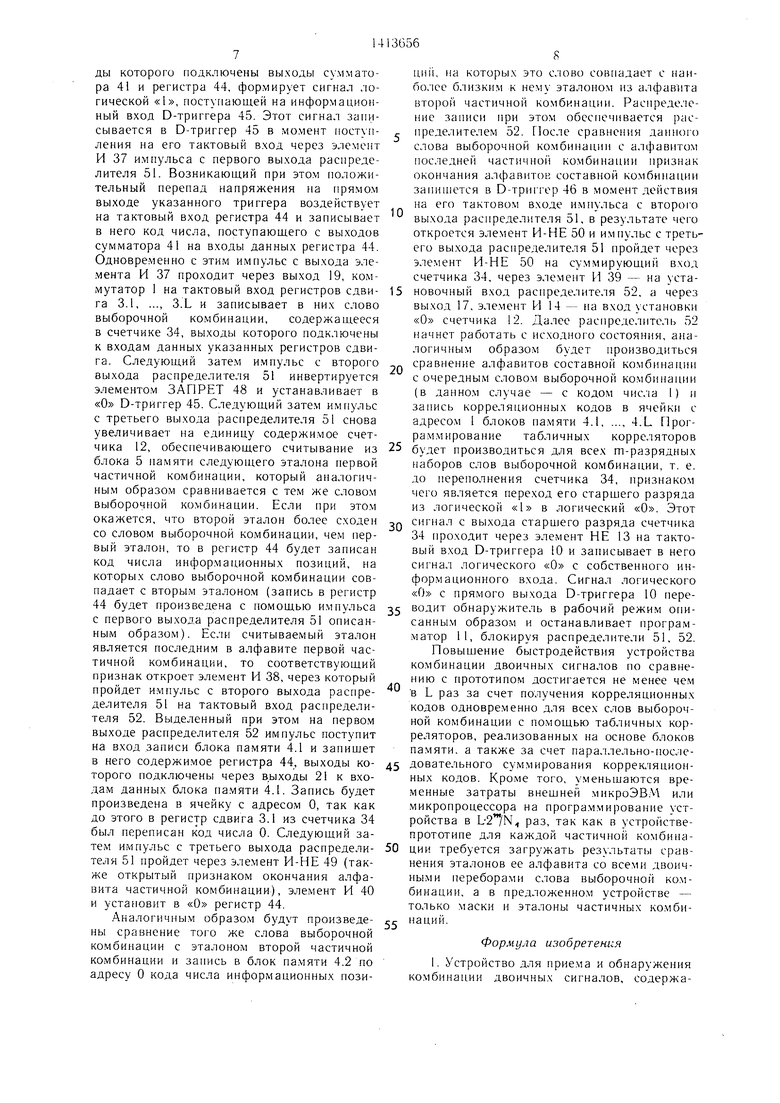

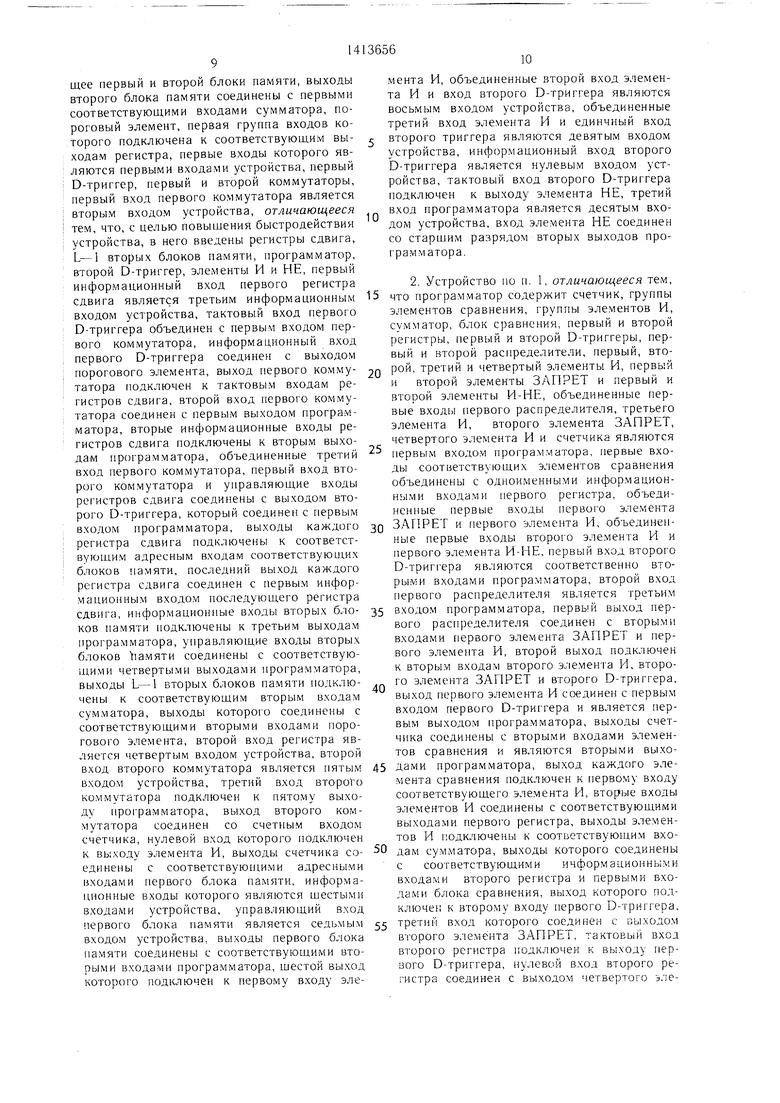

На фиг. 1 показана структурная схема нредлагаемого устройства; на фиг. 2 - структурная схема программатора; на фиг. 3 структурная схе.ма сум.матора; на фиг. 4 временные диаграммы входных и двоичных сигналов и первых тактовых импульсов; на фиг. 5 - расположение .lacoK и эталонов частичных комбинаций в блоке 5 памяти.

Устройство для приема и обнаружения комбинации двоичных сигналов (фиг. 1) содержит коммутаторы I, 2, регистры сдвига 3.1, ..., З.Ц блоки па.мяти 4.1,...,4.Ц 5, сумматор 6, пороговый элемент 7, регистр 8, D-триггеры 9, 10, программатор 11, счетчик 12, элемент НЕ 13, эле.меьгг И 14, входы 15, 16, выходы 17--22 программатора 11, информационный вход 23, тактовые входы 24 - 28, управляющие входы 29, 30, входы 31--32 данных устройства, выход 33 устройства.

Программатор I 1 (фиг. 2) содержит счетчик 34, элементов сравнения 35.1

Сумматор 6 (фиг. 3) содержит еуммато- ры 53, включенные по параллельно-последовательной схеме.

Устройство работает следующим образом В рабоче.м режиме устройство анализирует поток принимаемых двoич ыx сигналов, сопровождаемых тактовыми и.мпульса.ми, в

каждом тактово.м интервале (интервал .между соседни.ми тактовыми имнульса.ми) вычисляет корреляционное число, равное числу инфор.мацпонных позиций, на которых В1}|борочная комбинация совпадает с эта,точом (вариантом составной комбинации) и формирует решение об обнаружении комбинации, ес. ш это число не меньше порога. Нри этом обнаружение составной ко.мбинаций ос 1цеств.1яется путем сравнеш1я слов выборочной комбинации с алфавитами частичных ко.мбинаций и принятия рещения о приеме каждой частичной коибинацин по .методу макси.мального правдоподобия.

Составпая комбинация на передающей стороне представляет собой последовательность S Ь, bj,...,bj частичных ко.мбинаций, при этом i-я частичная комбинация (,2,.. ..., L) с. 1учайным образом выбирается из ал фавита {fli,, ii, . объемо.м ji частичных комбинаций известного вида, т.е.

iz --- частичные комбинации имеют одинаковую длину (число разрядов) гп, поэтому все реализации (варианты) составной комбинации имеют одинаковую длину N mL Часть из m позиций (разрядов) частичной комбинации .южет

быть неинформационной для обнаружителя и должна исключаться из анализа.

Принимаемые двоичные сигналы в виде последовательности элементарных посылок «О, «1 (фиг. 4) поступают по информационному входту 23 на первый информационный вход регистра сдвига 3.1. На тактовый вход 24 поступают синхронизированные с двоичными сигналами первые тактовые импульсы (фиг. 4). В рабочем режиме D-тригrep 10 находится в состоянии «О, сигнал логического «О с его прямого выхода поступает на управляющий вход коммутатора

1, регистров сдвига 3.1 3.L и переводит

последние в режим сдвига, а комм татор 1 в режим связи его выхода с входом 24. Указанные регистры сдвига яв.-1яются т-разрядными и соединены последовательно путем связи выхода старшего разряда регистра сдвига 3.1 (i L) с информационны.м входом регистра сдвига 3.1+1. Очередной тактовый импульс с в.хода 24 происходит через коммутатор 1 на тактовый выход решст- ров сдвига 3.1,...,З.Ьи сдвигает их содержимое на один бит в сторону старших разрядов. В результате в каждом тактовом интервале в указанных регистрах сдвига содержится N-разрядная выборочная комбинация, образованная двоичными сигналами, принятыми в данном и в N-1 предыдущих тактовых интервалах. При этом в каждом регистре сдвига 3.1 3.L содержится пьразрядное слово выборочной комбинапии.

Слова выборочной ко.мбинации с выходов pei-истров сдвига 3.1, ..., 3.L поступают параллельным кодом на адресные входы блоков памяти 4.1 4.L и считывают на их

выходы содержимое адресуемых ячеек. Ячейки каждого блока памяти 4.1 4.L образуют таблипу корреляционных кодов, представляющих числа информационных позиций, на KOTOpfcix адрес ячейки совпадает с наиболее б.чизкой к нему комбинацией (эталоном) алфавита частичной ко.мбинации. В результате на выходы блока памяти

Коды корреляционных чисел с выходов блоков памяти 4.1, ..., 4.L поступают на соответствующие входы су.м.матора 6, который выдает на вторые входы порогового элемен- Tii 7 :(i.i 1 уммы корре.-|япис 11п 1х чисе;|, равной числу ипформапи.Я1Н1)х псхзиций. па ко- . (рочпая KO.6unaLnm совпадает с иаибо, 11ч б. шзклми к nei i эта. юнами а,лфави- тов частичных комбинаций. Если это число

0

5

0

5

0

5

0

5

0

не меньше noporcMioi o чис. К), содержащегося в регистре 8, то пороговый элемсит формирует па своем выходе cnrna/i обнаружения со- ставпоГ комбинации, который за11пс1 1вает- ся в D-триггер 9 следующим тактовым им- п, 1ьсом, посгупаюшим на ) тактовьп вход с входа 24, и выдается на выход 33 устройства.

Сумматор 6 (фиг. 3) осуществляет параллельно-последовательное суммирование кодов чисел, ностунаюших на его входы, с по- мошыо сумматоров 53. Каждый сумматор 53 является комбинационным сумматором двух чисел. При этом на каждой ступени нары чисел, ностуиаюшие с предыдуше сту- iienn, участвуют в суммироваиии одновременно, а по,тучепие сумм от ступени к ступени осуществляется 11оследовател1)Н().

Перестро1 |ка устройства на другую со- ставпую комбипацию осуп1еств. 1яется прог- раммировапнем ei O таб, 1пчШ11х К())ре,1ят()р()в. Л:1Я эт1)го сначала, пе прерывая рабочий режим обнаружите. 1Я. в блок 5 памяти за- 1-ружаются маски и эта. юны ал(ра11итов частичных комбинаппй, затем программатор 11 формпруег таб. щцы корреляпноншпх кодов и загружаег их в блоки намяти 4.1

Для загрузки масок и эта. юнов частичных комбипаппй впешпее ycTpoiicTiio (на {|Mir. I не показано) vcranaii. uiBaer на управляющем входе 30 ко.манду загрузки в виде , 1ьса логического «О, которая поступает на вход установки «О О-трштера И) неносредственно и счетчика 12 через э. 1е- мент И 14 (носледний для сигна, 1ов , К)ги- ческо1Ч) «О выполняет функцию эле.мента ИЛП), устанавливая их в состояние «О. Сигна.м логического «О с прямого выхода D-триггера 10 иоступает на нерв1 1Й вход коммч татора 2 и переводит носледний в режим связи его выхода с тактовы.м входом 26. После этого внепп)ее устройство осуществляет загрузку данны.ч в блок 5 памятп по а. 1горитму: установка данных на входах 32 данных, соединенных с входами данных б. ю- ка 5 намяти; запись данных в б.чок 5 памяти подачей на его вход записи нмпчмьса записи по тактовому входу 27 (дапные записываются в ячейку с адресо.м, рав1Ц) с()дер- жимому счетчика 12, выходами соединенного с адресными входами блока 5 намяти); уве- .личепие на единиц.у адреса ячейки блока 5 памяти подаче и.пульса о входу 26 через коммутатор 2 па суммпруюший вход счетчика 12. Да.лее указанные а.л1Ч)ритма П()вторя огся до окончания загрузк.

(Лруктхра tj op . С().)жа- шихся в б,локе 5 иа.мят, нриведен1 1 па . Г д,ля (для сравнеп 1Я на . 4 1оказана

соответствующая фиг. 5 составная комбинация S а„ а,

aj в потоке принимаемых

двоичных сигналов). Данные располагаются в ячейках с адресами от О до N -1, где N - сумма чисел масок и эталонов всех алфавитов частичных комбинаций. Разряды О-7 (в общем случае от О до т- Г) являются разрядами масок и эталонов, разряд 8 (в общем случае т) содержит признак маски (в разряде логический «О) или эталона (в разряде логическая «1). Разряд 9 (в общем случае m-f 1) содержит признак продолжения (в разряде логический «О) и.чи окончания (в разряде логическая «1) алфавита частичной комбинации. Разряд 10 (в общем случае (т + 2) содержит признак продолжения или окончания алфавитов составной комбинации (в разряде соответственно логический «О или «1). Для каждой частичной комбинации первой следует маска, затем эталоны ее алфавита. Воз.можеп случай, когда отдельны.м эталонам может пред- П1ествовать своя .маска (см. на фиг. 5 содержимое для L-й частичной комбинации). Разряды маски, отвечающие инфор.мационным или неинформациопным позициям, содержат соответственно логическую «1 или логический «О. Число входов (выходов) блока 5 памяти равно т+3, число S его адресных входов равно числу разрядов двоичного кода числа N,.

Для программирования табличных корре .1яторов внешнее устройство устанавливает на управляющем входе 29 команду пуска в виде импульса логического «О, которая поступает па вход установки «1 D-триггера И) непосредственно, устанавливая его в состояние «1, и на вход установки «О счетчика 12 через элемент И 14, устанавливая счетчик 12 в состояние «О. Сигнал логической «1 с пря.мого выхода D-триггера 10 нск тунает на управляющий вход ко.ммутато- ров 1, 2, регистров 3.1, ..., З.Ц в результате чего последние переводятся в режим парал- ;1ельной записи, коммутатор Г нереводится в режим связи его выхода с выходо.м 19 програ.мматора 11, коммутатор 2 - в режим связи ею выхода с выходо.м 18 програм.ма- тора 11. Сигнал логической «1 с прямого выхода D-триггера 10 поступает по входу 6 в программатор 11 и запускает распределитель 51 по его установочному входу, разрешает работу счетчика 34 по его входу уста- новкп «О, проходит через элемент И 39 и запускает раснреде.читель 52 по его установочному входу, открывает элементы И 40, ЗАПРЕТ 48. При этом па выходе элементов И 40, ЗАПРЕТ 48 устанавливается логической «1, разрешающий но входу установки «О работу регистра 44, D-тpиl гe- ра 45 (носледпие и счетчик 34 были установ- ,лепы в состояние «О, когда D-триггер 10 находился в состонпии «О).

0

5

0

5

0

5

0

5

0

5

Запущенный распределитель 51 формирует из тактовых импульсов, поступающих на его тактовый вход по тактовому входу 28, три последовательности распределенных во времени и пространстве импульсов, при этом первыми, вторыми и третьи.ми следуют импульсы соответственно на нервом, втором и третьем выходе распределителя 51. Импульсы с третьего выхода распределителя 51 проходят на выход 18 программатора и через коммутатор 2 - на су.ммирующий вход счетчика 12, обеспечивая Тем самым последовательное считывание ячеек блока 5 памяти на входы 15 програ.мматора И, задействованные следующим образо.м: разряды от О до m-1 подключены к соответствующим входам данных регистра 43 и первым входам эле.ментов сравнения 35.1, ..., 35.m группы, вторые входы которых соединены с соответствующими выходами счетчика 34; гп-й разряд подключен к инверсному входу эле.мента ЗАПРЕТ 47 для выделения признака маски и входу э;1е.мента И 37 для выделения признака эталона; (т + 1)-й разряд подключен к входу элементов И 38, И-НЕ 49 для выделения признака окончания алфавита частичной ко.мбинации; (гп-f2)-й разряд подключен к информационному входу D-триггера 46 для выделения признака окончания алфавитов составной комбинации.

Процессы программирования протекают следующим образом.

ГТервой из ячейки с адресом О блока 5 памяти считывается маска (с.м. фиг. 5), признак которой открывает элемент ЗАПРЕТ 47. Маска записывается в регистр 43 и.мпульсом, поступающи.м на его тактовый вход с первого выхода раснределителя 5J через элемент ЗАПРЕТ 47. Импульс с третьего выхода раснределителя 51 увеличивает на единицу содержимое счетчика 12, обеспечивающего считывание из блока 5 на.мяти нервого эталона нервой частичной комбинации, который сравнивается в поразрядных элементах сравнения 35.1, .... 35.m группы с содержимым счетчика 34 (в данном случае-с число.м 0). имитирующи.м слово выборочной комбинации. На выходе каждого из указанных элементов сравнения формируется логическая «1 при совпадении или логический «О при несовпадении содержимого сравнивае.мых разрядов слова выборочной комбинации и эталона частичной комбинации. Результаты сравнения постунают на первые входы

поразрядных элементов И группы 36.1

Аналогичным образо.м будут произведены сравнение того же слова выборочной ко.мбинации с эталоном второй частичной комбинации и запись в блок памяти 4.2 по адресу О кода числа информационных пози:

20

55

luiii, па которых это слово совпадает с наиболее близким к нему эталоном из алфавита второй частичной комбинации. Раснределе- ние записи при этом обеспечивается распределителем 52. После сравнения данного слова выборочной комбинации с алфавитом юследней частичной комбинации признак окончания алфавитов составной комбинации запишется в D-триггер 46 в момент действия па его тактовом входе импульса с второго

выхода распределителя 51, в результате чего откроется элемент И-НЕ 50 и импульс с треть- его вы.чода распределителя 51 пройдет через элемент И-НЕ 50 на суммирующий вход счетчика 34, через элемент И 39 - на уста15 новочный вход распределителя 52, а через выход 17, эле.мент И 14 - на вход установки «О счетчика 12. Далее распреде,тптель 52 начнет работать с исходного состояния, аналогичным образом будет производиться сравнение алфавитов составной комбинации с очередным словом выборочной комбинации (в данном случае - с кодом числа I) и запись корреляционных кодов в ячейки с адресом 1 блоков памяти 4.1, ..., 4.L Прог- рам.мирование табличных корреляторов

25 будет производиться для всех гп-разрядных наборов слов выборочной комбинации, т. е. до переполнения счетчика 34, признаком чего является переход его старщего разряда из логической «1 в логический «О. Этот

OQ сигнал с выхода старщего разряда счетчика 34 проходит через элемент НЕ 13 на тактовый вход D-триггера 10 и записывает в него сигнал логического «О с собственного информационного входа. Сигнал логического «О с прямого выхода D-триггера 10 пере35 водит обнаружитель в рабочий режим описанным образом и останавливает программатор 11, блокируя распределители 51, 52. Повыщение быстродействия устройства комбинации двоичных сигналов по сравнению с прототипом достигается не менее чем в L раз за счет получения корреляционных кодов одновре.менно для всех слов выборочной комбинации с помощью табличных корреляторов, реализованных на основе блоков памяти, а также за счет параллельно-после45 довательного суммирования коррек чяцион- ных кодов. Кро.ме того, уменьшаются вре- .менные затраты внешней микроЭВЛА или микропроцессора на программирование устройства в L-2 7N;, раз, так как в устройстве- прототипе для каждой частичной комбина50 ции требуется загружать результаты сравнения эталонов ее алфавита со всеми двоичными перебора.ми слова выборочной комбинации, а в предложенном устройстве - только маски и эталоны частичных ко.мбинации.

40

Формула изобретения

I. Устройство для прие.ма и обнаружения комбинации двоичных сигналов, содержа дее первый и второй блоки памяти, выходы второго блока памяти соединены с первыми соответствующими входами сумматора, пороговый элемент, первая группа входов которого подключена к соответствующим выходам регистра, первые входы которого являются первыми входами устройства, первый D-триггер, первый и второй коммутаторы, первый вход первого коммутатора является вторым входом устройства, отличающееся тем, что, с целью повыщения быстродействия устройства, в него введены регистры сдвига, L-1 вторых блоков памяти, программатор, второй D-триггер, элементы И и НЕ, первый информационный вход первого регистра сдвига является третьим информационным входом устройства, тактовый вход первого D-триггера объединен с первым входом первого коммутатора, информационный вход первого D-триггера соединен с выходом порогового элемента, выход первого коммутатора подключен к тактовым входам регистров сдвига, второй вход первого коммутатора соединен с первым выходом программатора, вторые информационные входы регистров сдвига подключены к вторым выходам программатора, объединенные третий вход первого коммутатора, первый вход второго коммутатора и управляющие входы регистров сдвига соединены с выходом второго D-триггера, который соединен с первым входом программатора, выходы каждого регистра сдвига подключены к соответствующим адресным входам соответствующих блоков памяти, последний выход каждого регистра сдвига соединен с первым информационным входом последующего регистра сдвига, информационные входы вторых блоков памяти нодключены к третьим выходам программатора, управляющие входы вторых блоков памяти соединены с соответствующими четвертыми выходами программатора, выходы L-1 вторых блоков памяти подключены к соответствующим вторым входам сумматора, выходы которого соединены с соответствующими вторыми входами порогового элемента, второй вход регистра является четвертым входом устройства, второй вход второго коммутатора является пятым входом устройства, третий вход второго коммутатора подключен к пятому выходу программатора, выход второго коммутатора соединен со счетным входом счетчика, нулевой вход которого подключен к выходу элемента И, выходы счетчика соединены с соответствующими адресными входами первого блока памяти, информационные входы которого являются щестыми входами устройства, управляющий вход первого блока памяти является седьмым входом устройства, выходы первого блока памяти соединены с соответствующими вторыми входами программатора, щестой выход которого подключен к первому входу эле0

5

0

5

0

5

0

5

0

5

мента И, объединенные второй вход элемента И и вход второго D-триггера являются восьмым входом устройства, объединенные третий вход элемента И и единчный вход второго триггера являются девятым входом устройства, информационный вход второго D-триггера является нулевым входом устройства, тактовый вход второго D-триггера подключен к выходу элемента НЕ, третий вход программатора является десятым входом устройства, вход элемента НЕ соединен со старщим разрядом вторых выходов программатора.

единен с вторыми входами третьего элемента И и счетчика и является 1иестым выходом программатора, выходы второго и третьего э.тементов И соединены соответственно с первым и вторым входами второго распределителя, выход первого элемента ЗАПРЕТ подключен к тактовому входу первого регистра, выходы первого элемента И-НЕ и второго триггера соединены соответственно с вторыми входами четвертого элемента И и второго элемента И-НЕ.

Фиг.З

w/ I 1 I И I И I I I I I I I I I I

ТактоВыи интервал

Содержимое ячейки памяти по разрядап Ю9 В 7 6 5 3 21 О

1

00 1 1 О 1 1 1 1 00 } о 1 о о о П 011 о 1 о 1 1 1 OQ

О О 1 1 1 1 П

О О 1 О / 1

00000000 О О О J П 11

4 J 2 1

О О 1 1 1 1 1 1 О О О 1 П О О О f / 1 00 1 П 1 1 О 1 Ц 11 1 О О О

Разряды масок и этолонод

Признак наски (О), эталона (1)

Признак окончания алфобита частичной KOfidaHouuu (f)

Признак окончаний алсраёитоВ состабной комбинации (1)

Назначвние содержипого я Jeйкu папяти

Маска первой чцстицнои коп5инаиии Зтомн QI пердой чacmu Jнoй комбинации Зтолон конец алдзобита пербои частичноо к омбинации

Паска дторой acmuijHou коп5инат/и Эталон И. Второй частичной капВиноииа 3/полон О22 и коней ojJifiadumo дторой (частичной копбиноции

Носко эталона Ьй Jacmuчнoй комЬинации Зтолон ULiL-ij частичной комбинаиии

Паска эталона а, L-й частичной комбинации

Эталон /12 и конец алсраВита L-u частичной комбинации

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1984 |

|

SU1156110A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-07-30—Публикация

1987-01-08—Подача