первого блока сравнения и второму входу первого регистра, выход которого подключен к второму входу первого блока сравнения, выход которого подключен к второму входу блока управления, выход блока памяти подключен к первому входу второго регистра, второй вход которого подключен к тринадцатому выходу блока управления, выход второго регистра подключен к первому входу второго блока сравнения и первому входу четвертого блока элементов И, выход второго блока сравнения подключен к третьему входу блока управления, второй вход второго блока сравнения подключен к выходу третьего ре1:истра и первому входу пятого блока элементов И, второй- вход которого подключен к четырнадцатому выходу блока управления, выход пятого блока элементов И подключен к второму входу блока элементов ИЛИ, второй вход четвертого блока элементов И подключен к пятнадцатому выходу блока управления, выход четвертого блока элементов И подключен к второму входу узла формирования вектора, третий вход которого подключен к шестнадцатому выходу блока управления и второму входу счетчика, четвертый и пятый входы узла формирования вектора подключены соответственно к семнадцатому и восемнадцатому выходам блока управления, выходы узла формирования вектора подключены к вторым входам блока вычитания и первым входам четвертого регистра, второй вход которого подключен к девятнадцатому выходу блока управления, выход четвертого регистра подключен к первому входу шестого блока элементов И, второй вход которого подключен к двадцатому выходу блока управления, четвертый и пятый входы которого являются соответственно первым и вторым управляющими входами устройства, выход шестого блока элементов И яв Ляется информационным выходом устроства.2. Устройство по п. 1, о т л ич а ю щ е ее я тем, что блок упраления содержит распредел1 тели импусов, регистры, генератор импульсрв триггеры, элемент задержки, счетчи элементы ИЛИ и элементы И, выход генератора импульсов подключен к пвым входам первого - шестого элемен- тов И, выходы первого - четвертого элементов И подключены к входам соответствующих распределителей импульсов, первые выхбды первого и второго распределителей импульсов подключены к первым входам соответственно седьмого и восьмого элементов И, выходы которых подключены к первому и второму входам первого элемента ИЛИ, выход первого элемента ИЛИ подключен к входу первого регистра, выходы которого подключены к вторым входам соответственно четвертого - первого элементов И, первый выход четвертого распределителя импульсов подключен к первому входу второго элемента ИЛИ, второй выход четвертого распределителя импульсов подключен к первому входу счетчика, третий выход четвертого распределителя импульсов подключен к первому входу третьего элемента ИЛИ и первому входу четвертого элемента ШШ, вькод которого подключен к первому входу первого триггера, второй вход которого подключен к выходу пятого элемента ИЛИ, второй выход первого распределителя импульсов и первый выход третьего распределителя импульсов подключены соответственно к третьему и четвертому входам первого элемента ИЛИ, третий выход первого и второй выход третьего распределителей импульсов подключены соответственно к второму и третьему входам второго элемента ИЛИ, четвертый вход которого подключен к четвертому выходу первого распределителя импульсов, пятый выход первого распределителя импульсов и третий вькод третьего распределителя импульсов подключены соответственно к первому и второму входам пятого элемента ИЛИ и к второму и третьему входам третьего элемента ИЛИ, выход которого подключен к первому входу шестого элемента ИЛИ и входу элемента вадержки,шестой выход первого распределителя импульсов подключен к четвертому входу третьего элемента ИЛИ и второму входу четвертого элемента ИЛИ, седьмой выход первого и четвертый выход третьего распределителей импульсов подключены соответственно к первому и второму входам седьмого элемента ИЛИ, второй выход второго распределителя импульсов подключен к третьему входу седьмого элемента ИЛИ и вто рому входу счетчика, выход которого подключен к третьему входу первого элемента ИЛИ, восьмой выход первого распределителя импульсов подключен к первому входу восьмого элемента ИЛИ, выход которого подключен к первому входу второго триггера, .второй вход которого подключен к пя тому выходу третьего распределителя импульсов, девятый выход первого распределителя импульсов и тре тий выход второго распределителя подключены соответственно к первому и второму входам девятого элемента ИЛИ, десятый выход первого распределителя импульсов подключен к первому входу десятого элемента ИЛИ и первым входам второго .и третьего ре гистров, вторые входы которых подключены к четвертому выходу второго распределителя импульсов, второй вход десятого элемента ИЛИ подключен к первому входу пятого распреде лителя импульсов,.второй выход кото рого подключен к второму входу вось мого элемента ИЛИ, третий выход кот рого подключен к первьм входам третьего и четвертого триггеров, выход третьего триггера подключен к второму входу пятого элемента И, выход которого подключен к входу пяфого распределителя импульсов, вькод четвертого триггера подключён к /второму входу шестого элемента И, выход которого подключен к входу шестого распределителя импульсов, первый и второй выходы которого под ключены к второму и четвертому входам соответственно шестого и седьмого элементов ИЛИ, третий выход шестого распределителя импульсов подключен к первьш входам пя.ого и шестого триггеров, выход пятого триггера подключен к первому входу девятого элемента И, второй вход которого подключен к четвертому вых ду шестого распределителя импульсов, объединенные вторые входы седьмого и восьмого элементов И, второй вход четвертого триггера, вторые входы пятого и шестого тригг ров, шестой вход первого элемента И и второй вход третьего триггера явл ются соответственно перовым - пятым входами блока управления, выход эле мента задержки, выход второго эле95мента ИЛИ, одиннадцатый выход первого распределителя импульсов, выход девятого элемента ИЛИ, выход третьего регистра, выход второго регистра, пятый выход второго распределителя импульсов, второй выход четвертого распределителя импульсов, шестой выход второго распределителя импульсов, первьй выход первого триггера, пятый выход шестого распределителя импульсов, выход деся-, того элемента ИЛИ, шестой выход шестого распределителя импульсов, второй выход первого триггера, выход шестого триггера, выход шестого элемента ИЛИ, выход седьмого элемента ИЛИ, выходы второго триггера, седьмой выход шестого распределителя импульсов и выход девятого элемента И являются соответственно первым двадцатым выходами блока управления. 3. Устройство по п. 1, отличающаяся тем, что узел формирования вектора содержит блоки элементов И, блок элементов ИЛИ, блок регистров, блоки сумматоров, элементы И и элемент И1Ш, выход первого блока элементов И подключен к первому входу блока элементов ИЛИ, выходы которого подключены к соответствующим первым входам блока регистров, выход первого элемента И подключен к первому входу элемента ИЛИ, выход которого подключен к вто рому входу блока регистров, первый выход блока регистров подключен к первому входу второго блока элементов И и первому входу первого блока сумматоров, выход каждого блока сумматоров подключен к первому входу последующего блока сумматоров, группа 16ЫХОДОВ блока регистров подключена к вторым входам соответствуницих блоков сумматоров, кроме последнего, группа выходов блока регистров, кроме последнего выхода группы, подключена к вторым входам второго блока элементов И, выход которого подключен к второму входу блока элементов ИЛИ, выход последнего блока сумматоров подключен к первому входу второго элемента И, выход которого подключен к второму входу элемента ИЛИ, первый вход первого блока элементов И и первый вход первого элемента И, второй вход последнего блока сумматора, третий и четвертые входы блока регистров и вторые объединенные входы первого элемента И и первого блока элементов И и объединенные второй вход второго элемента И и третий вход второго блока элементов И являются соответственно первым, вторым, третьим, четвертым и пятым входами узла формирования вектора, первый и группа выходов блока регистров являются выходами узла формирования вектора.

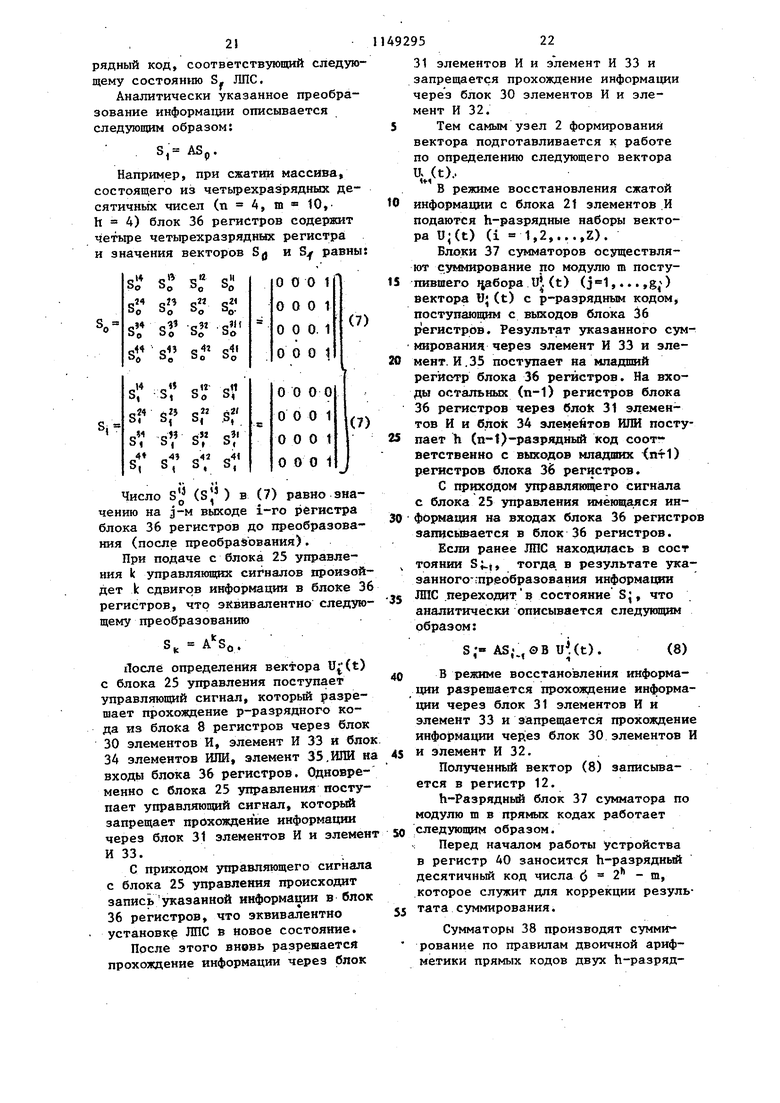

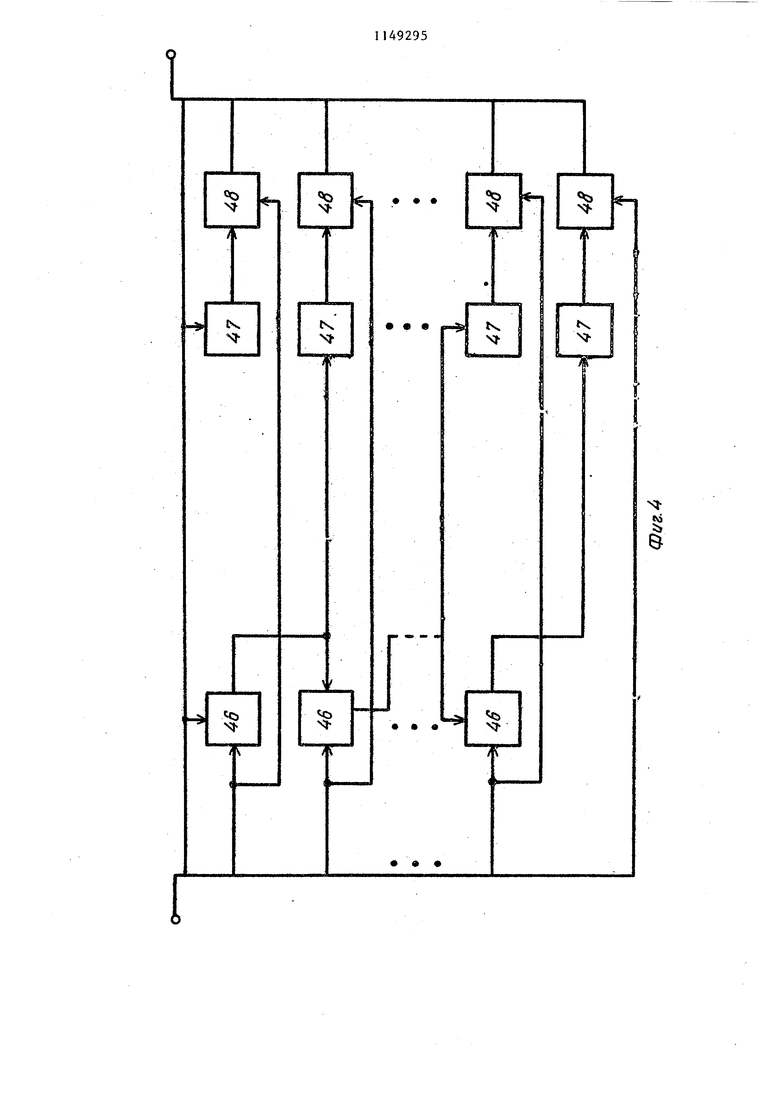

4. Устройство по п. 1, о т л ич а ю щ е е с я тем, что узел формирования входной последовательности содержит группу формирователе обратного кода и группы блоков сумматоров, выход каждого, кроме посленего блока сумматора первой группы, подключен к первому входу последующего блока сумматора первой группы и входу соответствующего формирователя обратного кода группы, выход последнего блока сумматоров первой группы подключен к входу последнего

формирователя (.)братного кода группы, первый вход первого блока сумматоров первой группы объединен с входом первого формирователя обратного кода группы, выход каждого формирователя обратного кода группы подключен к первому входу соответствующего блока сумматоров второй группы, вторые входы блоков сумматоров второй группы кроме последнего, объединены с вторыми входами соответствующих блоков сумматоров первой группы, первый вход первого блока сумматора первой группы, вторые входы каждого 6jioKa сумматора первой группы и второй вход последнего блока сумматора второй группы являются входами узла формирования входной последовательности, вход первого формирователя обратного кода группы и выход каждого блока сумматора второй группы являются выходами узла формирования входной последовательно ти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1141407A1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

| Устройство для решения системы линейных алгебраических уравнений | 1986 |

|

SU1405073A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Устройство для обработки приращений вектора | 1984 |

|

SU1203510A1 |

| Устройство для моделирования случайных блужданий | 1981 |

|

SU999063A1 |

| Устройство для ввода информации | 1983 |

|

SU1092486A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ РАДИОЛОКАЦИОННОГО ИЗОБРАЖЕНИЯ МЕСТНОСТИ | 1988 |

|

SU1841035A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

1. УСТРОЙСТВО ДЛЯ СЖАТИЯ И,ВОССТАНОВЛЕНИЯ ИНФОРМАЦИИ, содержащее блок управления, первый выход которого подключен к первому входу первого регистра, второй выход блока управления подключен к первому входу блока памяти, второй и третий регистры, первый блок сравнения, блок элементов ИЛИ, отличающееся тем, что, с целью повышения пропускной способности устройства, в него введены блоки регистров, четвертый регистр, блок вычитания, блоки элементов И, блок элементов НЕ, второй блок сравнения, узел формирования вектора, узел формирования входной последовательности, дешифратор, первбй вход первого блока регистров является информационным входом устройства, второй вход которого подключен к третьему выходу блока управления, выходы первого блока регистров подключены к первым нходпм учла формирования вектора и к первьм входам блока вычитания, выход которого подключен к первому входу второго блока регистров, второй вход которого .подключен к четвертому выходу блока управления, выход второго блока регистров подключен к первому входу первого блока, элементов И и через блок элементов Н& к первому входу второго блока элементов И, второй вход которого подключен к пятому выходу блока управления, выход второго блока элементов И подключен через дешифратор к первому входу блока управления, шестой выход которого подключен к второму входу первого блока элементов И, выход которого подключен к первому (Л входу третьего блока регистров, второй вход которого подключен к седьмому выходу блока управления, выходы третьего блока регистров подключены через узел формирования входной последовательности к входу четвертого блока регистров, первый и второй вхо4 СО Ю QD ды которого подключены соответственно к восьмому и девятому выходам блока управления, выход четвертого блока регистров подключен к первому % входу третьего блока элементов И, сл второй вход которого подключен к десятому выходу блока управления, выход третьего блока элементов И подключен к первому входу блока элементов ИЛИ, выход которого подключен к второму входу блока памяти, третий вход которого подключен к одиннадцатому выходу блока управления, двенадцатый выход которого подключен к первому входу счетчика, выход счетчика подключен к четвертому входу блока памяти, первому входу

1

Изобретение относится к вычислительной технике и может быть применено как преобразователь массивов информации в ЭВМ, в автоматизированных системах контроля логических блоков, а также в сист-емах передачи данных.

Известно устройство для сжатия информации, которое содержит два регистра сдвига, схему равнозначности, счетчик, генератор тактовых импульсов, распределитель тактовых импульсов, задатчик начального состояния регистров, индикаторный триггер, вентили, схе№ ИЛИ и инвертор И .

Недостаток этого устройства состоит в невозможности восстановления сжатой информации.

Наиболее близким к предлагаемому является устройство для сжатия и восстановления информации, содержащее блок памяти устройства, первьт выход которого соединен с первым выходом устройства, блок сравнения информационных комбинаций, регистр

комбинаций, регистр памяти постоянных информационных комбинаций, регистр памяти единиц, блок управления, блок элементов ИЛИ, формирователь

пакетов первичной информации, формирователь информационных комбинаций регистр памяти адреса и признака информационных комбинаций, преобразователь пакетов неупорядоченной

информации в коды и блок выдачи информации, первый вход формирователя пакетов первичной информации подключен к первому входу устройства, первый, второй, третий, четвертый и пятый выходы формирователя пакетов первичной информации соединены соответственно с первым входом преобразователя пакетов неупорядоченной информации в коды, первым

входом блока памяти информации, первым входом блока сравнения информационных комбинаций, первым входом регистра адреса информационных комбинаций и первым входом блока

управления, первый, второй, третий, четвертый и пятый выходы блока управления соединены соответственно

с вторым входом формирователя пакетов первичной информации, объединенными вторым и третьим входами регистра памяти адреса и признака информационньк комбинаций, вторым входом преобразователя пакетов неупорядоченной информации в коды, вторым входом блока памяти информации и объединенными первыми входами регистра памяти постоянных информационных комбинаций и регистра памяти едниц, вторые входы которых соединены с вторым и третьим входами устройства, выходы которых соединены с соответствующими входами формирователя информационных комбинаций, выход которого соединен с первым входом блока вьщачи информации и вторым входом блока сравнения информационных комбинаций, выход .блока сра нения информационных комбинаций соединен с четвертым входом регистра памяти адреса и признака информационных комбинаций и через блок элемента ИЩ с объединенными вторым входом блока управления и пятьм входом регистра памяти адреса и принака информационньк комбинаций, выход которого соединен с третьими входами формирователя пакетов первичной информации и блока памяти информации, второй, третий и четвертый выходы блока памяти информации соединены соответственно с объединенными третьим входом блока управления и четвертым входом форМ141рователя пакетов первичной информации, вторым входом блока вьщачи информации и третьим входом преобразователя пакетов неупорядоченной информации в коды, цервый и второй выходы которого соединены с четвертым входом блока памяти информации и третьим входом блок выдачи информации, первый , второй и третий выходы которого соединены соответственно с пятым входом формирователя пакетов первичной информации, пятым входом блока памяти информации и вторым выходом устройства

Недостатком этого устройства является ограниченная область применения, поскольку сжимаются только повторяющиеся, возрастающие и убывающие пакеты информации, а также низкий коэффициент сжатия инфор1 ации из-за наличия несжатых пакетов информации.

Целью изобретения является повышение пропускной способности устройства.

Поставленная цель достигается тем, что в устройство, содержащее блок управления, первый выход которого подключен к первому входу первого регистра, второй выход блока управления подключен к первому входу блока памяти, второй и третий регистры, первый блок сравнения, блок - элементов ИЛИ, введены, блоки регистров, четвертый регистр, блок вычитания, блоки элементов И, блок элементов НЕ, второй блок сравнения, узел формирования вектора, узел фор-, |мирования входной последовательности, дешифратор, первый вход первого блока регистров является информационным входом устройства, второй вход которого подключен к третьему выходу блока управления, выходы первого блока регистров подключены к первым входам узла формирования вектора и к первым входам блока вычитания, выход которого подключен к первому входу второго блока регистров, второй вход которого подключен к четвертому выходу блока управления, выход второго блока регистров подключен к первому входу первого блока элементов И и через блок элементов НЕ - к первому входу второго блока элементов И, второй вход которого подключен к пятому выходу блока управления, выход второго блока элементов И подключен через дешифратор к первому входу блока управления, шестой выход которого подключен к второму входу первого блока элементов И, выход которого подключен к первому входу третьего блока регистров, второй вход которого подключен к седьмому выходу блока управления, выходы третьего блока регистров подключены через узел формирования входной последовательности к входу четвертого блока регистров, первый и второй входы которого подключены соответственно к вось мому и девятому выходам блока управления, выход четвертого блока регистров подключен к первому входу третьего блока элементов И, второй вход которого подключен к десятому выходу блока .управления, выход третьего блока элементов И подключен к первому входу блока элементов ИЛИ,

выход которого подключен к второму входу блока памяти, третий вход которого подключен к одиннадцатому выходу блока управления, двенадцатый , выход которого подключен к первому входу счетчика, выход счетчика йодключен к четвертому входу блока памяти, первому входу первого блока сравнения и второму входу первого регистра, выход которого подключен к-второму входу первого блока сравнения, выход которого подключен к второму входу блока управления, выход блока памяти подключен к первому входу второго регистра, второй вход которого подключен к тринадцатому выходу блока з равления,, выход второго регистра подключен к первому входу второго блока сравнения и первому входу четвертого блока элементов И, выход второго блока сравнения подключен к третьему входу блока управления, второй вход второго блока сравнения подключен к выходу третьего регистра и первому входу пятого блока элементов И, второй вход которого подключен к четырнадцатому выходу блока управления, выход пятого блока элементов И подключен к второму входу блока элементов ИЛИ, второй вход четвертого блока элементов И подключен к пятнадцатому выходу блока управления, выход четвертого блока элементов И подключен к второму входу узла формирования вектора, третий вход которого подключен к шестнадцатому выходу блока управления и второму входу счетчика, четвертый и пятьй входы узла формирования вектора подключены соответственно к семнадцатому и восемнадцатым выходам блока управления, выходы узла формирования вектора подключены к вторым входам блока вычитания и первым входам четвертого регистра, второй вход которого подключен к девятнадцатому выходу блок управления, выход четвертого регистра подключен к первому входу шестого блока элементов И, второй вход которого подключен к двадцатому выходу блока управления, четвертый и пятый входЕа которого яв ляются соответственно первым и вторым управляющими входами ус тройств а, выход шестого блока элементов И является иформационным выходом устройства.

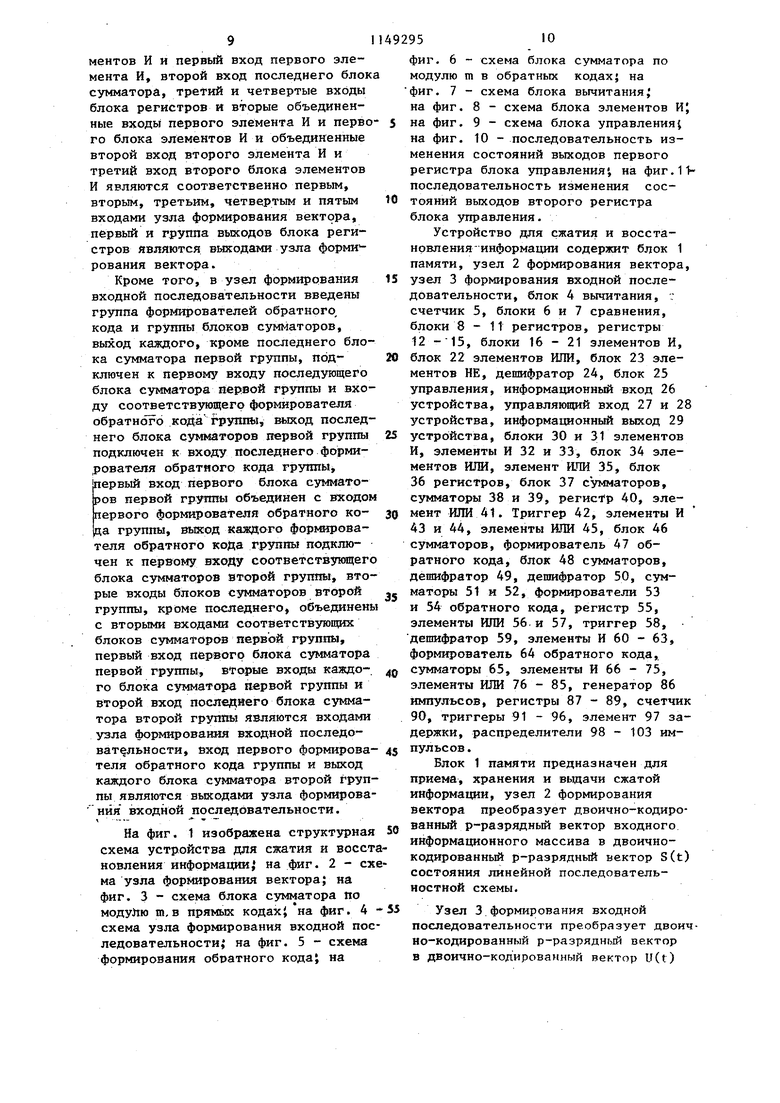

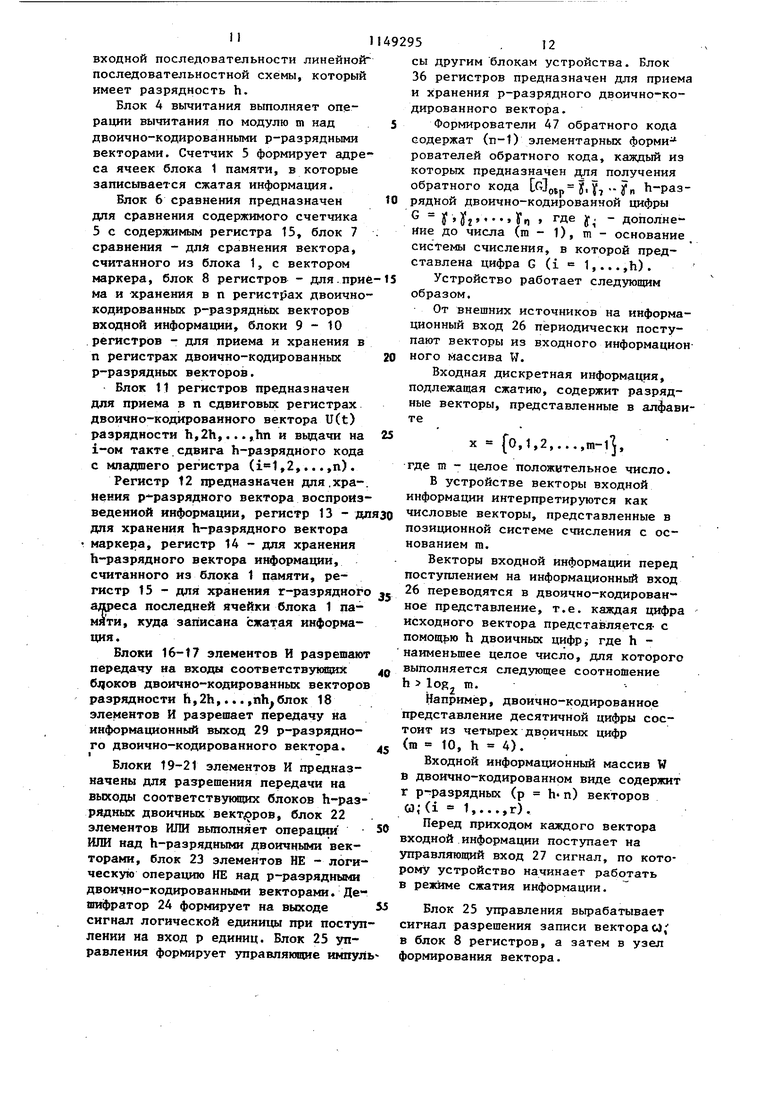

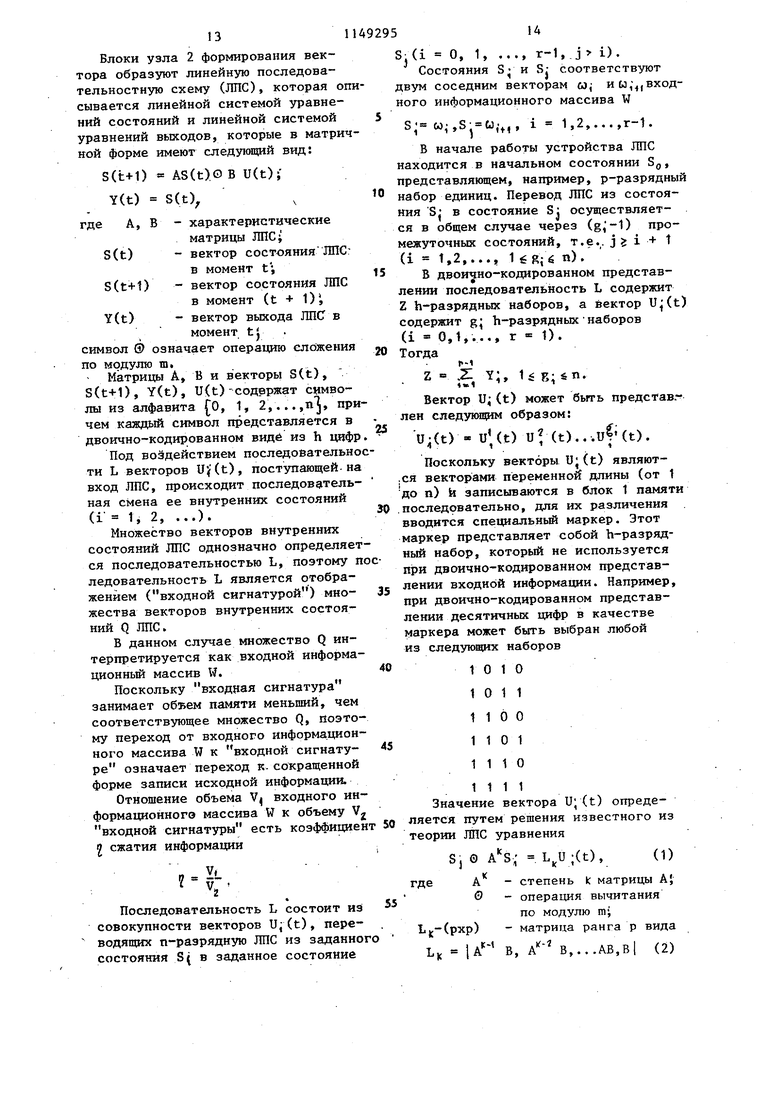

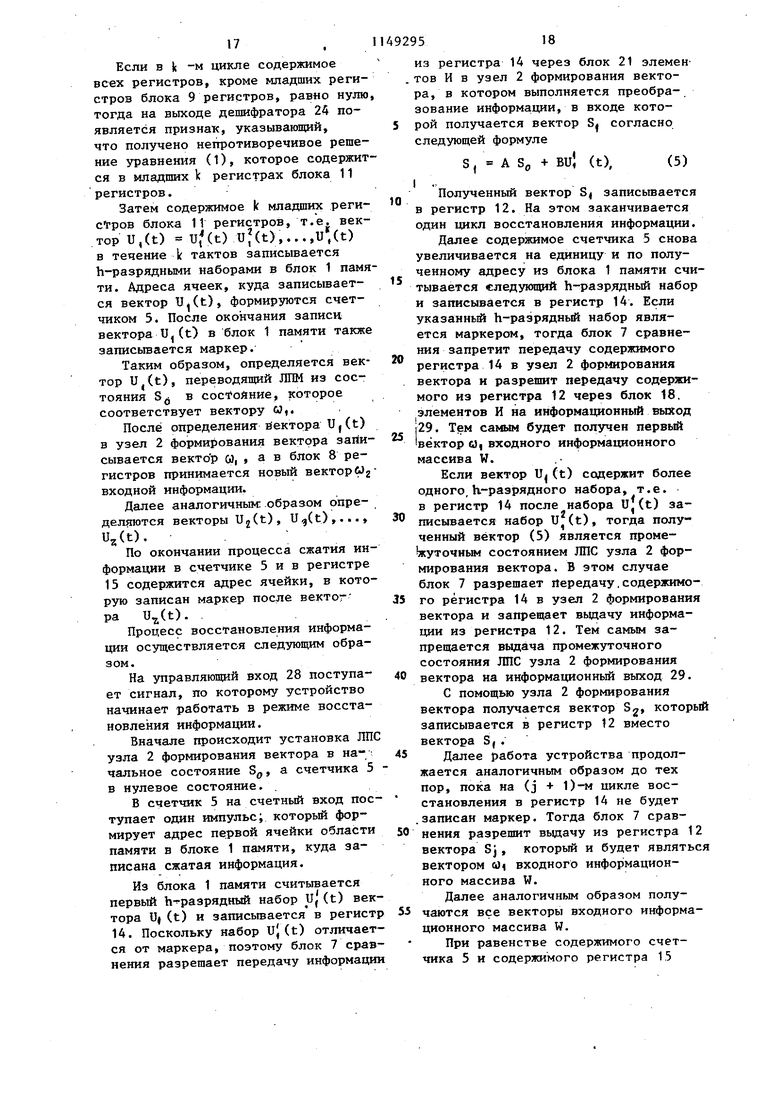

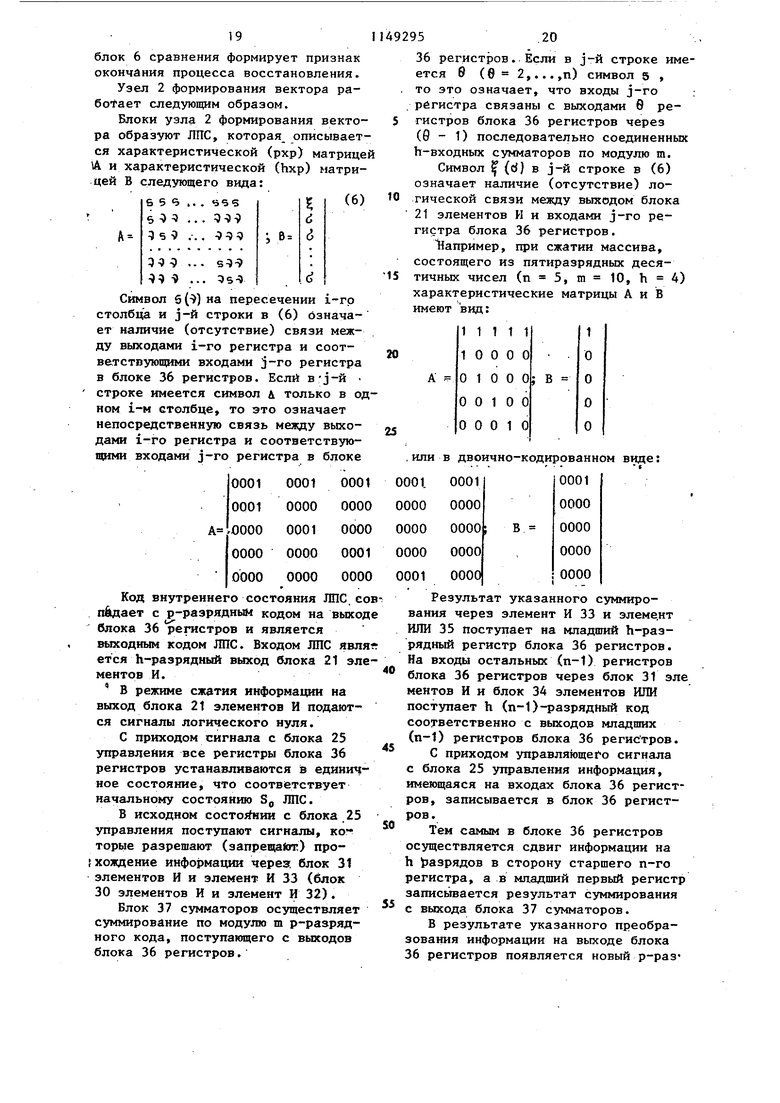

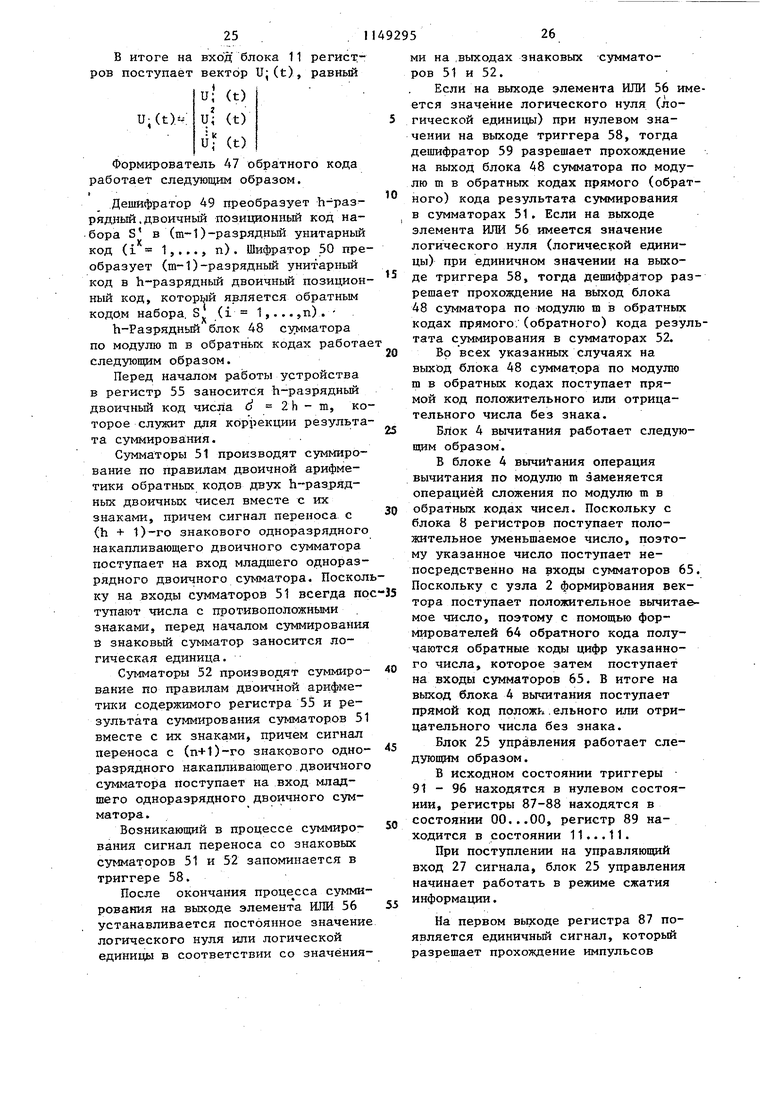

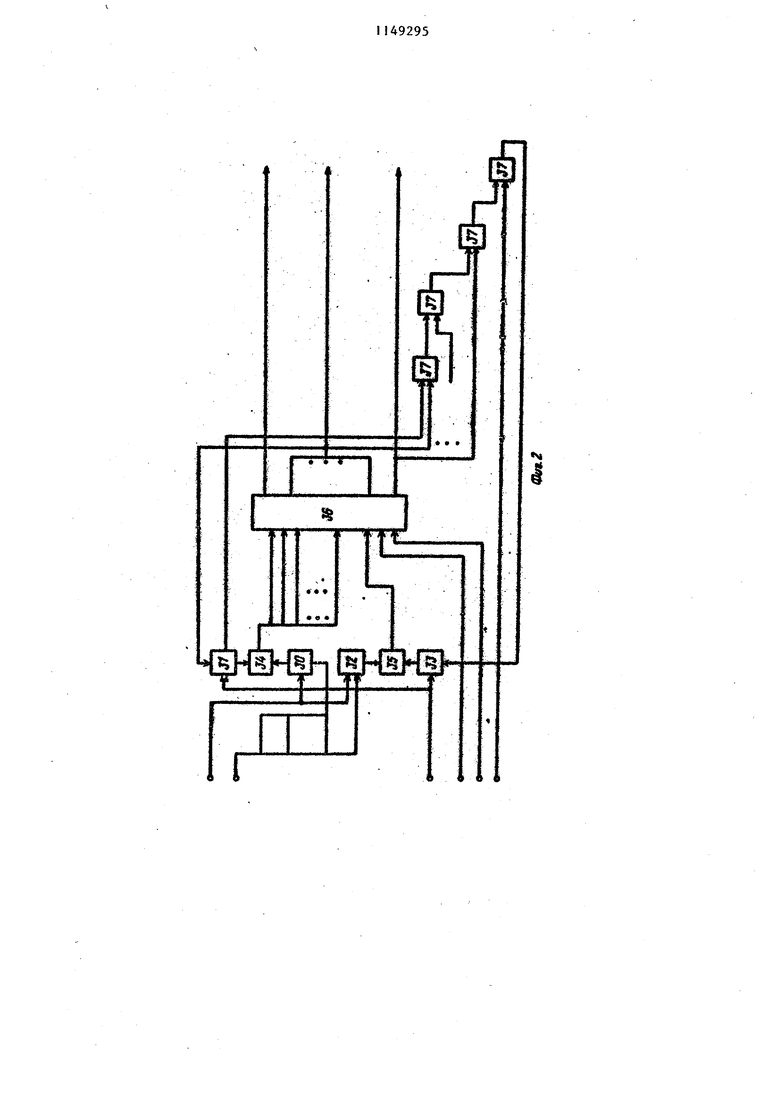

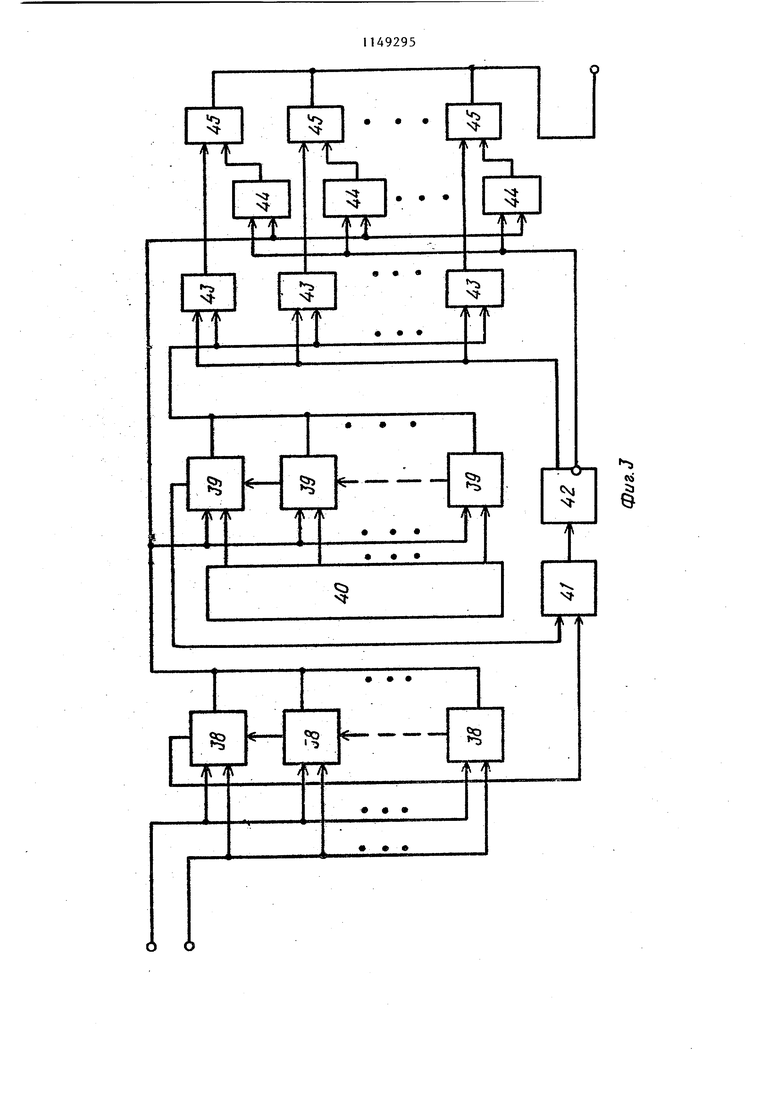

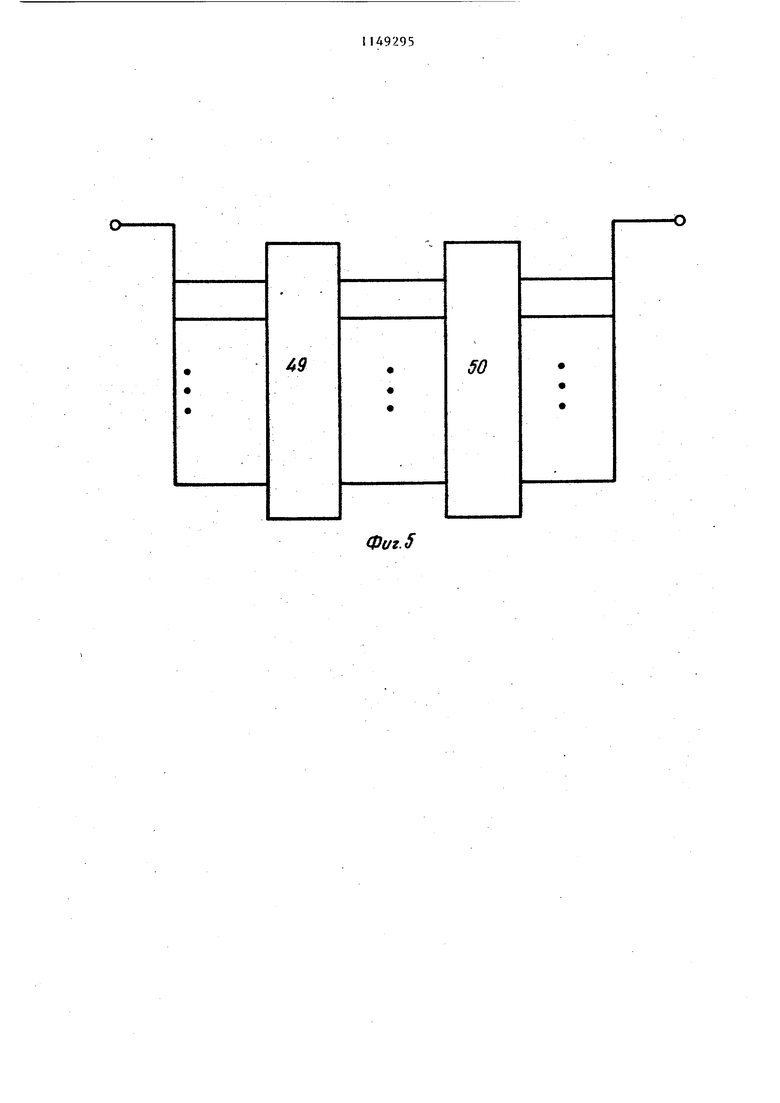

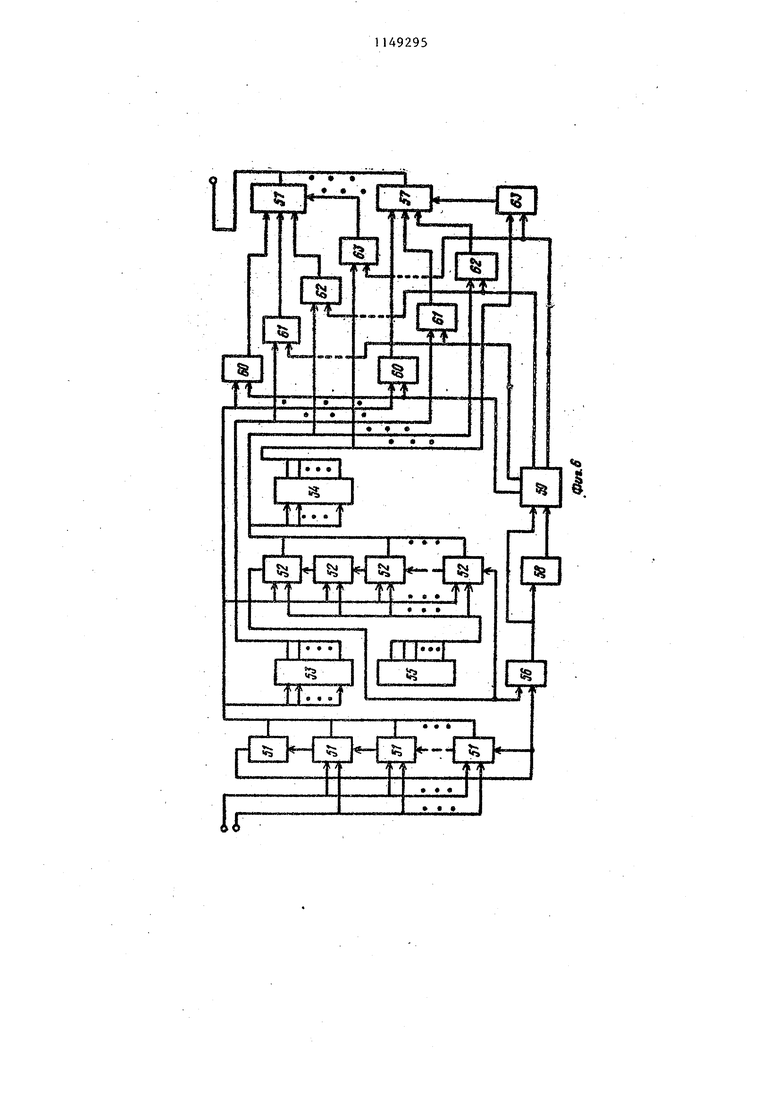

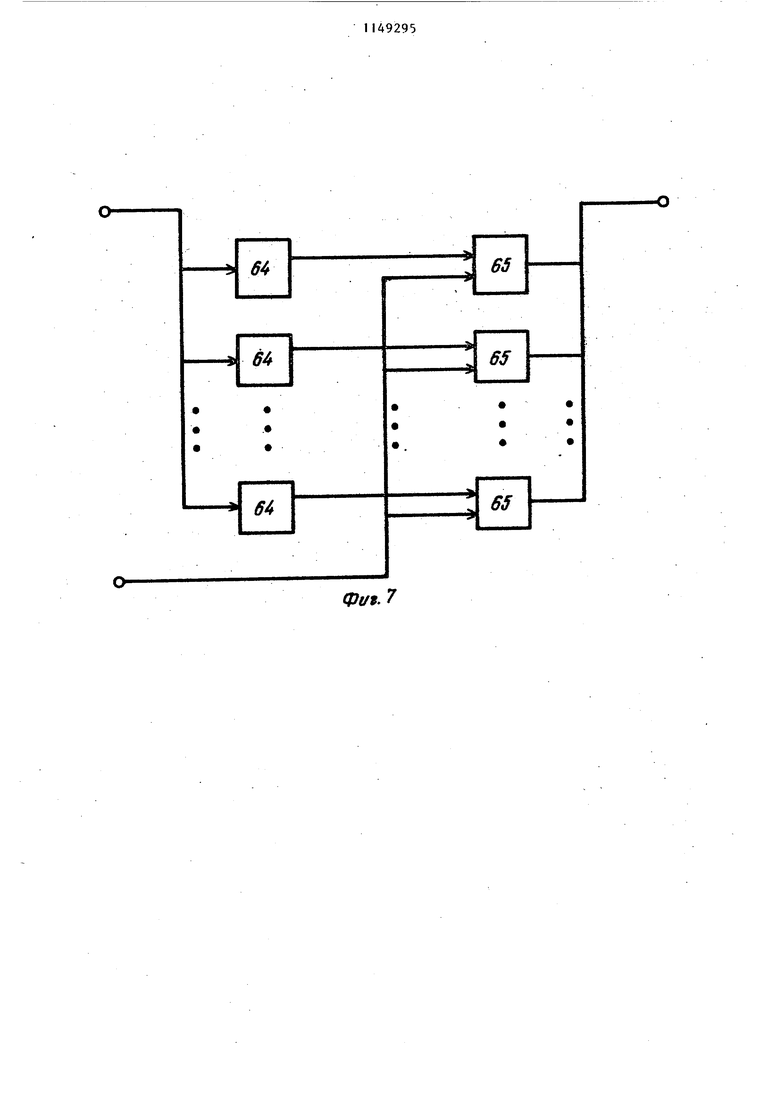

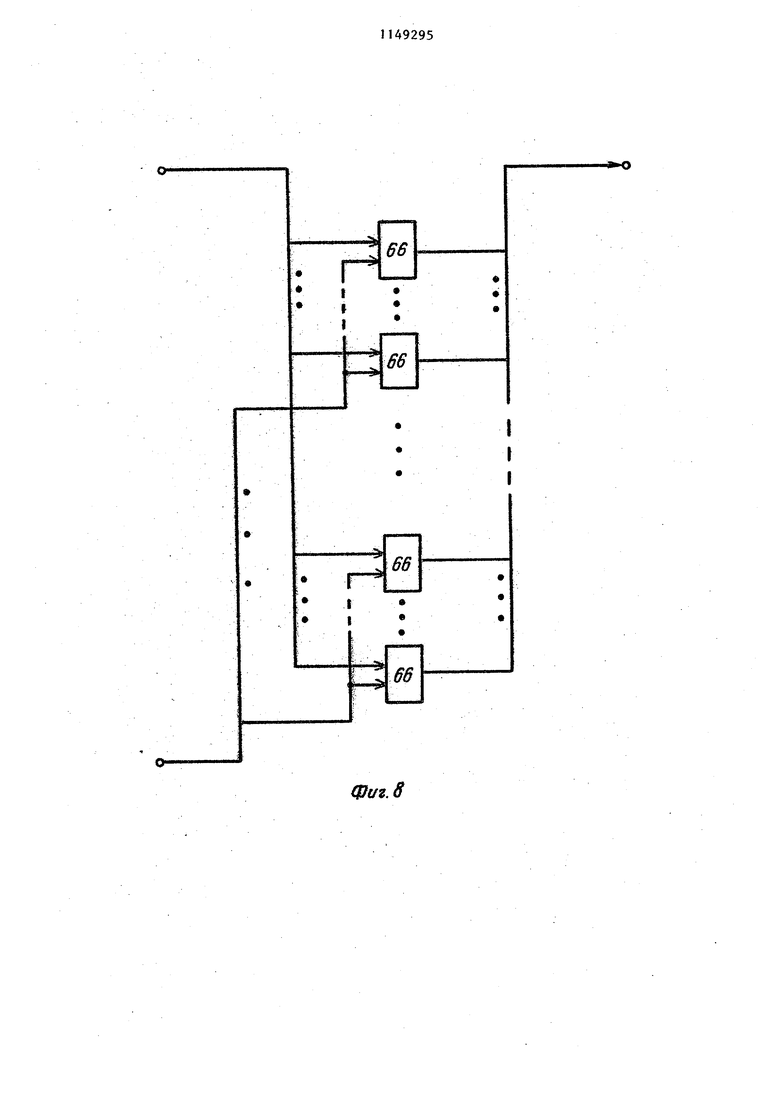

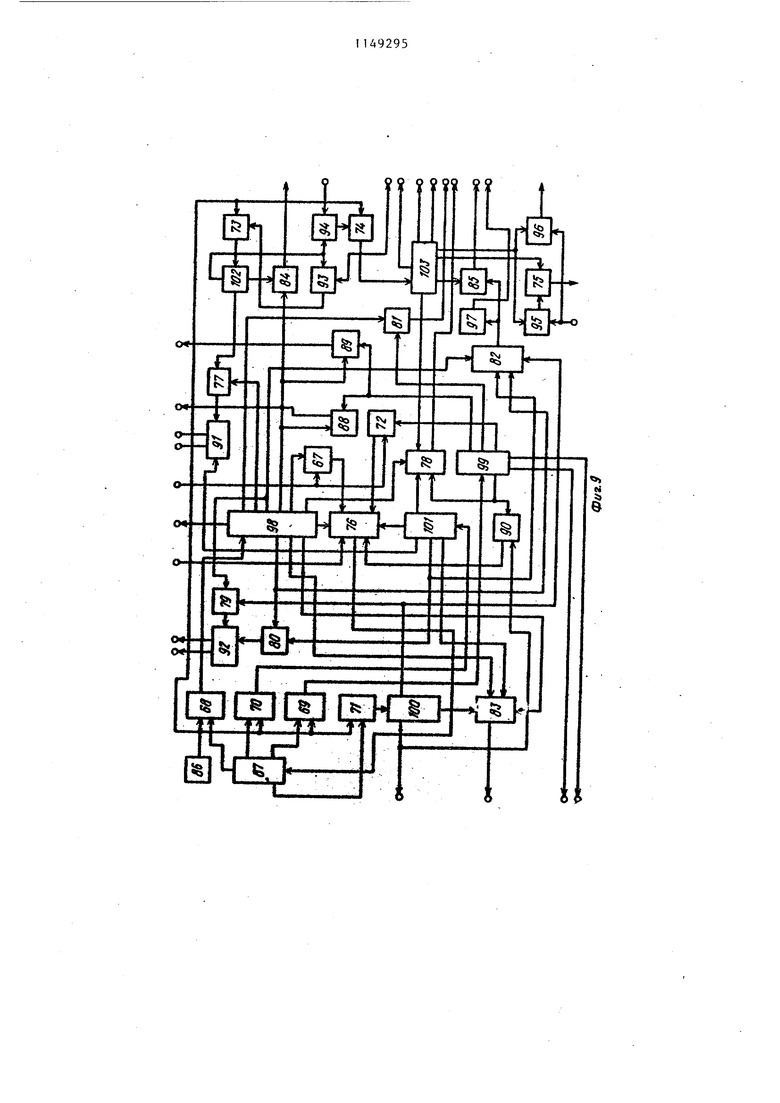

Кроме того, в блок управления введены распределители импульсов, регистры, генератор импульсов, триггеры элемент задержки, счетчик, элементы ИЛИ и элементы И, выход генератора импульсов подключен к первым входам первого - шестого элементов И, выходы первого - четвертого элементов И подключены к входам соответствующих распределителей импульсов, первые выходы первого и второго распределителей импульсов подключены к первьм входам соответственно седьмого и восьмого элементов И, выходы которых подключены к первому и второму входам первого элемента ИЛИ, выход первого элемента ИЛИ подключен к входу первого регистра, выходы которого подключены к вторым входам соответственно четвертого - первого элементов И, первый выход четвертого распределителя импульсов подключен к певому входу второго элемента ИЛИ, второй выход четвертого распределителя импульсов подключен к первому входу счетчика, третий выход четвертого распределителя импульсов подключен к первому входу третьего элемента ИЛИ и первому входу четвертого элемента ИЛИ, выход которого подключен к первому входу первого триггера второй вход которого подключен к выходу пятого элемента ИЛИ, второй выход первого распределителя импульсов и первый выход третьего распределителя импульсов подключены соответственно к третьему и четвертому входам первого элемента ИЛИ, третий выход первого и второй выход третьег распределителей импульсов подключены соответственно к второму и третьему входам второго элемента ИЛИ, четвертый вход которого подключен к четвертому выходу первого распределителя импульсов, пятый выход первого распределителя импульсов и третий выход третьего распределителя импульсов подключены соответственно к первому и второму входам пятого элемента ИЛИ и к второму и третьему входам третьего элемента ИЛИ, выход которого подключен к первому входу шестого элемента ИЛИ и входу элемента задержки, шестой выход первого распределителя импульсов подключен к четвертому входу третьего элемента ИЛИ и второму входу четвертого элемента ИЛИ, седьмой вьгход первого и четвертый выход третьего распределителей импульсов подключены соответственно к первому и второму входам седьмого элемента ИЛИ, второй .выход второго распределителя импульсов подключен к третьему входу седьмого элемента ИЛИ и второму входу счетчика, выход которого подключен к третьему входу первого элемента И1Ш, восьмой выход первого распре делителя импульсов подключен к первому входу восьмого элемента ИЛИ, выход которого подключен к первому входу второго триггера, второй вход которого подключен к пятому выходу третьего распределителя импульсов, девятый выход первого распределителя импульсов и третий выход второго рас пределителя подключены соответственно к первому и второму входам девятого элемента ИЛИ, десятый выход пер вого распределителя импульсов подклю чен к первому входу десятого элемента ИЛИ и первым, входам второго и третьего регистров, вторые входы которых подключены к четвертому выхо ду второго распределителя импульсов, второй вход десятого элемента ИЛИподключен к первому входу пятого распределителя импульсов, второй выход которого подключен к второму входу восьмого элемента ШШ, третий выход которого подключен к первьо4 входам третьего и четвертого триггеров, выход третьего триггера подключен к второму входу пятого элемен та И, выход которого подключен к вхо ду пятого распределителя импульсов, выход четвертого триггера подключ н к второму входу шестого элемента И, выход которого подюгаочен к вхо ду шестого распределителя импульсов, первый и второй выходы которого подключены к второму и четвертому входам соответственно шестого и седьмого элементов ИЛИ, третий выход шестого распределителя импульсов подключен к первым входам пятого и шестого триггеров, выход пятого триггера подключен к первому входу девятого элемента И, второй вход которого подключен к четвертому выхо ду шестого распределителя импульсов, объединенные вторые входы седьмого и восьмого элементов И, второй вход четвертого триггера, вторые входы пятого и шестого триггеров, шестой вход первого элемента ИЖ и второй вход третьего триггера являются соответственно первым - пятым входами блока управления, выход элемента эадержки, вьсход второго элемента ИЛИ, одиннадцатый вькод первого распределителя импульсов, выход девятого элемента ИЛИ, выход третьего регистра,выход второго регистра, пятый выход второго распределителя импульсов, второй выход четвертого распределителя импульсов, шестой выход второго распределителя импульсов, первый выход первого триггера, пятый выход шестого распределителя импульсов, выход десятого элемента ИЛИ, шестой выход шестого распределителя импульсов, второй выход первого триггера, выход шестого триггера, выход шестого элемента ИЛИ, выход седьмого элемента ИЛИ, выходы второго триггера, седьмой выход шестого распределителя импульсов и выход девятого элемента И являются соответственно первым - двадцатым выходами блока управления. Кроме того, в узел формирования вектора введены блоки элементов И, блок элементов ШШ, блок регистров блоки сумматоров, элементы И и элемент ИЛИ, выход первого блока элементов И подключен к первому входу блока элементов ИЛИ, выходы которого подключены к соответствующим первым входам блока регистров, выход первого элемента И подключен к первому входу элемента ИЛИ, выход которого подключен к второму входу блока регистров, первый выход блока регистров подключен к первому входу второго блока элементов И и первому входу первого блока сумматоров, выход каждого блока сумматоров подключен к первому входу последующего блока сумматоров, группа выходов блока регистров подключена к вторым входам соответствующих блоков сумматоров, кроме последнего, группа выходов блока регистров, кроме последнего выхода группы, подключена к вторым входам второго блока элементов И, выход которого подключен к второму входу блока элементов ИЛИ, выход последнего блока сумматоров подключен к первому входу второго элемента И, выход которого подключен к второму входу элемента ИЛИ, первый вход первого блока элементов И и первый вход первого элемента И, второй вход последнего блок сумматора, третий и четвертые входы блока регистров и вторые объединенные входы первого элемента И и перво го блока элементов И и объединенные второй вход второго элемента И и третий вход второго блока элементов И являются соответственно первым, вторым, третьим, четвертым и пятым входами узла формирования вектора, первый и группа вЬ1ходов блока регистров являются выходами узла форми рования вектора. Кроме того, в узел формирования входной последовательности введены группа формирователей обратного, кода и группы блоков сумматоров, выход каждого, кроме последнего блока сумматора первой группы, подключен к первому входу последующего блока сумматора иервой группы и вхо ду соответствующего формирователя обратного кода группы, выход послед него блока сумматоров первой группы подключен к входу последнего формирователя обратного кода грзтпы, первый вход первого блока сумматоров первой группы объединен с входо первого формирователя обратного кода группы, выход каждого формирователя обратного кода группы подключен к первому входу соответствующег блока сумматоров второй группы, вто рые входы блоков сумматоров второй группы, кроме последнего, объединен с вторыми входами соответствующих блоков сумматоров первой группы, первый вход первого блока сумматора первой группы, вторые входы каждого блока сумматора аервой группы и второй вход последнего блока сумматора второй группы являются входами узла формирования входной последоват льности, вход первого формирова теля обратного кода группы и выход каждого блока сумматора второй груп пы являются выходами узла формирова нйя входной последовательности. На фиг. 1 изображена структурная схема устройства для сжатия и восст новления информации на фиг. 2 - сх ма узла формирования вектора; на фиг. 3 - схема блока сумматора по модулю т,в прямых кодахJ на фиг. 4 схема узла формирования входной пос ледовательности; на фиг. 5 - схема формирования обратного кода; на фиг. 6 - схема блока сумматора по модулю m в обратных кодах; на фиг. 7 - схема блока вычитания; на фиг. 8 - схема блока элементов HJ на фиг. 9 - схема блока управленияi на фиг. 10 - последовательность изменения состояний выходов первого регистра блока управления , на фиг. 11последовательность изменения состояний выходов второго регистра блока управления. Устройство для сжатия и восстановления-информации содержит блок 1 памяти, узел 2 формирования вектора, узел 3 формирования входной последовательности, блок 4 вычитания, : счетчик 5, блоки 6 и 7 сравнения, блоки 8 - 11 регистров, регистры 12 -15, блоки 16 - 21 элементов И, блок 22 элементов ИЛИ, блок 23 элементов НЕ, дешифратор 24, блок 25 управления, информационный вход 26 устройства, управляющий вход 27 и 28 устройства, информационный выход 29 устройства, блоки 30 и 31 элементов И, элементы И 32 и 33, блок 34 элементов ИЛИ, элемент ИПИ 35, блок 36 регистров, блок 37 сумматоров, сумматоры 38 и 39, регистр 40, элемент ИЛИ 41. Триггер 42, элементы И 43 и 44, элементы ИЛИ 45, блок 46 сумматоров, формирователь 47 обратного кода, блок 48 сумматоров, дешифратор 49, дешифратор 50, сумматоры 51 и 52, формирователи 53 и 54 обратного кода, регистр 55, элементы ИЛИ 56. и 57, триггер 58, дешифратор 59, элементы И 60 - 63, формирователь 64 обратного кода, сз мматоры 65, элементы И 66 - 75, элементы ИШ 76 - 85, генератор 86 импульсов, регистры 87 - 89, счетчик 90, триггеры 91 - 96, элемент 97 задержки, распределители 98 - 103 импульсов . Блок 1 памяти предназначен для приема, хранения и вьщачи сжатой информации, узел 2 формирования вектора преобразует двоично-кодированный р-разрядный вектор входного информационного массива в двоичнокодированный р-разрядный вектор S(t) состояния линейной последовательиостной схемы. Узел 3.формирования входной последовательности преобразует двоично-кодированный р-разрядный вектор в двоично-кодированный вектор U(t)

входной последовательности линейной последовательностной схемы, который имеет разрядность h.

Блок 4 вычитания выполняет операции вычитания по модулю m над двоично-кодированными р-разрядными векторами. Счетчик 5 формирует адреса ячеек блока 1 памяти, в которые записывается сжатая информация.

Блок 6 сравнения предназначен для сравнения содержимого счетчика 5 с содержимым регистра 15, блок 7 сравнения - для сравнения вектора, считанного из блока 1, с вектором маркера, блок 8 регистров - для.при6 ма и хранения в п регист1;ах двоичнокодированных р-разрядных векторов входной информации, блоки 9-10 регистров - для приема и хранения в п регистрах двоично-кодированных р-разрядных векторов.

Блок 11 регистров предназначен для приема в п сдвиговых регистрах двоично-кодированного вектора U(t)

разрядности h,2hhn и вьщачи на

i-oM такте сдвига h-разрядного кода с младшего регистра (,2,...,п).

Регистр 12 предназначен для.хра-. нения р разрядного вектора воспроизведенной информации, регистр 13 - дл для хранения h-разрядного вектора маркера, регистр 14 - для хранения h-разрядного вектора информации, считанного из блока 1 памяти, регистр 15 - для хранения г-разрядного адреса последней йчейки блока 1 памяти, куда записана сжатая информация. Блоки 16-17 элементов И разрешают передачу на входы соответствугацих 6j|OKOB двоично-кодированных векторов разрядности Ь,2h,...,nh блок 18 элементов И разрешает передачу на информационный выход 29 р-разрядно- го двоично-кодированного вектора. Блоки 19-21 элементов И предназначены для разрешения передачи на выходы соответствунмцих блоков h-раэрядных двоичных , блок 22 элементов ИЛИ выполняет операции ЮШ над h-разрядными двоичными векторами, блок 23 элементов НЕ - логическую операцию НЕ над р-разрядными двоично-кодированными векторами. Дешифратор 24 формирует на выходе сигнал логической единицы при поступ лении на вход р единиц. Блок 25 управления формирует управляющие импул

сы другим блокам устройства. Блок 36 регистров предназначен для приема и хранения р-разрядного двоично-кодированного вектора.

Формирователи 47 обратного кода содержат (и-1) элементарных форми рователей обратного кода, каждый из которых предназначен для получения обратного кода Ир«р 1-У - п h-pasрядной двоично-кодированной цифры

G If УП Д if, дополнение до числа (га - 1), m - основание системы счисления, в которой представлена цифра G (i 1,...,h).

Устройство работает следующим образом.

От внешних источников на информационный вход 26 периодически поступают векторы из входного информацион ного массива W.

Входная дискретная информация, подлежащая сжатию, содержит разрядные векторы, представленные в алфавите

X о,1,2m-l,

где m - целое положительное число.

В устройстве векторы входной информации интерпретируются как числовые векторы, представленные в позиционной системе счисления с основанием га. Векторы входной информации перед поступлением на информационный вход 26 переводятся в двоично-кодированное представление, т.е. каждая цифра исходного вектора представляется- с помощью h двоичных цифр где h наименьшее целое число, для которого выполняется следующее соотношение h log m. Например, двоично-кодированное представление десятичной цифры состоит из четырех двричных цифр (га 10, h 4). Входной информационный массив W в двоично-кодированном виде содержит г р- разрядных (р h« п) векторов со; (1 1,...,г). Перед приходом каждого вектора входной информации постзшает на управляющий вход 27 сигнал, по которому устройство начинает работать в режиме сжатия информации. Блок 25 управления вырабатывает сигнал разрешения записи векторам, в блок 8 регистров, а затем в узел формирования вектора. 131 Блоки узла 2 формирования вектора образуют линейную последовательностную схему (ЛПС), которая опи сывается линейной системой уравнений состояний и линейной системой уравнений выходов, которые в матрич ной форме имеют следующий вид: S(t+1) « AS(t)CD В U(t); Y(t) S(t), где A, В характеристические матрицы Jinci S(t) - вектор состоянияЛПС: в момент ti S(t+1) - вектор состояния ЖС в момент (t + 1), Y(t) - вектор выхода ЛПС в момент ti символ & означает операцию слажения по модулю т. Ма.трицы А, В и векторы S(t), S(t+1), Y(t), U{t)-содержат символы из алфавита 0, 1, 2,...,п, при чем каждый символ представляется в двоично-кодированном виде из h цифр Под воздействием последовательно ти L векторов ), поступающей-на вход ЛПС, происходит последовательная смена ее внутренних состояний (Г 1, 2, ...). Множество векторов внутренних состояний ЛПС однозначно определяет ся последовательностью L, поэтому п ледовательность L является отобра женйем (входной сигнатурой) множества векторов внутренних состояний Q ЛПС.. В данном случае множество Q интерпретируется как входной информационный массив W. Поскольку входная сигнатура занимает обвем памяти меньший, чем соответствующее множество Q, поэтому переход от входного информационного массива W к входной сигнатуре означает переход к- сокращенной форме записи исходной информации. Отношение объема V входного информационного массива W к объему V,j входной сигнатуры есть коэффициент 7 сжатия информации . :. Последовательность L состоит из совокупности векторов U-(t), переводящих п-разряднзгю ЛПС из заданного состояния S( в заданное состояние , г-1, j i). Состояния S; и S: соответствуют двум соседним векторам «, и ы,,входного информационного массива W S; w-,S- eo,-,,, i 1,2,...,r-1. В начале работы устройства ЛПС находится в начальном состоянии Sg, представляющем, например, р-разрядный набор единиц. Перевод ЛПС из состояния S: в состояние S; . JO v,wv, w«x. U, осуществляется в общем случае через (g,-1) промежуточных состояний, т.е.. j i + t (i t,2,..., 1 g gjg n). В двоично-кодированном представлении последовательность L содержит Z h-разрядных наборов, а вектор U(t) содержит g h-разрядныхнаборов (i О,t,..., г 1) . Тогда 2 f, ; 1 г,. Вектор U;(t) может быть представь лен следунищда образом: u-(t) - u,(t) и (t)...uf(t). Поскольку векторы Uj(t) являются векторами переменной длины (от 1 до п) и записываются в блок 1 памяти последовательно, для их различения вводится специальный маркер. Этот маркер представляет собой h-разрядный набор, который не используется при двоично-кодированном представлении входной информации. Например, при двоично-кодированном представлении десятичных цифр в качестве маркера может быть выбран любой из следующих наборов 1010 1011 1111 Значение вектора U;(t) определяется путем решения известного из уравнения Sj 0 AS; (t), А - степень k матрицы AJ 0 - операция вычитания по модулю mj Lu-(pxp) - матрица ранга р вида В, В,.. .АБ,В| (2) 15 коэффиМинимальное значение циента k , при котором уравнение имеет непротиворечивое решение, определяет минимальную длину g вектора U- (t) R . С поступлением в блок 8 регистров первого вектора UJ, ЛПС устанавливается в начальное состояние Далее в узле 2 формирования вектора ползгчается произведение AS-, На выходе блока 4 вычитания п лучается вектор S| S J Ъ f @ Вектор S записывается в блок 9 регистров. Таким образом, получается левая часть уравнения (1) при 1с 1. Если вектор (3) равен нулю, тог да на выходе дешифратора 24 появля ется признак, указывающий, что при k 1 получено непротиворечивое решение уравнения (1), которое равно (t) .00.г О Далее в счетчик 5 на счетный вход поступает один импульс, который формирует адрес первой ячейки в блоке 1 памяти, куда будет записан полученный вектор U,(t). Затек в регистр 15 записывается содержим счетчика 5. . По сигналу разрешения записи в блок 1 памяти информащш, состояща из h нуле:й, из первого регистра бл ка 11 регистров через блок 19 элементов И и блок 22 элементов НПИ записывается в блок 1 памяти. Далее в счетчик 5 добавляется еще одна единица и по очередному адресу в следующую ячейку блока 1 памяти из регистра 13 через блок 2 ;элементов И и блок 22 элементов ИЛ записывается маркер. На этом заканчивается цикл работы устройства I Если вектор (3) н§ равен нулю, тогда содержимое первого регистра блока 9 регистров через блок 16 элементов И записывается в регистр блока 10 регистров. Указанна запись информации в блок 10 регист осуществляется при наличии на вход блока 16 элементов И соответствующ комбинации разрешающих сигналов, к рые поступают с блока 25 управлени 5 Затем содержимое блока 10 регистров поступает на узел 3 формирования входной последовательности на выходе которого формируется правая часть уравнения (1) при k 1, т.е. U,(t). Результат (4) записывается в блок 11 регистров. От блока 25 управления поступает комбинация сигналов, которая разрешает прохождение через блок 17 элементов И информации с выходов всех регистров, кроме первого, блока 9 регистров. Если содержимое всех регистров, кроме первого блока 9 регистров, равно нулю, тогда на выходе дешифратора 24 появляется признак, указывающий, что при k 1 получено непротиворечивое решение уравнения (1), которое содержится в первом регистре блока 11 регистров. Полученное решение затем из блока 11 регистров записывается в блок 1 памяти по адресу первой ячейки. Далее в счетчик 5 добавляется еще одна единица и по очередному адресу в следующую ячейку 6jjoKa 1 памяти записывается i apкер. На этом также заканчивается цикл работы устройства. Если содержимое всех регистров, , кроме первого блока 9 регистров, не равно нулю, тогда ищется непротиворечивое решение уравнения П) при k 2, 3,...,п. С этой целью с помощью узла 2 формирования вектора периодически формируются произведения А 5 ив блок 9 регистров записывается вектор S , равный S. , k 2,3,...п. В | -м цикле по управляющим выходам блока 25 управления поступает комбинация сигналов, которая разреШает прохождение через блок 17 элементов И информации с выходов всех регистров, кроме младших 1с регистров, блока 9 регистров. В k -м цикле также по выходам блока 25 поступает комбинация сигналов, которая разрешает прохождение через блок 16 элементов И информации с выходов 1 -k младших регистров блока 9 регистров соответственно на входы ; старших п - (п - k) регистров блока 10 регистров. .

Если в )( -м цикле содержимое всех регистров, кроме младших регистров блока 9 регистров, равно нулю тогда на выходе дешифратора 24 появляется признак, указывающий, что получено непротиворечивое решение уравнения (1), которое содержится в младших k регистрах блока 11 регистров.

Затем содержимое k младших регистров блока 11 регистров, т.е. вектор U,(t) U/(t) Uj(t),...,u;(t) в течение k тактов записывается h-разрядными наборами в блок 1 памяти. Адреса ячеек, куда записывается вектор tJ,(t), формируются счетчиком 5. После окончания записи вектора и(t) в блок 1 памяти также записьшается маркер.

Таким обрааом, определяется вектор и (t), переводящий ЛПМ из состояния S в сос ойние, которое соответствует вектору Ы«.

После определения вектрра и j(t) в узел 2 формирования вектора записывается вектор и, а в блок 8 регистров принимается новый вектор Wj входной информации.

Далее аналогичным: образом определяются векторы U2(t), U(t),... U(t).

По окончании процесса сжатия информации в счетчике 5 и в регистре 15 содержится адрес ячейки, в которую записан маркер после вектог ра U(t).

Процесс восстановления информации осуществляется следующим образом.

На управляющий вход 28 поступает сигнал, по которому устройство нагшнает работать в режиме восстановления информации.

Вначале происходит установка ЛПС узла 2 формирования вектора в на- ; чальное состояние Sg, а счетчика 5 в нулевое состояние.

В счетчик 5 на счетный вход поступает один импульс; который формирует адрес первой ячейки области памяти в блоке 1 памяти, куда записана сжатая информация.

Из блока 1 памяти считьгеается первый Ъ- разрядный набор и| (t) вектора U( (t) и записьгеается в регистр 14. Поскольку набор Uj(t) отличается от маркера, поэтому блок 7 сравнения разрешает передачу информации

из регистра 14 через блок 21 элемен тов И в узел 2 формирования вектора, в котором выполняется преобра-. зование информации, в входе которой получается вектор S| согласно следующей формуле

S, А So + ви; (t),

(5)

I

Полученный вектор S| записьшается в регистр 12. На этом заканчивается один цикл восстановления информации. Далее содержимое счетчика 5 снова увеличивается на единицу и по полученному адресу из блока 1 памяти счи5тывается следунлций h-разрядный набор и записывается в регистр 14. Если указанный h-разрядный набор является маркером, тогда блок 7 сравнения запретит передачу содержимого

0 регистра 14 в узел 2 формирования вектора и разрешит передачу содержимого из регистра 12 через блок 18, элементов И на информационный выход 129. Тем самым будет получен первый

5 вектор е, входного информационного массива W.

Если вектор U(t) содержит более одного, h-разрядного набора, т.е. в регистр 14 после набора UJ(t) записывается набор U (t), тогда полученный вектор (5) является промежуточнь состоянием ЛПС узла 2 формирования вектора. В этом случае блок 7 разрешает Передачу.содержимого регистра 14 в узел 2 формирования вектора и запрещает вьщачу информации из регистра 12. Тем самым запрещается вьщача промежуточного состояния ЛПС узла 2 формирования

0 вектора на информационный выход 29.

С помощью узла 2 формирования вектора получается вектор Sg, который записывается в регистр 12 вместо вектора S,.

5 Далее работа устройства продолжается аналогичным образом до тех пор, пока на (j + 1)-м цикле восстановления в регистр 14 не будет .записан маркер. Тогда блок 7 сравнения разрешит выдачу из регистра 12 вектора Sj, которьтй и будет являться вектором MI входного информационного массива W.

Далее аналогичным образом получаются все векторы входного информационного массива W,

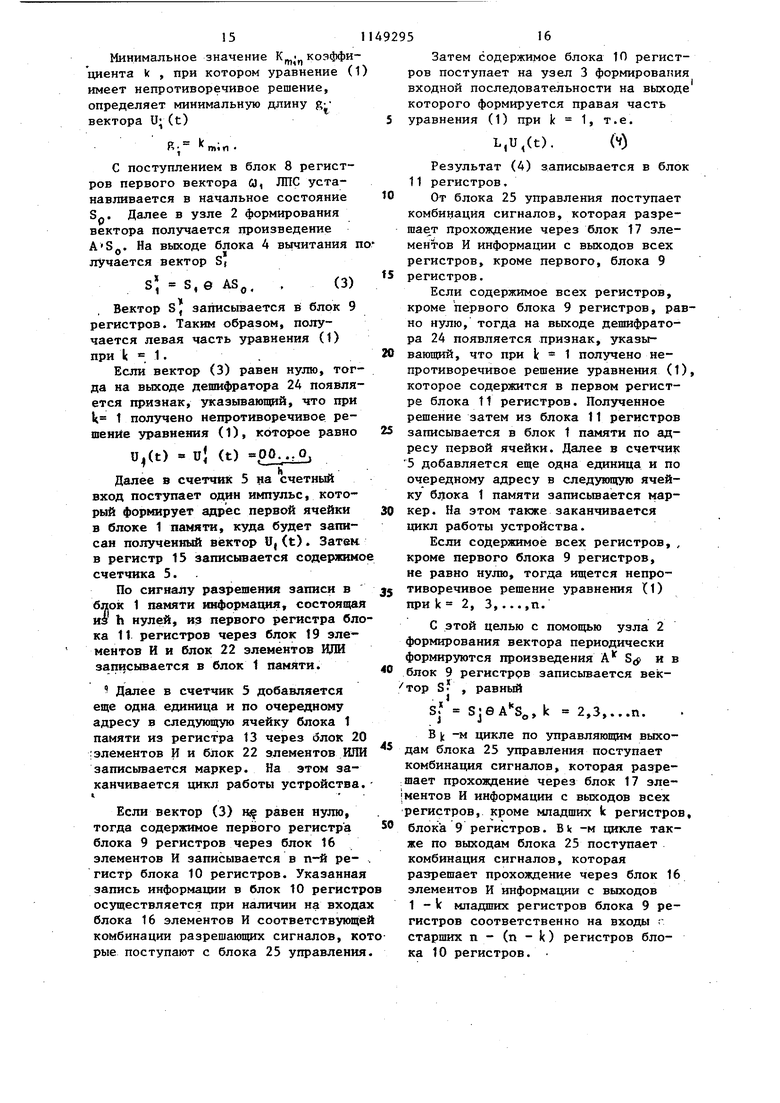

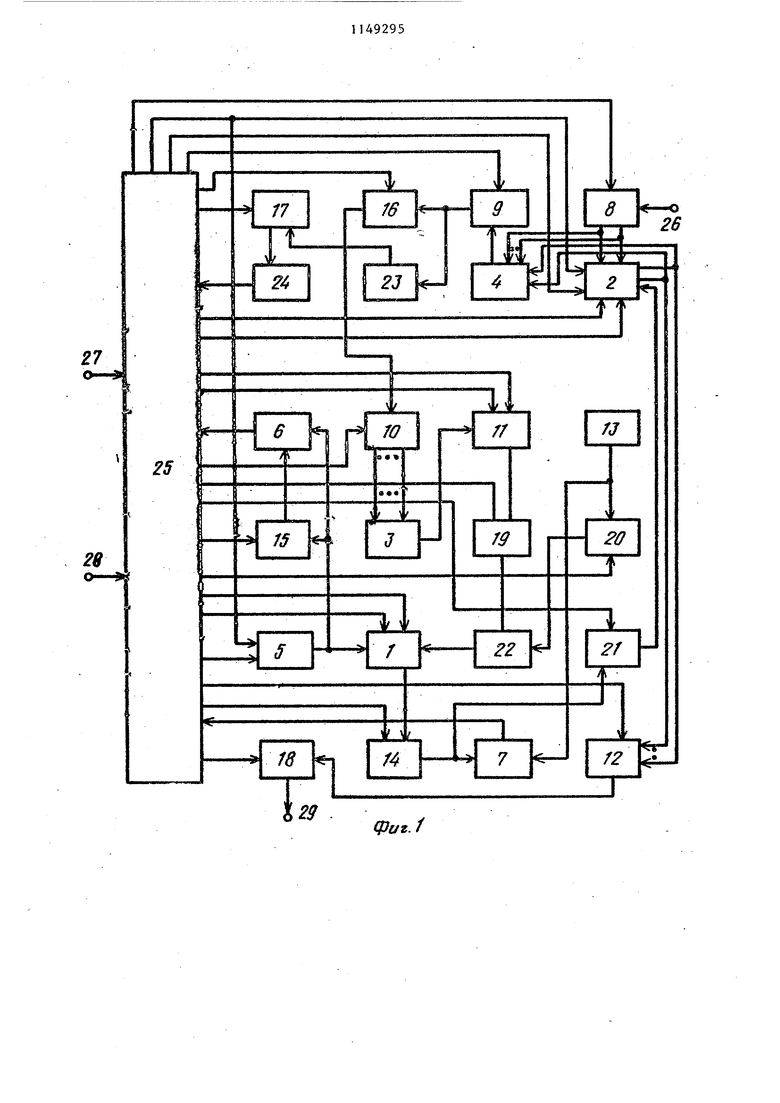

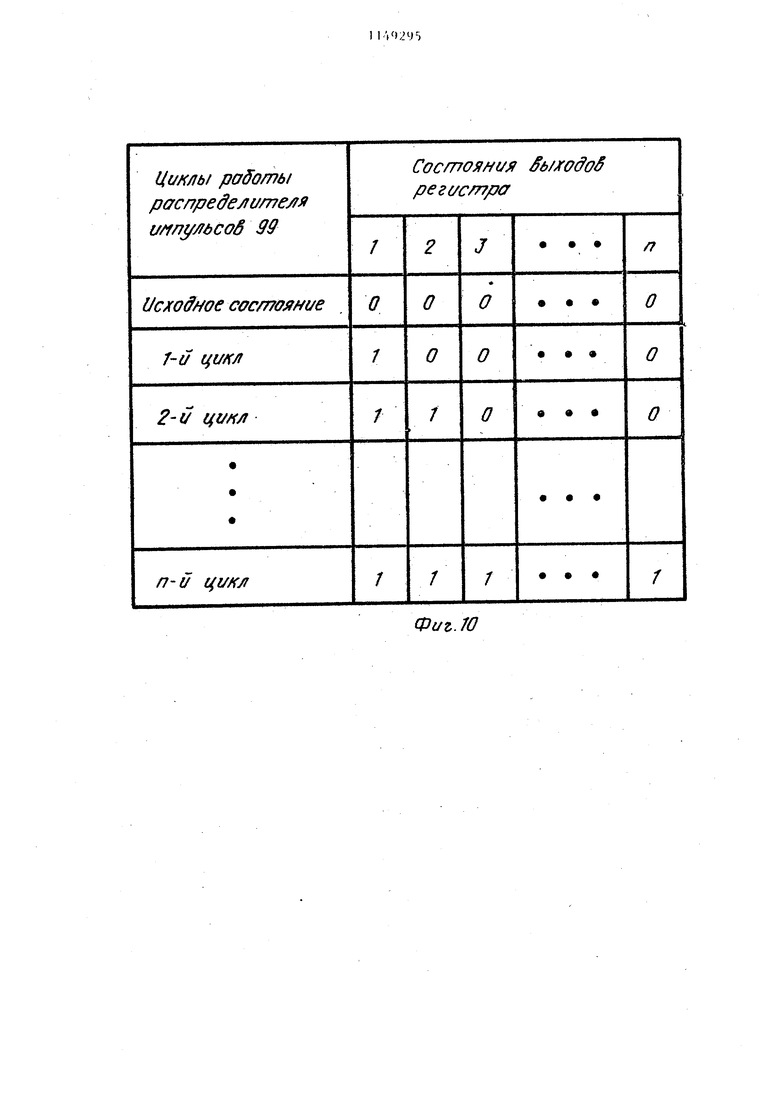

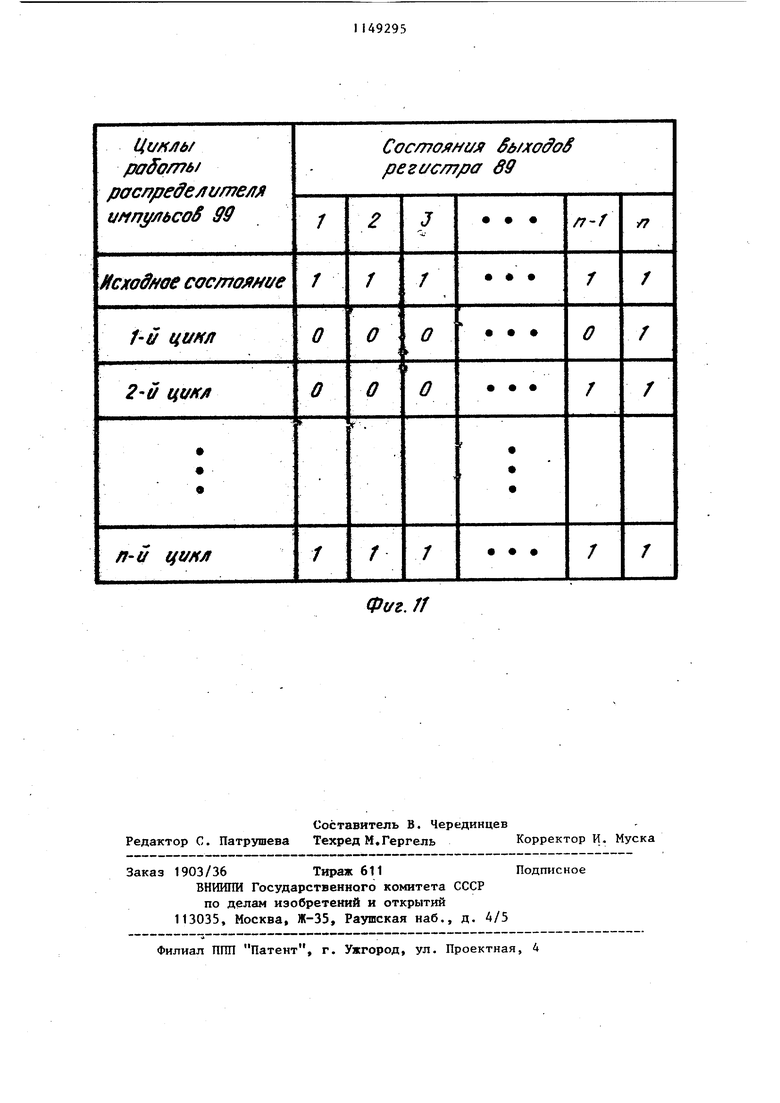

При равенстве содержимого счетчика 5 и содержимого регистра 15 блок 6 сравнения формирует признак окончания процесса восстановления. Узел 2 формирования вектора работает следующим образом. Блоки узла 2 формирования вектора образуют ЛПС, которая описывает ся характеристической (рхр) матрице А и характеристической (hxp) матрицей В следующего вида: Символ б() на пересечении i-rp столбца и j-й строки в (6) бзначает наличие (отсутствие) связи между выходами i-ro регистра и соответствующими входами J-TO регистра в блоке 36 регистров. Если вj-й строке имеется символ д только в о ном i-M столбце, то это означает непосредственную связь между выходами i-ro регистра и соответствующими входами j-ro регистра в блоке А 0000 0000 Код внутреннего состояния ЛПС.с с р-разрядным кодом на выхо блока 36 регистров и является выходным кодом ЛПС. Входом ЛПС язл ется h-разрядный выход блока 21 эл ментов И. В режиме сжатия информации на выход блока 21 элементов И подаются сигналы логического нуля. С приходом сигнала с блока 25 управления все регистры блока 36 регистров устанавливаются в единич ное состояние, что соответствует начальному состоянию Sg ЛПС. В исходном состо ии с блока 25 управления поступают сигналы, которые разрешают (запрещайт) прохождение информации через: блок 3t элементов И и элемент И 33 (блок 30 элементов И и элемент И 32). Блок 37 сумматоров ос ш1ествляет суммирование по модулю m р-разрядного кода, поступающего с выходов блока 36 регистров. 95.20 36 регистров. Если в j-й строке имеется Э (в 2,...,п) символ 5 , то это означает, что входы j-ro : регистра связаны с выходами 6 регистров блока 36 регистров через (0-1) последовательно соединенных h-входных сумматоров по модулю т. Символ (d) в j-й строке в (6) означает наличие (отсутствие) логической связи между выходом блока 21 элементов И и входами j-ro регистра блока 36 регистров. 11апример, при сжатии массива, состоящего из пятиразрядных десятичных чисел (п 5, m 10, h 4) характеристические матрицы А и В имеют вид: или в двоично-кодированном виде: В 0000 0000 0000 Результат указанного суммирования через элемент И 33 и элемент ИЛИ 35 поступает на младший h-разрядный регистр блока 36 регистров. На входы остальных (п-1) регистров блока 36 регистров через блок 31 эле ментов И и блок 34 элементов ИЛИ поступает h (п-1)-разрядный код соответственно с выходов младших (п-1) регистров блока 36 регистров. С приходом управляюще1 о сигнала с блока 25 управления информация, имеющаяся на входах блока 36 регистров, записывается в блок 36 регистров. Тем в блоке 36 регистров осуществляется сдвиг информации на h 1азрядов в сторону старшего п-го регистра, а .в младший первый регистр записывается результат суммирования с выхода блока 37 сумматоров. В результате указанного преобразования информации на выходе блока 36 регистров появляется новый р-раз 21 рядный код, соответствующий следующему cocTOHHtno S ЛПС. Аналитически указанное преобразование информадаи описывается следующим образом: S, ASp. Например, при сжатии массива, состоящего из четьфехразрядных десятичнь Х чисел (п « А, ш 10,h 4) блок 36 регистров содержит четыре четьфехразрядных регистра и значения векторов S0 и S равны Число Sj, (SjM в (7) равно значению на J-M выходе i-ro регистра блока 36 регистров до преобразования (после преобрайования). При подаче с блока 25 управления k управляющих сигналов произой дет k сдвигов информации в блоке 3 регистров, что эквивалентно следую щему преобразованию SK . Лосле определения вектора U(;(t) с блока 25 управления поступает управляющий сигнал, который разрешает прохождение р-разрядного кода из блока 8 регистров через блок 30 элементов И, элемент И 33 и бло 34 элементов ИШ, элемент 35,ИЛИ н входы блока 3& регистров. Одновременно с блока 25 управления поступает управляющий сигнал, который запрещает прохождение информации через блок 31 элементов И и элемен И 33. С приходом управляющего сигнал с блока 25 управления происходит записьуказанной информации в бло 36 регистров, что эквивалентно установке ЛПС в новое состояние. После этого вновь разрешается прохождение информации через блок (7 95 31 элементов И и элемент И 33 и запрещается прохождение информации через блок 30 элементов И и элемент И 32. Тем самым узел 2 формирования вектора подготавливается к работе по определению следующего вектора tt/t).. В режиме восстановления сжатой информации с блока 21 элементов .И подаются h-разрядные наборы вектора U;(t) (i 1,2,...,Z). Блоки 37 сумматоров осуществляют суммирование по модулю m поступившего бора UJ(t) (,...,g) вектора U;(t) с р-разрядным кодом, поступшощим с выходов блока 36 регистров. Результат указанного суммилования через элемент И 33 и элемент. И. 35 поступает на младщий регистр блока 36 регистров. На входы остальных (п-О регистров блока 36 регистров через 31 элементов И и блок 34 зле14ейтов ИЛИ поступает h (п-1)-разрядный код соответственно с выходов младших nfl) регистров блока 36 регистров. С приходом управляняцего сигнала с блока 25 управления имеющаяся информация на входах блока 36 регистров записывается в блок 36 регистров. Если ранее ЛПС находилась в сост тоянии S;.j, тогда, в результате указанного преобразования информации ЛПС .переходитв состояние Sj, что аналитически описывается следующим образом: S,- AS;,, 0В uj(t). (8) В режиме восстановления информации разрешается прохозвдение информации через блок 31 элементов И и элемент 33 и запрещается прохождение информации блок 30 элементов И и элемент И 32. Полученный вектор (8) записьгеается в регистр 12. h-Разрядный блок 37 сумматора по модулю m в прямых кодах работает следующим образом. ; Перед началом работы устройства в регистр 40 заносится h-раэрядный десятичный код числа б 2 - ю, которое служит для коррекции результата суммирования. Сумматоры 38 производят суммирование по правилам двоичной арифметики прямых кодов двух h-разряд23ных двоичных чисел. Сумматоры 39 производят суммирование по правилам двоичной арифметики содержимого регистра 40 и результата суммирования сумматоров 38. При появлении сигналов переноса из старшего одноразрядного сумматора 38 или из старшего одноразрядного сумматора 39 триггера 42 устанавливается в единичное значение и разрешает прохождение информации из сумматоров 39 через элементы И 4 и элементы ИЛИ 45 на выход блока 37 сумматора ло модулю m в прямых кодах При отсутствии сигналов переноса из старших одноразрядных сумматоров 38 и 39 триггер, 42 устанавливается в нулевое состояние и разрешает прохоядение информации иэ сумматоров 38 через элементы. И 44 и элемен ты ИЛИ 45 на выход блока 37 сумматора по модулю m в прямых кодах. Узел 3 формирования вхлодной последовательности работает следующим образом. В k -м 1Щ1сле работы устройства определяется нахождение неизвестной величины U(t) следующего уравненияL U;(t)Sx, k« 1,,..,n. (9) Вектор S поступает от блока 10 регистров, а полученное значение и(t) поступает на вход блока 11 регистров. ,j В k -м цикле работы устройства векторы Si и U{ (t) являются h- k -ра рядными векторами. Структура узла 3 формирования входной последовательности опредеЛ9ется видом матрицы L. По выбранньм характеристическим матрицам А и В (6) матрица L |, согласно (2) имеет вид где l;j , если i+j n 1 , если i+j «n+1 0 , если i+j

Например, при сжатии массива, состоящего из четырехразрядных де.сятичных чисел матрица „ будет |нметь вид

На выходах первых (t-l) блоков 46 по модулю m в прямых кодах сумма торов согласно (12) получаются разряды вектора U;(tX 95 или в двоично-кодированном виде: Решение уравнения (9) сводится к решению следующей системы уравненийЦ Iflj ... Для матрицы L вида (10) решение системы уравнений (11) следующее; Vl .es;,k 1,2,...n Операция вычитания по модулю m заменяемся операцией сложения по модулю m в обратных кйдах чисел. Для получения обратных кодов чисел предназначены формирователи 47 обратного коДа. В первом цикле работы устройства со старшего п-го регистра блока 10.регистров Н-разрядный набор S , который согласно (12) равен набору U(t). Поэтому указанный набор Sj без преобразований поступает на вход блока 11 регистров. . В k -м ( 1с 2,... п) цикле работы устройства со старших 1г регистров блока 10 регистров поступает К| -разрядный набор вектора В итоге на вход блока 11 регистров поступает вектор U;(t), равный и; (t) U,(t). uf (t) Формирователь 47 обратного кода работает следующим образам. Дешифратор 49 преобразует h-разрядиый,двоичный позиционный код набора S в (т-1)-разрядный унитарный код (i 1,..., п) . Шифратор 50 пре образует (т-1)-разрядный унитарный код в h-разрядный двоичньш позицион ный код, который является обратным кодо.м набора. S ,(i 1,.,. п) , Ъ-Разрядный блок 48 сумматора по модулю m в обратных кодах работа следующим образом. Перед началом работы устройства в регистр 55 заносится Ь-разрядный двоичный код числа d 2h - m, ко торое служит для коррекции результа та суммирова:ния. Сумматоры 51 производят суммирование ПС правилам двоичной арифметики обратных кодов двух .рядных двоичных чисел вместе с их знаками, причем сигнал переноса с (h + 1)-го знакового одноразрядного накапливающего двоичного сумматора поступает на вход младшего одноразрядного двоичного сумматора. Поскол ку на входы сумматоров 51 всегда no тупагот числа с противоположными знаками, перед началом суммирования в знаковый сз матор заносится логическая единица. Сумматоры 52 производят суммирование по правилам двоичной арифметгаси содержимого регистра 55 и результата суммирования сумматоров 5 вместе с их знаками, причем сигнал переноса с (п+1)-го знакового одноразрядного накапливающего двоичного сумматора поступает на вход младшего одноразрядного двоичного сумматора. Возникающий в процессе суммирования сигнал переноса со знаковых сумматоров 51 и 52 запоминается в триггере 58. После окончания проце сса сумми рования на выходе элемента ИЛИ 56 устанавливается постоянное значени логического нуля или логической единицы в соответствии со значёния ми на .выходах знаковых сумматоров 51 и 52. Если на выходе элемента ИЛИ 56 имеется значение логического нуля (логической единицы) при нулевом значении на выходе триггера 58, тогда дешифратор 59 разрешает прохождение на выход блока 48 сумматора по модулю m в обратных кодах прямого (обратного) кода результата суммирования в сумматорах 51, Если на выходе элемента ИЛИ 56 имеется значение логического нуля (логической единицы) при единичном значении на выходе триггера 58, тогда дешифратор разрешает прохождение на выход блока 48 сумматора по модулю m в обратных кодах прямого.(обратного) кода результата суммирования в сумматорах 52. Во всех указанных случаях на выход блока 48 суммат.ора по модулю m в обратных кодах поступает прямой код положительного или отрицательного числа без знака. Блок 4 вычитания работает следующим образом. В блоке 4 вычитания операция вычитания по модулю m заменяется операцией сложения по модулю m в обратных кодах чисел. Поскольку с блока 8 регистров поступает положительное уменьшаемое число, поэтому указанное число поступает непосредственно на входы сумматоров 65. Поскольку с узла 2 формирЬвания вектора поступает положительное вычитаемое число, поэтому с помощью формирователей 64 обратного кода получаются обратные коды цифр указанного числа, которое затем поступает на входы сумматоров 65. В итоге на выход блока 4 вычитания поступает прямой код положь.ельного или отрицательного числа без знака. Блок 25 управления работает следзлощнм образом. В исходном состоянии триггеры 91-96 находятся в нулевом состоянии, регистры 87-88 находятся в состоянии 00...00, регистр 89 находится в состоянии 11... 11. При поступлении на управляющий вход 27 сигнала, блок 25 управления начинает работать в режиме сжатия информации. На первом выходе регистра 87 появляется единичный сигнал, который разрешает прохоткдение импульсов от генератора 86 импульсов на вход распределителя 98 импульсов. Распределитель 98 импульсов последовательно формирует управляющие импуль сы. Импульс с третьего выхода распределителя 98 импульсов устанавливает в единичное состояние триггер 91, что приводит к появлению разрешающего сигнала на одном из входоз узла 2 формирования вектора. Пр появлении импульса на шестом выходе распределителя 98 импульсов и каличии сигнала на выходе дешифратора 24 на выходе элемента ИЛИ 76 формиру ется импульс, по которому происходит сдвиг единицы в регистре 87. В результате запрещается поступление импульсов от генератора 86 импульсо на вход распределителя 98 импульсов и разрешается поступление импульсов от генератора 86 импульсов, на вход распределителя 99 импульсов. При отсутствии сигнала с выхода дешифратора 24 распределитель 98 импульсов продолжает работать. Им-; пульс с седьмого выхода распределителя 98 импульсов устанавливает в единичное состояние триггер 92, что щ 1;водит к появлению разрешающего сигнала на входе блока 19 элементов И. Импульс с девятого выхода распределителя 98 импульсов устанавливает в нулевое состояние триггер 92, что приводит к появлению разрешающего сигнала на входе блока 20 элементов И. Импульс с одиннадцатого выхода распределителя 98 импульсов через элемент ИЛИ 76 вызьюает сдвиг единицы в регистре 8 В результате запрещается поступлен е импульсов от генератору 86 импульсов на вход распределителя 98 импульсов и разрешается поступление импульсов от генератора 86 импульсов на вход распределителя 99 импульсов. Распределитель 99 импульсов работает в кольцевом режиме. Импуль со второго выхода распределителя 99 импульсов в каждом цикле работы при водит к сдвигу информации в регистрах 88 и 89. Изменение состояний ре гистров 88 и 89 происходит в том порядке, как приведено соответственно на фиг. 10 и на фиг. 11. Импульс с четвертого вькода распредел 7еля 99 импульсов в каждом цикле работы увеличивает содержимое счетчика 90 на единицу. При появлении импульса на шестом выходе распределителя 99 импульсов и наличии сигнала с выхода дешифратора 24 на выходе элемента ИЛИ 76 формируется импульс, по которому происходит сдвиг единицы в регистре 87. В результате запрещается поступление импульсов от генератора 86 импульсов на вход распределителя 99 импульсов и разрешается поступление импульсов от генератора 86 импульсов на вход распределителя 100 импульсов. Распределитель 100 импульсов работает в кольцевом режиме. Импульс с первого выхода распределителя 100 импульсов устанавливает триггер 92 в единичное состояние. Импульс с третьего выхода распределителя 100 . импульсов в каждом цикле работы уменьшает содержимое счетчика 90 на единицу. При достижении нулевого состояния счетчика 90 импульс переноса с его выхода через элемент ИЛИ 76 вызьтает сдвиг единицы в регистре 87. В результате запрещается поступление импульсов от генератора 86 импульсов на вход распределителя 100 импульсов и разрешается поступление импульсов от генератора 86 импульсов на вход распределителя 101 импульсов. Распределитель 101 импульсов последовательно формирует управляющ е импульсы. Импульс с первого ;выхода распределителя 101 импульсов устанавливает в. нулевое состояние триггер 92, Импульс с третьего выхоца распределителя 101 импульсов устанавливает в нулевое состояние триг- гер 91, что приводит к появлению разрешающего сигнала на входе узла 2 формирования вектора. Импульс с пятого выхода распределителя lOt импульсов через элемент ИЛИ 76 вызывает сдвиг единицы в регистре 87. В результате запрещается поступле ние импульсов от генератора 86 импульсов на вход распределителя 101 импульсов. На этом заканчивается работа устройства по определению вектора Uj(t) и записи его в блок 1 памяти (i 1,2,..., Z). При поступлении на управляющий вход 27 очередного управлян щрго сигнала блок 25 управления снова начинает формировать упрап11ян.пцче импульсы, необходимые для о1111едглс29ния вектора 4j,(t) и записи его в блок 1 памяти (i 2,3,...,Z). При поступлении на управляющий вход 28 управлянщего сигнала блок 25 управления начинает работать в жиме восстановления информации. В этом случае триггер 93 устанавлива ется в единичное состояние и разрешает поступление импульсов от генератора 86 импульсов на вход распределителя- 102 импульсов. Распределитель Т02 импульсов последовательно формирует управляю щие импульсы. Импульс с второго вых да распределителя 102 импульсов устанавливает в единичное состояние триггер 91. Импульс с третьего выхода распределителя 102 импульсов устанавливает триггер 93 в нулевое состояние, а триггер 94 в единичное В результате запрещается поступление импульсов от генератора 86 импульсов на вход распределителя Т02 импульсов и раз решается постзшление импульсов от генератора 86импульсов на вход распределителя t03 импульсов. Распределитель 103 импульсов работает в кольцевом режиме. В первом цикле работы распределителя 103 импульсов триггер 96 запрещает постухШение импульса с пятого выхода распределителя 103 импульсо на вход блока 18 элементов И. В по ледующих даклах работы после появления импульса на третьем выходе распределителя 103 импульсов может появиться импульс, с блока 7, сравнения, который установит в единичное состояние триггеры 95 и 96, В результате появится разрешающий сигнал на входе блока 21 элементов И и будет разрешено прохождени импульса с пятого вьпсода распределителя 103 импульсов на вход блока 18 элементов и. Импульс с седьмого 5 выхода распределителя 103 импульсов в конце каждого цикла уртанавливает триггеры 95 и 96 . нулевое состояние. Распределитель 103 импульсов работает до тех пор, пока не появится сигнал с выхода блока 6 сравнения, который установит триггер 94 в нулевое состояние. В результате запрещается поступление импульсов от генератора 86 импульсов на вход распределителя 103 имдульсов. Предлагаемое устройство имеет следующие преимущества по сравнению с известными устройствами. На сжимаемую дискретную информацию не накладывается никаких ограничений в смысле наличия определенных закономерностей в информационном массиве, поэтому достигается универсальный характер сжатия информации. Коэффициент 2 сжатия информации не зависит от наличия определенных закономерностей в сжимаемой информации и находится в следующих пределах 1 и 1 п. Макйимальная эффективность сжатия информации достигается для массивов информации с отсутствием определенных закономерностей в массивах. В предлагаемом .устройстве можно сяотмать дискретную информацию, представленную в произвольном целочисленном алфавите х 0,1,2,...т-1j, где m - целое положительное число. Перед вводом в устройство некторы входной информации должны быть предварительно переведены в двоичнокодированное представление.. Благодаря этому в предла.аемом устройстве использзлются только двузначные элементы и узлы, что повышает технологичность изготовления устройства.

« NT

NT

Ъ

Ч

SJ

N

ГЖ

-а

Nh

тж

у /k

&

/Г/Г

:: Sh

«о

/ /

б о

bi

JQГЖ

х

i л.

с«

Nj Sh

А /1

Т

x

/ /.

00

50 NJN

Т

ts.

ч Мч

ТГ

«ъ

NT

1149295

Ч

«

NT

Nh

I t

ts.

N.

г

хг

ж

Nf

Sf

Ж

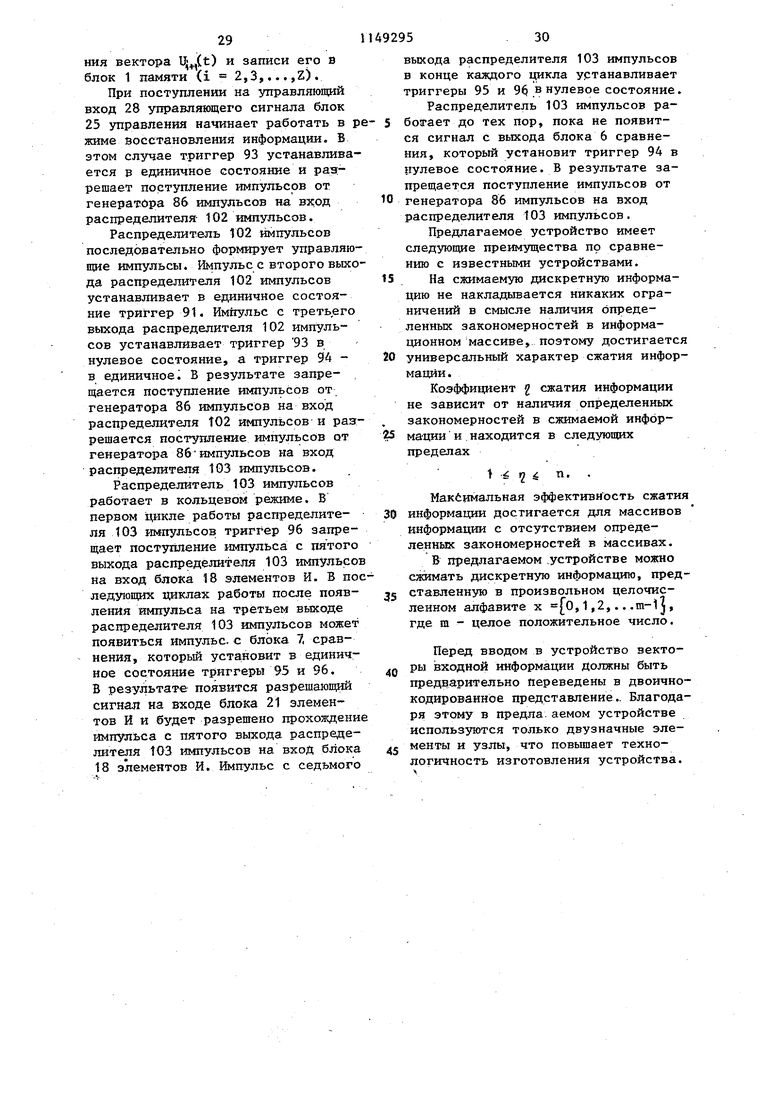

49

50

Фиг. 5

Фиг.7

фиг, 8

Фиг, //

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 431532, кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сжатия и восстановления информации | 1980 |

|

SU934523A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1985-04-07—Публикация

1983-11-28—Подача