МиА

4:

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный корректор межсимвольной интерференции | 1987 |

|

SU1540009A1 |

| Адаптивный корректор | 1989 |

|

SU1688418A1 |

| Двухканальное устройство приема сигналов данных | 1986 |

|

SU1415451A1 |

| Адаптивный корректор | 1987 |

|

SU1417197A1 |

| Устройство преобразования сигналов для передачи данных по первичному сетевому тракту | 1989 |

|

SU1739503A1 |

| Устройство адаптивного приема дискретных сигналов | 1982 |

|

SU1113891A1 |

| Адаптивный корректор многоканального сигнала с ортогональными составляющими | 1990 |

|

SU1807571A1 |

| Адаптивный корректор сигнала | 1987 |

|

SU1432730A1 |

| Устройство для адаптивного приема цифровых однополосных сигналов | 1989 |

|

SU1663776A2 |

| Устройство для приема дискретных сигналов | 1986 |

|

SU1374444A1 |

Изобретение относится к электро и областям, связанным с приемом ioдyлиpoвaнныx сигналов данных. Цель изобретения - повьпйение точности коррекции при одновременном повьшении быстродействия устр-ва за счет,передачи регуляторов отводов. Цель достигается введением в устр-во блоков 8, 9 памяти весовых коэффициентов, умножителей 11, 12 и блока 14 формирования адреса и организацией новых связей,. Если качество коррекции неудовлетворительное (режим настройки, смена канала и т.п.), на выходе детектора 10 качества формируется сигнал W(n) (например W(n) 1), по которому в умножителях П, 12 осуществляется умножение на постоянную адаптации S При этом .0 3, . Т.обр., осуществляется ускорение сходимости процесса адаптации. Для уменьшения времени сходимости процесса коррекции целе сообразно осуществлять регулировку не всех отводов корректора, а только тех, которые располагаются вблизи основного отвода, и только по истече НИИ времени осуществлять .регулировку всех отводов корректора. Изменение числа адаптируемых регуляторов обеспечивает ускорение процесса настройки и увеличение допустимой величины исходных искажений частотных х-к канала связи 2 ил. о С

О о:

114

Изобретение относится к электросвязи и областям, связанным с прие мом модулированных сигналов данных, и предназначено для коррекции межсимвольной интерференции (МСИ) принимаемого сигнала, обусловленной неидеаль ностью частотных характеристик широкополосных каналов связи

Целью изобретения является повышение точности коррекции при одновременном повышении быстродействия устройства за счет уменьшения числа :арифметических операций при вычислении коэффициентов передачи регуляторов отводов о

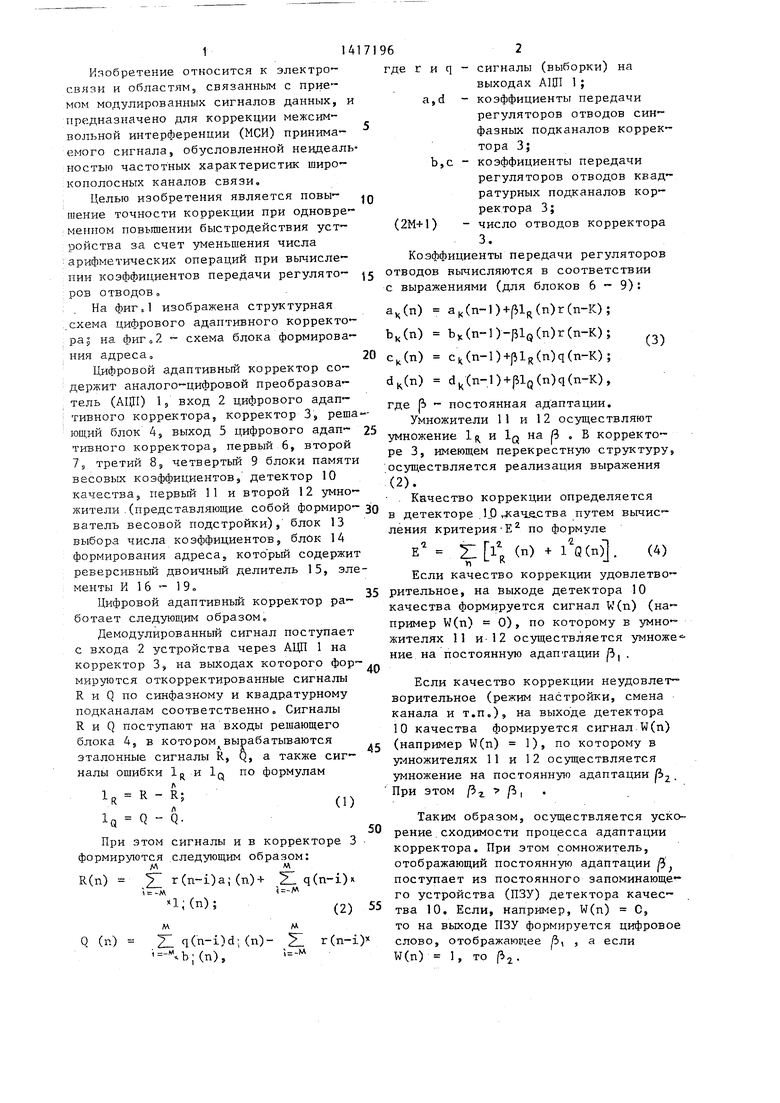

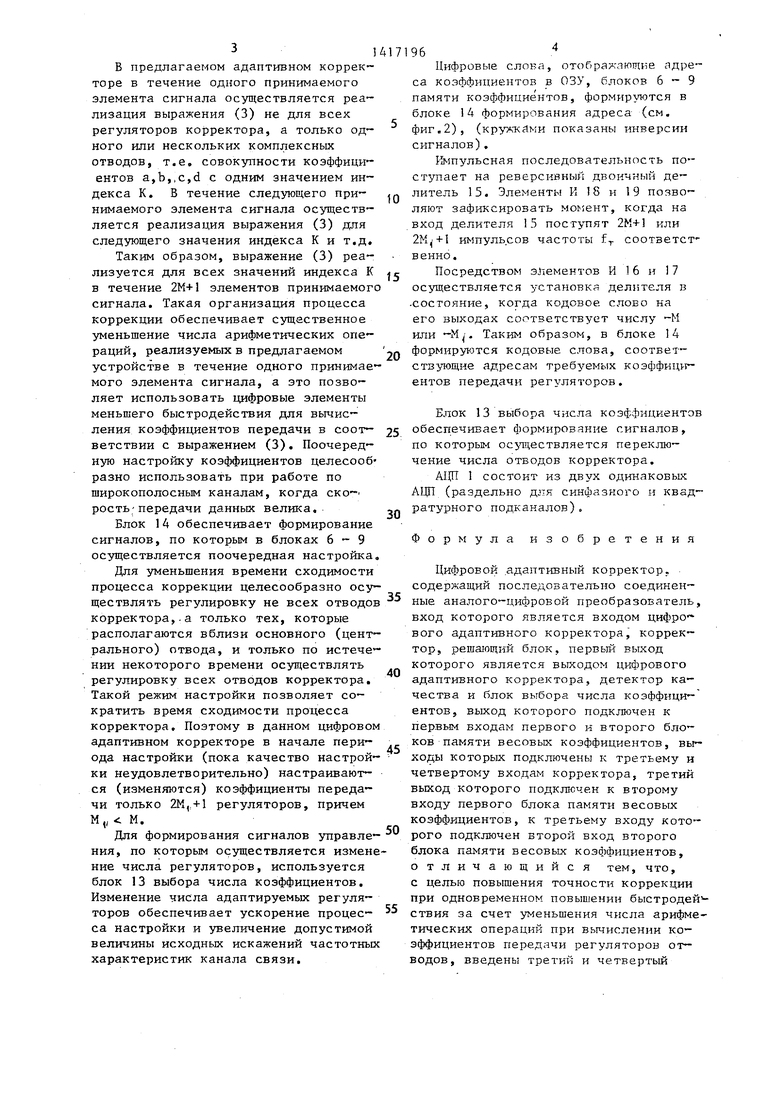

На фиг,1 изображена структурная схема цифрового адаптивного корректора j на фиг,2 - схема блока формирования адреса,

Цифровой адаптивный корректор содержит аналого-цифровой преобразователь (АЩ1) 1 э вход 2 цифрового адаптивного корректора, корректор 3, реша ющий блок 4, выход 5 цифрового адап- тивного корректора, первый 6, второй 7; третий 8j четвертый 9 блоки памяти весовых коэффициентов, детектор 10 качестваэ первый 11 и второй 12 умножители .(представляющие собой формиро- ватель весовой подстройки), блок 13 выбора числа коэффициентов, блок 14 формирования адресаS кото рый содержит реверсивньй двоичный делитель 15, элементы И 1 6 1 9

Цифровой адаптивный корректор работает следующим образом.

Демодулированный сигнал поступает с входа 2 устройства через АЦП 1 на корректор 3, на выходах которого фор мируются откорректированные сигналы R и Q по синфазному и квадратурному подканалам соответственно. Сигналы R и Q поступают на входы решающего блока 4; в котором вырабатываются эталонные сигналы R, Q, а также сиг-

1ц и л

Rj

Q.

IQ no формулам

(1)

При этом сигналы и в корректоре 3

ются .следующим образом:

м

Z

1 -л

r(n-i)a; (п) + 1;(п);

(-АЛ

q(n-i)n

21 q(n-i)d: (n)- (n).

м

(2) rCn-i)

962

где г и q - сигналы (выборки) на

выходах А1Щ 1; a,d - коэффициенты передачи

регуляторов отводов синфазных подканалов корректора 3; Ь,с - коэффициенты передачи

регуляторов отводов квадратурных подканалов корректора 3; (2М+1) - число отводов корректора

Коэффициенты передачи регуляторов отводов вычисляются в соответствии с выражениями (для блоков 6 - 9):

а(п) a(n-l)+pl(n)r(n-K); Ъ(п) b(n-l)-plQ(n)r(n-K); с(п) c,(n-l)+plR(n)q(n-K); d(n) d(n-l)+plQ(n)q(n-K),

Где |i - постоянная адаптации.

Умножители 11 и 12 осуществляют умножение 1д и IQ на /3 , В корректоре 3, имеющем перекрестную структуру, осуществляется реализация выражения (2).

. Качество коррекции определяется в детекторе . т сачас ТВ а путем вычисления критерия-Е по формуле

Е Ц К (п) + (п) . (4)

у, - кл

Если качество коррекции удовлетворительное, на выходе детектора 10 качества формируется сигнал W(n) (например W(n) 0), по которому в умножителях 11 и-12 осуществляется умноже - ние на постоянную адаптации р,.

Если качество коррекции неудовлет™ ворительное (режим настройки, смена канала и т.п.) на выходе детектора 10 качества формируется сигнал W(n) (например W(n) 1), по которому в уг-1ножителях 11 и 12 осуществляется умножение на постоянную адаптации ft. При этом /3 I .

Таким образом, осуществляется ускорение , сходимости процесса адаптации корректора. При этом сомножитель, отображающий постоянную адаптации /3 поступает из постоянного запоминающе го устройства (ПЗУ) детектора качества 10. Если, например, W(n) С, то на выходе ПЗУ формируется цифровое слово, отображающее , , а если W(n) 1, то .

3

В предлагаемом адаптивном корректоре в течение одного принимаемого элемента сигнала ос тцествляется реа лизация выражения (3) не для всех регуляторов корректора, а только одного или нескольких комплексных отводов, т.е. совокупности коэффициентов a,b,,c,d с одним значением индекса К. В течение следующего при- нимаемого элемента сигнала осуществляется реализация выражения (3) для следующего значения индекса К и т.д.

Таким образом, выражение (3) реализуется для всех значений индекса К в течение 2М+1 элементов принимаемого сигнала. Такая организация процесса коррекции обеспечивает существенное уменьшение числа арифметических операций, реализуемых в предлагаемом устройстве в течение одного принимае мого элемента сигнала, а это позволяет использовать цифровые элементы меньшего быстродействия для вычисления коэффициентов передачи в соот- ветствии с выражением (3). Поочередную настройку коэффициентов целесообразно использовать при работе по широкополосным каналам, когда рость; передачи данных велика.

Блок 14 обеспечивает формирование сигналов, по которым в блоках 6-9 осуществляется поочередная настройка

Для уменьшения времени сходимости процесса коррекции целесообразно осу ществлять регулировку не всех отводов корректора,.а только тех, которые располагаются вблизи основного (центрального) отвода, и только по истечении некоторого времени осуществлять регулировку всех отводов корректора. Такой режим настройки позволяет сократить время сходимости процесса корректора. Поэтому в данном цифровом адаптивном корректоре в начале периода настройки (пока качество настройки неудовлетворительно) настраиваются (изменяются) коэффициенты передачи только 2М,+1 регуляторов, причем .

Для формирования сигналов управле- ния, по которым осуществляется изменение числа регуляторов, используется блок 13 выбора числа коэффициентов. Изменение числа адаптируемых регуляторов обеспечивает ускорение цроцес- са настройки и увеличение допустимой величины исходных искажений частотных характеристик канала связи.

Q

Q 5 «

5

0

5

96

Цифровые слова, отображающие адреса коэффициентов в ОЗУ, блоков 6-9 памяти коэффициентов, формируются в блоке 14 формирования адреса (см. фиг.2), (кружками показаны инверсии сигналов).

Импульсная последовательность поступает на реверсивный двоичный делитель 15. Элементы И 18 и 19 позволяют зафиксировать , когда на вход делителя 15 поступят 2М+1 или импульсов частоты f соответственно.

Посредством элементов И 16 и 17 осуществляется установка делителя в .состояние, когда кодовое слово на его выходах соответствует числу -М или . Таким образом, в блоке 14 формирук тся кодовые слова, соответствующие адресам требуемых коэффициентов передачи регуляторов.

Блок 13 выбора числа коэффициентов обеспечивает формирование сигналов, по которым осзпдествляется переключение числа отводов корректора.

А1Щ 1 состоит из двух одинаковых АЦП (раздельно для синфазного и квадратурного подканалов),

Формула изобретения

Цифровой адаптивный корректор, содержащий последовательно соединенные аналого-цифровой преобразователь, вход которого является входом цифро вого адаптивного корректора, корректор, решающий блок, первый выход которого является выходом цифрового адаптивного корректора, детектор качества и блок выбора числа коэффициентов, выход которого подключен к первым входам первого и второго блоков памяти весовых коэффициентов, выходы которых подключены к третьему и четвертому входам корректора, третий выход которого подключен к второму входу первого блока памяти весовых коэффициентов, к третьему входу которого подключен второй вход второго блока памяти весовых коэффициентов, отличающийся тем, что, с целью повышения точности коррекции при одновременном повышении быстродей - ствия за счет уменьшения числа арифметических операций при вычислении коэффициентов передачи регуляторов отводов, введены третий и четвертый

51А171

блоки памяти весовых коэффициентов, к первым входам которых подключен вы- в ход блока выбора числа коэффициентов, , первый и второй умножители, выходы которых подключены соответственно к третьему и второму входам первого и второго блоков памяти весовых коэффициентов к к второму и третьему входам третьего и четвертого блоков па- д мяти весовых коэффициентов, блок формирования адреса, к входу которого и к управляющим входам умножителей подключен выход детектора качества.

Г

966

адресный выход блока формирования адреса подключен к четвертым входам первого и четвертого блоков памяти весовых коэффициентов и к третьим входам второго и третьего блоков памяти весовых коэффициентов, при этом к четвертым входам второго и третьего блоков памяти весовых коэффициентов подключен четвертый выход корректора, к пятому и шестому входам которого подключены соответственно вькоды третьего и четвертого ков памяти весовых коэффициентов.

| Патент США IP 4180705, кл | |||

| Способ получения кодеина | 1922 |

|

SU178A1 |

Авторы

Даты

1988-08-15—Публикация

1986-12-10—Подача