1

со

ND Ч

СО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления дискретного преобразования Фурье | 1989 |

|

SU1645967A1 |

| Адаптивный корректор многоканального сигнала с ортогональными составляющими | 1990 |

|

SU1807571A1 |

| Устройство для ассоциативного сжатия информации | 1983 |

|

SU1120390A1 |

| Устройство для цифровой обработки сигналов | 1989 |

|

SU1652981A1 |

| Цифровой фильтр | 1988 |

|

SU1566471A1 |

| Система передачи данных | 1989 |

|

SU1728976A2 |

| Устройство быстрого преобразования сигналов по Уолшу с упорядочением по Адамару | 1990 |

|

SU1784996A1 |

| УСТРОЙСТВО ДЛЯ НАСТРОЙКИ КОРРЕКТОРА МЕЖСИМВОЛЬНОЙ ИНТЕРФЕРЕНЦИИ | 1991 |

|

RU2034404C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2549360C1 |

| Устройство для контроля распределения ресурсов | 1989 |

|

SU1702372A1 |

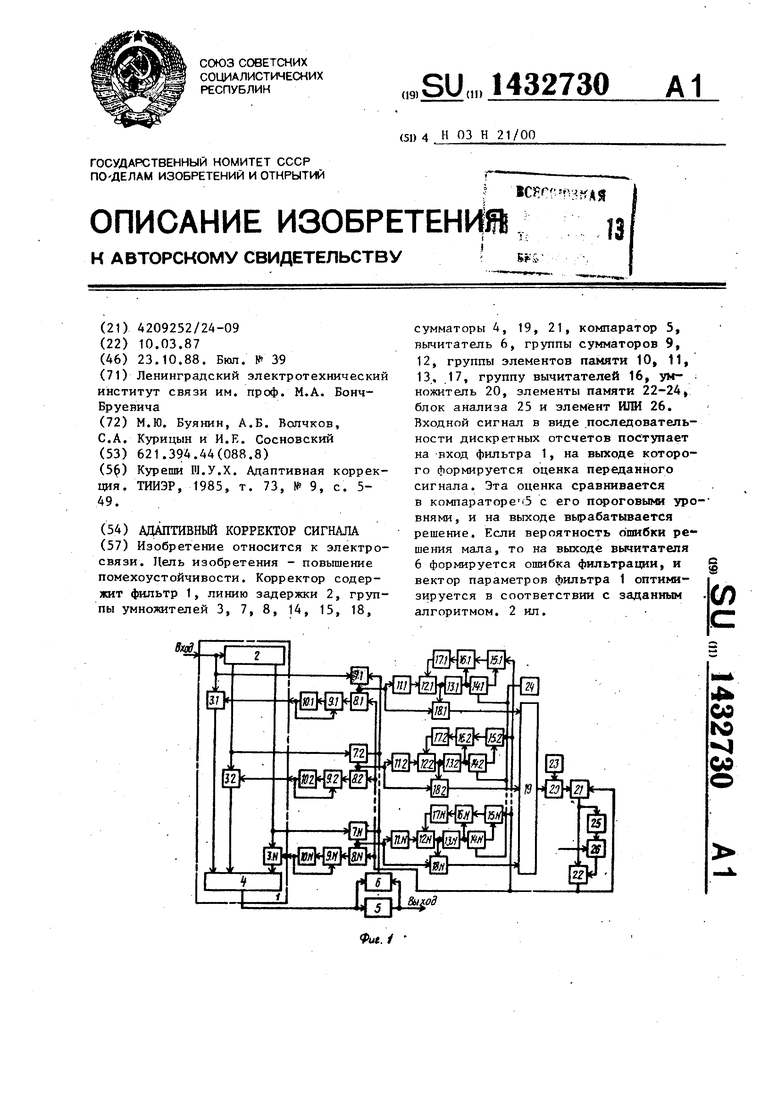

Изобретение относится к электросвязи. Цель изобретения - повьпиение помехоустойчивости. Корректор содержит фильтр 1, линию задержки 2, группы умножителей 3, 7, 8, 14, 15, 18, сумматоры 4, 19, 21, компаратор 5, вычитатель 6, группы сумматоров 9, 12,группы элементов памяти 10 11, 13,17, группу вычитателей 16, ум- ножитель 20, элементы памяти 22-24, блок анализа 25 и элем ент ШШ 26. Входной сигнал в виде последовательности дискретных отсчетов поступает на вход фильтра 1, на выходе которого формируется оценка переданного сигнала. Эта оценка сравнивается в компараторе (5 с его пороговыми уро- внями, и на выходе вырабатывается решение. Если вероятность о шибки шения мала, то на выходе вычитателя 6 формируется ошибка фильтрации, и вектор параметров фильтра 1 оптимизируется в соответствии с заданным алгоритмом. 2 ил.. i (Л

««./

I Изобретение относится к электро- 1 связи и может быть использовано в системах передачи данных для коррекции линейных искажений сигналов.

Цель изобретения - повышение помехоустойчивости адаптивного корректора сигнала. .

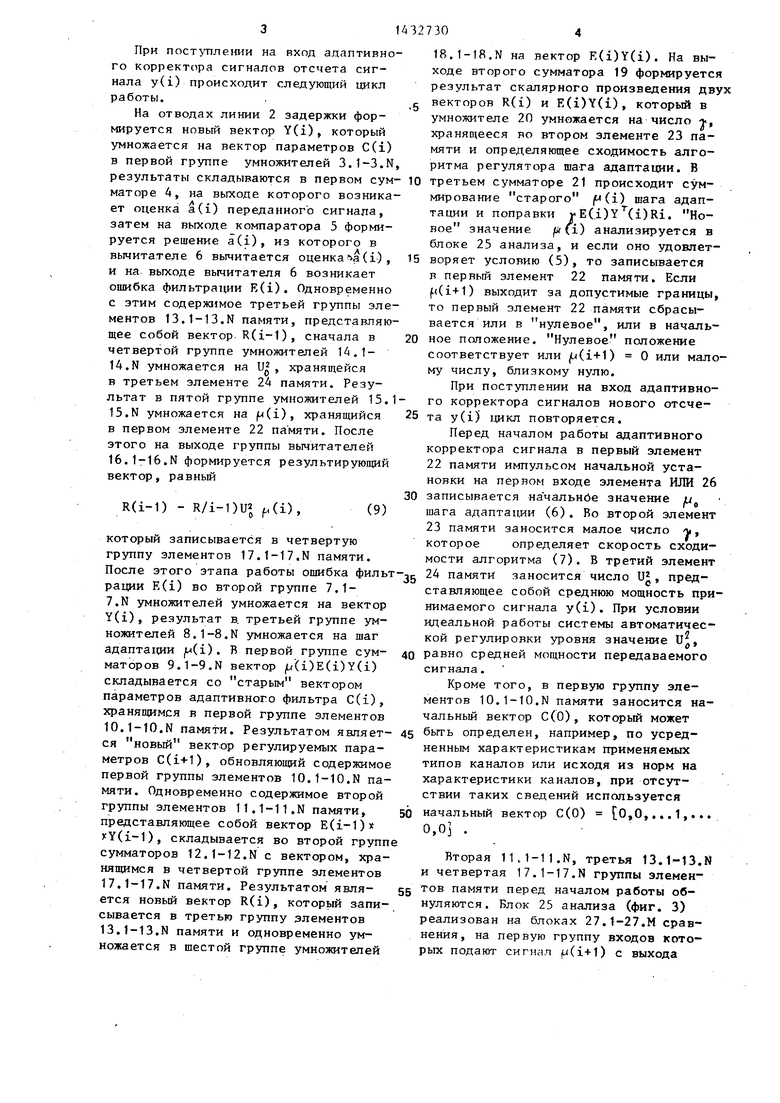

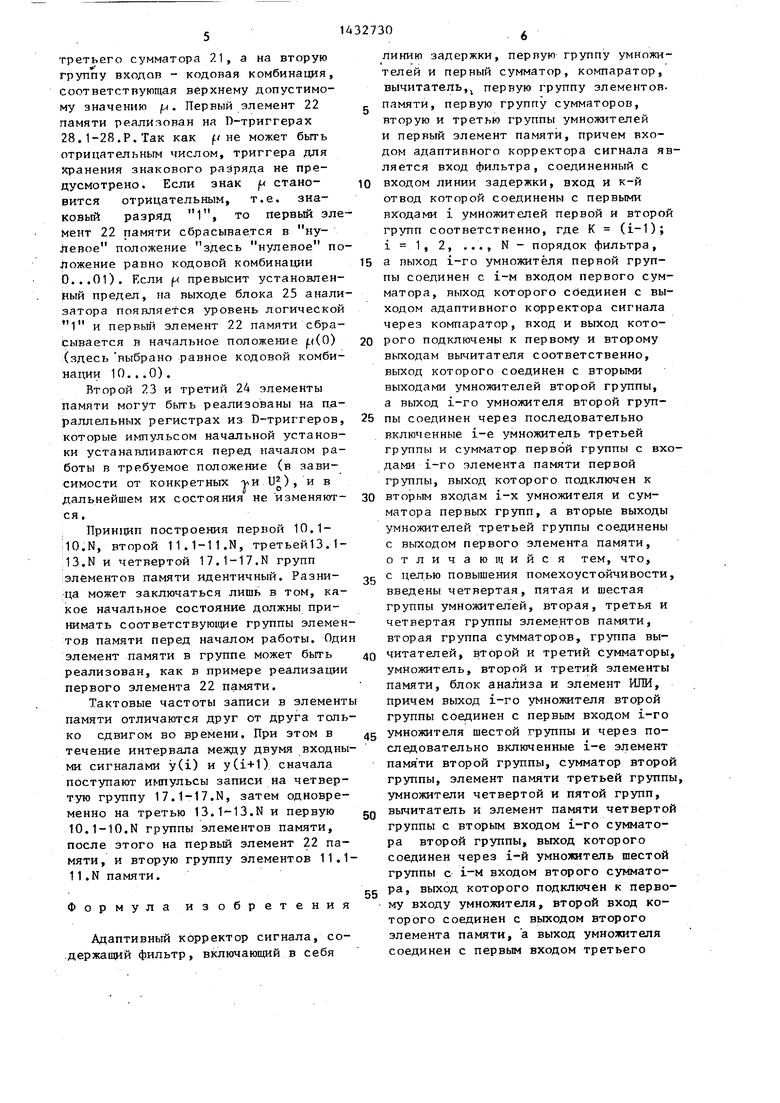

На фиг, 1 приведена структурная схема адаптивного корректора сигнала; i на фиг. 2 - блок анализа. I Адаптивный корректор сигналов I содержит фильтр 1, линию 2 задержки, I первую группу умножителей 3.1-3.N, I первый сумматор 4, компаратор 5, вы- i читатель 6, вторую 7.1-7.N и третью I 8.1-8.N группы умножителей, первую ; группу сумматоров 9.1-9.N, первую ; 10.1-10.N и вторую 11.1-11.N группы ; элементов памяти , вторую группу сум- : маторов. 12. 1-12.N, третью группу элементов 13.1-13.N памяти, четвертую 14.1-14.N и пятую 15.1-15.N группы : умножителей, группу вычитателей 16.1- ; 16.N, четвертую группу элементов

21, первый 22, второй 23 и третий 24 : элементы памяти, блок 25 анализа и элемент ИЛИ 26.

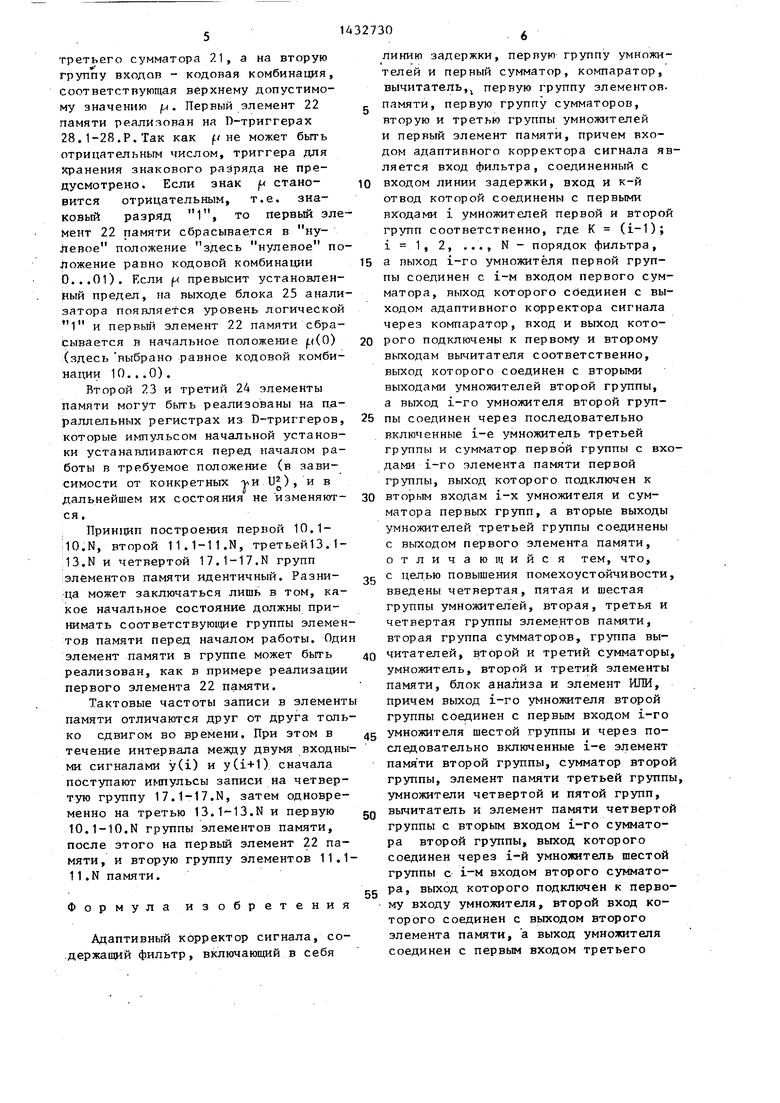

I Блок 25 анализа содержит блоки ; 27.1-27.М сравнения. Первый элемент : памяти содержит Г)-триггеры 28.1-28.Р и элементы ИЛИ 29.1-29.P-2. I Адаптивный корректор сигнала рабо- i тает следующим образом.

Входной сигнал в виде последовательности дискретных отсчетов y(i) поступает на вход фильтра 1. Совокуп- ность сигналов на входе и выходах линии 2 задержки образуют вектор Y(i). С выхода и отводов линии 2 задержки через первую группу умножителей 3.1- 3.N сигналы поступают на входы первого сумматора 4. На вторые входы первой группы умножителей 3.1-3.N подаются сигналы с первой группы элементов 10.1-10,N памяти, совокупность которых образует вектор C(i) регулируемых параметров адаптивного коррек- тора сигнала. На выходе первого сум- матоЬа 4 формируется оценка переданного сигнала (а)

Ш) (i)

(1)

В компараторе 5 оценка a(i) сравнивается с пороговыми уровнями и на

выходе вырабатывается решение a(i). Если вероятность ошибки мала.

то можно считать, что

5(1) а (i).

(2)

0

г 5

.Q

0

5

0

Тогда на выходе вычитателя 6 формируется ошибка фильтрации

E(i) a(i) - c (i).Y(i).

(3)

Вектор параметров фильтра 1 C(i) оптимизируется в соответствии с алгоритмом

C(i-H) C(i)+ (i)E(i)Y(i) . (4)

Произведение E(i)Y(i) вьмисляется во второй группе умножителей 7.1-7.N, затем результат умножается на шаг адаптации (i) в третьей группе умножителей 8,1-8.N, (j(i) хранится в первом элементе 22 памяти. Он определяет скорость сходимости алгоритма (4) и остаточный шум адаптации. .ji(i) должно находиться в определ§11ных границах

О 4 р 1/U4N+1)(5)

Для предотвращения выхода (i) из этих границ введен блок 25 анализа, в котором |a(it1) сравнивается с определенным опорным значением. Если fi (i+1) меньше его, то оно записывается в пер- 5 вый элемент 22 памяти, если больше, то первый элемент 22 памяти через вход сброса сбрасывается в начальное положение |L(0). Опорное значение в блоке 25 анализа целесообразно выбрать равным f(0). При f(i+1) меньше нуля первый элемент 22 памяти сбрасывается в нулевое положение.

Перед началом работы шаг адаптации (U (0) устанавливается равным

. (jt(o) I/UV(N+I),(6)

а дальнейшее его изменение происходит с помощью автоматического регулятора шага адаптации. Регулятор шага адаптации работает в соответствии с алгоритмом

(i-i-1) p(i)+YE(i))R(i) (7)

55 R(i) l-p/i)U| l-R(i-1)(i-1)Yri-1)

(8)

где

Ri

dC(i)

При пост тлении на вход адаптивного корректора сигналов отсчета сигнала у(i) происходит следующий цикл работы..

На отводах линии 2 задержки формируется новый вектор Y(i), который умножается на вектор параметров C(i) в первой группе умножителей 3.1-3.N результаты складываются в первом сум- маторе 4, на выходе которого возникает оценка a(i) переданного сигнала, затем на выходе компаратора 5 формируется решение a(i), из которого в вычитателе 6 вычитается оценка а(1), и на выходе вычитателя 6 возникает ошибка фильтрации R(i). Одновременно с этим содержимое третьей группы элементов 13.1-13.N памяти, представляющее собой вектор R(i-1), сначала в четвертой группе умножителей 14.1- 14.N умножается на U, хранящейся в третьем элементе 24 памяти. Результат в пятой группе умножителей 15. 15.N умножается на fx(i), хранящийся в первом элементе 22 памяти. После этого на выходе группы вычитателей 16.1-16.N формируется результирующий вектор, равный

R(i-1) - R/i-1)U2 p(i),(9)

который записывается в четвертую группу элементов 17.1-17.N памяти. После этого этапа работы ошибка фильт рации E(i) во второй группе 7.1- 7.N умножителей умножается на вектор Y(i) , результат в. третьей группе умножителей 8.1-8.N умножается на шаг адаптации w(i). В первой группе сум- маторов 9.1-9.N вектор (i)E(i)Y(i) складывается со старым вектором параметров адаптивного фильтра C(i), хранящимся в первой группе элементов 10.1-10.N памяти. Результатом являет- ся новьй вектор регулируемых параметров C(i-«-1), обновляющий содержимое первой группы элементов 10.1-10.N памяти. Одновременно содержимое второй группы элементов 11.1-11.N памяти, представляющее собой вектор E(i-1)x Y(i-l), складывается во второй групп сумматоров 12.1-12.N с вектором, хранящимся в четвертой группе элементов 17.1-17.N памяти. Результатом явля- ется новый вектор R(i), который записывается в третью группу элементов 13.1-13.N памяти и одновременно умножается в шестой группе умножителей

При поступлении на вход адаптивного корректора сигналов нового отсчета y(i) 1ДИКЛ повторяется.

Перед началом работы адаптивного корректора сигнала в первый элемент

22памяти импульсом начальной установки на первом входе элемента ИЛИ 26 записывается на чальнбе значение fj шага адаптации (6). Во второй элемент

23памяти заносится малое число -ji, которое определяет скорость сходимости алгоритма (7). В третий элемент

24памяти заносится число U , представляющее собой среднюю мощность принимаемого сигнала y(i). При условии идеальной работы системы автоматической регулировки уровня значение U, равно средней мощности передаваемого сигнала.

Кроме того, в первую группу элементов 10.1-10.N памяти заносится начальный вектор С(0), который может бьп ь определен, например, по усредненным характеристикам применяемых типов каналов или исходя из норм на характеристики каналов, при отсутствии таких сведений используется начальный вектор С(0) 0,0,...1,... 0,0 .

Вторая 11.1-11.N, третья 13,1-13.N и четвертая 17.1-17.N группы элементов памяти перед началом работы обнуляются. Блок 25 анализа (фиг. 3) реализован на блоках 27.1-27.М сравнения, на первую группу входов которых подают сигнал iu(i+1) с выхода

третьего сумматора 21, а на вторую Группу входов - кодовая комбинация. Соответствующая верхнему допустимому значению (. Первый элемент 22 памяти реализован на П-триггерах 28.1-28.Р. Так как f/не может бьп ь отрицательным числом, триггера для 5фанения знакового разряда не предусмотрено. Если знак |U становится отрицательным, т.е. знаковый разряд 1, то первый элемент 22 памяти сбрасывается в нулевое положение здесь нулевое положение равно кодовой комбинации D...01). Если fx превысит установленный предел, на выходе блока 25 анализатора появляется уровень логической 1 и первый элемент 22 памяти сбрасывается в начальное положение f.((0) (здесь выбрано равное кодовой комбинации 10...0).

Второй 23 и третий 24 элементы памяти могут бьп ь реализованы на п.а- раллельных регистрах из D-триггеров, которые импульсом начальной установки устанавливаются перед началом работы в требуемое положение (в зависимости от конкретных -VH Up, и в дальнейшем их состояния не изменяются.

Принцип построения первой 10.1- ilO.N, второй 11.1-11.N, третьей13.1- 13.N и четвертой 17.1-17.N групп :элементов памяти идентичный. Разница может заключаться лишь в том, какое начальное состояние должны принимать соответствующие группы элементов памяти перед началом работы. Оди элемент памяти в группе может быть реализован, как в примере реализации первого элемента 22 памяти.

Тактовые частоты записи в элемент памяти отличаются друг от друга только сдвигом во времени. При этом в течение интервала между двумя входными сигналами y(i) и y(i+1) сначала поступают импульсы записи на четвертую группу 17.1-17.N, затем одновременно на третью 13.1-13.N и первую 10.1-10.N группы элементов памяти, после этого на первый элемент 22 памяти, и вторую группу элементов 11.1 11.N памяти.

Формула изобретения

Адаптивный корректор сигнала, со- .держащий фильтр, включающий в себя

5

0

5

0

5

0

5

0

5

линию задержки, первую группу умножителей и первый сумматор, компаратор, вычитатель, первую группу элементов, памяти, первую группу сумматоров, вторую и третью группы умножителей и первый элемент памяти, причем входом адаптивного корректора сигнала является вход фильтра, соединенный с входом линии задержки, вход и к-й отвод которой соединены с первыми входами i умножителей первой и второй групп соответственно, где К (i-1); i 1, 2, ..., N- порядок фильтра, а выход i-ro умножителя первой группы соединен с i-M входом первого сумматора, выход которого соединен с выходом адаптивного корректора сигнала через компаратор, вход и выход которого подключены к первому и второму выходам вычитателя соответственно, выход которого соединен с вторыми выходами умножителей второй группы, а выход i-ro умножителя второй группы соединен через последовательно включенные i-e умножитель третьей группы и сумматор первой группы с входами i-ro элемента памяти первой группы, выход которого подключен к вторым входам i-x умножителя и сумматора первых групп, а вторые выходы умножителей третьей группы соединены с выходом первого элемента памяти, отличающийся тем, что, с целью повышения помехоустойчивости, введены четвертая, пятая и шестая группы умножителей, вторая, третья и четвертая группы элементов памяти, вторая группа сумматоров, группа вы- читателей, второй и третий сумматоры, умножитель, второй и третий элементы памяти, блок анализа и элемент ИЛИ, причем выход i-ro умножителя второй группы соединен с первым входом i-ro умножителя шестой группы и через последовательно включенные i-e элемент памя ти второй группы, сумматор второй группы, элемент памяти третьей группы, умножители четвертой и пятой групп, вычитатель и элемент памяти четвертой группы с вторым входом i-ro сумматора второй группы, выход которого соединен через i-й умножитель шестой группы с i-M входом второго сумматора, выход которого подключен к первому входу умножителя, второй вход которого соединен с выходом второго элемента памяти, а выход умножителя соединен с первым входом третьего

сумматора, выход которого соединен с информационным входом первого элемента памяти, вход сброса которого соединен с выходом элемента ИЛИ, первый вход которого является входом начальной установки первого элемента памяти, а второй вход элемента ИЛИ соединен через блок анализа с выхо,т

дом третьего сумматора, второй вход i которого соединен с выходами первого элемента памяти и вторыми входами умножителей пятой группы, выход третье : го элемента памяти соединен с вторыми входами умножителей четвертой группы, а выход i-ro элемента памяти подключен к второму входу i-ro вычитателя.

| Куреши Ш.У.Х | |||

| Адаптивная коррекция | |||

| ТИИЭР, 1985, т | |||

| Способ подготовки рафинадного сахара к высушиванию | 0 |

|

SU73A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-10-23—Публикация

1987-03-10—Подача