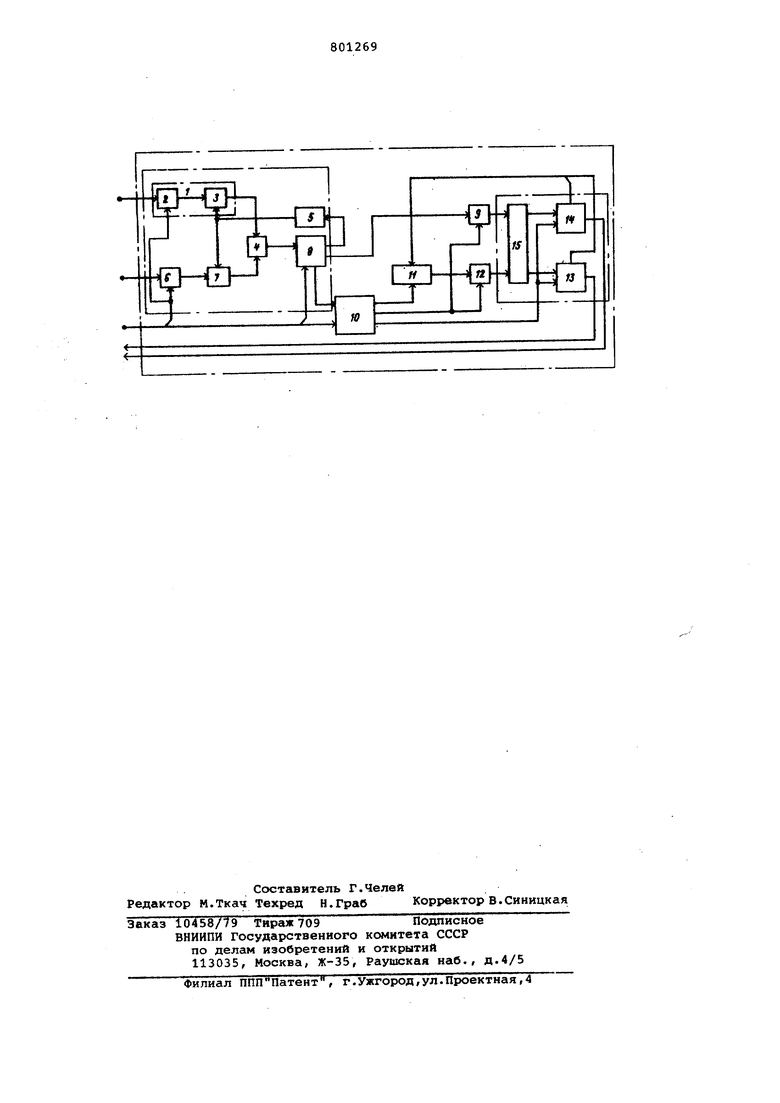

Изобретение относится к передаче сигналов и может использоваться для адаптивной коррекции межсимвольной интерференции в принимаемых сигналах данных, передаваемых в двух фазовых плоскостях многопоэиционными методами модуляции. Известен цифровой адаптивный корректор межсимвольных искажений в сиг налах данных, передаваемых в одной фазовой плоскости, содержащий аналого-цифровой преобразователь, состоящий из блока формирования и хранения выборок сигнала, выход которого подключен к первому входу компаратора, другой вход которого соединен с выходом цифроаналогового преобразователя, вход блока формирования и хранения выборок сигнала соединен с пер вьм входом программного блока, первый выход которого подключен к первы входам блока корреляции, запоминающего блока коэффициентов передачи, запоминающего блока выборок сигнала и сумматора, другой вход которого соединен с выходом блока корреляции через последовательно соединенные блок умножения и запоминающий блок коэффициентов передачи, выход сумматора соединен со вторым входом блока корреляции и с выходом устройства, выход блока запоминания выборок сигнала соединен со вторым входом блока умножения tl . Однако известный цифровой адаптивный корректор осуществляет коррекцию только синфазной составляющей межсимвольной интерференции при передаче сигналов данных в одной фазовой плоскости. Цель изобретения - обеспечение возможности коррекции межсимвольных искажений в сигналах данных, передаваемых в двух фазовых плоскостях. Цель достигается тем, что в цифровой адаптивный корректор межсимвольных искажений в сигналах данных, передаваемых в одной фазовой плоскости, содержащий аналого-цифровой преобразователь, состоящий из блока формирования и хранения выборок сигнала, выход которого подключен к первому входу компаратора, другой вход которого соединен о выходом цифроаналогового преобразователя,вход блока формирования и хранения выборок сигнала соединен с первым входом программного блока, первый выход которого подключен к первым входам . блока корреляции, запоминающего блока коэффициентов передачи, запоминающего блока выборок сигнала и сумматора, другой вход которого соединен с выходом блока корреляции через последовательно соединенные блок умножения и запоминающий блок коэффициентов передачи, выход сумматора соединен со вторым входом блока корреляции; и с выходом устройства, выход блока запоминания выборок сигнала соединен со вторым вхо дом блока умножения, введены коммута тор и блок управления, дополнительны блок формирования и хранения выборок сигнала, компаратор и сумматор, при этом выход дополнительного блока фор мирования и хранения выборок сигнала подключен через дополнительный компаратор, другой вход которого соединен с другим входом компаратора, к одному из входов коммутатора, друrofi вход которого соединен с выходом компаратора, выход коммутатора под-, ключен через блок управления ко входу цифроаналогового преобразователя второй и третий выходы блока управл ния соединены соответственно со вто входами программного блока и блока запоминания выборок сигнала, а другой выход блока умножения и выход программного блоха подключены ко входам дополнительного сумматора, выходам которого подключены к другому входу блока корреляции и к другому выходу устройства. На чертеже представлена структурная электрическая схема предложенного цифрового адаптивного корректора Цифровой адаптивный корректор меж символьных искажений содержит аналого-цифровой преобразователь 1, состо ящий из блока 2 формирования и хране НИН выборок сигнала и компаратора 3, коммутатор .4, цифроаналоговый преобразователь 5, дополнительный блок 6 формирования и хранения выбо рок сигнала дополнительный компаратор 7, блок 8 управления, запоминающий блок 9 выборок сигнала, программный блок 10, блок 11 корреляци запоминающий блок 12 коэффициентов передачи сумматор 13, дополнительны сукматор 14 и блок 15 умножения. Устройство работает следуюгцим об разом. Входные сигналы, представлякнаие собой аналоговые сигналы, с выходов синфазного и квадратурного демодуляторов приемника поступают на вход блоков 2 и б формирования и храие ния выборок сигнала,, где осуществляе ся стробирование демодулированных аналоговых сигналов-в отсчетные моменты времени, запоминание и хранен амплитуды полученного напряжения выборки. Напряжение выборки сигнала с выходов блоков 2 и 6 поступает на входы компараторов 3 и 7, выходы которых подключены ко входам коммутатора 4 . Преобразование напряжения выборки в п-разрядное кодовое число осуществляется посредством блока 8 управления и цифроаналогового преобразователя 5, на выходе которого формируется напряжение, пропорциональное п-разрядному коду. Это напряжение поступает на вторые входы компараторов 3 и 7, на выходах которых вырабатывается сигнал, свидетельствующий о неравенстве амплитуд напряжений на его входах. Коммутатор 4 осуществляет подключение одного из компараторов 3 или 7 к блоку 8 управления. Сначала преобразуют сигнал выборки с синфазного демодулятора (к блоку 8 управления через коммутатор 4 подключен компаратор 3), а затем - сигнал выборки с квадратурного демодулятора приемника (к блоку 8 управления через коммутатор 4 подключен компаратор 7). в такой же очередности осуществляется запись в запоминакяднй блок 9 выборок сигнала двух п-разрядных кодовых чисел выборок, полученных в результате преобразования. Импульсные последовательности, необходимые для работы блоков 2 и 6 . формирования и хранения выборок сих- нала и блока 8 управления, поступают с выхода приемника. Точность преобразования выборок, т.е. число разрядов п выбирается, исходя из требуемой ТОЧНОСТИ компенсации межсимвольной интерференции. По окончании формирования двух п-разрядных кодовых чисел блок 8 управления вырабатывает команду Пуск для nporpaiMMHoro блока 10. Програьв 1ный блок 10 вырабатывает сигналы, необходимые для работы блока 11 корреляции, запоминающих блоков 9 и 12 выборок сигнала и коэффициентов передачи соответственно и сумматоров 13 и 14. В блоке корреляции 11 на основании выбранного алгоритма работы по результатам анализа двоичных сигналов о полярности и отклонении цифровых сигналов на выходах сумматора 13 и 14 от их неискаженного значения вырабатываются управляющие сигналы, производится их интегрирование и формирование п-разрядного кодового числа, соответствующего коэффициенту передачи корректора. В каждом такте работы программного блока 10 .из запоминающих блоков 9 и 12 в блок 15 умножения поступают два п-разрядных кодовых числа, соответствующие модулям и полярностям кодов выборки и коэффициента передачи. Причем сначала в блок умножения поступает код выборки с синфазного демодулятора, а затем код выборки с квадратурного демодулятора приемника для умножения на один и тот же код коэффициента передачи регулятора,. Полученные произведения двух пар п-разрядных кодовых чисел записываются по командам, поступающим из программного блока 10, в соответствующие сумматоры 13 и 14 (в дополнительный сумматор 14 записываются произведения синфазных выборок, а в сумматор 13 квадратурных).

В следующем такте работы программного блока 10 из запоминающих блоков 9 и 12 на входы блока 15 умножения подаются другие разрядные числа, соответствующие коэффициенту передачи корректора. Результаты умножения алгебраически суммируются в сумматорах 13 и 14 с кодовыми числами, хранящимися в них от предыдущего такта работы программного блока 10. Этот процесс продолжается до тех пор, пока в сумматорах 13 и 14 не будут записаны суммы, полученные в результате суммирования произведений кодов выборок и коэффициентов передачи корректора для заданного числа тактов работы. Кодовые числа с выходом cyfe«iaTopOB 13 и 14 поступают в решающее устройство приемника, где осуществляется их декодирование.

В процессе настройки цифрового адаптивного корректора в запоминающем блоке 12 коэффициентов передачи записываются такие кодовые числа коэффициентов передачи, при которых величина межсимвольной интерференции будет минимальна.

Емкость запоминакжцих блоков 9 и 12 выбирается в зависимости от необходимой точности корректирования и величины исходных искажений в канале связи.

В предложенном адаптивном корректоре обеспечена возможность коррекции межсимвольных искажений в сигналах данных, передаваемь ос в двух фазовых плоскостях.

Формула изобретения

Цифровой ащаптивный корректор межсимвольных искажений в сигналах Данных, передаваекых в одной фазовой плоскости, содержащий аналогоцифровой преобразователь, состоящий

из блока формирования и хранения выборок сигнала, выход которого подключен к первому входу компаратора, другой вход которого соединен с выходом цифроаналогового.преобразовае теля, вход блока формирования и хранения выборок сигнала соединен с первым входом программного.блока, первый выход которого подключен к первьвл входам блока корреляции, Q запоминающего блока коэффициентов передачи, запоминающего блока выборок сигнала и сумматора, другой вход которого соединен с выходом блока корреляции через последовательно соединенные блок умножения и запоми5 накнций блок коэффициентов передачи, выход суквиатора соединен со вторым входом блока корреляции и с выходом устройства, выход блока запоминания выборок сигнала соединен со вторым

0 входом блока умножения, отличающийся тем, что, с целью обеспечения возможности коррекции межсимвольных искажений в сигналах данных передаваемых в двух фазовых

5 плоскостях, введены коммутатор и

блок управления, дополнительный блок формирования и хранения выборок сигнала, компаратор и сумматор, при этом выход дополнительного блока формировния и хранения выборок сиг0нала подключен через дополнительный компаратор, другой вход которого соединен с другим входом компаратора, к одному из входов коммутатора, другой вход которого соединен с

выходом компаратора, выход когФ1утатора подключен через блок управления ко входу цифроаналогового преобразователя, второй и третий выходы блока управления соединены соотнет0 ственно со вторыми входами программного блока и блока запоминания выборок сигнала, а другой выход блока умножения и выход nporpaNHviHoro блока подключены ко входам допсшнис тельного сумматора, выходакоторого подключены к другому входу блока корреляции и к другому выходу устройства.

Источники информации, принятые во внимание при экспертизе

1.Патент США 3633105, кл. 325-42, опублик. 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой адаптивный корректорСигНАлА | 1978 |

|

SU832733A1 |

| Адаптивный корректор сигнала | 1978 |

|

SU794735A1 |

| Устройство для адаптивной коррекции межсимвольных искажений | 1981 |

|

SU951725A1 |

| Цифровой адаптивный корректор межсимвольной интерференции | 1982 |

|

SU1083374A1 |

| Цифровой адаптивный корректор межсимвольных искажений в сигналах данных | 1979 |

|

SU921099A2 |

| Цифровой корректор сигналов | 1979 |

|

SU862366A1 |

| Адаптивный корректор межсимвольной интерференции | 1987 |

|

SU1540009A1 |

| Корректор межсимвольных искажений | 1984 |

|

SU1220130A1 |

| Адаптивный корректор | 1987 |

|

SU1417197A1 |

| Устройство для адаптивной коррекции межсимвольной интерференции | 1981 |

|

SU951724A1 |

Авторы

Даты

1981-01-30—Публикация

1978-02-27—Подача