tmA

00

vj

о

со

11

Изобретение относится к вычислительной технике и может быть исполь- :зовано в системах обработки информа- |циИэ к которым предъявляются повышен- 1ные требования по надежности и досто- верности данной обработки.

Целью изобретения является повыше- ние достоверности вычислений и повышение надежности путем сообщения уст- ройству CBOPiCTBa отказоустойчивости.

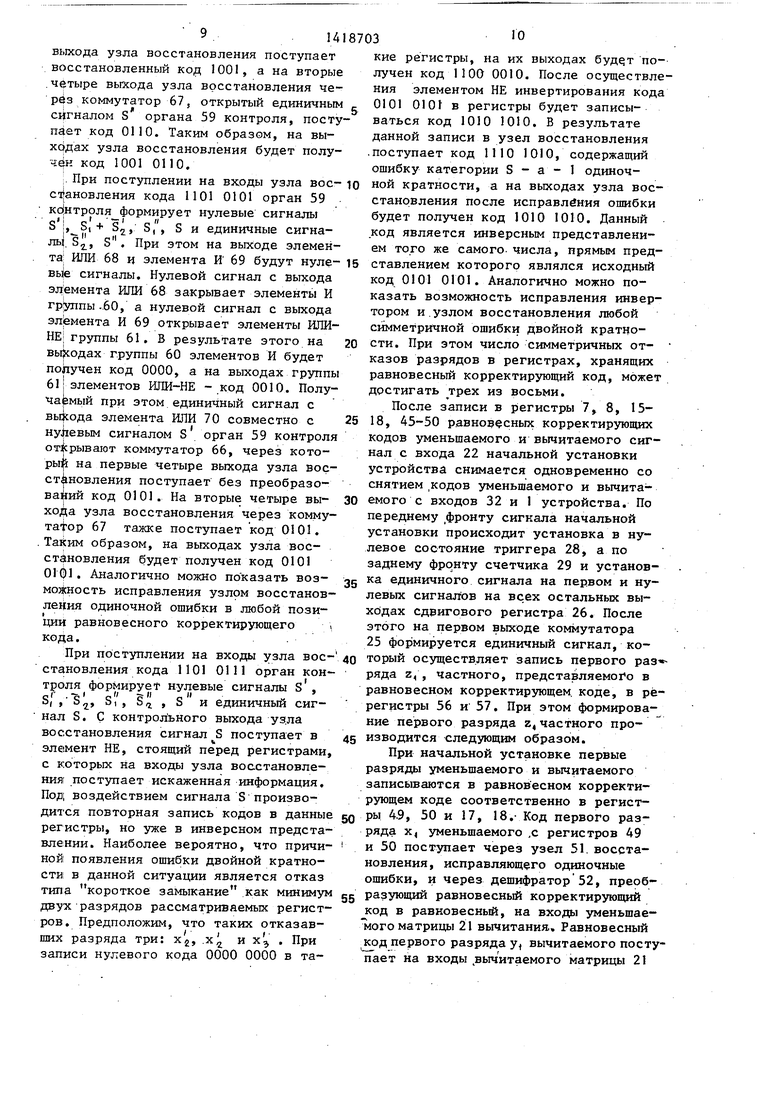

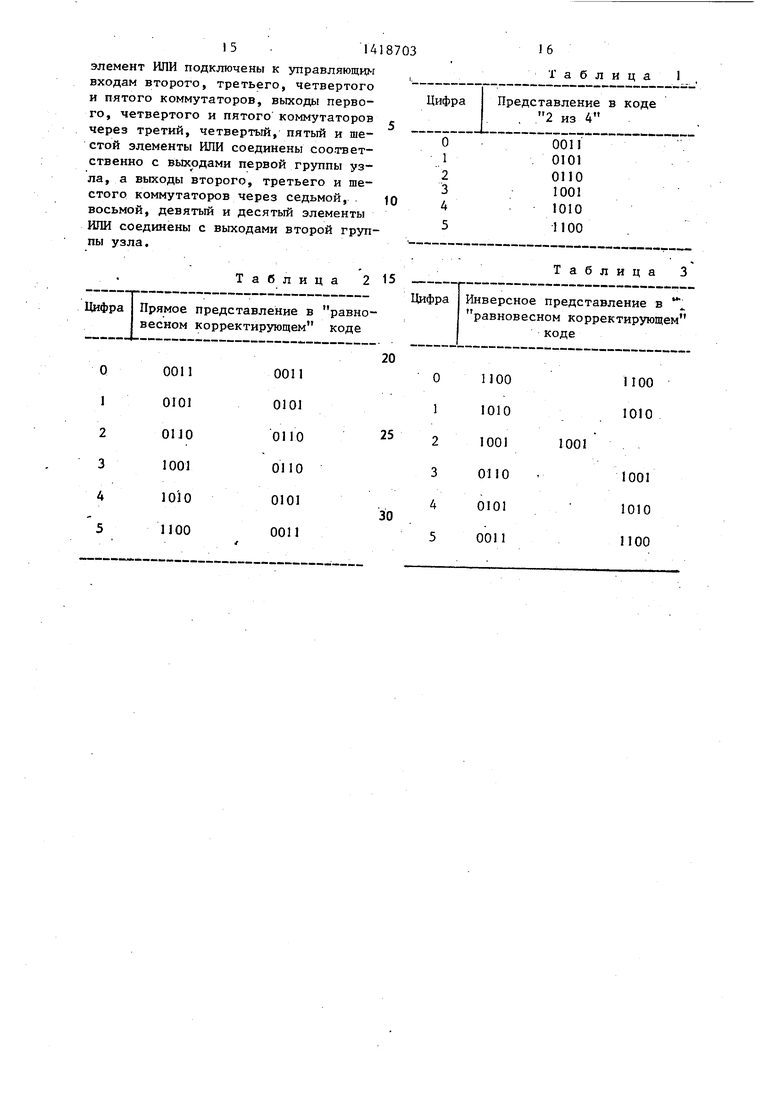

На фиг. 1 представлена функциональ ная схема устройства для вычитания; на фиг 2 - то же, узла восстановле- ния.

Устройство для вычитания содержит подключенные к входам 1 вычитаемого :устройства шифраторы 2-4. Выходы пшф- :ратора 2 через последова ельно соеди- ненные узел 5 восстановления и эле- ;мент НЕ 6 подключены к входам регист- IpoB 7 и 8. Выходы шифраторов 3-4 сое- |динены с входами групп 9-10 элементов ЩПИ. Вторые входы групп 9 элементов ИПИ подключены к выходам регистров 7 ;и 8. Выходы групп 9-10 элементов ИЛИ :через соответствующие последователь- ;но соединенные узлы 11-12 восстановления и элементы НЕ 13-14 подключены

:к входам регистров 15, 16-17, 18. Вы-30 и 57. Каждый узел восстановления

35

|ходы регистров 17 и 18 через последо- рательно соединенные узел 19,восстановления и дешифратор 20 подключены (с входам вычитаемого матрицы 21 вычитания . Вход 22 начальной установки устройства подключен непосредственно Нерез элемент И 23 и элемент 24 за- рержки и управляющим входам коммутатора 25, информационные входы которо- о через сдвиговый регистр 26 соеди- 0 Нены с выходом генератора 27 импульсов. Вход 22 начальной установки устройства подключен также к установочным входам сдвигового регистра 26, триггера 28 и счетчика 29, счетный вход которого соединен с выходом : сдвигового регистра 26, а вькод подключен к выходу 30 признака окончания работы устройства. Тактирз щий вход триггера 28 подключен к выходу сдвигового регистра 26, а информаци- онньм вход триггера 28 соединен с выходом знака разности матрицы 21 вЫ читания, вход переноса которой подключен к. выходу триггера 28 и знаковому выходу 31 устройства. Выходы 32 уменьшаемого устройства через шифраторы 33-35 соединены с входами групп 36-38 элементов НИИ, выходы которых

45

50

55

(фиг. 2) содержит подключенные к дам орган 59 контроля, группу. 60 элементов И, группу 61 элементов НЕ и коммутаторы 62-67. Выходы ор 59 контроля подкгаочены к контрол му выходу узла восстановления, к равляющим коммутаторов 62и через элементы ИЛИ 68 и И 69 - общим входам группы 60 элементов группы 61 элементов ИЛИ-НЕ, выход которых через элемент ИЛИ 70 соед ны с управляющими входами коммута ров 62-67. Выходы .коммутаторов 62 через элементы ИЛИ 71-78 подключе к выходам узла восстановления.

Уменьшаемое и вычитаемое посту на входы 1 и 32 устройства в равн весном коде 2 из 4.

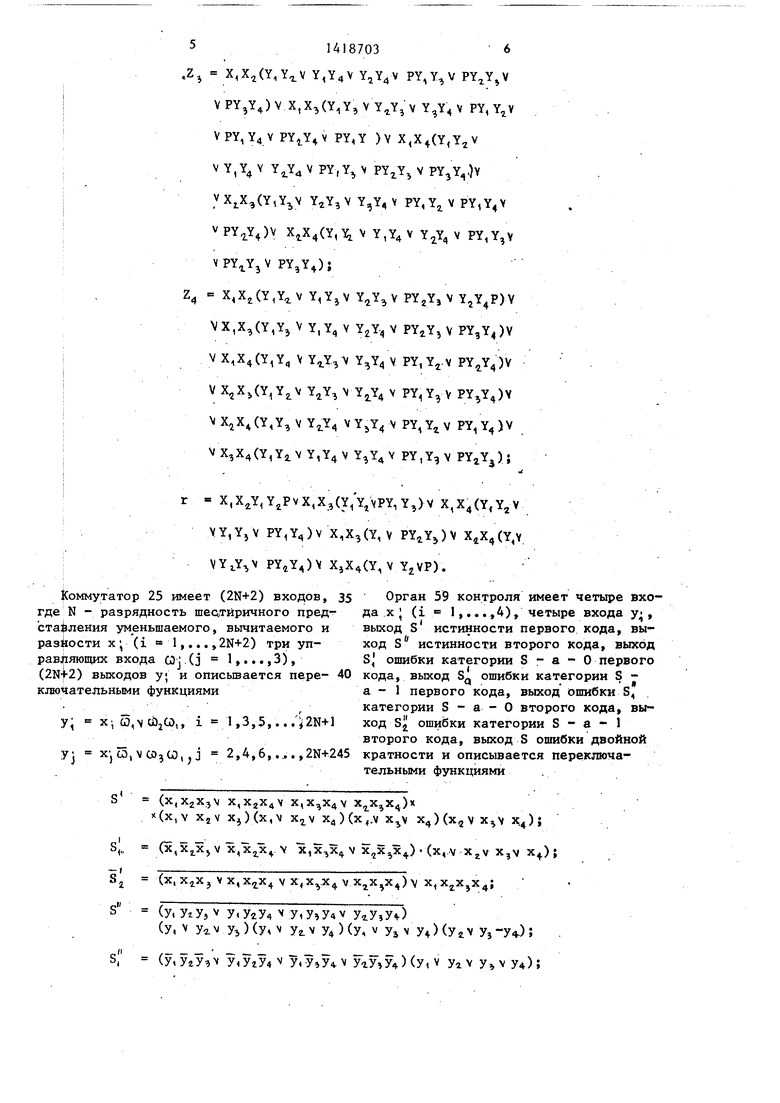

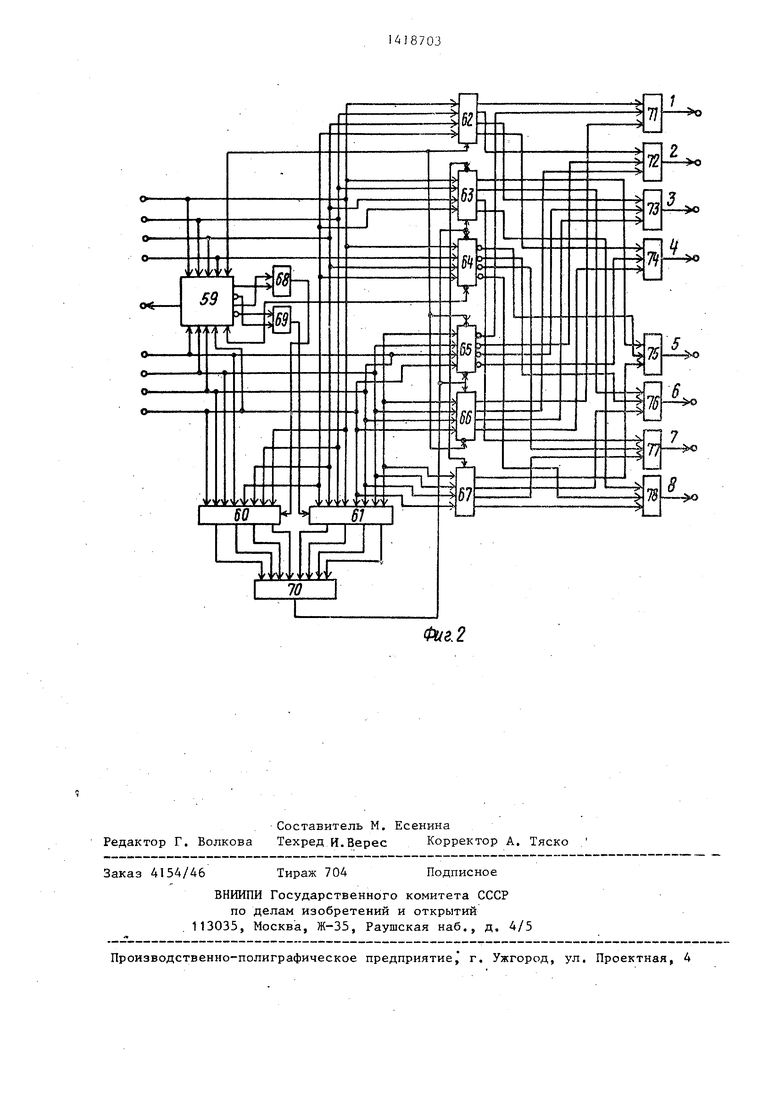

Соответствие между цифрами от до 5 и их представлениями в коде из 4 представлено в табл. 1.

Устойчивость к отказам .отдельн элементов устройства обеспечивает за счет перекодирования непосредс венно в устройстве равновесных ко уменьшаемого, вычитаемого и частн в так назьшаемые равновесные кор ректирующие коды. В этих кодах п

через последовательно соединенные узлы 39-41 восстановления и элементы НЕ 42-44 подключены к входам регистров 45, 46-49, 50. Выходы регистров 45 и 46 соединены с вторыми входами группы 37 элементов ИЛИ, а выходы регистров 49 и 50 через последовательно соединенные узлы 51 восстановления- и дешифратор 52 подключены к входам уменьшаемого матрицы 21 вычитания. Выходы разности матрицы 21 вычитания через 11осле1ддвательно соединенные шифратор 53, узел 54 восстановления и элемент НЕ 55 подключены к входам регистров 56 и 57, выходы которых соединены с входами группы 36 элементов ИЛИ. -Контрольные выходы узлов 11, 12, 19, 39-41 51 восстановления подключены к входам соответствующих инверторов 6, 13, 14, 55, 42 и и 44. Контрольный выход узла 54 воестановления соединен с контрольным выходом 58 устройства. Выходы коммутатора 25 подключены к синхронизирующим входам инверторов 6, 13, 14, 42, 43, 44 и 55, тактирующие выходы которых соединены с тактирующими входами регистров 7, 8, 15-18, 45-50, 56

(фиг. 2) содержит подключенные к вхог дам орган 59 контроля, группу. 60 элементов И, группу 61 элементов ИПИ- НЕ и коммутаторы 62-67. Выходы органа 59 контроля подкгаочены к контрольному выходу узла восстановления, к управляющим коммутаторов 6267 и через элементы ИЛИ 68 и И 69 - к общим входам группы 60 элементов И и группы 61 элементов ИЛИ-НЕ, выходы которых через элемент ИЛИ 70 соединены с управляющими входами коммутаторов 62-67. Выходы .коммутаторов 62-67 . через элементы ИЛИ 71-78 подключены к выходам узла восстановления.

Уменьшаемое и вычитаемое поступают на входы 1 и 32 устройства в равновесном коде 2 из 4.

Соответствие между цифрами от О до 5 и их представлениями в коде 2 из 4 представлено в табл. 1.

Устойчивость к отказам .отдельных элементов устройства обеспечивается за счет перекодирования непосредственно в устройстве равновесных кодов уменьшаемого, вычитаемого и частного в так назьшаемые равновесные корректирующие коды. В этих кодах при3141

нято рассматривать два представления: прямое и инверсное.

Соответствие между цифрами от О до 5 и их црямыми представлениями в равновесном корректирующем коде представлено в табл. 2.

Соответствие между цифрами от О до 5 и их инверсными представлениями в равновесных корректирующих кодах представлено в табл. 3,

Преобразование равновесных кодов уменьшаемого, вычитаемого и разности производится дешифраторами 2-4, 33-35 и 53. Данные дешифраторы имеют по четыре входа к j (i 1,...,4), по четыре выхода у., по четыре выхода у; и описываются переключательными функциями

8703

выхода У;, по четыре выхода у, по тактирующему выходу v и описьшаются переключательными функциями

у x.U,v xlUjk} у I x :u,V V .

10

Группы.9. 10, 36-38 элементов ИЛИ

имеют по четыре входа х; (i 1,...,4) по четыре входа х , по четыре входа yj , по четыре входа у, по «етыре выхода , по четыре выхода z / и описываются переключательными функциями

20

.1 f x.,vy, ;

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор быстрого преобразования уолша-адамара | 1989 |

|

SU1795471A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для быстрого ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1989 |

|

SU1615742A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Устройство для программного управления | 1985 |

|

SU1280571A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1987 |

|

SU1413627A1 |

| Устройство для последовательного деления | 1986 |

|

SU1304017A1 |

| Экстраполятор | 1990 |

|

SU1837317A1 |

| Устройство для быстрого преобразования Уолша-Адамара | 1987 |

|

SU1443002A1 |

Изобретение относится к вычислительной технике и позволяет повысить достоверность результатов выполнения операций и надежность путем придания устройству для вычитания свойств самокоррекции и устойчивости к отказам. С этой целью устройство содержит шифраторы, узлы восстановления, элементы НЕ, регистры, группы элементов И, два дешифратора, матрицу вычитания, элемент задержки, коммутатор, сдвиговый регистр, генератор импульсов и счет чик. Уменьшаемое и вычитаемое поступают в устройство- в равновесном коде 2 из 4, преобразуются в корректирующие равновесные коды и при необходимости корректируютсяJ- Исправление ошибок двойной кратности и выше осуществляется как в операндах, так и в результате вьтолнения операции. 1 3.п. ф-лы, 2 ил. 3 табл. «g

V t

. 1

у, Х;Х, V Х-Х, , i 1,...,4

Узлы 5, 11, 12, 19, 39-41, 54 восстановления предназначены для исправления в поступающих на их входы равновесных корректирующих кодах ошибок одиночной кратности и обнаружения оши- ошибск двойной кратности.

Элементы НЕ 6, 13, 14, 42-44, 53 предназначены для изменения с прямого на инверсное представление цифр ,в равновесных корректирующих кодах. Элементы НЕ имеют по четыре входа

i

(i 1,, ..,4), по четыре входа х, два синхронизирующих входа U, U, контрольному входу k, по четыре

Z, X,X( ,)v

Матрица входа умень 2g четыре вход переноса р

выход з

ется перекл

VX,X,(Y, PY,Y, V YiY4)V

VX.. Y,Y2V Y,Y)V

VX,Xj(,V Y,Y4 V ,v Y,Y)V

VXiX4(Y4Y5 V Y, Y V PY2Y4 V Y,Y, )V VX,X4(Y2Y4V PY,Y4 V Y,Y4) ; X,,X(Y, Y,Y4 PY,,Y, Y

VX,X3(Y,Ya V Y,Y4 V PY, Y.V )V VX,X4(YiY3 V , V PY,Y4)V

V ,(Y,Y4 y V PY, Y2 ,)Y V Y,iY3 V , v PY,Y v PY2Y4)Y

, v PY,Y4 v PY,Y4);

z . .

Дешифраторы 20 и 52 предназначены для преобразования равновесньск кор- 25 ректирующих - кодов в равновесные коды. Дешифраторы имеют по четыре входа х , (i 1,...,4), по четыре входа х по четыре выхода уj и описьшаются переключательными функциями

у. X х 1 11

vx;

Xj

Матрица 21 вычитания имеет четыре входа уменьшаемого х; (i 1,...,4), 2g четыре входа вычитаемого у , вход переноса р, четыре выхода разности

i

выход знака разности г и описыва

ется переключательными функциями

514187036

.z X,X,J(Y,YTV Y,Y4V PY,Y,V PY,,

IVPY,Y)V X,X,(Y,Y, PY,Y,,V

VPY,Y4V PY,Y )V X,X(Y,Y,jV

V Y, Y Y Y,Y4 V PY, Y, V V PY,Y.)V ;: Xj,X,(Y, Y,Y, V PY,,Y4V

V )V X X CYtYi V Y,Y4 V V PY,Y,y

); Z X,X,(Y, Y,YjV Y Y VPY YjVYjY PyV

VX,X,(Y,Y5 V Y,Y V V PYjY, V PY,Y4)V

:vx,x,(Y,Y, Y,Y;VPY,Y.)V

IVX,X,(,,V YjY4VPY,Y,VPY5Y)V

(Y,Y, VYjT VY Y4VPY,YiV PY,Y)V

X,X4(Y,YiVY,Y4V PY,Y3VPYiY);

i

r - X,,X3(Y;Y,yPY,Y,)V X,X(Y,Y2V VY,YjV PY,Y4)Y Х;ХЗ(У, V PYiY5)V PY4Y4)V , V YzVP).

Коммутатор 25 имеет (2N+2) входов, 35 Орган 59 контроля имеет четьфе вхо- где N - разрядность шестиричного пред- да хJ (i 1,...,4), четыре входа у, ста ления уменьшаемого, вычитаемого и выход S истинности первого хода, вы- разйости х; (i l,...,2N+2) три уп- ход S истинности второго кода, выход paвJ(Iяющшc входа СО; .(J ), S ошибки категории S - а - О первого (2N+2) выходов у; и описьшается пере- 40 кода, выход S ошибки категории S - ключательными функциямиа - 1 первого кода, выход ошибки S,

. категории S - а - О второго кода, выу X; Q,ci)jG),, i 1,3,5,... i2N+l ход SJI ошибки категории S - а - 1

второго кода, выход S ошибки двойной

у. Xj с5, V (,, j 2,4,6, .J.. ,2N+245 кратности и описывается переключательными функциями

S (XjXjX V X,X2X4V Х,Х,Х4 )

(к, XjV Xj)(x,vj х X4)(x,.v X4)(x2V x.); s|. (x, V x, XjX V x,x,X4 V ) (x,v XjV x,v x);

Sj (X, Y X, V X,X.X V XjX,X4)v X,X2XjX4;

S (y, yiYjV у,УгУ4 )

(у, V УЗ)(У N Уг.У У4)(у, V yj V yj-y.);

S, (У1УгУэ УаУзУ4)(У) Уг У4);

71418703

Sj (, v у, V ) у, У Уэ У4;

S s sl v sis V v X, V vy. V x, V у, .

Группа 60 элементов И имеет четыре действием управляющего сигнала, по- входа х; (i 1,...,4), четыре входа ступающего с выхода элемента 24 за- , четыре выхода z,; , общий вход держки через коммутатор 25 на вторые и описьшается переключательными функ- синхронизирующие входы элементов НЕ 6, циями .13, 14, 42-44. Равновесные корректирующие коды уменьшаемого и вьтитаемо- Zj x, i 1,...,4. го поступают на информационные входы

регистров 7j 8, 15-18, 45-50 с шифраГруппа 6.1 элементов ЮТИ-НЕ имеет торов 2-4, 33-35 через группы 9, 10, четыре входа х; (i 1,,..,4), четыре 36-38 элементов ИЛИ, узлы 5, 11, 12,. входа У; , общий вход Т , четыре выхо- 39-41 восстановления и элементы НЕ 6, да Z; и описывается переключательными 13, 14, .42-44.

функциями При осуществлении записи- в регист-т- ... 20

- ры устройства кодов уменьшаемого и

z; - X, V у; vjj J 1 - I ,...,4. вычитаемого возможно исправление одиночных ощибок как .категории S-a-0,

Коммутаторы 63 и 66 имеют по четы- .к и категории S-a-1 с помощью узла ре входа х; (i - 1,..,,4), по управ- восстановления и двойных ошибок с .ляющему.входу S, по управляющему вхо- 25 „епользованием органа 59 контроля, ду г, по четыре выхода у; и описьша- восстановления и элемента НЕ. Ис- ются переключательными функциями правление ошибок -в равновесных коррек- тирующих кодах рассмотрим на следуюУ1 в v « . 1 1 щих примерах.

Пусть два разряда уменьщаемого

Коммутаторы 64 и 65 имеют по четы- (вычитаемого) имеют прямое представ- ре входа к,; (i 1,...,4), по управ- равновесном корректирующем ко- ляющему входу S, по управляющему вхо- следующего вида 1001 ОНО и 0101 ду г, по четыре выхода у,- и описьшают Предположим, что в результате ся переключательными функциями 35 воздействия физических отказов элемен

. .тов или сбоя на входы узла восстанову, - JJ1 у SvT

1 ления поступил искаженный код: 1000

ОНО, 1101,0101, 1101 0111, 1111 0101.

Устройство работает следующим образом.40 При поступлении на входы узла восОдновременно с поступлением на вхо- становления кода 1000 0110 орган 59 входы 32 уменьшаемого устройства и контроля сформирует нулевые сигналы входы 1 вычитаемого устройства равно- S , s, S и единичные сигналы S,, Sj, весных кодов уменьшаемого и вычитае-, S , Sj,. При этом на выходе элемента мрго подается сигнал на вход 22 на- 45 элемента И 69 будут единич- чальной установки устройства. Под ные сигналы. Единичный сигнал с вы- воздействием этого сигнала, открывает- хода элемента ИЛИ-68 открывает элемен- ся элемент И 23 и импульс с его выхо- ты И группы 60, а единичный сигнал с да через коммутатор 25 поступает на выхода элемента И 69 закрьшает эле- первые синхронизирующие входы всех 50 ИЛИ-НЕ группы 61. В результате элементов НЕ 6, 13, 14, 42-44 и 55. этого как на выходах группы 60 элеВ результате этого в соответству- ментов И, так и на выходах группы 61 ющие регистры 7, 8, 15-18, 45-50 за- элементов ИЛИ-НЕ будут получены коды писываются в прямом представлении 0000 -. Нулевой сигнал с выхода элемен- равновесные корректирующие коды умень-55 совместно с нулевым сигна- шаемого и вычитаемого. Запись,, при лом органа 59 контроля открьшают ком- необходимости, данных кодов в регист- мутатор 65, который производит инвер- ры 7, 8, 15-18, 45-50 в инверсном - , тирование разрядов кода 0110.. Это представлении осуществляется под воз- приводит к тому, что на первые четыре

выхода узла восстановления поступает восстановленный кo 1001, а на вторые .четыре выхода узла восстановления через коммутатор 67, открытый единичным сигналом S органа 59 контроля, поступает код 0110. Таким образом, на выходах узла восстановления будет полу- код 1001 0110,

;. При поступлении на входы узла вос- ст ановления кода 1101 0101 орган 59 контроля формирует нулевые сигналы S |,S, + S, S,, S и единичные сигналь S, S. При этом на выходе элемента; ИПИ 68 и элемента И 69 будут нулевые сигналы. Нулевой сигнал с выхода элемента ИЛИ 68 закрывает элементы И группы ..60, а нулевой сигнал с выхода элемента И 69 открывает элементы ИЛИ- НЕ| группы 61. В результате этого на вы|х;одах группы 60 элементов И будет получен код 0000, а на выходах группы 61 элементов ИЛИ-НЕ -.код 0010. Полу- при этом единичный сигнал с вьфода элемента ИЛИ 70 совместно с ну41евым сигналом S орган 59 контроля открывают коммутатор 66, через который на первые четыре выхода узла вос- ст новления поступает без преобразо- ва1|1ий код 0101. На вторые четыре вы- xo;jia узла восстановления через комму- Tafop 67 тажке поступает код 0101. Тайим образом, на выходах узла восстановления будет получен код 0101 0101. Аналогично можно показать возможность исправления узлом восстановления одиночной ошибки в любой пози- 1ЩИ равновесного корректирующего , кода.

При поступлении на входы узла воестановления кода 1101 0111 орган контроля формирует нулевые сигналы S , S,, S, Si, S/i , S и единичный сигнал S. С контрольного выхода уз.ла восстановления сигнал S поступает в элемент НЕ, стоящий перед регистрами, с которых на входы узла восстановле- нияг поступает искаженная информация. Под воздействием сигнала S производится повторная запись кодов в данные регистры, но уже в инверсном представлении. Наиболее вероятно, что причиной появления ошибки двойной кратности в данной ситуации является отказ типа короткое замыкание как минимум дв-ух разрядов рассматриваемых регистров. Предположим, что таких отказавших разряда три: Xg, .х и х . При записи нулевого кода 0000 0000 в такие регистры, на их выходах получен код 1100 0010. После осуществления элементом НЕ инвертирования кода

0101 OlOf в регистры будет записываться код 1010 1010. В результате данной записи в узел восстановления .поступает код 1110 1010, содержащий ошибку категории S - а - 1 одиночной кратности, а на выходах узла восстановления после исправления ошибки будет получен код 1010 1010. Данный .код является инверсным представлением того же самого, числа, прямым представлением которого являлся исходный код 0101 0101. Аналогично можно показать возможность исправления инвертором и узлом восстановления любой симметричной ошибки двойной кратности. При этом число симметричных от- казов разрядов в регистрах, хранящих равновесный корректирующий код, может достигать трех из восьми.

После записи в регистры 7, 8, 1518, 45-50 равновесных корректирующих кодов уменьшаемого и вычитаемого сигнал с входа 22 начальной установки устройства снимается одновременно со снятием ,кодов уменьшаемого и вычитаемого с входов 32 и 1 устройства. По переднему фронту сигнала начальной установки происходит установка в нулевое состояние триггера 28, а по заднему фронту счетчика 29 и установка единичного сигнала на первом и нулевых сигналов на всех остальных вы- хЬдах сдвигового регистра 26. После этого на первом выходе коммутатора 25 формируется единичный сигнал, который осуществляет запись первого ряда Z, , частного, представляемого в равновесном корректирующем, коде, в рё- регистры 56 и 57. При этом формирование первого разряда z,частного производится следующим образом.

При начальной установке первые разряды уменьшаемого и вычитаемого записываются в равновесном корректирующем коде соответственно в регистры 4-9, 50 и 17, 18.- Код первого разряда х, уменьшаемого ,с регистров 49

и 50 поступает через узел 51. восстановления, исправляющего одиночные ошибки, и через дешифратор 52, преобразующий равновесный корректирующий код в равновесный, на входы уменьшае- мого матрицы 21 вычитания. Равновесный код первого разряда у вычитаемого поступает на входы вьтаитаемого матрицы 21

вычитания с регистров 17 и 18 через узел 19 восстановления и дешифратор 20. Так как триггер 28 при начальной установке сбрасьшается в О, то на выходах .разности матрицы 21 вычитания формируется равновесньй код цифры

Z, (х, - у, - 0)modq., а на выходе знака разности сигнал

Р

0,при X , i у,

1,при X , у,

Данный сигнал Р поступает на информационный вход триггера 28, который по сигналу с первого выхода сдвигового регистра 26 устанавливается. при Р 1 в единичное, а при Р О - в нулевое состояние., Равновесный код цифры z после преобразования в равновесный коррекФор-мула изобретения

тирующий код в шифраторе 53 и исправ- 25 при этом индицируется величиной сиг- ления ошибок в узле 54 восстановле- нала на знаковом выходе 31 устройства. ния через элемент НЕ 55 поступает на входы регистров 56 и 57, где он хранится до следующего такта работы устройства. При обнаружении в равновесном корректирующем коде цифры z , ошибки двойной кратности одной из , категорий S-a-0 или S-a-1 узел 54

30

контрольном выходе 58 устройства, ин- чика, а выход триггера соединен со формируя тем самым вьш1естоящую систе- знаковым выходом устройства, о т - му о невозможности получения неискаженного кода разности.

После записи в регистры 56 и 57

личающееся тем, что, с целью повышения достоверности вычислений и повьшения надежности путем со- равновесного корректирующего кода общения устройству свойства отказоустойчивости, - в него введены 2N+1 шифраторов, где N - разрядность шестиричного представления уменьшаемого и

вого разряда z разности управляющими сигналами с третьего и четвертого вы-. ходов коммутатора 25, поступающими на

синхронизирующие входы элементов НЕ 14 вычитаемого, 2N+3 узлов восстановле- и 44, производится перезапись в реги- .д ния, 2N+1 элементов НЕ, 2N+2 регист- стры 49, 50 и 17, 18 равновесных кор-, ров, 2N-1 групп элементов И, два де- ректирзтещих. кодов вторых разрядов шифратора, матрица вычитания, элемент уменьшаемого и вычитаемого и т.д. По управляющим сигналам с (2N-l)-ro и

И, элемент задержки, коммутатор, сдвиговый регистр, триггер и счетчик.

2 N-ro, где N - разрядность шестиричного представления уменьшаемого и вьиитаемого, выходов коммутатора 25 производится перезапись равновесных корректирующих кодов старших разрядов уменьшаемого и вычитаемого из регистров 45, 46 и 7, 8 в регистры 47, 48 и 15, 16.

По управляющим сигналам с (2N+l)-r и (2N+2)-ro выхода коммутатора 25 :

производится обнуление регистров 7 и 8 и перезапись равновесного корректирующего кода первого разряда z, из регистров 56 и 57 в -регистры 45 и 46. Кроме того, по сигналу с (2N+2)-ro выхода коммутатора 25 производится увеличение содержимого счетчика 29 на единицу. На этом первый такт работы

устройства заканчивается.

Все последующие такты выполняются аналогично первому. После окончания последнего N-ro такта счетчик 29 формирует сигнал на выход 30 признака

окончания работы. Данный сигнал указывает на то, что выполнение операции закончено и результат выражений в равновесном корректирующем дополнительном коде находится в регистрах

45-50. При этом понятие дополнительный код в равновесных кодах имеет то же значение, что и в классической двоичной системе счисления.- Знаковый разряд дополнительного кода разности

Фор-мула изобретения

при этом индицируется величиной сиг- нала на знаковом выходе 31 устройства

при этом индицируется величиной сиг- нала на знаковом выходе 31 устройства

И, элемент задержки, коммутатор, сдвиговый регистр, триггер и счетчик.

0

при этом 1-я грзшпа входов вычитаемого устройства, где i 1, N, подключена к входам i-ro шифратора, вьпсоды первого шифратора.через последовательно соединенные первый узел восстановления и первый элемент НЕ подключены к входам первого и второго pefHCTpOB,

выходы J-X шифраторов, где j 2, N, через, последовательно соединенные (j-l)-ю группу элементов ИЛИ, i-й

13

узел восстановления и 1-й элемент НЕ подключены к входам (21-1)-го и 21- го регистров соответственно, вторая Группа входов q-й, где q 1, jN-1), Группы элементов ИЛИ-соединены с вы- кодами (2q-l)-ro и 2q-ro реп стров, тактирующий выход i-ro элемента НЕ Ьодключен к тактирующим входам (21141870314

ходы (N+2)-ro узла восстановлекия рез второй дешифратор соединены С входами уменьшаемого матрицы вычитания, выходы разности которой через последовательно соединенные (2К+1)-й шифратор, (2Ы+3)-й узел восстановления и (2Ы-И)-й элемент НЕ подключены к входам (AN+l)-ro и (4Ы+2)-го региJ)-ro и 21-го регистров, а контроль- Ю стров, выходы которьк соединены с

ный,выход К-го узла восстановления, где К 2, (N+1), соединен с Ляющим входом (K-l)-ro элемента НЕ, выходы (N+l)-ro узла восстановления 1ерез первый дешифратор соединены с входами вычитаемого матрицы вычитания, выход знака разности которой . пoдkлючeн к информационному входу Триггера, вход начальной установки

второй группой входов N-й группы элементов ИЛИ, контрольный выход (2N+ +3)-го узла восстановления соединен с контрольным выходом устройства, 15 тактирующий выход (N+l)-ro элемента НЕ подключен к тактирующим входам (4N+l)-ro и (4N+2)-ro регистров, а контрольный выход (N+2)-ro узла восстановления соединен с управляющим

Устройства подключен к первому управ- 20 входом (2N+I)-ro элемента НЕ, первый яющему входу коммутатора, к устано- и второй синхронизирующие входы крто- io4HOMy входу сдвигового регистра, рого подключены к первому и второму входам установки в О триггера и выходам коммутатора, (214-1 )-й выход счетчика, к первому входу первого коммутатора подключен к первым син- флеманта И и входу элемента задержки, 25 хронизирующим входам (N+l-i)-ro и инверсный выход которого через эле- (2N+l-i)-ro элементов НЕ (21+2)-й И соединен с вторым управляющим входом коммутатора, прямой выход эле- ivieHTa задержки подключен к третьему управляющему входу коммутатора, ин- 30 формационные входы которого через сдвиговый регистр соединены с выходом енератора импульсов, первый выход сдвигового регистра подключен к так- ; пирующему входу триггера, выход кото- з5 г°Р° при этом первая группа входов рого соединен с входом переноса мат- узла подключена к первым входам блока |)ицы вычитания и со знаковым выходом устройства, (2N+2)-й выход сдвигового регистра подключен к счетному входу счетчика, выход которого соединен с 40 Р группа входов узла соединена с выходом признака окончания работы уст вторыми входами блока контроля, груп- ройства, 1-я, с первой по 1-ю, группа входов уменьшаемого устройства подвыход коммутатора подключен к вторым синхронизирующим входам (N+l-i)-ro и (2N+l-i)-ro элементов НЕ.

2, Устройство ПОП.1, отличающееся тем, что узел восстановления содержит блок контроля, десять.элементов ИЛИ, элемент И, груп пу элементов ИЛИ-НЕ и шесть коммутаконтроля, группы элементов И, группы элементов ИЛИ-НЕ и входам первого, второго, третьего коммутаторов, втоклкзчена к входам (i+N)-ro шифратора.

пы элементов И, группы элементов ИЛИ- НЕ и входам четвертого, пятого, шестого коммутаторов, первый выход бло- выходы которых через последовательно 45 контроля подключен к контрольному соединенные (1+Ы-1)-ю группу элемен- выходу узла, второй выход блока конто в ИЛИ, (1+Ы+1)й узел восстановления, (1+К)-й элемент НЕ подключены к входам (2i+2N-l)-ro ji (2i+2N)-ro разрядов, вторая группа входов п-й груп-CQ пы элементов ИЛИ, где п (N+1)(2N-1) соединена с выходами (2п-1)-го и 2п- го регистров, тактирующий выход J-ro элемента НЕ, где J (N-1)(2N), подключен к тактирующим входам ()- НЕ группы, седьмой выход блока конт- о и 2 J- -го регистров, а контрольный роля подключай к управляющим входам иыход J-го узла восстановления, где второго, третьего и шестого коммута- В (N+3)(2N+2), соединен с Управля- торов, выходы группы элементов И и ющим входом (3-2)-го элемента НЕ, вытроля соединен с управляющими входами первого, четвертого и пятого коммутаторов, третий и пятый выходы блока контроля через первый элемент ИЛИ подключены к первым входам эламентов И группы, четвертый и шестой выходы блока контроля черезэлемент И соединены с первыми входами элементов ИЛИгруппы элементов ИЛИ-НЕ через второй

ния, выходы разности которой через последовательно соединенные (2К+1)-й шифратор, (2Ы+3)-й узел восстановления и (2Ы-И)-й элемент НЕ подключены к входам (AN+l)-ro и (4Ы+2)-го регивходом (2N+I)-ro элемента НЕ, первый и второй синхронизирующие входы крто- рого подключены к первому и второму выходам коммутатора, (214-1 )-й выход коммутатора подключен к первым син- хронизирующим входам (N+l-i)-ro и (2N+l-i)-ro элементов НЕ (21+2)-й г°Р° при этом первая группа входов узла подключена к первым входам блока Р группа входов узла соединена с вторыми входами блока контроля, груп-

выход коммутатора подключен к вторым синхронизирующим входам (N+l-i)-ro и (2N+l-i)-ro элементов НЕ.

2, Устройство ПОП.1, отличающееся тем, что узел восстановления содержит блок контроля, десять.элементов ИЛИ, элемент И, группу элементов ИЛИ-НЕ и шесть коммутавходом (2N+I)-ro элемента НЕ, первый и второй синхронизирующие входы крто- рого подключены к первому и второму выходам коммутатора, (214-1 )-й выход коммутатора подключен к первым син- хронизирующим входам (N+l-i)-ro и (2N+l-i)-ro элементов НЕ (21+2)-й г°Р° при этом первая группа входов узла подключена к первым входам блока Р группа входов узла соединена с вторыми входами блока контроля, груп-

контроля, группы элементов И, группы элементов ИЛИ-НЕ и входам первого, второго, третьего коммутаторов, втопы элементов И, группы элементов ИЛИ- НЕ и входам четвертого, пятого, шестого коммутаторов, первый выход бло- контроля подключен к контрольному выходу узла, второй выход блока конНЕ группы, седьмой выход блока конт- роля подключай к управляющим входам второго, третьего и шестого коммута- торов, выходы группы элементов И и

троля соединен с управляющими входами первого, четвертого и пятого коммутаторов, третий и пятый выходы блока контроля через первый элемент ИЛИ подключены к первым входам эламентов И группы, четвертый и шестой выходы блока контроля черезэлемент И соединены с первыми входами элементов ИЛИпы элементов И, группы элементов ИЛИ- НЕ и входам четвертого, пятого, шестого коммутаторов, первый выход бло- контроля подключен к контрольному выходу узла, второй выход блока конНЕ группы, седьмой выход блока конт- роля подключай к управляющим входам второго, третьего и шестого коммута- торов, выходы группы элементов И и

группы элементов ИЛИ-НЕ через второй

элемент ИЛИ подключены к управляющим входам второго, третьего, четвертого и пятого коммутаторов, выходы первого, четвертого и пятого коммутаторов через третий, четвертый, пятый и шестой элементы ИЛИ соединены соответственно с выходами первой группы узла, а выходы второго, третьего и шестого коммутаторов через седьмой, . восьмой, девятый и десятый элементы ИЛИ соединены с выходами второй группы узла.

10

ООП 0101 QUO 1001

loJo

1100

ООП 0101

оно оно

0101 ООП

16 Таблица

k-Фиг.2

| Устройство для вычитания | 1982 |

|

SU1016781A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычитания | 1982 |

|

SU1083183A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-06—Подача