113

Изобретение относится к вычислительной технике, предназначено для последойательноро деления чисел,

золотой

представленных в кодах

порции и может быть использовано в

отказоустойчивых процессорах ЦВМ.

Целью изобретения является повышение надежности устройства.

Алгоритм поразрядного деления кодов золотой 1-пропорции основывается на методе деления с восстановлением остатка. Остаток В. на i-м такте деления и i-я цифра частного Z. вычисляются по формулам:

про-

.

1 + К

С

В,„

«(в,

+х

1-Ш

-к о , при Z .

,.,., -YbK., )Х.,,Ы

при Z.

. P b,

.

если B.Y., если B. ,Y.

п

+ Е . d

jri-fKti

rt..j i-t-K+1

-J

oi a 1.

де X UK

14 к

О, у

... n, X- 1,

(i+k) цифра делимого;

01

У,Чк

п делитель на i-м такте}

основание золотой 1-системы счисления; разрядность операндов.

35 ции результата, являющийся первым входом логического условия блока 1, выход 35 результата, выход 36 индикадии

Величина k зависит от максимальной величины ошибки (4j)aKc усечения операндов на i-м такте. Можно по- ошибки, выход 37 индикации готовнос- казать, что эта ошибка может быть ти к работе, являющийся первым выхо- скомпенсирована в последующих тактах Дом блока 1, вход 38 второй констан- деленч, если она не больше . ™ °Д первой константы, выходы Следовательно, .40-42 четвертого, (п+1)-го и (п+4)-го

Алгоритм последовательного деления разрядов распределителя 4 импульсов, кодов золотой 1-пропорции имеет вид: являющиеся иторым, третьим и четвер45 тым входами логического блока 1, шес- 2 0той и пятый входы 43, 44 логического

условия блока 1, пятый и второй выходы 45, 46 блока 1, шестой,седьмой, восьмой, девятый, десятый и одиннад- 50 цатый выходы 47-52 блока 1, первая и вторая групгш выходов 53, 54 блока 1,

В.

В

1+5

.f S,4,X.,, ,чГ,ч

IL , при Z.

0

при 1

выходы 55-57 блока 19, выходы 58-60 блока 20.

-.О. Ь,

где 1«

золотой 1-системы счисления.

10

На фиг. 1 показана схема устройст-- ва для последовательного деления; на фиг. 2 - пример построения блока .микропрограммного управления; на

фиг. 3 - граф состояний и переходов управления; на фиг. 4 - функциональная схема j-ro разряда блока развертки; на фиг. 5 - функциональная схема узла вьщеления ошибки.

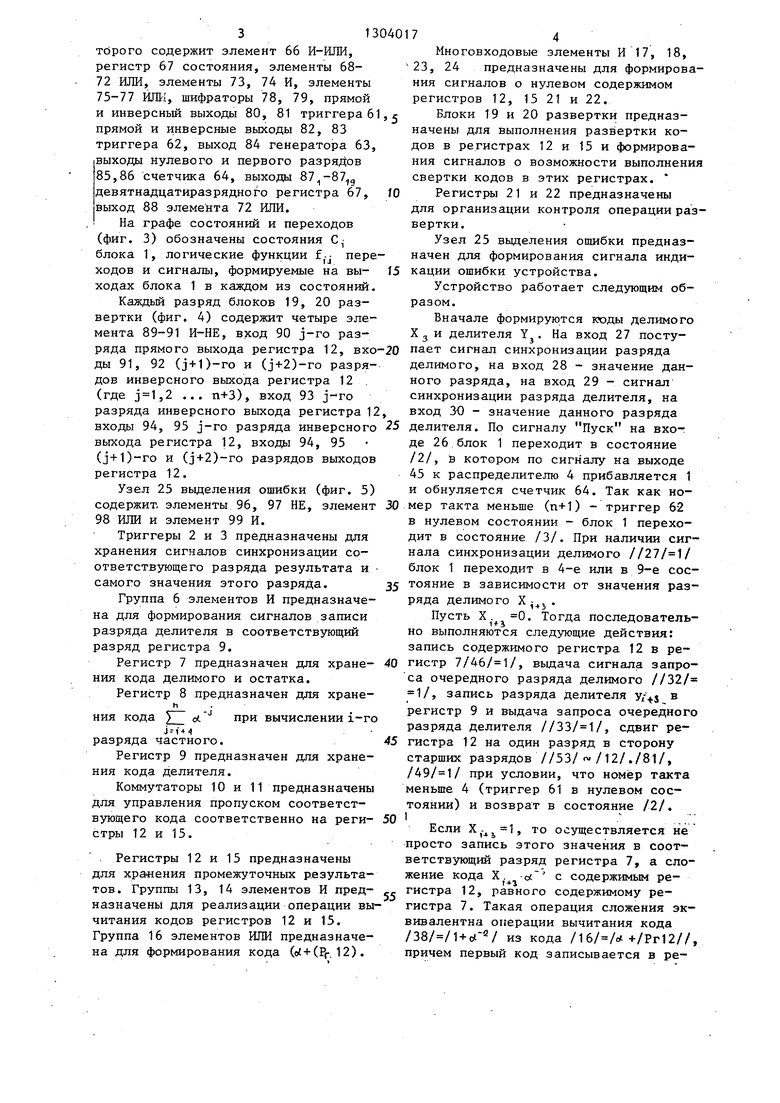

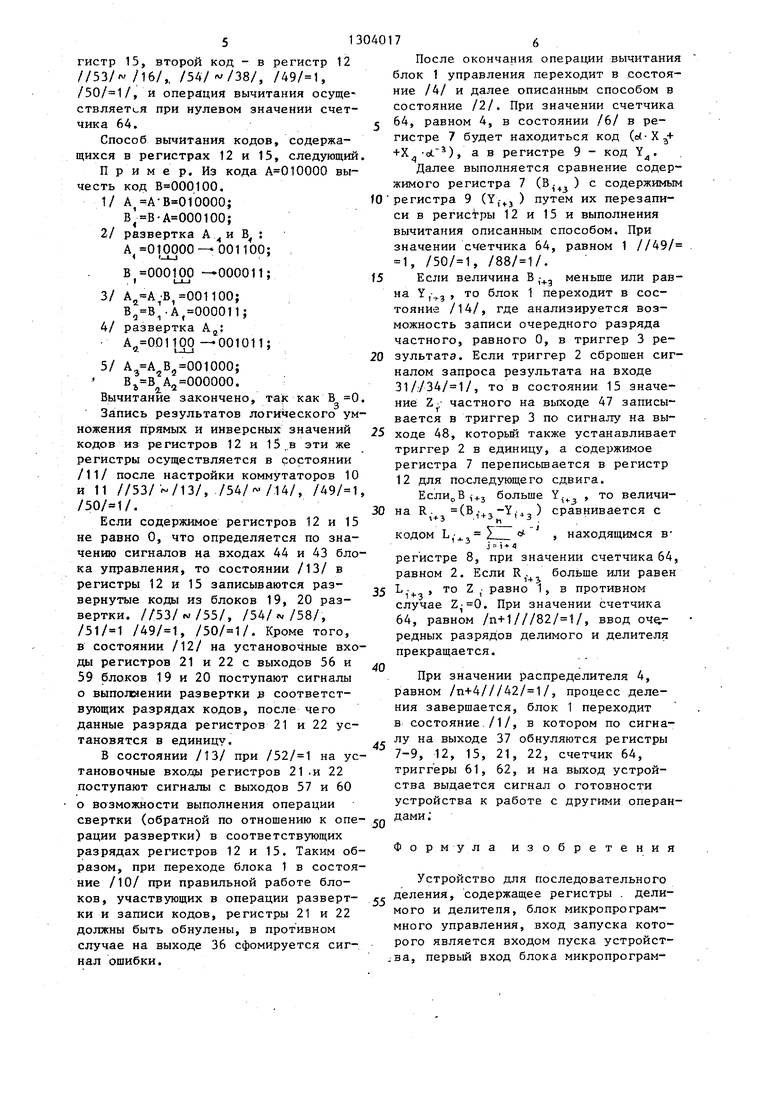

Устройство для последовательного деления (фиг. 1) содержит блок 1 микропрограммного управления, первый, второй триггеры 2, 3, распределитель 4 импульсов, (п+4) выхода 5 распреде15 лителя 4 импульсов, первую группу 6 элементов И, регистр 7 делимого, первый регистр 8, регистр 9 делителя, первый и второй коммутаторы 10, 11, второй 12 регистр, вторую и третью

20 группы 13, 14.элементов И, третий регистр 15, группу элементов 16 ИЛИ, первый и второй элементы 17, 18 И, первый и второй блоки.19, 20 развертки, четвертый и пятый регистры 21,

2 22, третий и .четвертый элементы 23, 24 И, узел 25 вьщеления ошибки, вход 26 пуска, вход 27 синхронизации делимого, вход 28 делимого, вход 29 син- хрониза.дии делителя, вход 30 делите30 ля, вход 31 запроса результата, вы- : ход 32 запроса делимого, являющийся, первым выходом блока 1, выход 33 запроса делителя, являющийся третьим выхрдом блока 1, выход 34 синхрониза35 ции результата, являющийся первым входом логического условия блока 1, выход 35 результата, выход 36 индикадии

- ошибки, выход 37 индикации готовнос- ти к работе, являющийся первым выхо- Дом блока 1, вход 38 второй констан- ™ °Д первой константы, выходы 40-42 четвертого, (п+1)-го и (п+4)-го

выходы 55-57 блока 19, выходы 58-60 блока 20.

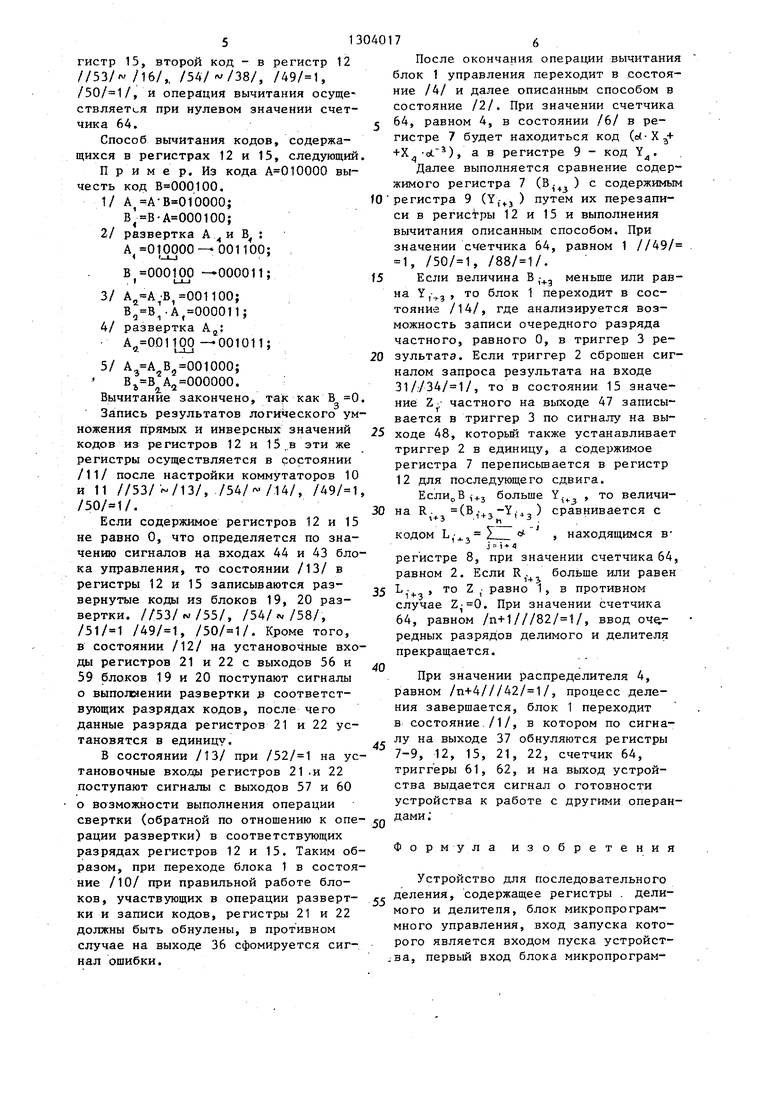

Блок микропрограммного управления (фиг.. 2) содержит триггеры 61, 62, генератор -63 тактовых импульсов, счетчик 64, девятнадцатиразрядный узел установки 65, каждый разряд ко313

тброго содержит элемент 66 И-ИЛИ, регистр 67 состояния, элементы 68- 72 ИЛИ, элементы 73, 74 И, элементы 75-77 ЙШ1, шифраторы 78, 79, прямой и инверсный выходы 80, 81 триггера 61 прямой и инверсные выходы 82, 83 триггера 62, выход 84 генератора 63, выходы нулевого и первого разрядов 85,86 счетчика 64, выходы девятнадцатиразрядного регистра 67, выход 88 элемента 72 ИЛИ.

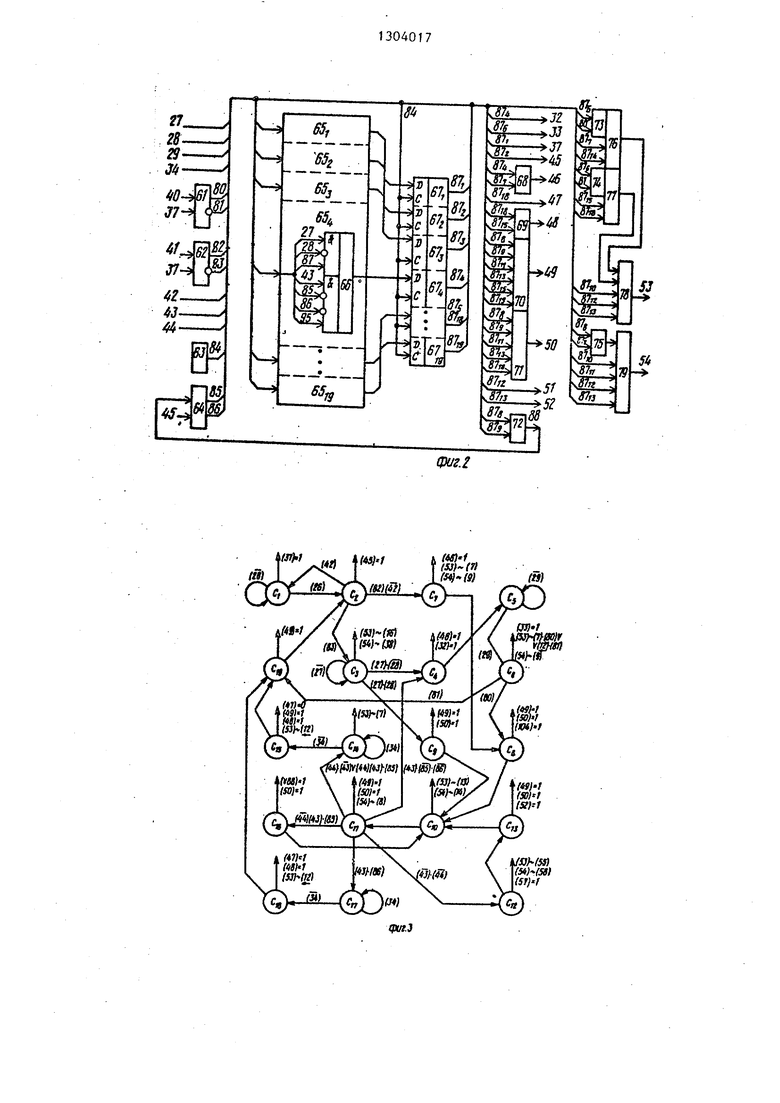

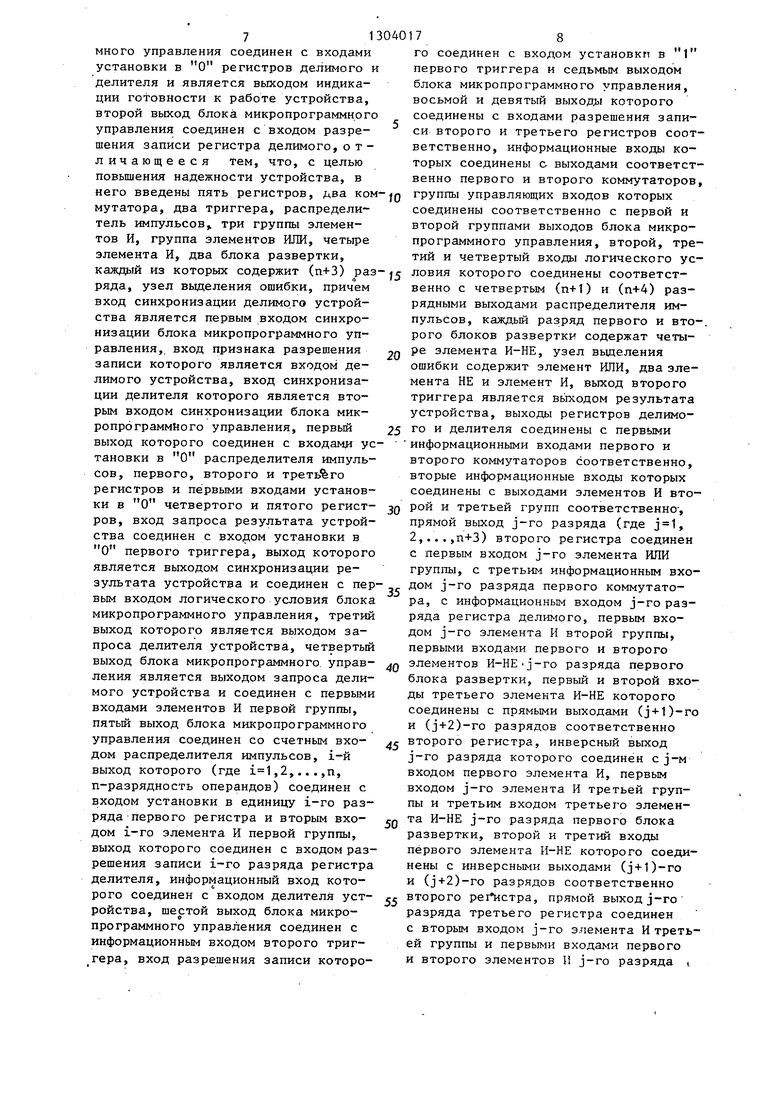

На графе состояний и переходов (фиг. 3) обозначены состояния С, блока 1, логические функции f,-j переходов и сигналы, формируемые на вы- ходах блока 1 в каждом из состояний.

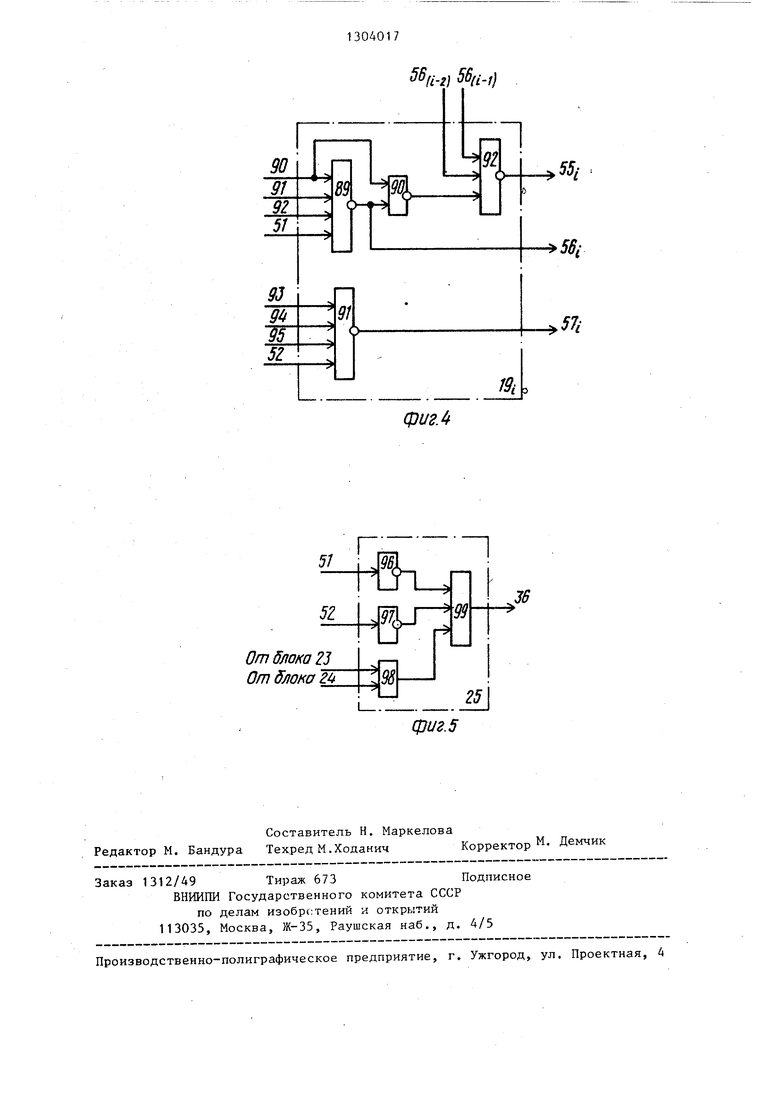

Каждый разряд блоков 19, 20 развертки (фиг. 4) содержит четыре элемента 89-91 И-НЕ, вход 90 j-ro разряда прямого выхода регистра 12, вхо ды 91, 92 (j+1)-ro и (j+2)-ro разрядов инверсного выхода регистра 12 . (где ,2 ... п+3), вход 93 j-ro разряда инверсного выхода регистра 12 входы 94, 95 j-ro разряда инверсного выхода регистра 12, входы 94, 95 (j+1)-ro и (j+2)-ro разрядов выходов регистра 12.

Узел 25 вьщеления ошибки (фиг. 5) содержит, элементы 96, 97 НЕ, элемент 98 ИЛИ и элемент 99 И.

Триггеры 2 и 3 предназначены для хранения сигналов синхронизации соответствующего разряда результата и самого значения этого разряда.

Группа 6 элементов И предназначена для формирования сигналов записи разряда делителя в соответствующий разряд регистра 9.

Регистр 7 предназначен для хране- ния кода делимого и остатка.

Регистр 8 предназначен для хранеh

НИЯ кода о. при вычислении i-ro

разряда частного.

Регистр 9 предназначен для хранения кода делителя.

Коммутаторы 10 и 11 предназначены для управления пропуском соответствующего кода соответственно на реги- стры 12 и 15.

. Регистры 12 и 15 предназначены для хранения промежуточных результатов. Группы 13, 14 элементов И пред- назначены для реализации операции вычитания кодов регистров 12 и 15. Группа 16 элементов ИЛИ предназначена для формирования кода (ot + (Pr. 12).

74

Многовходовые элементы И 17, 18, 23, 24 предназначены для формирования сигналов о нулевом содержимом регистров 12, 15 21 и 22.

Блоки 19 и 20 развертки предназначены для выполнения развертки кодов в регистрах 12 и 15 и формирования сигналов о возможности выполнения свертки кодов в этих регистрах.

Регистры 21 и 22 предназначены для организации контроля операции развертки.

Узел 25 вьщеления ошибки предназначен для формирования сигнала индикации ошибки устройства.

Устройство работает следующим образом.

Вначале формируются коды делимого X 3 и делителя Y. На вход 27 поступает сигнал синхронизации разряда делимого, на вход 28 - значение данного разряда, на вход 29 - сигнал синхронизации разряда делителя, на вход 30 - значение данного разряда делителя. По сигналу Пуск на входе 26 блок 1 переходит в состояние /2/, в котором по сигналу на выходе 45 к распределителю 4 прибавляется 1 и обнуляется счетчик 64. Так как номер такта меньше (п+1) - триггер 62 в нулевом состоянии - блок 1 переходит в состояние /3/. При наличии сигнала синхронизации делимого //27/ 1/ блок 1 переходит в 4-е или в 9-е состояние в зависимости от значения разряда делимого X .

Пусть X. 0. Тогда последовательно выполняются следующие действия: запись содержимого регистра 12 в регистр 7/46/ 1/, выдача сигнала запроса очередного разряда делимого //32/ 1/, запись разряда делителя в регистр 9 и выдача запроса очередного разряда делителя //33/ 1/, сдвиг регистра 12 на один разряд в сторону старших разрядив //53/ /12/./81/, при условии, что номер такта меньше 4 (триггер 61 в нулевом состоянии) и возврат в состояние /2/. I;

Если , то осуществляется не просто запись этого значения в соответствующий разряд регистра 7, а сложение кода X. -ot с содержимым регистра 12, равного содержимому регистра 7. Такая операция сложения эквивалентна операции вычитания кода /38/ /И-ы / из кода /16/ / +/Рг12// причем первый код записывается в ре513

гистр 15, второй код - в регистр 12 //53/ /16/,, /547 /38/, , , и операция вычитания осуще ствляется при нулевом значении счетчика 64.

Способ вычитания кодов, содержащихся в регистрах 12 и 15, следующий

Приме р. Из кода А 010000 вычесть код В 000100.

1/ А,А-В 010000;

В В-А 000100;

27

развертка В

А 010000

В 000100

. t ULJ

001100; -000011;

3/ А5,А;В,001100;

B,. А,000011; 4/ развертка

-001011;

A,0011QQ

5/ В2 001000;

В,В А.000000.

О

Вычитание закончено, так как В 0

Запись результатов логического умножения прямых и инверсных значений кодов из регистров 12 и 15,.в эти же регистры осуществляется в состоянии /11/ после настройки коммутаторов 10 и 11 //53/ /13/, ., .

Если содержимое регистров 12 и 15 не равно О, что определяется по значению сигналов на входах 44 и 43 блока управления, то состоянии /13/ в регистры 12 и 15 записываются развернутые коды из блоков 19, 20 развертки. //53/со/55/, /54/«./58/, , . Кроме того, в состоянии /12/ на установочные входы регистров 21 и 22 с выходов 56 и 59 блоков 19 и 20 поступают сигналы о выполнении развертки р соответствующих разрядах кодов, после чего данные разряда регистров 21 и 22 установятся в единицу.

В состоянии /13/ при на установочные входы регистров 21 -и 22 поступают сигналы с выходов 57 и 60 о возможности выполнения операции свертки (обратной по отношению к one- рации развертки) в соответствующих разрядах регистров 12 и 15. Таким образом, при переходе блока 1 в состояние /10/ при правильной работе блоков, участвующих в операции разверт- ки и записи кодов, регистры 21 и 22 должны быть обнулены, в противном случае на выходе 36 сфомируется сигнал ошибки.

76

После окончания операции вычитания блок 1 управления переходит в состояние /4/ и далее описанным способом в состояние /2/. При значении счетчика 64, равном 4, в состоянии /6/ в регистре 7 будет находиться код (ы-Х +Х -о1- ), а в регистре 9 - код Y.

Далее выполняется сравнение содержимого регистра 7 (В,- ) с содержимьш регистра 9 (Y, ) путем их перезаписи в регис гры 12 и 15 и выполнения вычитания описанным способом. При значении счетчика 64, равном 1 //49/ 1, , .

Если величина В меньше или рав0

5

5

Q с

Q 5

на Y

1-3

то блок 1 переходит в состояние /14/, где анализируется возможность записи очередного разряда частного, равного О, в триггер 3 результата. Если триггер 2 сброшен сигналом запроса результата на входе 31/., то в состоянии 15 значение Z частного на выходе 47 записывается в триггер 3 по сигналу на выходе 48, которьй также устанавливает триггер 2 в единицу, а содержимое регистра 7 переписьюается в регистр 12 для по-следующего сдвига.

больше Y. , то величина R . (B,..j-Y,4i3 ) сравнивается с

кодом L,- Z el , находящимся вj i 1

регистре 8, при значении счетчика 64, равном 2. Если R,-, больше или равен L - , то Z , равно 1, в противном случае . При значении счетчика 64, равном /п+1///82/ 1/, ввод очо.- редных разрядов делимого и делителя прекращается.

При значении распределителя 4, равном /п+4///42/ 1/, процесс деления завершается, блок 1 переходит в состояние,, в котором по сигналу на выходе 37 обнуляются регистры 7-9, 12, 15, 21, 22, счетчик 64, триггеры 61, 62, и на выход устройства выдается сигнал о готовности устройства к работе с другими операндами i

Фор мул а изобретения

Устройство для последовательного деления, содержащее регистры . делимого и делителя, блок микропрограммного управления, вход запуска которого является входом пуска устройст- ;ва, первый вход блока микропрограммного управления соединен с входами установки в О регистров делимого и делителя и является выходом индикации готовности к работе устройства, второй выход блока микропрограммного управления соединен с входом разрешения записи регистра делимого, отличающееся тем, что, с целью повышения надежности устройства, в него введены пять регистров, два KOM-JQ мутатора, два триггера, распределитель импульсов,, три группы элементов И, группа элементов ИЛИ, четыре элемента И, два блока развертки.

го соединен с входом установки в 1 первого триггера и седьмым выходом блока микропрограммного управления, восьмой и девятый BMxop i которого соединены с входами разрешения запи си второго и третьего регистров соо ветственно, информационные входы которых соединены с. выходами соответс венно первого и второго коммутаторов группы управляющих входов которых соединены соответственно с первой и второй группами выходов блока микропрограммного управления, второй, тр тий и четвертый входы логического у

каждый из которых содержит (п+3) раз-jj ловия которого соединены соответстряда, узел выделения ошибки, причем вход синхронизации делимо.го устройства является первым входом синхронизации блока микропрограммного управления,, вход признака разрешения записи которого является входом делимого устройства, вход синхронизации делителя которого является вторым входом синхронизации блока микропрограммного управления, первый выход которого соединен с входамл установки в О распределителя импульсов, первого, второго и третьего регистров и первыми входами установки в О четвертого и пятого регистров, вход запроса результата устройства соединен с входом установки в О первого триггера, выход которого является выходом синхронизации результата устройства и соединен с первым входом логического условия блока микропрограммного управления, третий выход которого является выходом запроса делителя устройства, четвертый выход блока микропрограммного, управления является выходом запроса делимого устройства и соединен с первыми входами элементов И первой группы, пятый выход блока микропрограммного управления соединен со счетным входом распределителя импульсов, i-й выход которого (где ,2,...,n, п-разрядность операндов) соединен с входом установки в единицу i-ro разряда первого регистра и вторым входом i-ro элемента И первой группы, выход которого соединен с входом разрешения записи i-ro разряда регистра делителя, информационный вход которого соединен с входом делителя устройства, шестой выход блока микропрограммного управления соединен с информационным входом второго триггера, вход разрешения записи которо20

25

30

35

венно с четвертым (п+1) и (п+4) разрядными выходами распределителя импульсов, каждый разряд первого и вто рого блоков развертки содержат четыре элемента И-НЕ, узел вьщеления ошибки содержит элемент ИЛИ, два эле мента НЕ и элемент И, выход второго триггера является вь гходом результата устройства, выходы регистров делимого и делителя соединены с первыми информационными входами первого и второго коммутаторов соответственно вторые информационные входы которых соединены с выходами элементов И вто рой и третьей групп соответственно-, прямой выход j-ro разряда (где , 2,...,п+3) второго регистра соединен с первым входом j-ro элемента ИЛИ группы, с третьим информационным вхо дом j-ro разряда первого коммутатора, с информационным входом j-ro раз ряда регистра делимого, первым входом j-ro элемента И второй группы, первыми входами первого и второго элементов И-НЕ j-ro разряда первого блока развертки, первый и второй вхо ды третьего элемента И-НЕ которого соединены с прямыми выходами (j-t-l)-r и (j+2)-ro разрядов соответственно второго регистра, инверсный выход j-ro разряда которого соединен cj-м входом первого элемента И, первым входом j-ro элемента И третьей группы и третьим входом третьего элемента И-НЕ j-ro разряда первого блока развертки, второй и третий входы первого элемента И-НЕ которого соеди нены с инверсными выходами (j+1)-ro и (j+2)-ro разрядов соответственно „ второго ре1 истра, прямой выход j-ro разряда третьего регистра соединен с вторьм входом j-ro элемента И трет ей группы и первыми входами первого и второго элементов И j-ro разряда

40

45

50

го соединен с входом установки в 1 первого триггера и седьмым выходом блока микропрограммного управления, восьмой и девятый BMxop i которого соединены с входами разрешения записи второго и третьего регистров соответственно, информационные входы которых соединены с. выходами соответственно первого и второго коммутаторов, группы управляющих входов которых соединены соответственно с первой и второй группами выходов блока микропрограммного управления, второй, третий и четвертый входы логического усj ловия которого соединены соответст0

5

0

5

венно с четвертым (п+1) и (п+4) разрядными выходами распределителя импульсов, каждый разряд первого и вто-. рого блоков развертки содержат четыре элемента И-НЕ, узел вьщеления ошибки содержит элемент ИЛИ, два элемента НЕ и элемент И, выход второго триггера является вь гходом результата устройства, выходы регистров делимого и делителя соединены с первыми информационными входами первого и второго коммутаторов соответственно, вторые информационные входы которых соединены с выходами элементов И второй и третьей групп соответственно-, прямой выход j-ro разряда (где , 2,...,п+3) второго регистра соединен с первым входом j-ro элемента ИЛИ группы, с третьим информационным входом j-ro разряда первого коммутатора, с информационным входом j-ro разряда регистра делимого, первым входом j-ro элемента И второй группы, первыми входами первого и второго элементов И-НЕ j-ro разряда первого блока развертки, первый и второй входы третьего элемента И-НЕ которого соединены с прямыми выходами (j-t-l)-ro и (j+2)-ro разрядов соответственно второго регистра, инверсный выход j-ro разряда которого соединен cj-м входом первого элемента И, первым входом j-ro элемента И третьей группы и третьим входом третьего элемента И-НЕ j-ro разряда первого блока развертки, второй и третий входы первого элемента И-НЕ которого соединены с инверсными выходами (j+1)-ro и (j+2)-ro разрядов соответственно второго ре1 истра, прямой выход j-ro разряда третьего регистра соединен с вторьм входом j-ro элемента И третьей группы и первыми входами первого и второго элементов И j-ro разряда (

0

5

0

второго блока развертки, первый и второй входы третьего элемента И которого соединены с прямыми выходами (j+1)-ro и (j+2)-ro разрядов соответственно третьего регистра, инверсньй выход j-ro разряда которого соединен с вторым входом j-ro элемента И второй группы, с J-M входом треть- го элемента И и третьим входом третьего элемента И-НЕ j-ro разряда вто- рого блока развертки, второй и третий входы первого элемента И-НЕ которого соединены с инверсными выходами (j+1)-ro и (j+2)-ro разрядов соответственно третьего регистра, четвертые входы первых элементов И-НЕ j-x разрядов первого и второго блока развертки соединены с входом первого элемента НЕ узла вьщеления ошибки и с десятым выходом блока микропрограммного управления, одиннадцатый выход которого соединен с входом второго элемента НЕ узла выделения ошибки и четвертыми входами третьих элементов И j-x разрядов первого и вто- рого блоков развертки, выходы которых соединены с вторыми входами установки в О j-ro разряда четвертого и пятого регистров соответственно, инверсные выходы которых соединены с j-MH входами соответственно третьего и четвертого элементов И, выходы которых соединены с первыми и вторыми входами элемента ИЛИ узла вьщеления .ошибки, выход которого соединен с первым входом элемента И узла выделения ошибки, второй и третий входы которого соединены с выходами первого и второго элементов НЕ, выход элемента И узла выделения ошибки явля- ется выходом индикации ошибки устройства, вход j-ro разряда первой константы устройства является вторым

входом j-ro элемента ИЛИ группы, выход которого является четвертым информационным входом j-ro разряда первого коммутатора, пятый информацион- ньй вход j-ro разряда которого соединен с выходом четвертого элемента И-НЕ J-го разряда первого блока развертки, первый вход которрго соединен с выходом второго элемента И-НЕ j-ro разряда первого блока развертки, второй вход которого соединен с выходом первого элемента И-НЕ j-ro разряда первого блока развертки и входом установки в 1 j-ro разряда четвертого регистра, вход j-ro разряда второй константы устройства является третьим информационным входом j-ro разряда второго коммутатора, четвертый информационный вход которого соединен с выходом первого регистра, пятый информационный вход j-ro разряда второго коммутатора соединен с выходом четвертого элемента И-НЕ j-ro разряда второго блока развертки, первый вход которого соединен с выходом второго элемента И-НЕ j-ro разряда второго блока развертки, второй вход которого Соединен с выходом первого элемента И-НЕ j-ro разряда второго блока развертки и входом установки в 1 j-ro разряда пятого регистра,, второй и Третий входы четвертого элемента И j-ro разряда первого и второго блоков развертки соответственно соединены с выходами первых элементов И (j-1)-ro и (j-2)-ro разрядов соответственно первого и второго бло- ,ков развертки соответственно, выходы первого и второго элементов И соединены с пятым и шестым входами логического условия соответственно блока йикропрограммного управления.

J7

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор кодов с иррациональным основанием | 1991 |

|

SU1837279A1 |

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Устройство для деления | 1988 |

|

SU1552210A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для деления кодов "золотой" пропорции | 1986 |

|

SU1361544A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

| Устройство для контроля и восстановления вычислительного процесса | 1988 |

|

SU1605233A1 |

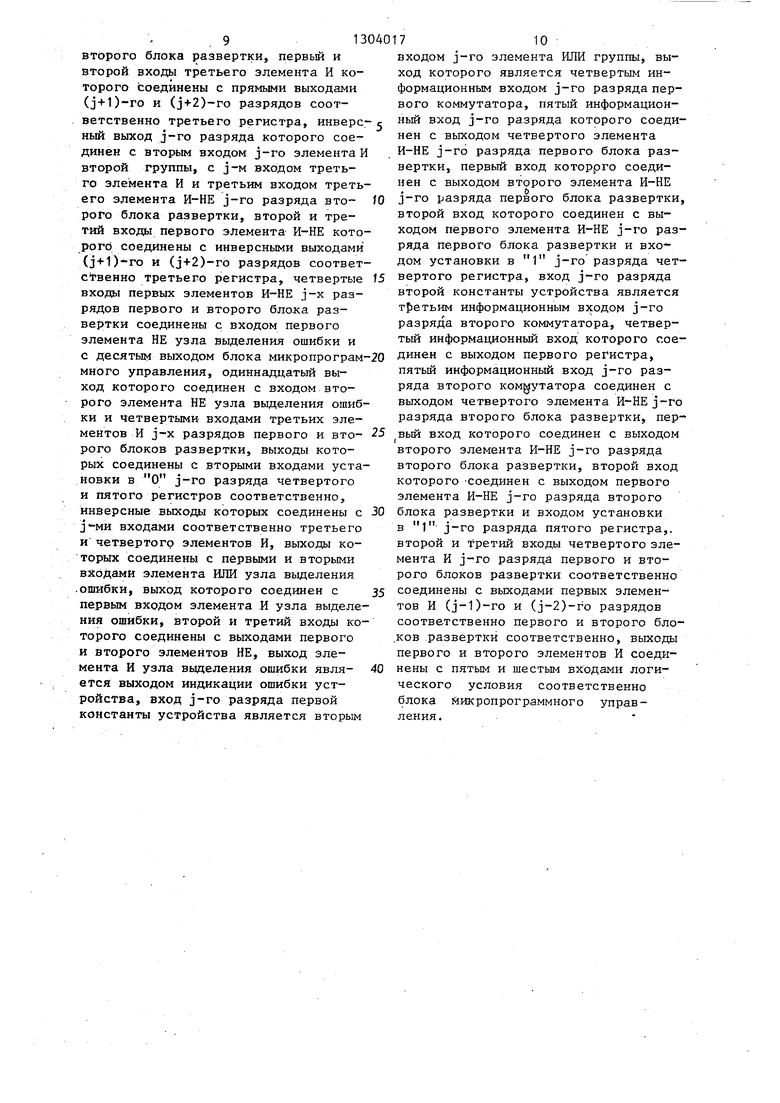

Изобретение относится к цифровой вычислительной технике и может быть использовано в отказоустойчивых процессорах ЦВМ. Целью изобретения является повышение надежности устройства. Это достигается тем, что гбпгггя устройство для последовательного деления, содержащее регистр 7 делимого, регистр 9 делителя, блок 1 микропрограммного управления и функциональные связи, снабжено двумя триггерами 2 и 3, распределителем 4 импульсов, тремя группами элементов И 6, 13 и 14, пятью регистрами 8, 12, 15, 21 и 22, двумя коммутаторами 10, 11, группой элементов ИЛИ 16, четырьмя элементами И 17, 18, 23 и 24, двумя блоками развертки 19 и 20, узлом 25 выделения ошибки и дополнительными функциональными связями, что позволяет для 20-разрядного устройства уменьшить число внешних связей в 5,5 раз, а следовательно, повысить надежность устройства. 5 ил. fi i У 33 а (Л с со о N Wt.i

tit)

ta}

(StHSS) (5I) f

56ц.2) 56fi.f)

фигЛ

От блока 23 От блока 2

фиг. 5

| Стахов А.П | |||

| Коды золотой пропор- ции | |||

| М.: Радио и связь, 1984 | |||

| Устройство для деления | 1983 |

|

SU1151955A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-15—Публикация

1986-07-09—Подача