Изобретение относится к информационно-измерительной технике и может использоваться в технике магнитной записи. . .

Цель изобретения - повьшение информативности и точности устройства.

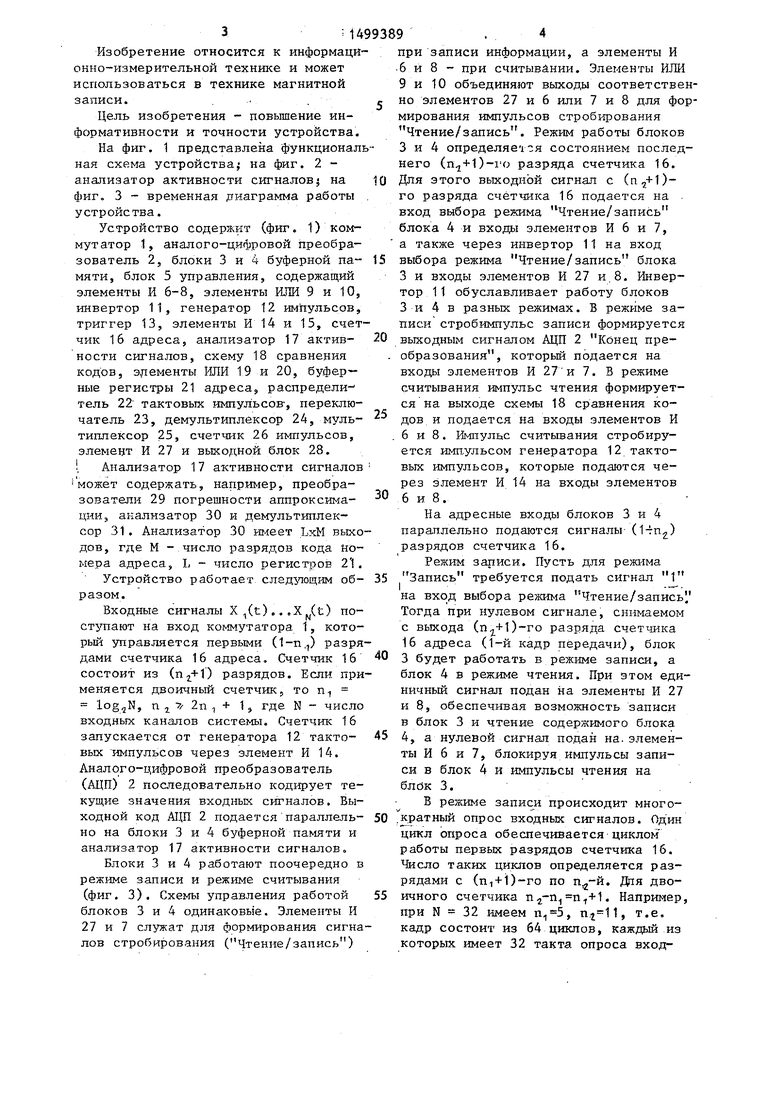

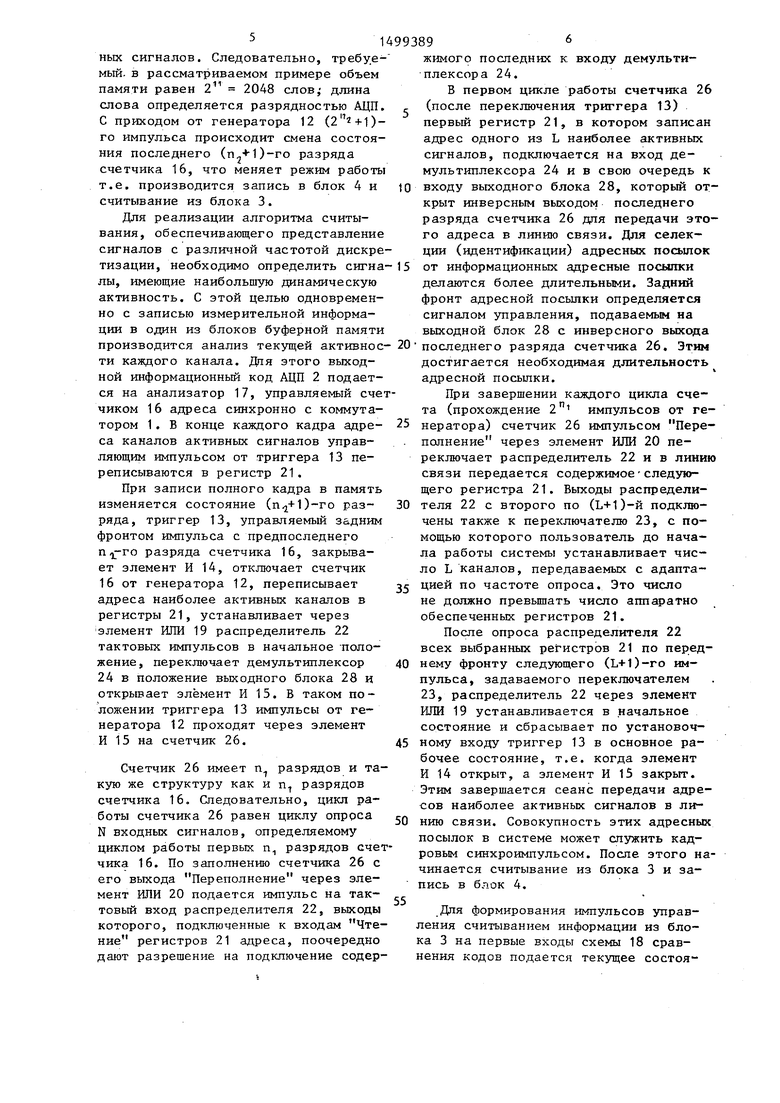

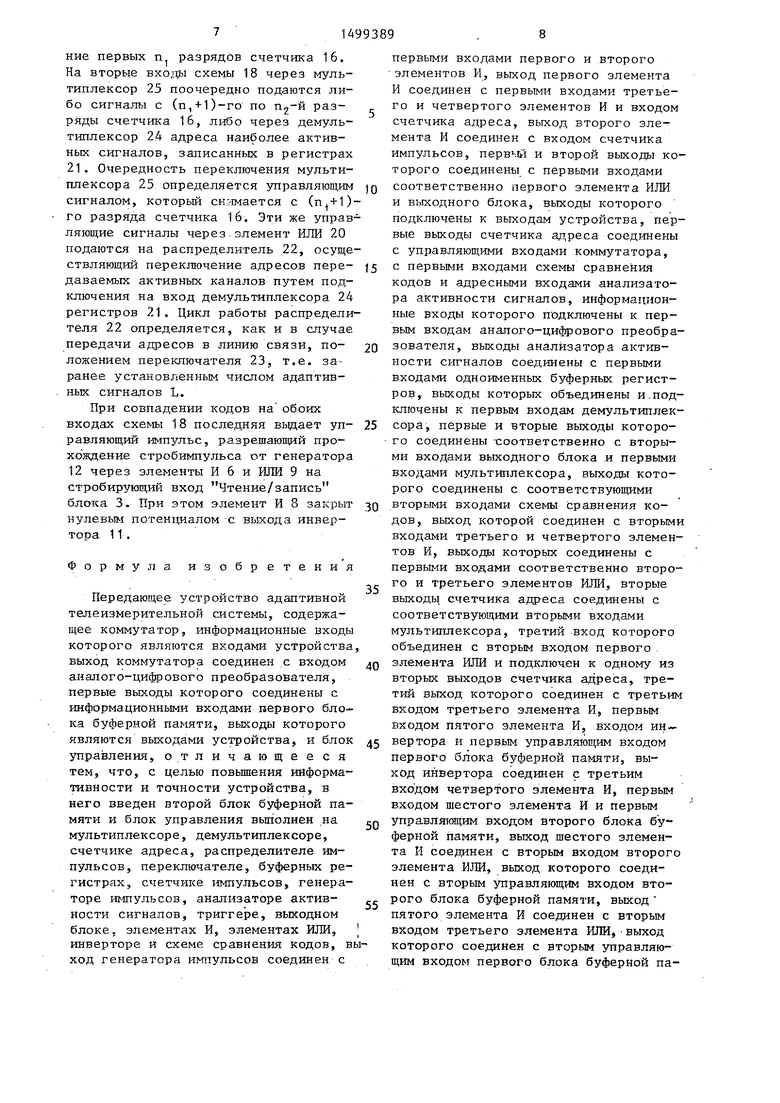

На фиг. 1 представлена функциональная схема устройстваJ на фиг. 2 - анализатор активности сигналов на фиг, 3 - временная диаграмма работы устройства.

Устройство содержит (фиг. 1) коммутатор 1, аналого-цифровой преобразователь 2, блоки 3 и 4 буферной па- мяти, блок 5 управления, содержащий элементы И 6-8, элементы ИЛИ 9 и 10, инвертор 11, генератор 12 импульсов, триггер 13, элементы И 14 и 15, счетчик 16 адреса, анализатор 17 актив- ности сигналов, схему 18 сравнения кодов, элементы ИЛИ 19 и 20, буферные регистры 21 адреса, распределитель 22 тактовых импульсов, переключатель 23, демультиплексор 24, муль- типлексор 25, счетчик 26 импульсов, элемент И 27 и выходной блок 28. , Анализатор 17 активности сигналов может содержать, например, преобразователи 29 погрешности аппроксима- ции, анализатор 30 и демультиплексор 31. Анализатор 30 LxM выходов, где М -.число разрядов кода номера адреса, L - число регистров 21.

Устройство работает, cлeдs oш,им об- разом.

Входные сигналы X(t)...X (t) по- на вход коммутатора 1, который управляется первыми (1-п,,) разрядами счетчика 16 адреса. Счетчик 16 состоит из () разрядов. Если применяется двоичный счетчик, то п log,jN, п 2. 7 2п , + 15 где N - число входных каналов системы. Счетчик 16 запускается от генератора 12 такто- вых импульсов через элемент И 14. Аналого-цифровой преобразователь (АЦП) 2 последовательно кодирует текущие значения входных сигналов. Выходной код АЦП 2 подается параллель- но на блоки 3 и 4 буферной памяти и анализатор 17 активности сигналов.

Блоки 3 и 4 работают поочередно в режиме записи и режиме считывания (фиг. 3), Схемы управления работой блоков 3 и 4 одинаковые. Элементы И 27 и 1 служат для формирования сигналов стробирования (Чтение/запись)

ри записи информации, а элементы И 6 и 8 - при считывании. Элементы ИЛИ 9 и 10 объединяют выходы соответствено элементов 27 и 6 или 7 и В для форирования импульсов стробирования Чтение/запись. Режим работы блоков 3 и 4 определяемся состоянием последнего ()-1 о разряда счетчика 16. ля этого выходной сигнал с (n,+ 1)- го разряда счётчика 16 подается на . вход выбора режима Чтение/запись блока 4 и входы элементов И 6 и 7, а также через инвертор 11 на вход выбора режима Чтение/запись блока 3 и входы элементов И 27 и,8. Инвертор 11 обуславливает работу блоков 3 и 4 в разных режимах. В режиме записи стробимпульс записи формируется выходным сигналом АЦП 2 Конец преобразования, который подается на входы элементов И 27 и 7. В режиме считывания импульс чтения формируется на выходе схемы 18 сравнения кодов и подается на входы элементов И 6 и 8. Импульс считывания стробиру- ется импульсом генератора 12 тактовых импульсов, которые подаются через элемент И 14 на входы элементов 6 и 8.

На адресные входы блоков 3 и 4 параилельно подаются сигналы- (Нп) разрядов счетчика 16.

Режим записи. Пусть для режима Запись требуется подать сигнал 1

на вход выбора режима Чтение/запись Тогда при нулевом сигнале, снимаемом с выхода ()-го разряда 16 адреса (1-й кадр передачи), блок 3 будет работать в режиме записи, а блок 4 в режиме чтения. При этом единичный сигнал подан на элементы И 27 и 8, обеспечивая возможность записи в блок 3 и чтение содержимого блока 4, а нулевой сигнал подан на. элементы И 6 и 7, блокируя импульсы записи в блок 4 и импульсы чтения на бльк 3. .

в режиме записи происходит много- кратный опрос входных сигналов. Один цикл опроса обеспечивается циклом работы первых разрядов счетчика 15. Число таких циклов определяется разрядами с (ni + 1)-ro по П.2-Й. Для двоичного счетчика . Например, при N 32 имеем п,5, n., т.е. кадр состоит из 64 циклов, каждый из которых имеет 32 такта опроса входных сигналов. Следовательно, требу.е- мый. в рассматриваемом примере объем памяти равен 2048 слов,- длина слова определяется разрядностью АЦП. С приходом от генератора 12 ()- го импульса происходит смена состояния последнего (п +О-го разряда счетчика 16, что меняет режим работы т.е. производится запись в блок 4 и считывание из блока 3.

Для реализации алгоритма считывания, обеспечивающего представление

В первом цикле работы счетчика 26 (после переключения триггера 13) первый регистр 21, в котором записан адрес одного из L наиболее активных сигналов, подключается на вход де- мультиплексора 24 и в свою очередь к входу выходного блока 28, который от крыт инверсным выходом последнего разряда счетчика 26 дпя передачи этого адреса в линию связи. Для селекции (идентификации) адресных посылок

сигналов с различной частотой дискретизации, необходимо определить сигна-15 от информационных адресные посыпки лы, имеющие наибольшую динамическую делаются более длительными. Задний активность. С этой целью одновремен- фронт адресной посылки определяется но с записью измерительной информа- сигналом управления, подаваемым на ции в один из блоков буферной памяти выходной блок 28 с инверсного выхода производится анализ текущей активное- 20 последнего разряда счетчика 26. Этим ти каждого канала. Дпя этого выход- достигается необходимая длительность ной информационный код АЦП 2 подает- адресной посылки.

ся на анализатор 17, управляемый счет- При завершении каждого цикла сче- чиком 16 адреса синхронно с коммута- та (прохождение 2 импульсов от ге- тором 1. В конце каждого кадра адре- 25 нератора) счетчик 26 импульсом Переса каналов активных сигналов управ- . полнение через элемент ИЛИ 20 пе- ляющим импульсом от триггера 13 пе- реключает распределитель 22 и в линию реписываются в регистр 21.связи передается содержимое следуюПри записи полного кадра в память изменяется состояние (п,+1)-го разряда, триггер 13, управляемый задним фронтом импульса с предпоследнего разряда счетчика 16, закрывает элемент И 14, отключает счетчик 16 от генератора 12, переписывает адреса наиболее активных каналов в регистры 21, устанавливает через элемент ИЛИ 19 распределитель 22

щего регистра 21. Выходы распредели30 теля 22 с второго по (Ь+1)-й подключены также к переключателю 23, с помощью которого пользователь до начала работы системы устанавливает число L каналов, передаваемых с адапта35 цией по частоте опроса. Это число не должно превьш1ать число аппаратно обеспеченных регистров 21.

После опроса распределителя 22 всех выбранных регистров 21 по передтактовых импульсов в начальное положение, переключает демультиплексор 24 в положение выходного блока 28 и открывает элемент И 15. В таком положении триггера 13 импульсы от генератора 12 проходят через элемент И 15 на счетчик 26.

Счетчик 26 имеет п разрядов и такую же структуру как и п разрядов счетчика 16. Следовательно, цикл работы счетчика 26 равен циклу опроса N входных сигналов, определяемому циклом работы первых п разрядов счетчика 16. По заполнению счетчика 26 с его выхода Переполнение через элемент ИЛИ 20 подается импульс на тактовый вход распределителя 22, выходы которого, подключенные к входам Чтение регистров 21 адреса, поочередно дают разрешение на подключение содер0

жимого последних к входу демульти- плексора 24.

В первом цикле работы счетчика 26 (после переключения триггера 13) первый регистр 21, в котором записан адрес одного из L наиболее активных сигналов, подключается на вход де- мультиплексора 24 и в свою очередь к входу выходного блока 28, который от крыт инверсным выходом последнего разряда счетчика 26 дпя передачи этого адреса в линию связи. Для селекции (идентификации) адресных посылок

5 от информационных адресные посыпки делаются более длительными. Задний фронт адресной посылки определяется сигналом управления, подаваемым на выходной блок 28 с инверсного выхода 0 последнего разряда счетчика 26. Этим достигается необходимая длительность адресной посылки.

щего регистра 21. Выходы распределителя 22 с второго по (Ь+1)-й подключены также к переключателю 23, с помощью которого пользователь до начала работы системы устанавливает число L каналов, передаваемых с адаптацией по частоте опроса. Это число не должно превьш1ать число аппаратно обеспеченных регистров 21.

После опроса распределителя 22 всех выбранных регистров 21 по переднему фронту следующего (L+1)-ro импульса, задаваемого переключателем 23, распределитель 22 через элемент ИЛИ 19 устанавливается в начальное состояние и сбрасывает по установоч-

ному входу триггер 13 в основное рабочее состояние, т.е. когда элемент И 14 открыт, а элемент И 15 закрыт. Этим завершается сеанс передачи адресов наиболее активных сигналов в линию связи. Совокупность этих адресных посылок в системе может кадровым синхроимпульсом. После этого начинается считывание из блока 3 и запись в блок 4.

Для формирования импульсов управления считыванием информации из блока 3 на первые входы схемы 18 сравнения кодов подается текущее состояние первых п. разрядов счетчика 16. На вторые входа схемы 18 через мультиплексор 25 поочередно подаются либо сигналы с (п,+1)-го по разряды счетчика 16, либо через демуль- типлексор 2А адреса наиболее актив- ньк сигналов, записанных в регистрах 21. Очередность переключения мультиплексора 25 определяется управляющим сигналом, который снимается с ()- го разряда счетчика 16. Эти же управляющие сигналы через.элемент ИЛИ 20 подаются на распределитель 22, осуществляющий переключение адресов пере- даваемых активных каналов путем подключения на вход демультиплексора 24 регистров 21. Цикл работы распределителя 22 определяется, как и в случае передачи адресов в линию связи, по- ложением переключателя 23, т.е. заранее установленным числом адаптивных сигналов L.

При совпадении кодов на обоих входах схемы 18 последняя вьщает уп- равляющий импульс, разрешающий про- хо ждение стробимпульса от генератора 12 через элементы И 6 и ИЛИ 9 на стробирующий вход Чтение/запись блока 3. При этом элемент И 8 закрыт нулевым потенциалом с выхода инвер- тооа 11.

Формула изобретения

Передающее устройство адаптивной телеизмерительной cиcтe ЯзI, содержащее коммутатор, информационные входы которого являются входами устройства выход коммутатора соединен с входом аналого-цифрового преобразователя, первые выходы которого соединены с информационными входами первого блока буферной памяти, выходы которого являются выходами устройства, и блок управления, отличающееся тем, что, с целью повьшения информативности и точности устройства, в него введен второй блок буферной памяти и блок управления вьтолнен ,на мультиплексоре, демультиплексоре, счетчике адреса, распределителе импульсов, переключателе, буферных регистрах, счетчике io-шульсов, генераторе импульсов, анализаторе актив- ности сигналов, триггере, выходном блоке, элементах И, элементах ИЛИ, инверторе и схеме сравнения кодов, вход генератора импульсов соединен с

0

5 о

5

д 5 Q первыми входами первого и второго элементов И, выход первого элемента И соединен с первыми входами третьего и четвертого элементов И и входом счетчика адреса, выход второго элемента И соединен с входом счетчика импульсов, первой и второй выходы которого соединены с первыми входами соответственно первого элемента ИЛИ и выкодного блока, выходы которого подключены к выходам устройства, первые выходы счетчика адреса соединены с управляющими входами коммутатора, с первыми входами схемы сравнения кодов и адресными входами анализатора активности сигналов, информационные входы которого подключены к первым входам аналого-цифрового преобразователя, выходы анализатора активности сигналов соединены с первыми входами одноименных буферных регистров, выходы которых объединены и.подключены к первым входам демультиплексора, первые и вторые выходы которого соединены -соответственно с вторыми входами выходного блока и первыми входами мультиплексора, выходы которого соединены с соответствующими вторыми входами схемы сравнения кодов, выход которой соединен с вторыми входами третьего и четвертого элементов И, выходы которых соединены с первыми входами соответственно второго и третьего элементов ИЛИ, вторые выходы счетчика адреса соединены с соответствующими вторыми входами мультиплексора, третий вход которого объединен с вторым входом первого элемента ИЛИ и подключен к одному из вторьк выходов счетчика адреса, третий выход которого соединен с третьим входом третьего элемента И, первым входом пятого элемента И, входом инвертора и первым управляющим входом первого блока буферной памяти, выход инвертора соединен с третьим входом четвертого элемента И, первым входом шестого элемента И и первым управляющим входом второго блока буферной памяти, выход шестого элемента И соединен с вторым входом второго элемента ИЖ, выход которого соединен с вторым управляющим входом второго блока буферной памяти, выход пятого элемента И соединен с вторым входом третьего элемента ИЛИ,выход которого соединен с вторым управляющим входом первого блока буферной памяти, первый выход триггера соединен с вторыми входами первого элемента И, демультиплексора и буферных регистров адреса и первым входом четвертого элемента ИЛИ, выход которого и выход первого элемента ИЛИ соединены соответственно с первым и вторым входами распределителя импульсов, выхотого элемента и первым входом триггера, второй выход которого соединен с вторым входом второго элемен та И, второй выход аналого- цифрово- го преобразователя соединен с вторыми входами пятого и шестого элементов И, первые и вторые выходы счетчика адреса соединены с адресными

ды которого, кроме последнего, соеди- ювходами первого и второго блока бунены с третьими входами соответствую-ферной памяти, информационные входы

щих буферных регистров, первые и вто-которого подключены к первым выходам

рой выводы.переключателя соединеныаналого-цифрового преобразователя,

соответственно с соответствующими вы-выходы второго блока буферной памяти

ходами, кроме первого, распределите- 15подключены к выходу устройства, ля импульсов и вторым входом четвертого элемента и первым входом триггера, второй выход которого соединен с вторым входом второго элемента И, второй выход аналого- цифрово- го преобразователя соединен с вторыми входами пятого и шестого элементов И, первые и вторые выходы счетчика адреса соединены с адресными

| название | год | авторы | номер документа |

|---|---|---|---|

| Передающее устройство адаптивной телеизмерительной системы | 1989 |

|

SU1679517A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Устройство для индикации | 1990 |

|

SU1795511A1 |

| Устройство для формирования тестов памяти | 1989 |

|

SU1711235A1 |

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОММУТАЦИИ СООБЩЕНИЙ | 2009 |

|

RU2416121C2 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для приема и обработки информации | 1989 |

|

SU1603418A1 |

Изобретение относится к информационно-измерительной технике и может быть использовано в тех случаях, когда требуется сокращение избыточности при дискретном представлении сигналов. Цель изобретения - повышение информативности и точности устройства. Устройство содержит коммутатор 1, аналого-цифровой преобразователь 2, блоки 3 и 4 буферной памяти, блок 5 управления, содержащий элементы И 6,7,8,14,15,27, элементы ИЛИ 9,10,19,20, инвертор 11, генератор 12 импульсов, триггер 13, счетчик 16 адреса, анализатор 17 активности сигналов, схему 18 сравнения кодов, буферные регистры 21 адреса, распределитель 22 тактовых импульсов, переключатель 23, демультиплексор 24, мультиплексор 25, счетчик 26 импульсов и выходной блок 28. 3 ил.

Л

...

КЦ

W

П1

Фиг.2

| Авдеев Б.Я | |||

| и др | |||

| Адаптивные телеизмерительные системы | |||

| - Л.: Энерго- издат, 1981, с | |||

| Способ крашения тканей | 1922 |

|

SU62A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-07—Публикация

1988-01-11—Подача