4(23вШ

||ка.1Ж

00

4

СО

Изобретение относится к вычислительной технике и может быть использовано для операций над матрицами.

Целью изобретения является повышение, быстродействия

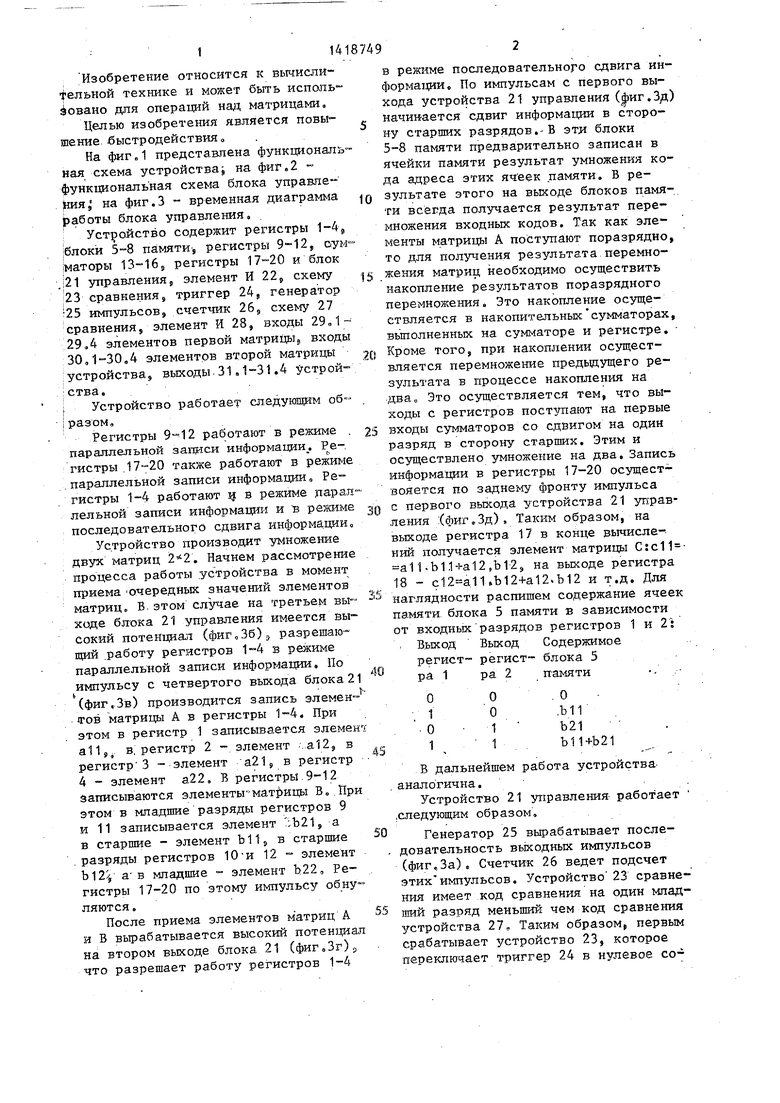

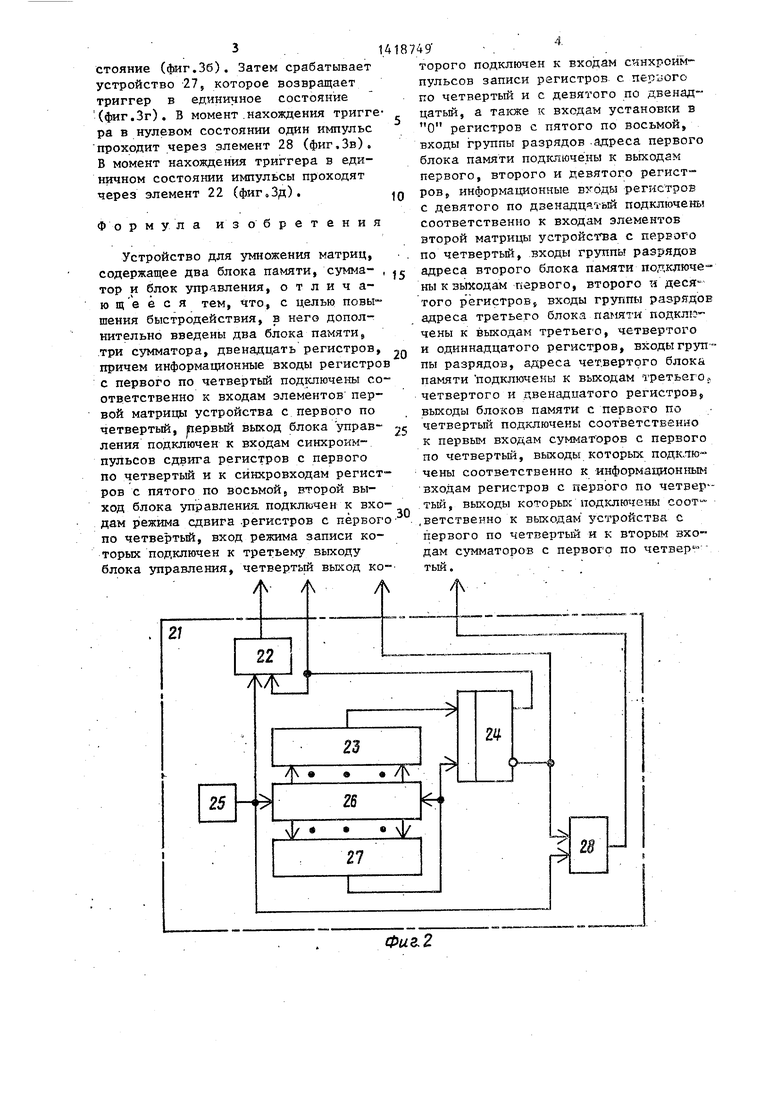

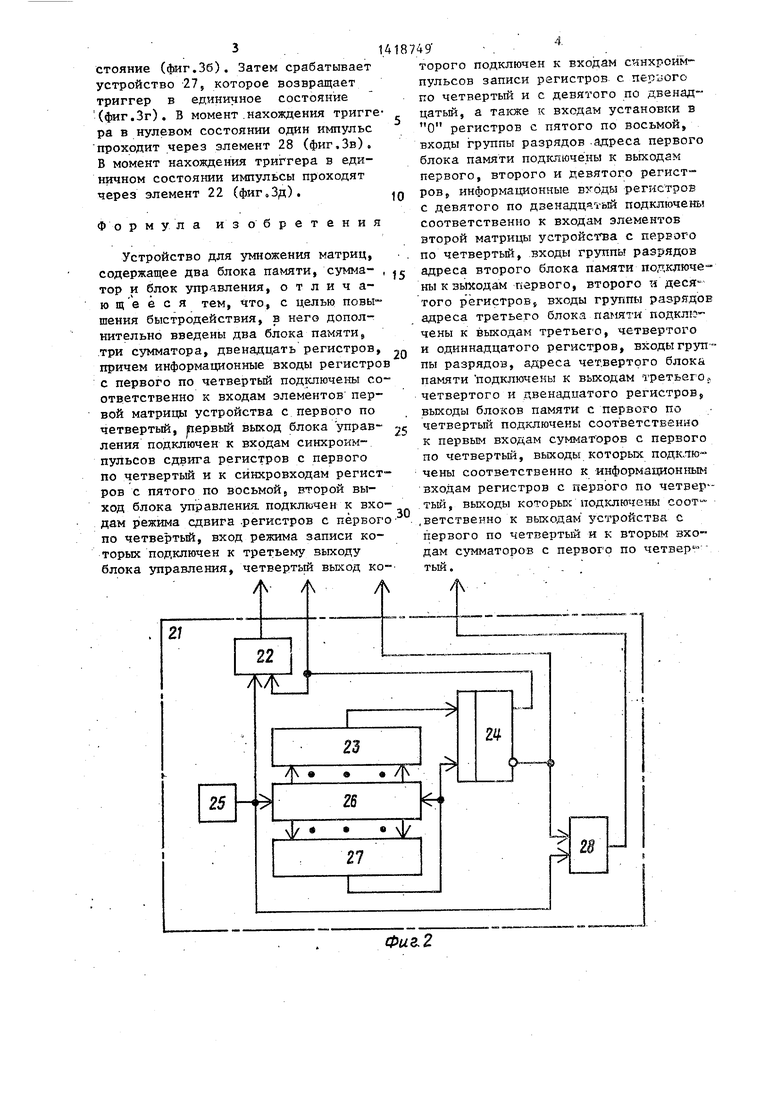

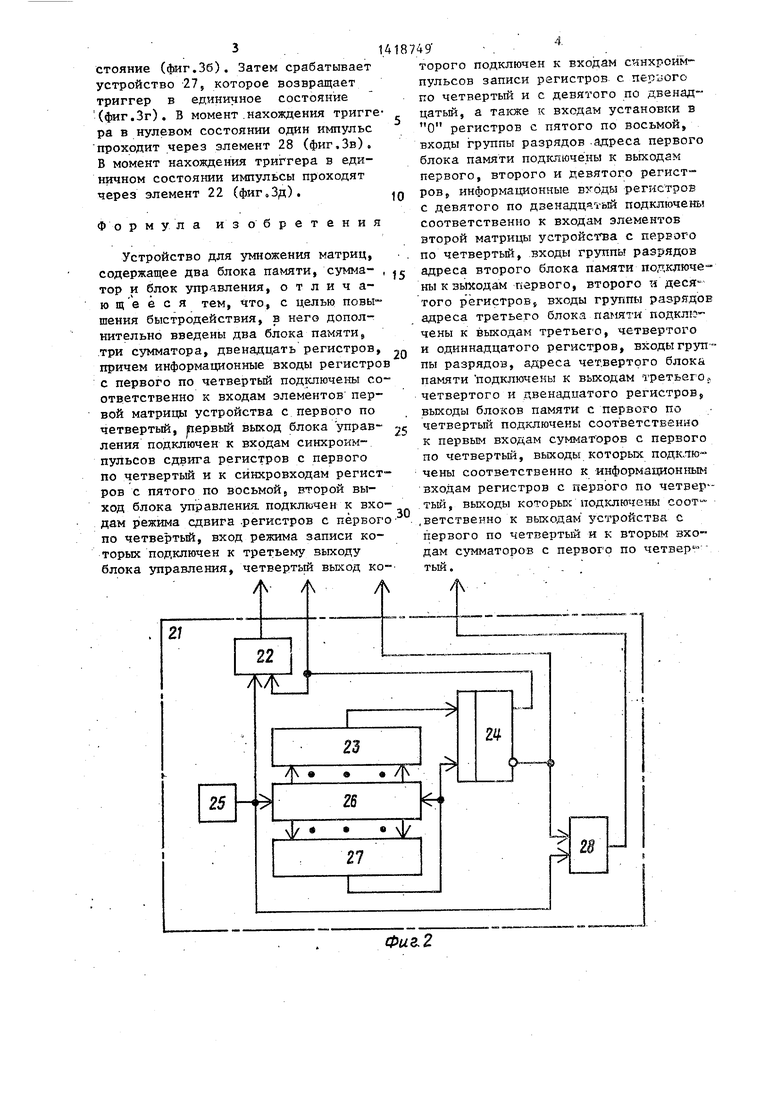

На фиг.1 представлена функциональная схема устройства, на фиг.2 - функциональная схема блока управле- щя, на фиг.З - временная диаграмма работы блока управления, ; Устройство содержит рег- истры 1-4, |блокй 5-8 памяти, регистры 9-12, сум |маторы 13-16j регистры 17--20 и блок

.121 управления, элемент И 22 схему |23 сравнения, триггер 24, генератор 25 импульсов, счетчик 26д схему 27 сравнения, элемент И 28, входы 29И- 29,4 элементов первой матрицы, входы 30,1-30,4 элементов второй матрицы

:устройства9 выходы.31 а 1-31.4 устрой:ства.

i Устройство работает сл.едующим обI разом,:

Регистры работают в режиме . параллельной записи информации. гистры . 17-20 также работают в режиме

.параллельной записи информации. Регистры 1-4 работают щ в режиме дарап лельной записи информации и в ратгсиме последовательного сдвига информа.цнис

Устройство производит умножение двух матриц 22. Начнем рассмотрение процесса работы устройства в момент приема очередньк значений элементов матриц. В. этом случае на третьем вы ходе блока 21 управления имеется высокий потенциал (фиг,36) разрешающий .работу регистров в режиме параллельной записи информации. По импульсу с четвертого выхода блока 21 (фиГгЗв) производится запись элемен тов матрицы А в регистры 1--4, При этом в регистр 1 записывается элемен all, в, регистр 2 - элемент .a12, в регистр 3 - элемент а21, в регистр 4 - элемент а22. В регистры 9-12 записываются элементы мат)ицы В „.При этом в младшие разряды регистров 9 и 11 записывается элемент :Ь21,) а в старпше - элемент Ъ11j в старшие

.разряды регистров 10-и 12 - элемент Ь12, а в младшие - элемент Ь.22, Ре- гистры 17-20 по этому импульсу обнуляются.

После приема элементов матриц А и В вырабатывается высокий потеш.щат1 на втором выходе блока 21 (фиГоЗг) что разрешает работу регистров 1-4

0

5 .

0

5

0

5

в режиме последовательного сдвига информации. По импульсам с первого выхода устройства 21 управления (фиг,Зд) начинается сдвиг информации в сторону старших разрядов.-В этл блоки 5-8 памяти предварительно записан в ячейки памяти результат умножения кода адреса этих ячеек памяти. В результате этого на выходе блоков памя-. ти всегда получается результат перемножения входньк кодов. Так как элементы матрицы А поступают поразрядно, то для получения результата перемножения матриц необходимо осуществить накопление результатов поразрядного перемножения. Это накопление осуществляется в накопительных сумматорах, вьшолненных на сумматоре и регистре. - Кроме того, при накоплении осуществляется перемножение предыдущего результата в процессе накопления на два о Это осуществляется тем, что выходы с регистров поступают на первые входы сумматоров со сдвигом на один разряд в сторону старших. Этим и осуществлено умножение на два. Запись информации в регистры 17-20 осущест- вояется по заднему фронту импульса с первого выхода устройства 21 управления ;(фиг,3д) , Таким образом, на выходе регистра 17 в конце вычислений получается элемент матрицы a11-Ы .1+а12|,Ъ12,, на выходе регистра 18 - .b12+a12.b12 и т.д. Для наглядно.сти распишем содержание ячеек памяти блока 5 памяти в зависимости от входных разрядов регистров 1 и 2; , В.ЫХОД Выход Содержимое

регист- регист- блока 5

ра 1 ра 2 памяти -.

О 1 О 1

О

о 1 1

о

.Ъ1Г

Ь21

Ь1НЬ21

5

В дальнейшем работа устройства, аналогична. . .

Устройство 21 управления работает

.следующим образом,

Генератор 25 вьграбатывает последовательность вь1ходных импульсов (фиг,За), Счетчик 26 ведет подсчет этих импульсов. Устройство 23 сравнения имеет код сравнения на один мпад- ший разряд меньший чем код сравнения устройства 27 о Таким образом, первым срабатывает устройство 23, которое переключает триггер 24 в нулевое состояние (фиг.36). Затем срабатывает устройство 27, которое возвращает триггер в единичное состояние (фиг.Зг). В момент .нахождения тригге ра в нулевом состоянии один импульс проходит через элемент 28 (фиг.Зв), В момент нахождения триггера в единичном состоянии импульсы проходят через элемент 22 ().

Формула изобретения

Устройство для умножения матриц, содержащее два блока памяти, сумма- , тор и блок управления, о т л и ч а ю щ е ё с я тем, что, с целью повышения быстродействия, в него дополнительно введены два блока памятиj .три сумматора, двенадцать регистров, причем информационные входы регистров с первого по четвертый под1слючены соответственно к входам элементов первой матрицы устройства с первого по четвертый, й.ервый выход блока зшрав- ления подключен к входам синхроимпульсов сдвига регистров с первого по четвертый и к сйнхровходам регистров с пятого по восьмойJ второй выход блока управления, подключен к входам режима сдвига .регистров с первого по четвертый, вход режима записи которых подключен к третьему выходу блока управления, четвертьй выход ко10

15

418749 .

торого подключен к входам синхроимпульсов записи регистров с первого по четвертый и с девятого по двенад цатьй, а также к входам установки в О регистров с пятого по восьмой, входы группы разрядов .адреса первого блока памяти подключены к выходам первого, второго и девятого регистров, информационные входы регистров с девятого по двенадця1 ый подключены соответственно к входам элементов второй матрицы устройства с первого по четвертьй, входы группы разрядов адреса второго блока памяти подключены к выходам первого, второго и десятого регистров, входы группы разрядов адреса третьего блока памяти подключены к выходам третьего, четвертого и одиннадцатого регистров, входыгруп- пы разрядов, адреса четвертого блока памяти подключены к выходам третьего., четвертого и .двенадиатого регистров, выходы блоков памяти с первого по четвертьш подключены соответственно к первым входам сумматоров с первого по четвертьй, выходы которых подключены соответственно к информационным входам регистров с первого по четвертьй, выходы которых подключены ссот- ветственно к выходам устройства с первого по четвертьй и к вторым входам сумматоров с первого по четвер тый.

20

25

30

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления преобразования Фурье-Галуа и свертки | 1985 |

|

SU1295415A1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

| Устройство для обработки изображений | 1991 |

|

SU1836693A3 |

| Устройство для решения систем алгебраических уравнений | 1986 |

|

SU1324036A1 |

| Устройство для умножения матриц | 1991 |

|

SU1807499A1 |

| Устройство для вычисления суммы произведений двух массивов чисел | 1980 |

|

SU985782A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Устройство для решения системы алгебраических уравнений | 1982 |

|

SU1024932A2 |

| Многоканальный многомерный цифровой коррелометр | 1984 |

|

SU1187177A1 |

Изобретение относится к вычисли тельной технике и может быть использовано для операций над матрицами. Целью изобретения является повьшение быстродействия. Устройство содержит регистры 1-4, блоки 5-8 памяти,, регистры 9-12, сумматоры 13-16,.регистры 17-20, блок 21 управления. В устройстве осуществляется одновременное вычисление всех элементов результиру- кяцей матрицы. „ 3 ил,

Фив.2

а

1 I I I I I I I i I I 1 I LI ULJJ L

3

1 i M i 1 I i 1 I 11LLLLM

Фие.З

| Однородная параллельная вычислительная структура для вычисления произведения матрицы на вектор | 1984 |

|

SU1236500A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для операций над матрицами | 1976 |

|

SU647687A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-23—Подача