(5) УСТРОЙСТВО для ВЫЧИСЛЕНИЯ СУММЫ ПРОИЗВЕДЕНИЙ ДВУХ МАССИВОВ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления суммпРОизВЕдЕНий упОРядОчЕННыХ МАССиВОВчиСЕл | 1978 |

|

SU807280A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для вычисления коэффициентов цифрового фильтра | 1981 |

|

SU987804A1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для потенцирования | 1990 |

|

SU1815635A1 |

| Устройство для вычисления скользящего среднего | 1988 |

|

SU1642478A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СКОЛЬЗЯЩЕГО СРЕДНЕГО ЗНАЧЕНИЯ | 1990 |

|

RU2015552C1 |

1

Устройство относится к вычислительной технике и может быть применено в специализированных устройствах, ориентированных на решение систем алгебраических, дифференциальных и интегральных уравнений, вычисление корреляционных функций, коэффициентов Фурье, цифровую фильтрацию сигналов и т.п., при вычислении суммы произведений двух мас-,о сивов чисел.

Известны устройства для вычисления суммы произведения двух массивов чисел, содержащие блок памяти для хранения иассивов числе и про- 5 цессор для перемножения сомножителей и вычисления их суммы Cl.

Недостатком таких устройств является их низкое быстродействие,обусловленное тем, что процессор в со- 20 ответствии с программой последовательно во времени формирует адреса первого и второго сомножителей выбирает по ним сомножители из блока

памяти, осуществляет их перемножение «выбирает текущее значение.суммы, добавляет его к полученному произведению и отсылает в рабочую ячейку памяти, после чего сравнивает текущие адреса чисел массива с концом массива и переходит на начало программы.

Известны устройства для вычисления суммы произведений двух массивов чисел, содержащие множительные устройства по числу пар сомножителей и многовходовой сумматор, осуществляющий суммирование,полученных произведений Г 2 J,

Недостатком таких устройств являются большие аппаратурные затраты, обусловленные наличием N мнояительных устройств и многовходового сумматора (N - число пар сомножителей).

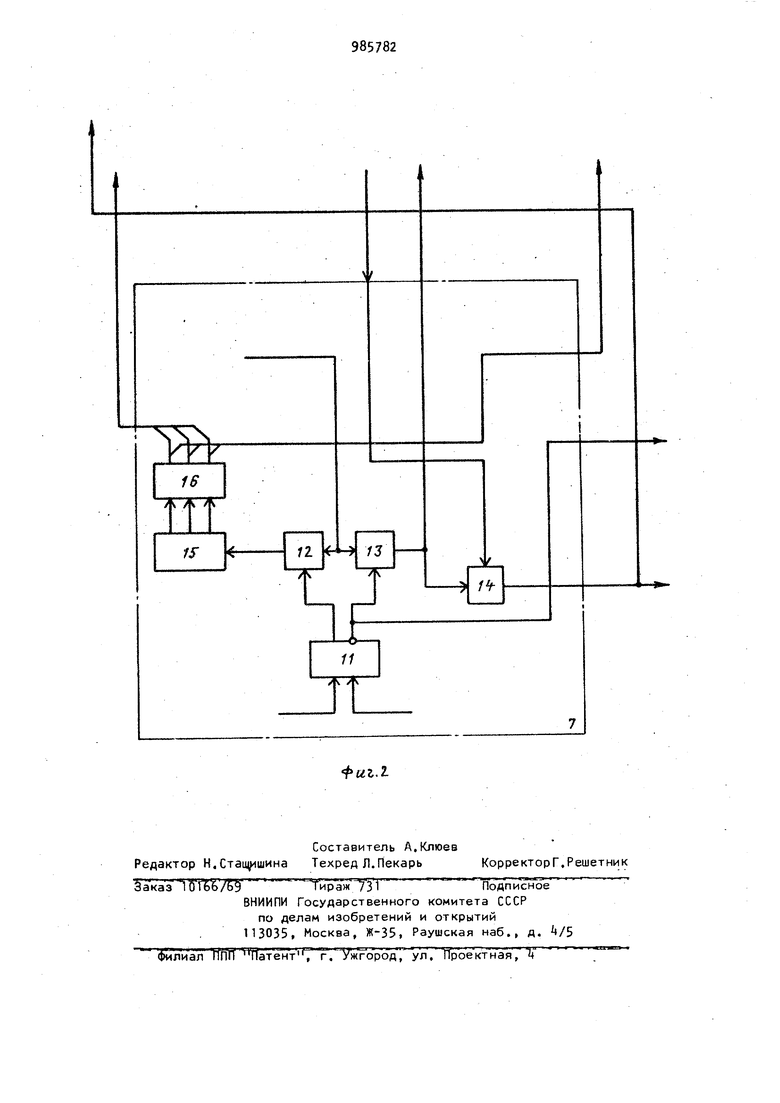

Наиболее близким к предлагаемому по технической сущности является устройство для вычисления суммы произведений двух массивов чисел, содер39жащее два блока памяти, блок умноже ния, накапливающий сумматор, два ре гистра, счетчик адреса, элементы И по числу разрядов, блок управления, причем выходы счетчика адреса соеди нены с адресными входами первого и второго блоков памяти, информационные входы которых подключены к соответствующим входам устройства, а выходы - соединены соответственно с входами первого и второго регистров, выходы которых соединены соответственно с входами первого и вт рого сомножителей блока умножения, выходы которого подключены соответственно к первым входам элементов И, вторые входы которых подключены к первому выходу блока управления, а выходы соединены с соответствующими входами накапливающего сумматора, выходы которого являются выходами устройства, вторые и третьи выходы блока управления соединены соответственно с входами записи и чтения первого и второго блоко памяти, четвертый и пятый выходы блока управления соединены соответственно с входом счетчика адреса и управляющим входом блока умножения Недостатком известного устройств является низкое быстродействие, обусловленное тем, что для вычисления произведений N пар чисел необходимо выполнить Nin сложений и сдвигов В блоке умножения (п - раз рядность чисел) , Цель изобретения - повышение быстродействия -устройства. Поставленная цель достигается тем, что устройство для вычисления суммы произведений двух массивов чи сел, содержащее два блока памяти, накапливающий сумматор,элементы/ И по числу разрядов, блок управления, причем информационные входы первого и второго блоков памяти сое динены соответственно с первой и второй группами /ийформационных вхо дов устройства, первый выход блока управления соединен с первыми входами элементов И, выходы которых подключены к соответствующим входам накапливающего сумматора, выходы которого являются выходами устройства, второй выход блока управления соединен с входами записи перво го и второго блоков памяти, содержит приоритетный блок, сумматор-вы читатель, причем вход счета первого блока памяти соединен с первым выходом блока управления, выходы первого блока памяти соединены с информационными входами приоритетного блока, управляющий вход которого соединен с третьим выходом блока управления, информационные выходы приоритетного блока подключены к входам чтения второго блока памяти, выход сигнала окончания работы приоритетного блока соединен с первым входом блока управления, четвертый выход которого подключен к управляющему входу сумматора- вычитателя , входы разрядов которого соединены с информационными входами второго блока памяти и информационными выходами второго блока памяти, выходы сумматора-вычитателя подключены соответственно к вторым входам элементов И, второй, третий и четвертый входы блока управления соединены соответ-. ственно с управляющими шинами записи, счета и тактовой шиной устройства. Кроме того, первый блок памяти содержит счетчики по количеству чисел в массиве, информационные входы которых соединены соответственно с информационными входами блока, счетные входы подключены к входу счета блока, выходы переполнения счетчиков Я8ЛЯЮТСЯ выходами блока, а входы записи счетчиков соединены с входом записи блока. Блок управления содержит триггер, счетчик, дешифратор, три элемента И, причем единичный и нулевой входы триггера соединены соответственно с вторым и третьим входами блока, а единичный и нулевой выходы триггера соединены соответственно с первыми входами первого и второго элемеитов И, вторые входы которых соединены с четвертым входом блока, выход первого элемента. И соединен с входом счетчика, выходы которого подключены соответственно к входам дешифратора, выходы которого соединены с вторым выходом блока, выход второго элемента И соединен с третьим выходом блока и первым входом третьего элемента И, второй вход которого соединен с первым входом блока, а выход - с первым выходом блока, нулевой выход триггера соединен с четвертым выходом блока. На фиг. 1 представлена структурная схема устройства для вычисления суммы произведений двух массивов чисел; на фиг. 2 - схема блока управления. Устройство содержит первый и второй блоки 1 и 2 памяти,и приоритзтный блок 3 сумматор-вычитатель , элементы И 5 накапливающий сумматор .6, блок управления 7, входы 8 и 9 устройства, выход 10 устройства, Блок управления содержит триггер 11, элементы И 12-1Ц, счетчик 15, дешифратор t6. Устройство работает следующим образом. По входам 8 и 9 под управлением сигналов с вторых выходов блока управления осуществляется запись чисел первого и второго массивов в первый 1 и второй 2 блоки памяти, причем запись чисел в первый блок 1 памяти производится в дополнительном коде, а во второй - в прямом. Наряду с записью.чисел во второй запоминающий блок 2 под управлением сигналов по четвертому выходу схемы управления 7 производится их суммирование в- сумматоре-вычитателе Ц, После записи всех чисел массивов и вычисления суммы чисел второго массива блок 7 управления по первому выходу выдает тактовые импульсы, которые открывают элементы И 5 и осуществляют передачу содержимого сумматора-вычитателя 4 в накапливающий сумматор 6 и добавление единиц во все счетчики первого запоминающего блока. IjB которых были записаны дополнительные коды чисел первог массива. Тогда переполнение счетчиков первого запоминающего блока 1 с детельствует о равенстве прямого ко да числа, записанного в нем, количе ству импульсов, пришедших на его вход. Импульс переполнения каждого счетчика первого запоминающего,блок 1 проходит через приоритетный блок 3 и разрешает чтение содержимого ячейки, соответствующей номеру пере полнившегося счетчика первого запом нающего блока 1. Блок 7 управления, получив сигнал о переполнении счетчи ка с второго выхода приоритетного блока 3 по четвертому выходу управ ляет вычитанием из содержимого сумматора- вычитателя k содержимого счи танной ячейки второго запоминающего блока 2, Таким образом получается, что каждый импульс, прошедший на сче чики первого запоминающего блока 1, умножается на сумму тех чисел второго массива, соответствующие счетчики которых из первого запоминающего блока 1 еще не переполнились. Результаты умножения накапливаются в накапливающем сумматоре 6. После переполнения счетчика первого запоминающего блока 1, содержащего максимальное число в первом массиве , из содержимого сумматора-вычитлтеля t вычитается число из второго массива, адрес которого во втором запоминающем блоке 2 соответствует номеру последнего переполнившегося счетчика. При этом в сумматоре-вычитателе k появляется нулевой код, а в накапливающем сумматоре б фиксируется сумма парных произведений двух массивов чисел. При одновременномпереполнении нескольких счетчиков первого запоминающего блока 1 приоритетный блок 3 последовательно разрешает прохождение сигналов на управляющие входы чтения второго запоминающего блока 2, а по второму выходу через блок 7 управления запрещает прохождение на это время тактовых импульсов на входы счетчиков первого запоминающего блока 1 и управляющие входы элементов ИЗ. Блок управления работает следующим образом. Управляющий сигнал Запись на входе триггера 11 приводит к установке его в состояние, при котором открывается, первый элемент И 12, разрешающий прохождение тактовых импульсов на вход счетчика 15. При этом на .выходах дешифратора 16 последовательно появляются сигналы, разрешающие запись кодов коэффициентов в счетчики и регистры первого и второго запоминающих 1 и 2 блоков. На четвертый выход блока управления в процессе записи выдается разрешение суммирования. После окончания записи управляющий сигнал Счет переводит триггер 11 в состояние, при котором закрывается первый элемент И 12 и открывается второй элемент И 13, пропускающий тактовые импульсы на третий выход блока управления и через элемент И 1 на первый выход блока управления. На Четвертый выход блока управления в процессе счета выдается разрешение вычитания. 7 Отсутствие сигнала на входе блока управления от приоритетного бло ка 3 приводит к запрещению прохождения тактовых импульсов через элемент И 14 на первый выход блока управления. Время перемножения двух массивов чисел практически не зависит от величины массивов, а зависит от разрядности чисел первого массива как 2, в то время как в прототипеоно зависит от количества чисел в массиве и их разрядности как их произведение N«1:1. Выигрыш по быстродействию устрой ства по сравнению с прототипом составитТ fipoT N . п (сл оже ни и) ТпрГ:# тр. () +N -п (сдвигрв1) 2(сложений формула изобретения 1 , Устройство для вычисления сум мы произведений двух массивов чисел, содержащее два блока памяти, накапливающий сумматор, элементы И по числу разрядов, блок управления, причем информационные входы первого и второго блоков памяти соединены соответственно с первой и второй группами информационных входов устройства, первый выход блока управле ния соединен с первыми входами элементов И, выходы которых подключены к соответствующим входам накапливающего сумматора, выходы которого являются выходами устройства, второй выход блока управления соединен с входами записи первого и второго блоков памяти, отличающееся тем, что, с целью повышения быстродействия, оно содержит приори тетный блок и сумматор-вычитатель, причем вход счета первого блока памяти соединен с первым выходом блока управления, выходы первого блока памяти соединены с информационными входами приоритетного блока, управляющий вход которого соединен с тре тьим выходом блока управления, инфо мационные выходы приоритетного блок подключены к входам чтения второго блока памяти, выход сигнала окон чания работы прифитетного блока соединен с первым входом блока управле 2 ния, четвертый выход которого подключен к управляющему входу сумматора-вычитателя, входы разрядов которого соединены с информационными входами второго блока памяти и информационными выходами второго блока памяти, выходы сумматора-вимитателя подключены соответственно к вторым входам элементов И, второй, третий и четвертый входы блока управления соединены соответственно с управляющими шинами записи, счета и тактовой шиной устройства. 2. Устройство по п. 1, отличающееся тем, что первый блок памяти содержит счетчики по количеству чисел в массиве, информационные входы которых соединены соответ-, ственно с информационными входами блока, счетные входы подключены к входу счета блока, входы записи счетчиков соединены с входом записи блока, а выходы переполнения счетчиков являются выходами блока. 3. Устройство по п. 1, о т л и чающееся тем, что блок управления содержит триггер, счетчик, дешифратор, три элемента И, причем единичный и нулевой входы триггера соединены соответственно с вторым и третьим входами блока, а единичный и нулевой выходы триггера соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены с четвертым входом блока, выход первого элемента И соединение входом счетчика, выходы которого подключены соответственно к входамдешифратора, выходы которого .соединены с вторым выходом блока, выход второго элемента И соединен с третьим выходом блока и первым входом третьего элемента И, второй вход которого соединен с первым входом блока, а выход - с первым выходом блока J нулевой выход триггера соеди.,нен с четвёртым выходом блока. Источники информации, принятые во внимание при экспертизе 1,Каган Б.М,, Каневский М.М, Цифровые вычислительные машины и системы. М., Энергия, 1973, с. 12-18. 2,Семотюк М.В,, Бсион В.П. Операционные устройства для суммирования парных произведений и перемножения комплексных чисел, - Управляющие системы и машины, 1978, №.3 с. 87-92, рис. 3.

998578210

ляшцие системы и машины, 1Э78, Н 3, с. 87-92, рис, 1 (прототип).

Авторы

Даты

1982-12-30—Публикация

1980-12-11—Подача