управления соединен с шестым управляющим входом блока суммирования точного значения переменной.

Алгоритм работы интегрирующего устройства имеет следующий вид:

+ а а;

C2 BT+Јja;

,4; 1/2; 1 ;

# Дг/Зз/2. Дз 3;/34 О,;

где С - накопленная переменная в знако- разрядной избыточной двоичной системе счисления;

С2-точное значение переменной интегрирования в знакоразрядной избыточной двоичной системе счисления;

В - накопленная переменная в обычной двоичной системе счисления;

Вт - вычисленная переменная в точке в обычной двоичной системе счисления;

а - значение дифференциалов; а,/9-коэффициенты.

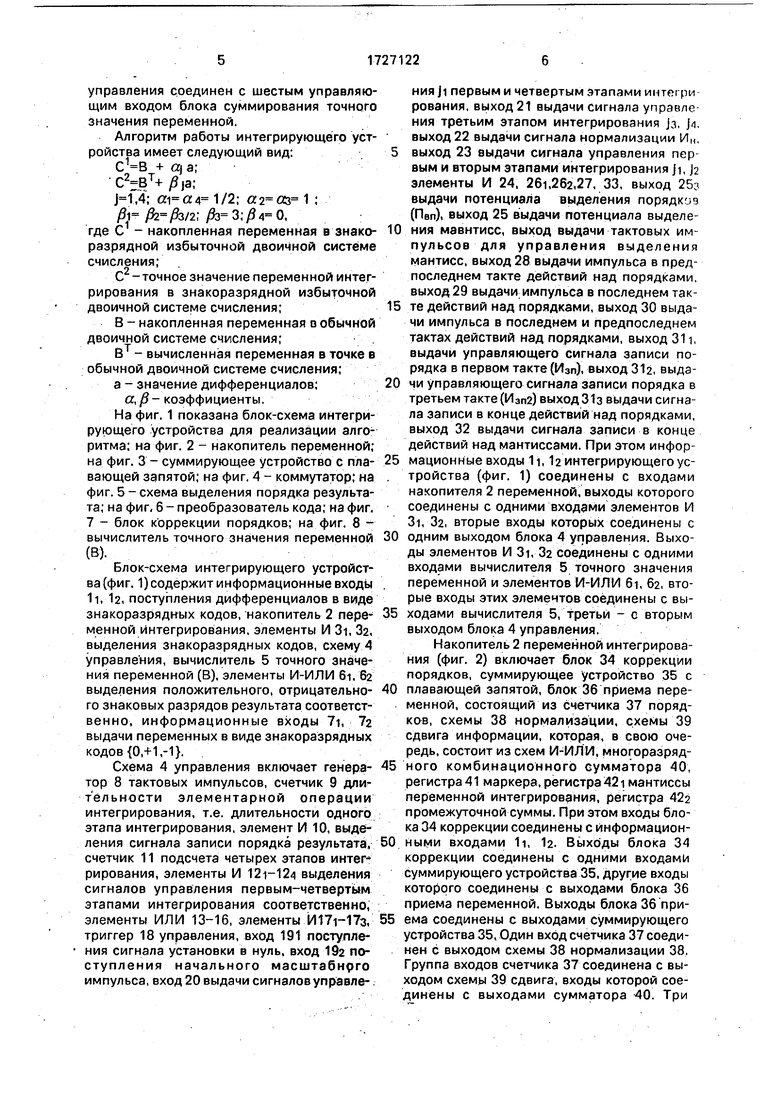

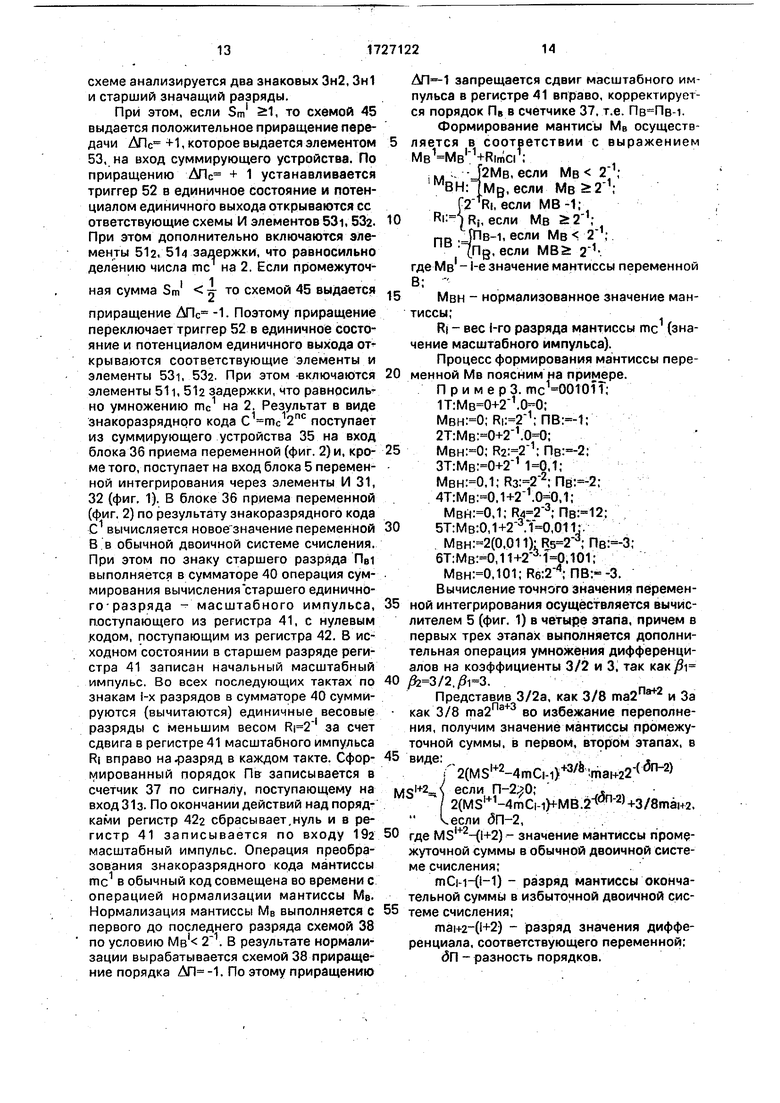

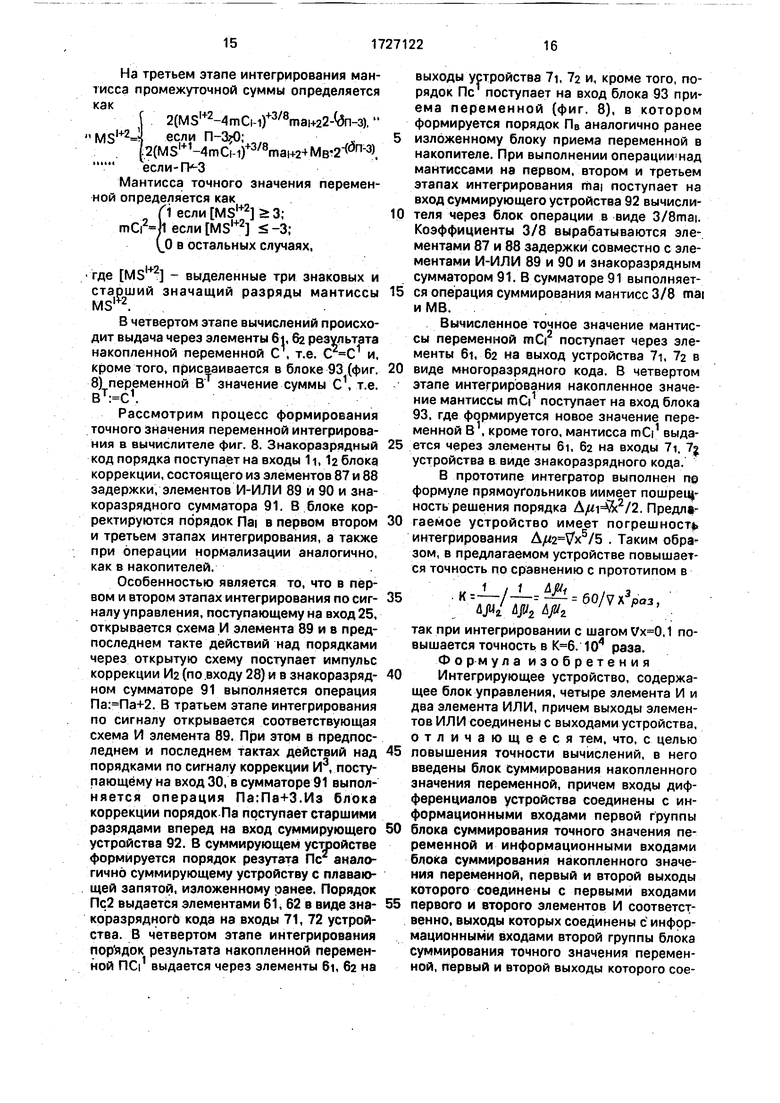

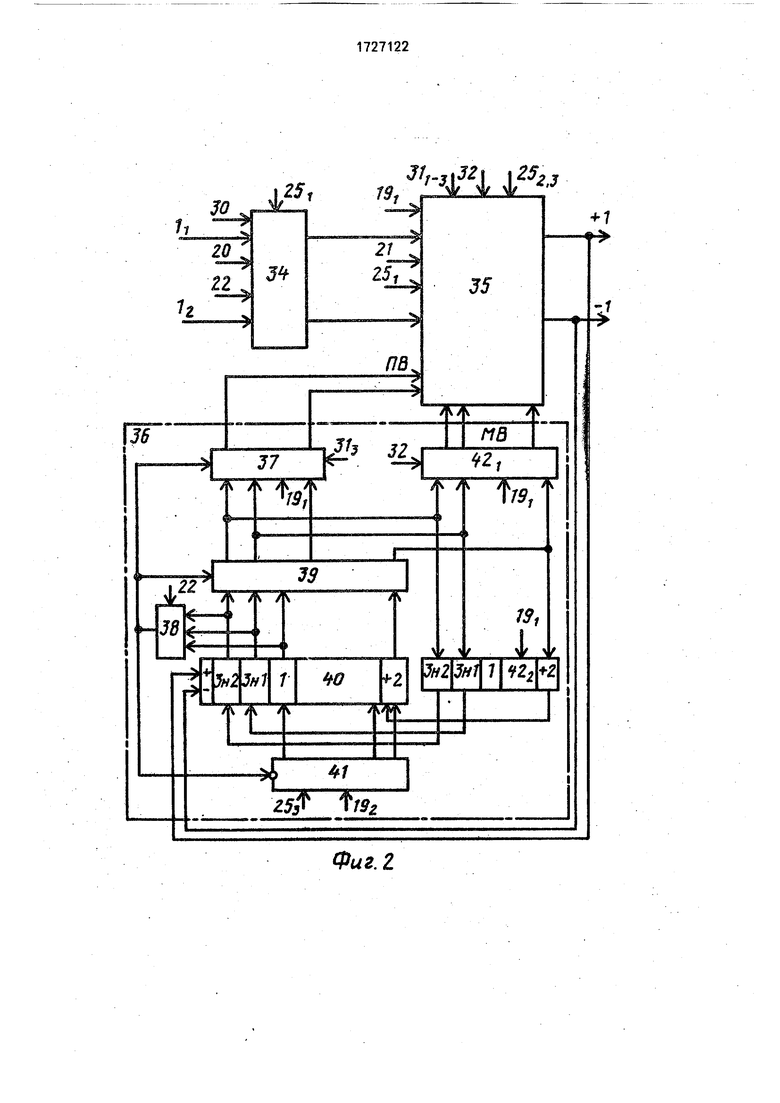

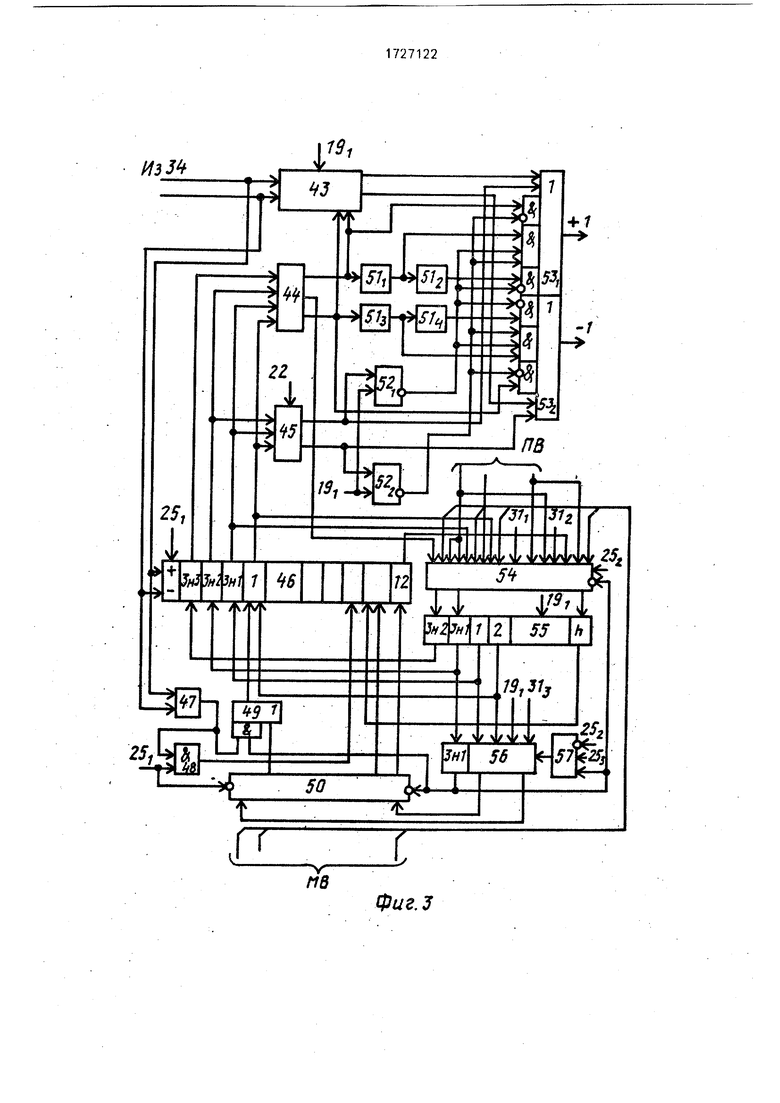

На фиг. 1 показана блок-схема интегрирующего устройства для реализации алгоритма; на фиг. 2 - накопитель переменной; на фиг. 3 - суммирующее устройство с плавающей запятой; на фиг. 4 - коммутатор; на фиг. 5 - схема выделения порядка результата; на фиг, 6 - преобразователь кода; на фиг. 7 - блок коррекции порядков; на фиг. 8 - вычислитель точного значения переменной (В).

Блок-схема интегрирующего устройства (фиг. 1) содержит информационные входы 1i. 12, поступления дифференциалов в виде знакоразрядных кодов, накопитель 2 переменной интегрирования, элементы И 3i, 32, выделения знакоразрядных кодов, схему А управления, вычислитель 5 точного значения переменной (В), элементы И-ИЛИ 6.1, б2 выделения положительного, отрицательного знаковых разрядов результата соответственно, информационные входы 7т, 7z выдачи переменных в виде знакоразрядных кодов {0,+1,-1}.

Схема 4 управления включает генератор 8 тактовых импульсов, счетчик 9 дли- т ёльности элементарной операции интегрирования, т.е. длительности одного этапа интегрирования, элемент И 10, выделения сигнала записи порядка результата, счетчик 11 подсчета четырех этапов интег рирования, элементы И 121-124 выделения сигналов управления первым-четвертым этапами интегрирования соответственно, элементы ИЛИ 13-16, элементы И 17г-17з, триггер 18 управления, вход 191 поступления сигнала установки в нуль, вход 192 поступления начального масштабнрго импульса, вход 20 выдачи сигналов управле-.

ния ji первым и четвертым этапами интегри рования, выход 21 выдачи сигнала управления третьим этапом интегрирования J3, J4, выход 22 выдачи сигнала нормализации Им, 5 выход 23 выдачи сигнала управления первым и вторым этапами интегрирования ,2 элементы И 24, 26i,262,27, 33, выход 25з выдачи потенциала выделения порядков (Поп), выход 25 выдачи потенциала выделе- 0 ния мавнтисс, выход выдачи тактовых импульсов для управления выделения мантисс, выход 28 выдачи импульса в предпоследнем такте действий над порядками, выход 29 выдачи импульса в последнем так- 5 те действий над порядками, выход 30 выдачи импульса в последнем и предпоследнем тактах действий над порядками, выход 311, выдачи управляющего сигнала записи порядка в первом такте (И3п), выход 312, выда0 чи управляющего сигнала записи порядка в третьем такте (И3п2) выход 31з выдачи сигнала записи в конце действий над порядками, выход 32 выдачи сигнала записи в конце действий над мантиссами. При этом инфор5 мационные входы 11,12 интегрирующего устройства (фиг. 1) соединены с входами накопителя 2 переменной, выходы которого соединены с одними входами элементов И 3i, 32, вторые входы которых соединены с

0 одним выходом блока 4 управления. Выходы элементов И 3i, 32 соединены с одними входами вычислителя 5 точного значения переменной и элементов И-ИЛИ 6т, 62, вторые входы этих элементов соединены с вы5 ходами вычислителя 5, третьи - с вторым выходом блока 4 управления.

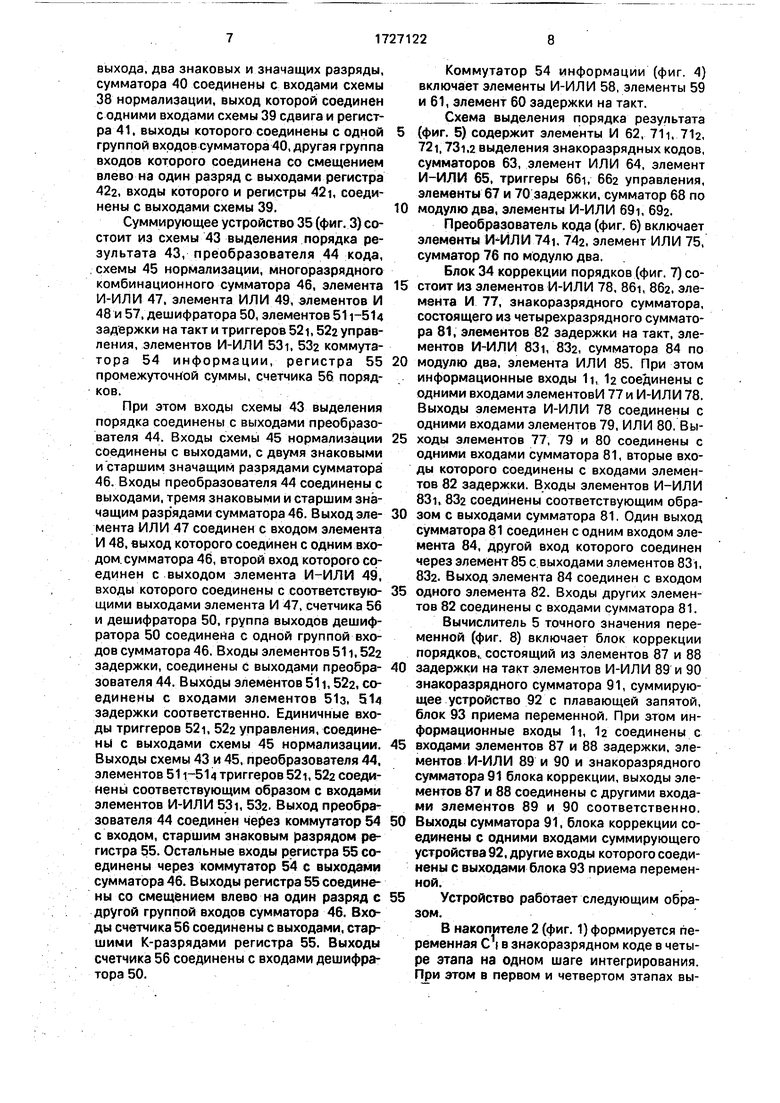

Накопитель 2 переменной интегрирования (фиг. 2) включает блок 34 коррекции порядков, суммирующее устройство 35 с

0 плавающей запятой, блок 36 приема переменной, состоящий из счетчика 37 порядков, схемы 38 нормализации, схемы 39 сдвига информации, которая, в свою очередь, состоит из схем И-ИЛИ, многоразряд5 ного комбинационного сумматора 40, регистра 41 маркера, регистра 421 мантиссы переменной интегрирования, регистра 422 промежуточной суммы. При этом входы блока 34 коррекции соединены с информацион0 ными входами 1i, 12. Выходы блока 34 коррекции соединены с одними входами суммирующего устройства 35, другие входы которого соединены с выходами блока 36 приема переменной. Выходы блока 36 при5 ема соединены с выходами суммирующего устройства 35, Один вход счетчика 37 соединен с выходом схемы 38 нормализации 38. Группа входов счетчика 37 соединена с выходом схемы 39 сдвига, входы которой соединены с выходами сумматора 40. Три

выхода, два знаковых и значащих разряды, сумматора 40 соединены с входами схемы 38 нормализации, выход которой соединен с одними входами схемы 39 сдвига и регистра 41, выходы которого соединены с одной группой входов сумматора 40, другая группа входов которого соединена со смещением влево на один разряд с выходами регистра 422, входы которого и регистры 421, соединены с выходами схемы 39.

Суммирующее устройство 35 (фиг. 3) состоит из схемы 43 выделения порядка результата 43, преобразователя 44 кода, /схемы 45 нормализации, многоразрядного комбинационного сумматора 46, элемента И-ИЛИ 47, элемента ИЛИ 49, элементов И 48 и 57, дешифратора 50, элементов 511-514 задержки на такт и триггеров 52i, 52гуправ- ления, элементов И-ИЛИ 53i, 532 коммутатора 54 информации, регистра 55 промежуточной суммы, счетчика 56 порядков.

При этом входы схемы 43 выделения порядка соединены с выходами преобразователя 44. Входы схемы 45 нормализации соединены с выходами, с двумя знаковыми и старшим значащим разрядами сумматора 46. Входы преобразователя 44 соединены с выходами, тремя знаковыми и старшим значащим разр ядами сумматора 46. Выход элемента ИЛИ 47 соединен с входом элемента И 48, выход которого соединен с одним входом, сумматора 46, второй вход которого соединен с выходом элемента И-ИЛИ 49, входы которого соединены с соответствующими выходами элемента И 47, счетчика 56 и дешифратора 50, группа выходов дешифратора 50 соединена с одной группой входов сумматора 46. Входы элементов 511,522 задержки, соединены с выходами преобразователя 44. Выходы элементов 51.1,522, соединены с входами элементов 51з, 514 задержки соответственно. Единичные входы триггеров 52i, 522 управления, соединены с выходами схемы 45 нормализации. Выходы схемы 43 и 45, преобразователя 44, элементов 511-514 триггеров 52i, 522 соединены соответствующим образом с входами элементов И-ИЛИ 531, 532. Выход преобразователя 44 соединен через коммутатор 54 с входом, старшим знаковым разрядом регистра 55. Остальные входы регистра 55 соединены через коммутатор 54 с выходами сумматора 46. Выходы регистра 55 соединены со смещением влево на один разряд с другой группой входов сумматора 46. Входы счетчика 56 соединены с выходами, старшими К-разрядами регистра 55. Выходы счетчика 56 соединены с входами дешифратора 50.

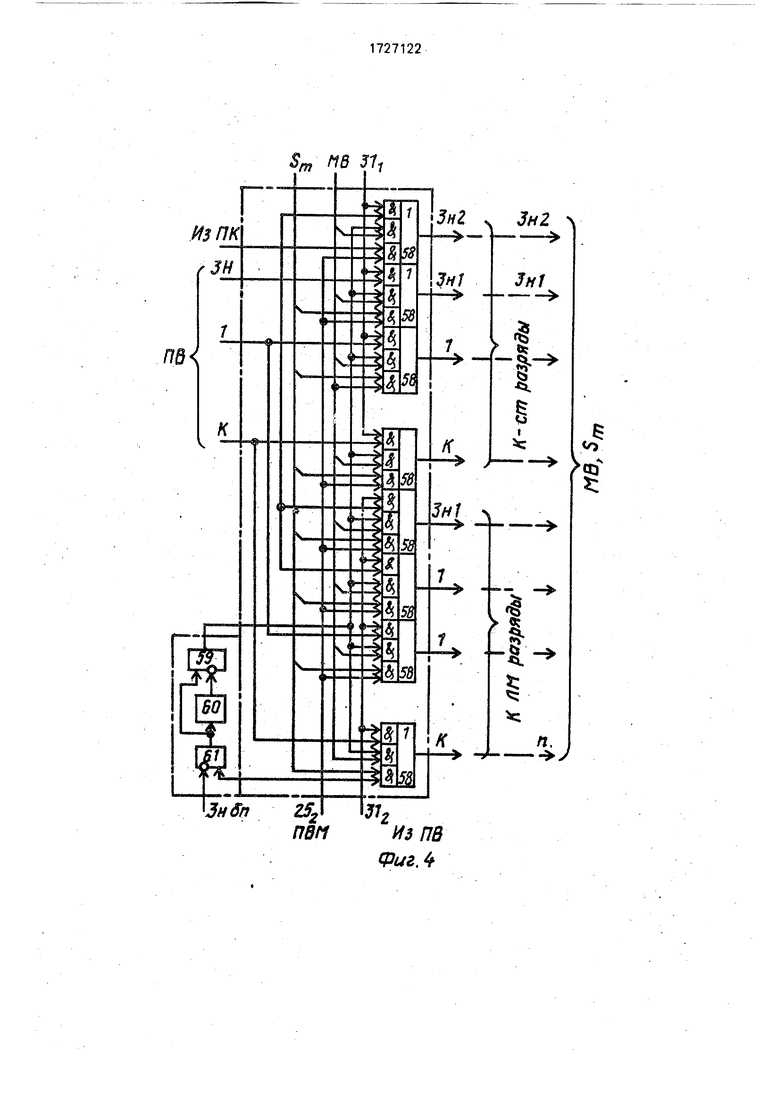

Коммутатор 54 информации (фиг. 4) включает элементы И-ИЛИ 58, элементы 59 и 61, элемент 60 задержки на такт.

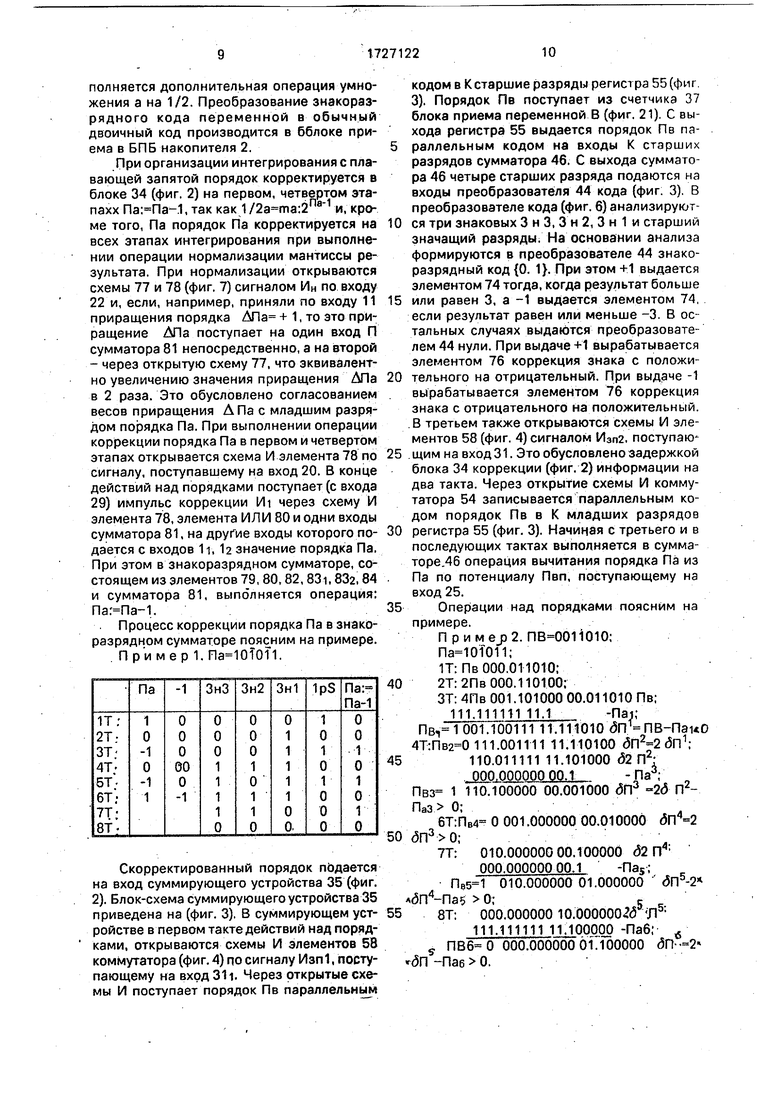

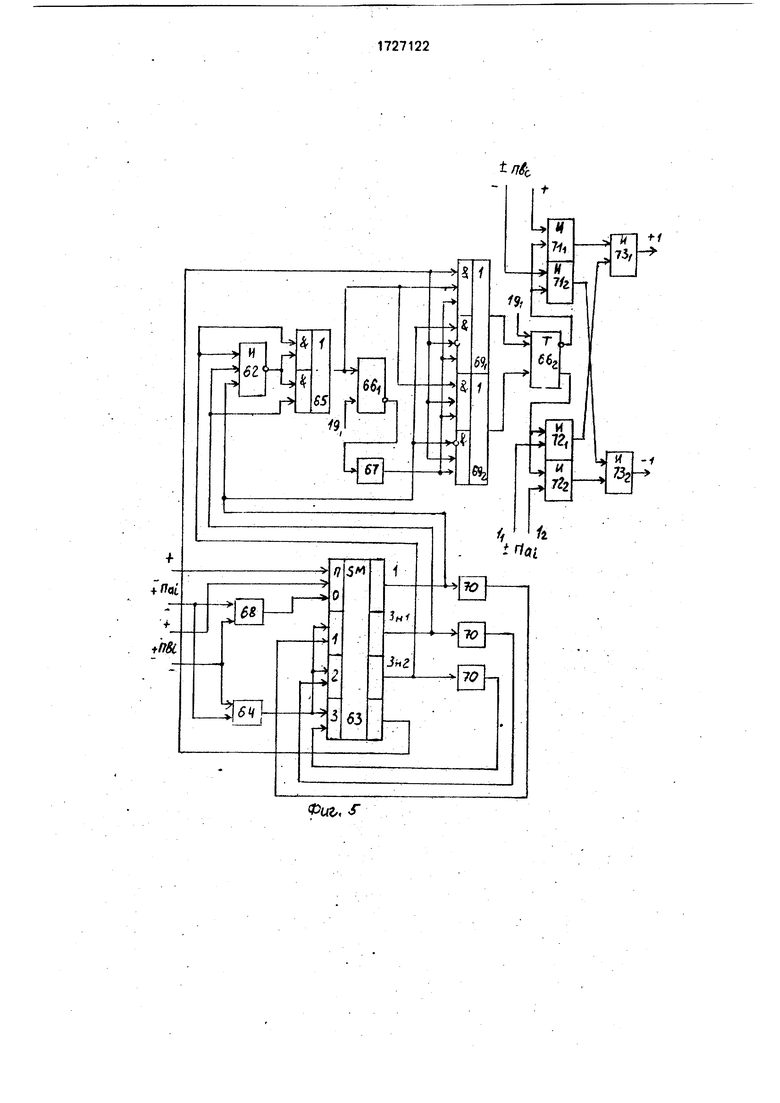

Схема выделения порядка результата

(фиг. 5) содержит элементы И 62, 71i,.7l2, 721,73i,2 выделения знакоразрядных кодов, сумматоров 63, элемент ИЛИ 64, элемент И-ИЛИ 65, триггеры 66i, 662 управления, элементы 67 и 70 задержки, сумматор 68 по

0 модулю два, элементы И-ИЛИ 69i, 692.

Преобразователь кода (фиг. 6) включает элементы 74i, 742, элемент ИЛИ 75, сумматор 76 по модулю два.

Блок 34 коррекции порядков (фиг. 7) со5 стоит из элементов И-ИЛИ 78, 86i, 862, элемента И 77, знакоразрядного сумматора, состоящего из четырехразрядного сумматора 81, элементов 82 задержки на такт, элементов И-ИЛИ 831, 832, сумматора 84 по

0 модулю два, элемента ИЛИ 85. При этом информационные входы 1i, 1a соединены с одними входами элементовИ 77 и И-ИЛИ 78. Выходы элемента И-ИЛИ 78 соединены с одними входами элементов 79, ИЛИ 80, Вы5 ходы элементов 77, 79 и 80 соединены с одними входами сумматора 81, вторые входы которого соединены с входами элементов 82 задержки. Входы элементов И-ИЛИ 83п 832 соединены соответствующим обра0 зом с выходами сумматора 81. Один выход сумматора 81 соединен с одним входом элемента 84, другой вход которого соединен через элемент85 с выходами элементов 83i, 832. Выход элемента 84 соединен с входом

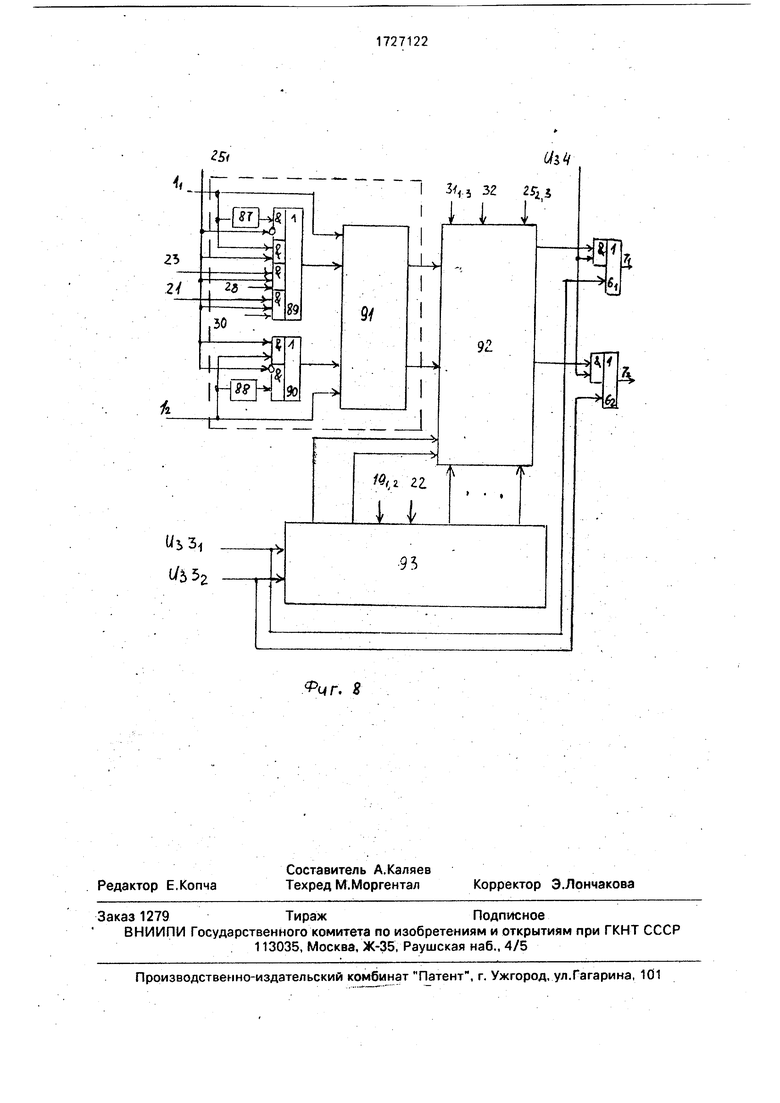

5 одного элемента 82. Входы других элементов 82 соединены с входами сумматора 81. Вычислитель 5 точного значения переменной (фиг. 8) включает блок коррекции порядков,, состоящий из элементов 87 и 88

0 задержки на такт элементов И-ИЛИ 89 и 90 знакоразрядного сумматора 91, суммирующее устройство 92 с плавающей запятой, блок 93 приема переменной, При этом информационные входы 1i, 12 соединены с

5 входами элементов 87 и 88 задержки, элементов И-ИЛИ 89 и 90 и знакоразрядного сумматора 91 блока коррекции, выходы элементов 87 и 88 соединены с другими входами элементов 89 и 90 соответственно.

0 Выходы сумматора 91, блока коррекции соединены с одними входами суммирующего устройства 92, другие входы которого соединены с выходами блока 93 приема переменной,

5 Устройство работает следующим образом.

В накопителе 2 (фиг. 1) формируется переменная С i в знакоразрядном коде в четыре этапа на одном шаге интегрирования. При этом в первом и четвертом этапах выполняется дополнительная операция умножения а на 1/2. Преобразование знакораз- рядного кода переменной в обычный двоичный код производится в бблоке приема в БПБ накопителя 2.

При организации интегрирования с плавающей запятой порядок корректируется в блоке 34 (фиг. 2) на первом, четвертом эта- пахх , так как 1 /2а та:2Па 1 и, кроме того, Па порядок Па корректируется на всех этапах интегрирования при выполнении операции нормализации мантиссы результата. При нормализации открываются схемы 77 и 78 (фиг, 7) сигналом Ин по входу 22 и, если, например, приняли по входу 11 приращения порядка ДПа + 1, то это приращение ДПа поступает на один вход П сумматора 81 непосредственно, а на второй - через открытую схему 77, что эквивалентно увеличению значения приращения ДПа в 2 раза. Это обусловлено согласованием весов приращения А Па с младшим разрядом порядка Па. При выполнении операции коррекции порядка Па в первом и четвертом этапах открывается схема И элемента 78 по сигналу, поступавшему на вход 20. В конце действий над порядками поступает (с входа 29) импульс коррекции Ит через схему И элемента 78, элемента ИЛИ 80 и одни входы сумматора 81, на другие входы которого подается с входов 1т, 12 значение порядка Па. При этом в знакоразрядном сумматоре, состоящем из элементов 79, 80,82, 83i, 832,84 и сумматора 81, выполняется операция: .

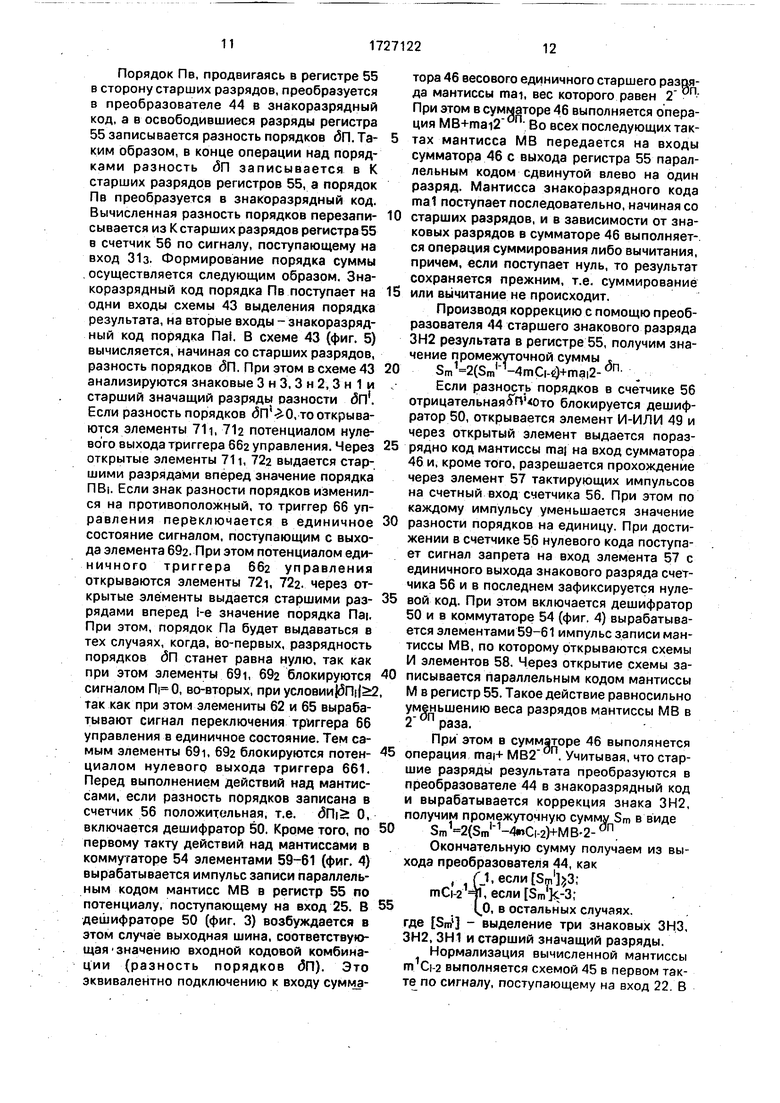

. Процесс коррекции порядка Па в знакоразрядном сумматоре поясним на примере. . П ри ме р 1. Па 10ТоТ1.

Скорректированный порядок подается на вход суммирующего устройства 35 (фиг. 2). Блок-схема суммирующего устройства 35 приведена на (фиг. 3). В суммирующем устройстве в первом такте действий над порядками, открываются схемы И элементов 58 коммутатора (фиг. 4) по сигналу Изп1, поступающему на вход 311. Через открытые схемы И поступает порядок Пв параллельным

кодом в К старшие разряды регистра 55 (фиг. 3). Порядок Пв поступает из счетчика 37 блока приема переменной В (фиг. 21). С выхода регистра 55 выдается порядок Пв па- 5 раллельным кодом на входы К старших разрядов сумматора 46. С выхода сумматора 46 четыре старших разряда подаются на входы преобразователя 44 кода (фиг. 3). В преобразователе кода (фиг. 6) анализируют- 0 ся три знаковых 3 н 3, 3 н 2, 3 н 1 и старший значащий разряды. На основании анализа формируются в преобразователе 44 знако- разрядный код {0. 1}. При этом +1 выдается элементом 74 тогда, когда результат больше 5 или равен 3, а -1 выдается элементом 74, если результат равен или меньше -3. В остальных случаях выдаются преобразователем 44 нули. При выдаче +1 вырабатывается элементом 76 коррекция знака с положи- 0 тельного на отрицательный. При выдаче -1 вырабатывается элементом 76 коррекция знака с отрицательного на положительный. .В третьем также открываются схемы И элементов 58 (фиг. 4) сигналом Иэп2, поступаю 5 .щим на вход 31. Это обусловлено задержкой блока 34 коррекции (фиг. 2) информации на два такта. Через открытие схемы И коммутатора 54 записывается параллельным кодом порядок Пв в К младших разрядов 0 регистра 55 (фиг. 3). Начиная с третьего и в последующих тактах выполняется в сумма- торе.46 операция вычитания порядка Па из Па по потенциалу Пвп, поступающему на вход 25.

5 Операции над порядками поясним на примере.

П р и . ПВ 0011010; Па 101011; 1Т:Пв 000.011010; 0 2Т:2Пв 000.110100;

ЗТ: 4Пв 001.101000 00.011010 Пв;

111.111111 11.1-nai;

Пв, 1001.100111 11.111010 5ПТ ПВ-ПакО 4Т:Пв2 0111.001111 11.110100 5П1; 5110.011111 11.101000 52П2:

,000.00000000.1-Па3;

Пвз 1 110.100000 00.001000 5П3 П2- Паз 0;

6Т:ПВ4 0 001.000000 00.010000 0

7Т: 010.00000000.100000 62 П4:

000.00000000.1 -Па5; 010.000000 01.000000 5П5-2 л(5П4-Па5 0;с

5 8Т: 000.000000 Ю.ОООООО б Л5:

111.111111 11,100000 -Паб; в «, 000.000000 ОГ100000 ( ч5П -Пае 0.

Порядок Пв, продвигаясь в регистре 55 в сторону старших разрядов, преобразуется в преобразователе 44 в знакоразрядный код, а в освободившиеся разряды регистра 55 записывается разность порядков дП.Та- ким образом, в конце операции над порядками разность (5П записывается в К старших разрядов регистров 55, а порядок Пв преобразуется в знакоразрядный код. Вычисленная разность порядков перезапи- сывается из К старших разрядов регистра 55 в счетчик 56 по сигналу, поступающему на вход 31з. Формирование порядка суммы , осуществляется следующим образом. Знакоразрядный код порядка П в поступает на одни входы схемы 43 выделения порядка результата, на вторые входы - знакоразрядный код порядка Па). В схеме 43 (фиг. 5) вычисляется, начиная со старших разрядов, разность порядков дГ. При этом в схеме 43 анализируются знаковые 3 н 3, 3 н 2, 3 н 1 и старший значащий разряды разности 5П. Если разность порядков (, то открываются элементы 711, 712 потенциалом нулевого выхода триггера 662 управления. Через открытые элементы 711, 722 выдается старшими разрядами вперед значение порядка ПВ|. Если знак разности порядков изменился на противоположный, то триггер 66 управления переключается в единичное состояние сигналом, поступающим с выхода элемента 692. При этом потенциалом еди- ничного триггера 662 управления открываются элементы 72i, 722. через открытые элементы выдается старшими раз- рядами вперед 1-е значение порядка Па|. При этом, порядок Па будет выдаваться в тех случаях, когда, во-первых, разрядность порядков 5П станет равна нулю, так как при этом элементы 69i, 692 блокируются сигналом П| 0, во-вторых, при условии| 5П | так как при этом элемениты 62 и 65 вырабатывают сигнал переключения триггера 66 управления в единичное состояние. Тем самым элементы 691, 692 блокируются потен- циалом нулевого выхода триггера 661. Перед выполнением действий над мантиссами, если разность порядков записана в счетчик 56 положительная, т.е. 5П|Э: О, включается дешифратор 50. Кроме того, по первому такту действий над мантиссами в коммутаторе 54 элементами 59-61 (фиг. 4) вырабатывается импульс записи параллельным кодом мантисс MB в регистр 55 по потенциалу, поступающему на вход 25. В дешифраторе 50 (фиг. 3) возбуждается в этом случае выходная шина, соответствующая значению входной кодовой комбинации (разность порядков 5П). Это эквивалентно подключению к входу сумматора 46 весового единичного старшего разоя- да мантиссы mai, вес которого равен 2 п При этом в сумматоре 46 выполняется операция MB+mai2 п; Во всех последующих тактах мантисса MB передается на входы сумматора 46 с выхода регистра 55 параллельным кодом сдвинутой влево на один разряд. Мантисса знакоразрядного кода ma1 поступает последовательно, начиная со старших разрядов, и в зависимости от знаковых разрядов в сумматоре 46 выполняет-, ся операция суммирования либо вычитания, причем, если поступает нуль, то результат сохраняется прежним, т.е. суммирование или вычитание не происходит.

Производя коррекцию с помощю преобразователя 44 старшего знакового разряда ЗН2 результата в регистре 55, получим значение промежуточной суммы с

Sm Sm mCHO+matf- п V Если разность порядков в счетчике 56 отрицательная 5п 40то блокируется дешифратор 50, открывается элемент И-ИЛИ 49 и через открытый элемент выдается поразрядно код мантиссы та; на вход сумматора 46 и, кроме того, разрешается прохождение через элемент 57 тактирующих импульсов на счетный вход счетчика 56. При этом по каждому импульсу уменьшается значение разности порядков на единицу. При достижении в счетчике 56 нулевого кода поступает сигнал запрета на вход элемента 57 с единичного выхода знакового разряда счетчика 56 и в последнем зафиксируется нулевой код. При этом включается дешифратор 50 и в коммутаторе 54 (фиг. 4) вырабатывается элементами 59-61 импульс записи мантиссы MB, по которому открываются схемы И элементов 58. Через открытие схемы записывается параллельным кодом мантиссы М в регистр 55. Такое действие равносильно уменьшению веса разрядов мантиссы MB в раза.

При этом в сумматоре 46 выполянется операция mai+ MB2 . Учитывая, что старшие разряды результата преобразуются в преобразователе 44 в знакоразрядный код и вырабатывается коррекция знака ЗН2, получим промежуточную сумму Sm в виде (SmM-4«Ci-2)+MB-2- Оп, Окончательную сумму получаем из выхода преобразователя 44, как

р, mCi-21 |l, если Sm }С-3;

0, в остальных случаях, где Sm 3 выделение три знаковых ЗНЗ, ЗН2, ЗН1 и старший значащий разряды.

Нормализация вычисленной мантиссы m Ci-2 выполняется схемой 45 в первом такте по сигналу, поступающему на вход 22. В

мая сумма Sm тг то схемой 45 выдается

схеме анализируется два знаковых Зн2, Зн1 и старший значащий разряды.

При этом, если Sm S1, то схемой 45 выдается положительное приращение передачи ДПс +1, которое выдается элементом 53, на вход суммирующего устройства. По приращению АПС + 1 устанавливается триггер 52 в единичное состояние и потенциалом единичного выхода открываются ее ответствующие схемы И элементов 53ч, 532. При этом дополнительно включаются элементы 512, 514 задержки, что равносильно делению числа тс на 2. Если промежугоч- 2

приращение ДПс -1. Поэтому приращение переключает триггер 52 в единичное состояние и потенциалом единичного выхода открываются соответствующие элементы и элементы 53ч, 532. При этом -включаются элементы 511, 512 задержки, что равносильно умножению глс1 на 2. Результат в виде знакоразрядного кода C1 mc12nc поступает из суммирующего устройства 35 на вход блока 36 приема переменной (фиг. 2) и, кроме того, поступает на вход блока 5 переменной интегрирования через элементы И 31, 32 (фиг. 1). В блоке 36 приема переменной (фиг. 2) по результату знакоразрядного кода С1 вычисляется новое значение переменной В в обычной двоичной системе счисления. При этом по знаку старшего разряда ПВ1 выполняется в сумматоре 40 операция суммирования вычисления старшего единичного-разряда - масштабного импульса, поступающего из регистра 41, с нулевым кодом, поступающим из регистра 42. В исходном состоянии в старшем разряде регистра 41 записан начальный масштабный импульс. Во всех последующих тактах по знакам 1-х разрядов в сумматоре 40 суммируются (вычитаются) единичные весовые разряды с меньшим весом за счет сдвига в регистре 41 масштабного импульса RI вправо на .разряд в каждом такте. Сформированный порядок Пв записывается в счетчик 37 по сигналу, поступающему на вход31з. По окончании действий над порядками регистр 422 сбрасывает.нуль и в регистр 41 записывается по входу 192 масштабный импульс. Операция преобразования знакоразрядного кода мантиссы тс1 в обычный код совмещена во времени с операцией нормализации мантиссы MB. Нормализация мантиссы Мв выполняется с первого до последнего разряда схемой 38 по условию Мв . В результате нормализации вырабатывается схемой 38 приращение порядка . По этому приращению

запрещается сдвиг масштабного импульса в регистре 41 вправо, корректируется порядок Пв в счетчике 37, т.е. .

Формирование мантисы Мв осуществ- ляе.тся .в соответствии с выражением

ляется в соответствии

MB1 MBM+Rlma1-1.

0

:.. .. - j2Me, если MB 2 1МВН:1мв,если если МВ-1; 2S2 1J2 R| , если MB.

пк .Jf18-1 если MB 2 1; (Пц.если MBS .

где MB - 1-е значение мантиссы переменной В;

5 Мвн - нормализованное значение мантиссы;

RI - вес 1-го разряда мантиссы тс1 (значение масштабного импульса).

Процесс формирования мантиссы пере- 0 менной Мв поясним на примере. П р и м е р 3. mc1 0010lT;

1Т:Мв 0+2 .0-0;

5

0

(: 2м;ПВ: -1; 2Т:М8: 0+2 1.

STiMB O 1 ,1; ,1;

-1

4Т:МВ: О.И-2 |.,1; ,1; ,

5Т:Мв:0,.,011.-. -з.

(0,011): , 6Т:Мв: 0,11+2 3-1 0.101; ,101; ПВ;«-3. Вычисление точного значения перемен- 5 ной интегрирования осуществляется вычислителем 5 (фиг. 1) в четыре этапа, причем в первых трех этапах выполняется дополнительная операция умножения дифференциалов на коэффициенты 3/2 и 3, так 0 ..

Представив 3/2а, как 3/8 та2Па+2 и За как 3/8 та2Па+3 во избежание переполнения, получим значение мантиссы промежуточной суммы, в первом, втором этапах, в 5 виде:.,

Г 2(М5|+2-4тСм)+3/йЧтан-22-( «

М51 Гесли

).

2(MSl+1-4mCi-i fMB.24a -i-3/8mai+2l Чесли бП-2, 0 где MSl+2-(i+2) - значение мантиссы промежуточной суммы в обычной двоичной системе счисления;

тСм-(Ы) - разряд мантиссы окончательной суммы в избыточной двоичной сис- 5 теме счисления;

тажг-(+2) - разряд значения дифференциала, соответствующего переменной; 5П - разность порядков.

На третьем этапе интегрирования манисса промежуточной суммы определяется ак

{ 2(М5|+2-4тСи)+3/8та|+22Л5п-з),

MSl+24- если , А

Ь(М5м-4тСм)43/втан Мв«-« н91 если-ГН-3

Мантисса точного значения переменой определяется как

С1 если 3; mCiMl если MSI+2 Ј -3; (О в остальных случаях,

где MSI+2 - выделенные три знаковых и тарший значащий разряды мантиссы MS 4

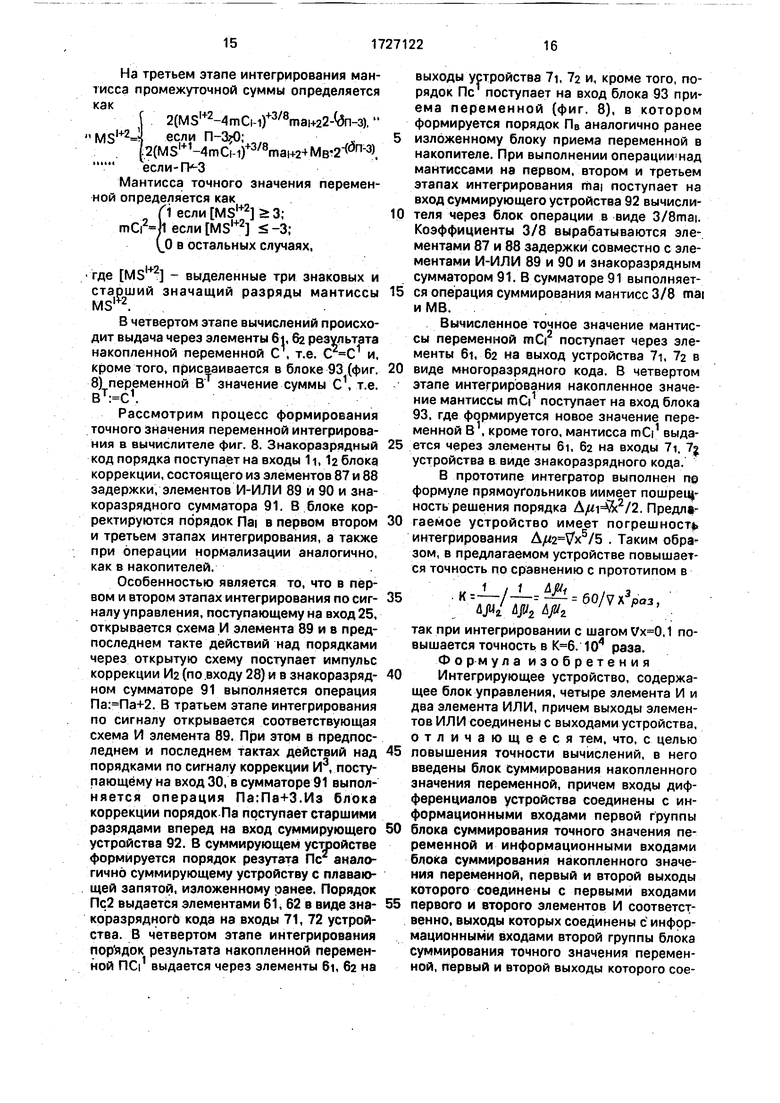

В четвертом этапе вычислений происхоит выдача через элементы 6i, 62 результата накопленной переменной С , т.е. С С1 и, кроме того, присваивается в блоке 93 (фиг. ) переменной Вт значение суммы С1, т.е. ,

Рассмотрим процесс формирования точного значения переменной интегрирования в вычислителе фиг. 8. Знакоразрядный код порядка поступает на входы 11,1a блока коррекции, состоящего из элементов 87 и 88 задержки, элементов И-ИЛИ 89 и 90 и зна- коразрядного сумматора 91. В блоке корректируются порядок Па| в первом втором и третьем этапах интегрирования, а также при операции нормализации аналогично, как в накопителей.

Особенностью является то, что в первом и втором этапах интегрирования по сигналу управления, поступающему на вход 25, открывается схема И элемента 89 и в предпоследнем такте действий над порядками через открытую схему поступает импульс коррекции Иг (по .входу 28) и в знакоразряд- ном сумматоре 91 выполняется операция . В тратьем этапе интегрирования по сигналу открывается соответствующая схема И элемента 89. При этом в предпоследнем и последнем тактах действий над порядками по сигналу коррекции И3, поступающему на вход 30, в сумматоре 91 выполняется операция Па:Па+З.Из блока коррекции порядок Па поступает старшими разрядами вперед на вход суммирующего устройства 92. В суммирующем устройстве формируется порядок резутата Пс аналогично суммирующему устройству с плавающей запятой, изложенному ранее. Порядок Пс2 выдается элементами 61, 62 в виде зна- коразрядного кода на входы 71, 72 устройства. В четвертом этапе интегрирования пор ядок результата накопленной переменной nd1 выдается через элементы 6i, 62 на

выходы устройства 7i, 72 и, кроме того, порядок Пс поступает на вход блока 93 приема переменной (фиг. 8), в котором формируется порядок Пв аналогично ранее

изложенному блоку приема переменной в накопителе. При выполнении операции над мантиссами на первом, втором и третьем этапах интегрирования mai поступает на вход суммирующего устройства 92 вычислителя через блок операции в виде 3/8mai. Коэффициенты 3/8 вырабатываются элементами 87 и 88 задержки совместно с элементами И-ИЛИ 89 и 90 и знакоразрядным сумматором 91. В сумматоре 91 выполняется операция суммирования мантисс 3/8 mai и MB.

Вычисленное точное значение мантиссы переменной mCi2 поступает через элементы 6.1,-62 на выход устройства 7i, 1г в

виде многоразрядного кода. В четвертом этапе интегрирования накопленное значение мантиссы mCi1 поступает на вход блока 93. где формируется новое значение переменной В1, кроме того, мантисса mCi1 выдается через элементы 6i, 62 на входы 7i, 7j устройства в виде знакоразрядного кода.

В прототипе интегратор выполнен п0 формуле прямоугольников иимеет пошрещ- ность решения порядка . Предл гаемое устройство имеет погрешности интегрирования . Таким образом, в предлагаемом устройстве повышается точность по сравнению с прототипом в

. кД-/-и бО/7хар«,

djM/ W2 Wz

так при интегрировании с шагом ,1 повышается точность в . 104 раза. Формула изобретения

Интегрирующее устройство, содержащее блок управления, четыре элемента И и два элемента ИЛИ, причем выходы элементов ИЛИ соединены с выходами устройства, отличающееся тем, что, с целью

повышения точности вычислений, в него введены блок суммирования накопленного значения переменной, причем входы дифференциалов устройства соединены с информационными входами первой группы

блока суммирования точного значения переменной и информационными входами блока суммирования накопленного значения переменной, первый и второй выходы которого соединены с первыми входами

первого и второго элементов И соответственно, выходы которых соединены с информационными входами второй группы блока суммирования точного значения переменной, первый и второй выходы которого соединены с первыми входами второго и третьего элементов И соответственно, выходы которых соединены с первыми входами первого и второго элементов ИЛИ соответственно, вторые входы которых подключены к выходам первого и второго элементов И соотетствен- но, вход начальной установки устройства соединен с входами начальной установки блока управления блока суммирования накопленного значения переменной и блока суммирования точного значения переменной, первый и второй выходы блока управления соединены с вторыми входами первого и второго элементов И и вторыми входами третьего и четвертого элементов И соответственно, третий и четвертый выходы блока управления соединены с первыми управляющими входами блоков суммирования накопленного и точного значений переменной соответственно, вторые управ- ляющие входы этих блоков подключены к

пятому выходу блока управления, шестой выход которого соединен с третьим управляющим входом блока суммирования точного значения переменной, выходы первой и второй групп блока управления подключены к управляющим входам первой и второй групп соответственно блоков суммирования накопленного и точного значения переменной, седьмой и восьмой выходы блока управления соединены с четвертым и пятым управляющими входами соответственно блока суммирования точного значения переменной, девятый и десятый выходы блока управления подключены к третьему и четвертому входам управления блока суммирования накопленного значения переменных, кроме этого, десятый выход блока управления соединен с шестым управляющим входом блока суммирования точного значения переменной.

30

№

20

22

3t

35

+1 &

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1984 |

|

SU1226447A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для деления с плавающей запятой | 1979 |

|

SU860063A1 |

| Устройство для умножения | 1979 |

|

SU868751A1 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2069009C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1991 |

|

RU2006915C1 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

Ч

J7

А / .-А

я/

J2

-Ч

22

Ч

J

/ / /V

38

WM

Ј

v r

Т/

Фиг 2

7Г7

2

«а

-Ч

«2

Т,

v v

/Л 1

J5v2 J///

«s

2

л

r

MB

I

фиг. J

Sm П6 311

Фиг -Г

Г

5 cb

1

ZZILZLI

2S

Фцг. 8

и$ч

Авторы

Даты

1992-04-15—Публикация

1990-02-01—Подача