Дг.

вб/Jr

В iff

| название | год | авторы | номер документа |

|---|---|---|---|

| Система асинхронного сопряжения импульсных потоков | 1986 |

|

SU1427583A1 |

| ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ С ДВУСТОРОННИМ СОГЛАСОВАНИЕМ СКОРОСТИ | 1991 |

|

RU2022476C1 |

| Приемник синхросигнала | 1986 |

|

SU1424129A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| Устройство символьной синхронизации | 1990 |

|

SU1775869A1 |

Изобретение относится к электросвязи. Цель изобретения - улучшение использования пропускной способг ности канала связи. Система содержит на передающей стороне выделитель 1 тактовой частоты, временной детектор .2, блок динамической памяти (БДИ) 3, г-р 4 тактовых импульсов, логический блок 5, селектор 10 синхросигнала, блок управления (ВУ) 11 и делитель 12 частоты, а на приемной стороне приемник 6 синхросигнала, логический блок 7, блок фазовой автоподстройки 8 частоты, БДП 9, БУ 13 и делители 14 и ;15 частоты. Входной цифровой поток, -содержащий m бит, используемых для передачи циклового синхронизирующего сигнала, и п бит информационных, пос-- тупает на выделитель 1, к.оторый вьще-, ляет тактовую частоту, и на селектор 10, который входной цифровой поток задерж ивает на длительность синхронизирующей комбинации и передает его в БДП 3. Запись информации в БДП 3 осуществляется тактовой частотой вьвдели- теля 1, а считывание информации из БДП 3-станционной импульсной последовательностью г-ра 4. При этом на передающей стороне осуществляется введение дублирующей посыпки в пере-- даваемый сигнал, формируемый в БДП 3. Т.обр. на приемную сторону поступают сигнал с введенными в него дублирую-, щими посылками и сопровождающая его тактовая последовательность. После дешифрации квазипериодического синхросигнала и его задержки в приемнике 6 он поступает в БДП 9. При обнаружении циклов, в которые введены дублирующие посылки, эти посыпки не записьюаются в БДП 9. Считывание записанлой информации осуществляется восстановленной тактовой частотой. Цель достигаеглся введением селектора 10,БУ 11 и 13 и делителей 12, 14 и 15. Даны ил., выполнения БДП 3 и БУ 11 и 13. 4 ил. ... Ш (Л

-

ю

IZi

{

ггт

12

TJ

Изобретение относится к электросвязи и может применяться на линиях связи и сетях, использующих цифровые системы передачи.,

Цел изобретения - улучшение использования пропускной способности канала связи.

На фиг. 1 изображена структурная электрическая схема системы для асин-JQ хронного сопряжения импульсных потоков; на фиг.2-;- 4 - примеры выполнения, соответственно, блока динамической памяти передающей стороны и блоков управления передающей и приемной стог 15 рои.

Система для асинхронного сопряжения импульсных потоков содержит на передающей стороне в ьщелитель 1 тактовой частоты, временной детектор 2, 20 блок 3 динамической памяти, генератор 4 тактовых импульсов и логический блок 5, а на приемной стороне - йри- емник 6 синхросигнала, логический блок 7, блок 8 фазойой автоподстройки25 частоты и блок 9 Динамической памяти, и также содержит на передающей стороне селектор 10 синхросигнала, блок 11 .управления и делитель 12 частоты, а на приемной стороне - блок 13 управле- JQ ния, первый и второй делители 14 и 15 частоты.

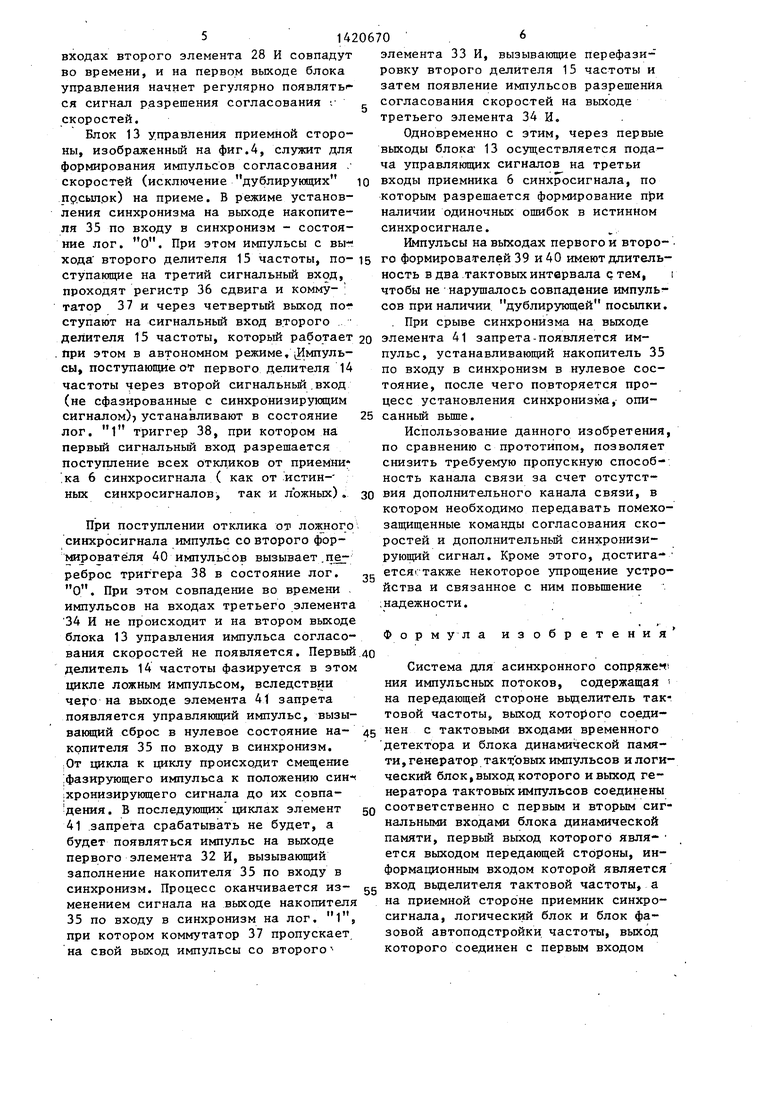

Блок 3 динамической памяти передающей стороны, изображенный на фиг.2, содержит первый элемент 16 И, первый регистр 17 сдвига, второй регистр 18 сдвига, второй элемент 19 И, третий регистр 20 сдвига, первый и второй элементы 21 и 22 ИЛИ и первые и вторые ячейки 23 и 24 памяти, каждая из которых состоит из элемента 25 памяти и элемента 26 И,

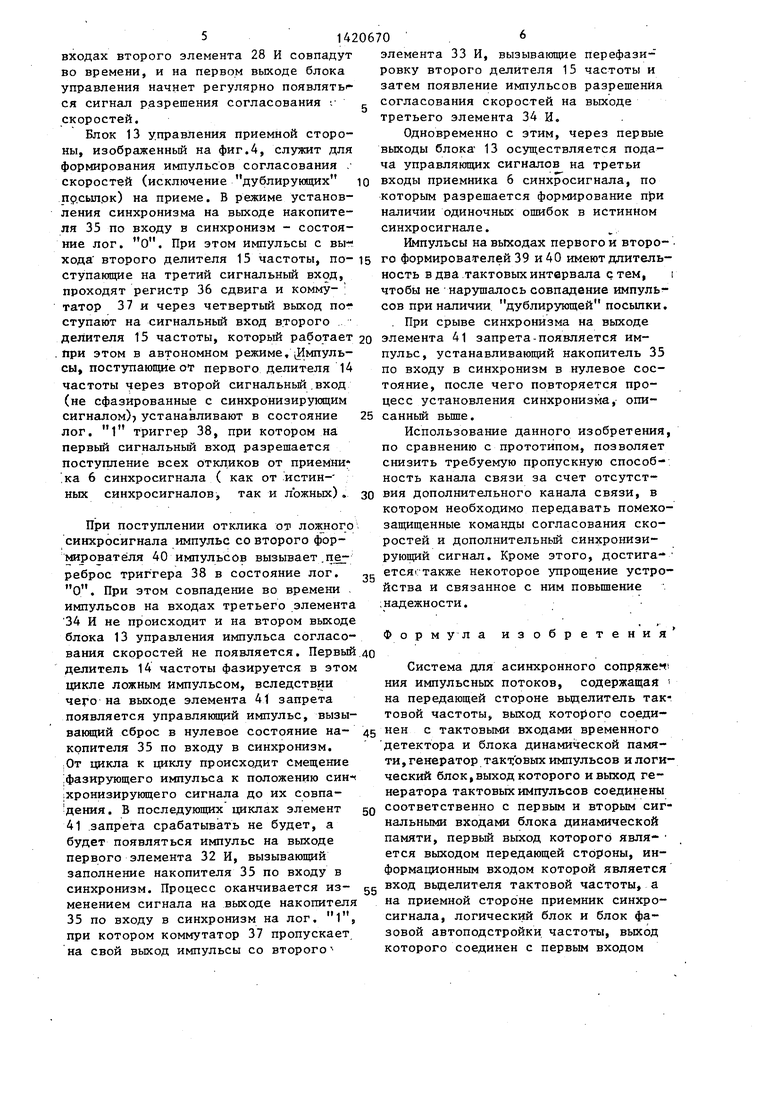

Блок 11 управления передающей стороны, изображенный на фиг.3, содержит первьш и второй элементы 27 и 28 И, первьй и второй регистры 29 и 30 . сдвига и триггер 31.

Блок 13 управления приемной стороны, изображенный на фиг.4, содержит пер- вый, второй и третий элементы 32, 33 и 34 И, накопитель 35 по входу в син- хронизм, регистр 36 сдвига, коммутатор 37,триггер 38, первый и второй формирователи 39 и 40 сигнала и элемент 41 запрета.

55 i

Система для асинхронного сопряжения

импульсных потоков работает следующим образом.

40

45

Выделитель 1 тактовой .частоты на передающей стороне из входного цифрового потока, содержащего т -бит, используемых для передачи циклового синхро- .низирующего сигнала, и п информационных бит (составляющих в сумме один цикл), вьщеляет тактовую частоту, которая поступает на тактовые входы ряда блоков передающей стороны. Генератор 4 тактовых импульсов вырабатьгоает станционную импульсную последовательность, частота которой незначительно 1превьщ1ает ( с учетом возможных неста- бильностей обоих частот) частоту, по-- лученную из входного цифрового пото- :ка. На первом выходе селектора 10 Син- хросигнала всякий раз появляются отклики, {согда во входном цифровом потоке появляется кодовая комбинация типа циклового синхронизирующего сигнала. Делитель 12 частоты, имеющий коэффициент деления tn + п , вьфабаты- вает на своем выходе последовательность импульсов с частотой циклов входного сигнала. Блок 11 управления осуществляет фазировку делителя 12 частоты узкими управляющими импульсами, поступающими на его сигнальньй вход. На третий сигнальный вход блока 3 динамической памяти с селектора 10 синхросигнала поступает задержанный на длительность синхронизирующей комбинации входной цифровой поток. Запись информации в ячейки блока 3 динаг-. мической памяти осуществляется так- товой .частотой с выхода выделителя 1 тактовой частоты. Считывание информации из блока 3 динамическбй памяти осуществляется станционной импульсной последовательностью,.вырабатываемой генератором 4 тактовых импульсов. Временной детектор 2, подключенный ко вторым выходам блока 3 динамической памяти, определяет сдвиг.фаз, действующий между соответствующими импульсами записи и считывания информации.

При достижении сдвига фаз, равного тактовому интервалу станционной частоты, на третьем входе логического блока 5 появляется х:игнал лог. 1 и схема переходит в режим ожидания сигнала согласования скоростей, вьграба- тываемого блоком 11 управления на определенной временной позиции, например, на границе цикла принимаемого с сигнала. По этому сигналу логический блок 5 исключает один тактовьй им-. пульс из стационной последовательности, поступающей на первый сигналь- ньй вход блока 3 динамической памяти. Благодаря этому осуществляется введение дублирующей посьшки в передаваемый сигнал, формируемьм в блок 3 дин амической памяти.

На входах приемной стороны дейг ствует сигнал с введенными в него дублирующими посылками и сопровож. дающая его тактовая последовательность, формируемые обычным регенератором (не показан).

Приемник 6 синхросигнала осуществ- ляет дешифрацию квазипериодического синхросигнала и соответствующую задержку принимаемого сигнала, подаваемого на третий вход блока 9 динамической памяти. Первый и второй дели тели 14 и 15 частоты имеют коэффициент деления, равный m +п, и выраба- тырают импульсы с частотой циклов ш-шульсного потока, подаваемые, соответственно, на второй и третий сигнальные входы блока 13 управления. Блок 13 управления формирует импульсы установки делителей 14 и 15 частоты и обнаруживает циклы, в которые введен дублирующие вставки, выра- батывая при этом на своем втором выходе сигнал исключения одного тактового импульса из тактовой последовательности. Исключение одного импульса осуществляется в логическом блоке 7 в момент поступления на третий вход блока- 9 динамической памяти дублиру- юще1й посьшки, т.е. эта посыпка не записывается- в блок динамической памяти. Считывание записанной информа.ции осуществляется тактовой частотой переданного сигнала, восстановленной блоком 8 фазовой автоподстройки частоты. На фиг.2 приведен пример выполнения блока 3 динамической памяти передающей стороны. Распределитель записи, состоящий из первого регистра 17 и первого элемента 16 И из тактовой частоты подлежащего передаче сигнала формирует ряд сдвинутых во

вая последовательность считывания от логического блока 5 поступает на пер- вьй сигнальньй вход. Второй регистр 18 сдвига и второй элемент 19 И образуют распределитель считывания, создающий импульсные последавательности, аналогичные импульсным последовательностям распределителя записи.

10 Считывание информации из элементов 25 памяти осуществляется через элементы 26 И. В первом элементе 21 ИЛИ осуществляется сборка полного сигна-: ла, включающего дублирующие посыл15 ки. Сигналы с одноименных ячеек первого и второго регистрав 17 и 18 .- сдвига через вторые выходы поступают на соответствукщие входы временного детектора 2. Сигнал разрешения согла

20 сования скоростей, формируемый блоком 11 управления, через 4 сигнальный вход записывается во вторые ячейки 24 памяти и считывается импульсами, вырабатываемыми третьим регистром сдвиг

30

25 га, на тактовый вход которого через второй сигнальный вход поступает та к- товая последовательностьнепосредственно от генератора 4 тактовых импу- -льсов. На вьпсоде второго элемента 22 ИЛИ формируется сигнал управления работой логического блока 5.

На фиг.3 представлен пример выполнения блока 11 управления передающей стороны. В режиме установления син-ч хр.онизма отклики селектора 10 синхросигнала и импульсы с делителя 12 частоты, поступакяцие соответственно рез первьш и второй сигнальные входы, не совпадают во времени. Текущий импульс с делителя 12 частоты устанавливает триггер 31 в состояние 1, при котором первый,элемент 27 И от- : крыт для прохождения отклика (от истинного синхросигнала или ложного).

. Этот отклик, проходя через первый резв

40

гистр 29 сдвига,вызьшает сброс триггера 31 в состояние О и установку в начальное состояние делителя 12 частоты.В случае отклика, вызванного ложным син- времени импульсньк последовательное- gQ хросигналом, второй элемент 28 И не тей, управляющих, записью информации срабатывает, и импульс разрешения со,в элементы 25 памяти первых ячеек 23 памяти. Частота каждой из сдвинутых последовательностей меньше тактовой частоты в число раз, равное -числу первых или вторых ячеек памяти (6). Информация, подлежащая записи, пос- тупает.;через третий сигнальный вход от селектора 10 синхросигнала, Такто55

гласования скоростей не появится на первом выходе. Однако новая ,ф.азировка делителя 12 частоты приводит к смещению импульса на втором сигнальном входе ближе к временному, положению : - истинного-синхросигнала. В процессе такого смещения наступает момент - . синхронизм, когда импульсы на обоих

0670

вая последовательность считывания от логического блока 5 поступает на пер- вьй сигнальньй вход. Второй регистр 18 сдвига и второй элемент 19 И образуют распределитель считывания, создающий импульсные последавательности, аналогичные импульсным последовательностям распределителя записи.

10 Считывание информации из элементов 25 памяти осуществляется через элементы 26 И. В первом элементе 21 ИЛИ осуществляется сборка полного сигна-: . ла, включающего дублирующие посыл15 ки. Сигналы с одноименных ячеек первого и второго регистрав 17 и 18 .- сдвига через вторые выходы поступают на соответствукщие входы временного детектора 2. Сигнал разрешения согла

20 сования скоростей, формируемый блоком 11 управления, через 4 сигнальный вход записывается во вторые ячейки 24 памяти и считывается импульсами, вырабатываемыми третьим регистром сдвиг

га, на тактовый вход которого через второй сигнальный вход поступает та к- товая последовательностьнепосредственно от генератора 4 тактовых импу- льсов. На вьпсоде второго элемента 22 ИЛИ формируется сигнал управления работой логического блока 5.

На фиг.3 представлен пример выполнения блока 11 управления передающей стороны. В режиме установления син-ч хр.онизма отклики селектора 10 синхросигнала и импульсы с делителя 12 частоты, поступакяцие соответственно рез первьш и второй сигнальные входы, не совпадают во времени. Текущий импульс с делителя 12 частоты устанавливает триггер 31 в состояние 1, при котором первый,элемент 27 И от- : крыт для прохождения отклика (от истинного синхросигнала или ложного).

Этот отклик, проходя через первый ре

гистр 29 сдвига,вызьшает сброс триггера 31 в состояние О и установку в начальное состояние делителя 12 частоты.В случае отклика, вызванного ложным син- росигналом, второй элемент 28 И не срабатывает, и импульс разрешения со55

гласования скоростей не появится на первом выходе. Однако новая ,ф.азировка делителя 12 частоты приводит к смещению импульса на втором сигнальном входе ближе к временному, положению : - истинного-синхросигнала. В процессе такого смещения наступает момент - . синхронизм, когда импульсы на обоих

входах второго элемента 28 И совпадут во времени, и на первом выходе блока управления начнет регулярно появляты- ся сигнал разрешения согласования ; скоростей.

Блок 13 управления приемной стороны, изображенный на фиг.4, служит для формирования импульсов согласования . скоростей (исключение дублирующих пр.сьшок) на приеме. В режиме установления синхронизма на выходе накопителя 35 по входу в синхронизм - состояние лог. о. При этом импульсы с выг

хода второго делителя 15 частоты, по-ig го формирователей 39 и 40 имеют длительступающие на третий сигнальньй вход, проходят регистр 36 сдвига и комму- татор 37 и через четвертый выход nor ступают на сигнальный вход второго . делителя 15 частоты, который работает 2о элемента 41 запрета-появляется им- . при этом в автономном режиме,Импyль- пульс, устанавливающий накопитель 35

ность в два .тактовых интервала Q тем, чтобы не нарушалось совпадение импульсов при наличии, дублирующей посылки. . При срыве синхронизма на выходе

сы, поступающие от первого делителя 14 частоты через второй сигнальньй .вход (не сфазированные с синхронизирующим сигналом) устанавливают в состояние лог. 1 триггер 38, при котором на первый сигнальный вход разрешается поступление всех откликов от приемни

как от истин- так и ложных).

ка 6 синхросигнала ( ных синхросигналов.

по входу в синхронизм в нулевое состояние, после чего повторяется процесс установления синхронизма, опи25 санньй вьш1е.

Использование данного изобретения по сравнению с прототипом, позволяет снизить требуемую пропускную способность канала связи за счет отсутст30 ВИЯ дополнительного канала связи, в котором необходимо передавать помехо защищенные команды согласования скоростей и дополнительный синхронизирующий сигнал. Кроме этого, достига- ется1: также некоторое упрощение устро йства и связанное с ним повьш1ение надежности.

При поступлении отклика от ложного синхросигнала импульс со второго формирователя 40 импульсов вызывает.nej реброс триггера 38 в состояние лог. о. При этом совпадение во времени импульсов на входах третьего элемента 34 И не происходит и на втором выходе блока 13 управления импульса согласования скоростей не появляется. Первый делитель 14 частоты фазируется в этом цикле ложным импульсом, вследствии чего на выходе элемента 41 запрета появляется управлянлций импульс, вызывающий сброс в нулевое состояние на- крпителя 35 по входу в синхронизм. ;0т цикла к циклу происходит Смещение фазирующего импульса к положению син- ;хронизирующего сигнала до их совпа- дения. В последующих циклах элемент 41 .запрета срабатывать не будет, а будет появляться импульс на выходе первого элемента 32 И, вызывающий заполнение накопителя 35 по входу в синхронизм. Процесс оканчивается из- менением сигнала на выходе накопителя 35 по входу в синхронизм на лог. 1, при котором коммутатор 37 пропускает на свой выход импульсы со второго

элемента 33 И, вызывающие перефази- ровку второго делителя 15 частоты и затем появление импульсов разрешения согласования скоростей на выходе третьего элемента 34 И.

Одновременно с этим, через первые выходы блока 13 осуществляется подача управляющих сигналов на третьи входы приемника 6 синхросигнала, по которым разрешается формирование при наличии одиночных ошибок в истинном синхросигнале.

Импульсы на выходах первого и второэлемента 41 запрета-появляется им- пульс, устанавливающий накопитель 35

ность в два .тактовых интервала Q тем, i чтобы не нарушалось совпадение импульсов при наличии, дублирующей посылки. . При срыве синхронизма на выходе

35

до 45 50 gg

по входу в синхронизм в нулевое состояние, после чего повторяется процесс установления синхронизма, опи25 санньй вьш1е.

Использование данного изобретения по сравнению с прототипом, позволяет снизить требуемую пропускную способность канала связи за счет отсутст30 ВИЯ дополнительного канала связи, в котором необходимо передавать помехо защищенные команды согласования скоростей и дополнительный синхронизирующий сигнал. Кроме этого, достига- ется1: также некоторое упрощение устройства и связанное с ним повьш1ение надежности.

Формула изобретения

Система для асинхронного сопряжеч ния импульсных потоков, содержащая на передающей стороне вьщелитель тактовой частоты, выход которого соединен с тактовыми входами временного детектора и блока динамической памяти, генератор тактговых импульсов и логический блок,выход которого и выход генератора тактовых импульсов соединены соответственно с первым и вторым сигнальными входами блока динамической памяти, первьй выход которого явля- ется выходом передающей стороны, информационным входом которой является вход вьщелителя тактовой частоты, а на приемной стороне приемник синхросигнала, логический блок и блок фазовой автоподстройки частоты, выход которого соединен с первым входом

блока AHHaNtH4ecKOH памяти, второй и первый выход которого подключены соответственно к выходу логического блока и первому входу блока фазовой автоподстройки частоты, причем информационным выходом системы, сигнальным и тактовым входами приемной стороны являются соответственно второй выход блока динамической памяти и первый и второй входы приемника синхросигнала, отли,чающаяся тем, что с целью улучшения использования пропускной способности канала связи, введены на передающей стороне селектор синхросигнала, блок управления и делитель частоты, тактовый вход которого объединен с выходом вьщелителя тактовой частоты и тактовыми входами блока управления и селектора синхросигнала, сигнальный вход, первьй и второй выходы которого подключены соответственно к входу вьиелителя тактовой частоты, перому сигнальному .входу блока управления и третьему сигнальному входу блока динамической памяти, четвертый сигнальный вход, вторые и третьи выходы которого соединены Соответственно с первым выхо- дом блока управления, первыми сигналь- ,ными входами временного детектора.и

11 г

. 1В

Такт: .gx.

Т

77

J-a СигндлвЗ

ТЕ

Si-т

82-2

RT

9UZ.2

первым входом логического блока, второй и третий входы которого пощслюче- ны соответственно к выходу генератора тактовых импульсов и выходу времен-- ного детектора, причем вторрй выход и второй сигнальный вход блока управ- ления соединены соответственно с сигнальным входом и выходом делителя ча,стоты, а второй сигнальный вход вре-: менного детектора подключен к третьему выходу блока динамической памяти, а на приемной стороне введены блок г управления, первьй и второй делители

мастоты, тактовые входы кото1УЫХ и тактовьй вход логического блока объединены с тактовым входом приемника синхросигнала, первьй и второй.выходы и третьи входы которого соединены соответственно с третьим входом блока динамической памяти, первым сигнальным входом и первыми выходами блока управления, второй и третий сигнальные -входы и второй, третий и четвертый выходы -которого подключены соответственно к выходу первого делителя частоты, выходу второго делителя частоты, сигнальному входу логического блока и сигнальным входам

первого и второго делителей частоты.

Распределитель | записи j.j

I Sno8

-лh

«-г/ сиг6х.

3-ий Лм.

2-й сиен. 1х.

фи. 3

Такт.бх

15

l cumSx.

.

фие.Ц

.

| :Левин Л.С | |||

| и др | |||

| Цифровые сие- , темы передачи информации | |||

| М.: Связь, 1982, с.56-57 рис.3.2. |

Авторы

Даты

1988-08-30—Публикация

1986-04-23—Подача