ВхК

1«

.

ВШК1

fMoi

Ч

СД 00

.

Вш

Здесь обнаруживаются циклы, в которых введены вставки, и в зависимости от того, обнаружены положительные или отрицательные,вставки, формируется одна из двух последовательностей импульсов для управления процессом

и-сключения вставок, введенных и. передающей стороне. После этого восстанавливаются первые символы синхросигналов и восстановленный импульсный поток поступает на соответствующий выход системы. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для асинхронного сопряжения импульсных потоков | 1986 |

|

SU1420670A1 |

| ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ С ДВУСТОРОННИМ СОГЛАСОВАНИЕМ СКОРОСТИ | 1991 |

|

RU2022476C1 |

| Устройство передачи цифровых сигналов | 1980 |

|

SU919129A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| Приемник синхросигнала | 1986 |

|

SU1424129A1 |

| СПОСОБ ТЕЛЕВИЗИОННОГО ВЕЩАНИЯ С ЗАЩИТОЙ ОТ НЕСАНКЦИОНИРОВАННОГО ПРИЕМА И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2013024C1 |

| Система передачи и приема цифровой информации | 1985 |

|

SU1288923A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1826135A1 |

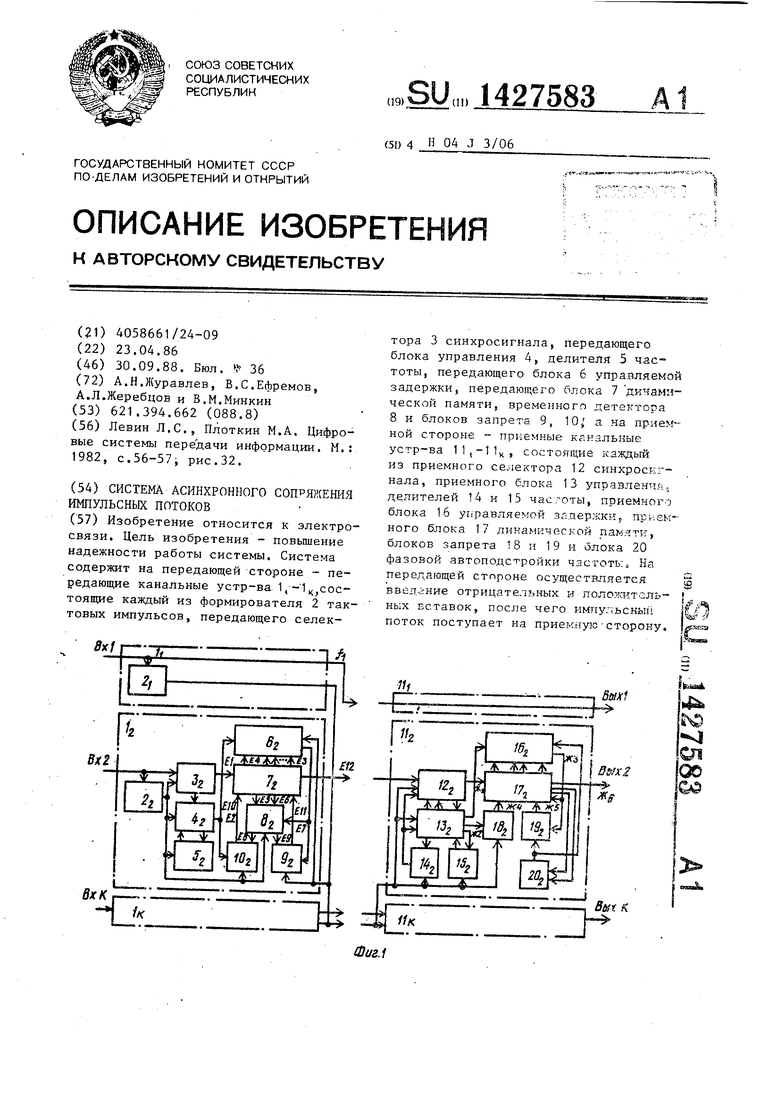

Изобретение относится к электросвязи. Цель изобретения - повышение надежности работы системы. Система содержит на передающей стороне - передающие канальные устр-ва 1, тоящие каждый из формирователя 2 тактовых импульсов, передающего селектора 3 синхросигнала, передающего блока управления 4, делителя 5 частоты, передающего блока 6 управляемой задержки, передающего блока 7 дичамн- ческой памяти, временного детектора 8 и блоков запрета 9, 10, а на приемной стороне - приемные канальные устр-ва 11,-11х состоящие каждый из приемного селектора 12 синхросмг- нала, приемного блока 13 управленчяо делителей 14 и 15 час готы, приемного блока 16 угфавляемой зйдержкис пряеь-;- ного блока 17 динамической памяти, блоков запрета 18 и 19 и блока 20 фазовой автоподстройки чзстоть:« На передающей стороне осуществляется отрицательных и пололдатгль- ных вставок, после чего импульсны поток поступает на приемную-сторону. S // У jL

1

Изобретение относится к электросвязи, а именно к устройствам передачи и приема дискретных сообщений с асинхронными вводами и выводом информации, и может быть использовано при разработке устройства асинхронного согласования скоростей импульсных

потоков на передающей и приемной сто- I

ронах.

Цель изобретения - повышение надежности работы системы.

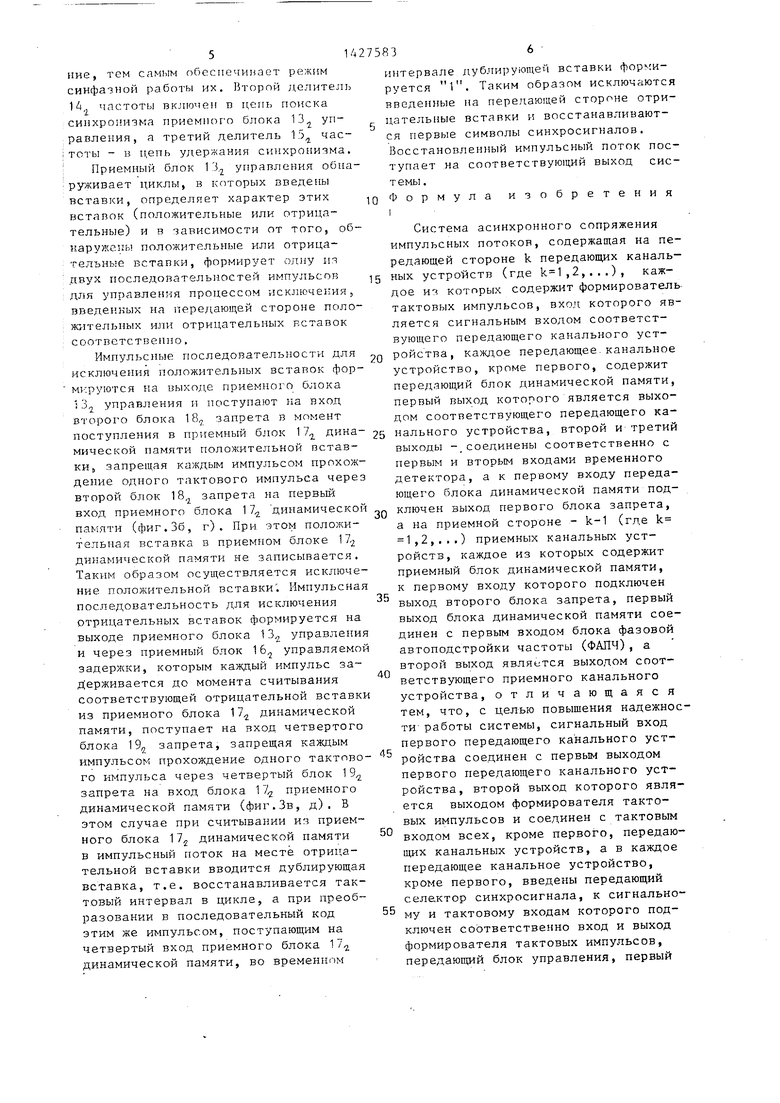

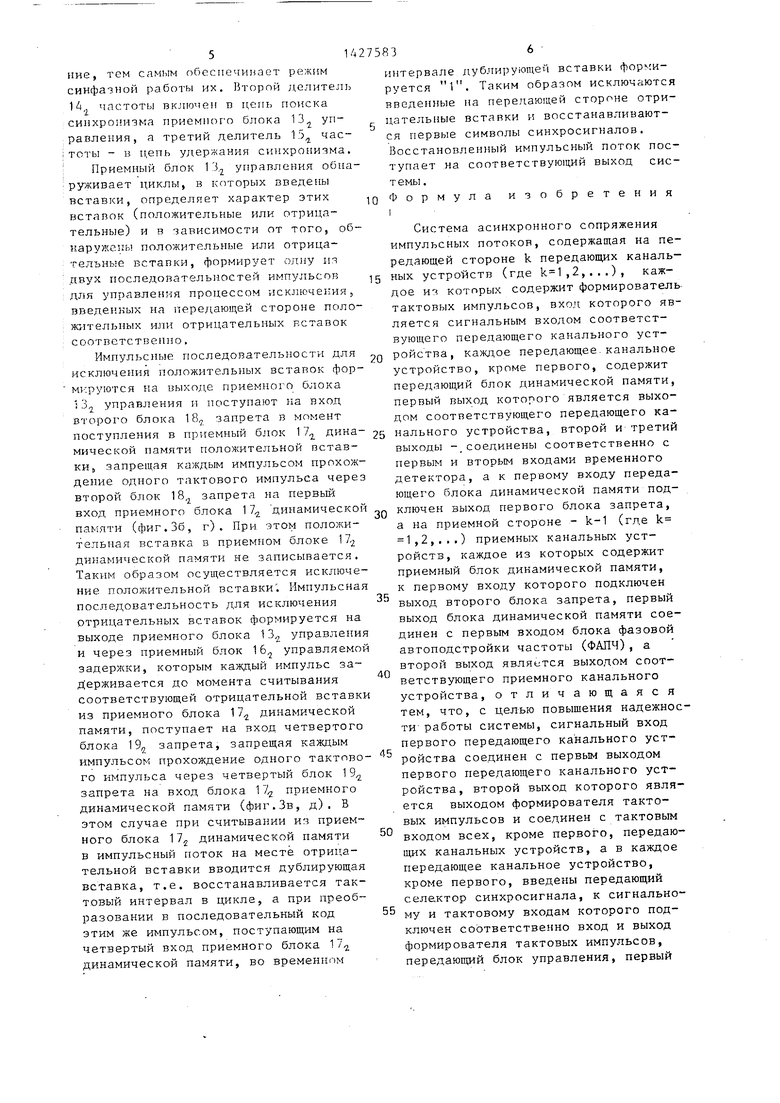

На фиг.1 представлена структурная электрическая схема системы асинхронного сопряжения импульсных потоков; на фиг.2 - временные диаграммы работы передающего канального устройства; на фиг.З - временные диаграммы работы приемного канального устройств а.

Система асинхронного сбпряжения импульсных потоков содержит на передающей стороне k передающих канальных устройств 1 (где ,2,...)s каждое канальное устройство содержит формирователь 2 тактовых импульсов, каждое канальное устройство, кроме первого, содержит передающий селектор 3, синхросигнала, передающий блок 4; управления, первый делитель 5 частоты, передающий блок 6 у управляемой

Система асинхронного сопряжения импульсных ПОТ-ОКОВ работает следующим образом.

На передающей стороне для каждого

5 импульсного потока имеется передающее канальное устройство 1j,, вход которого является входом соответствующего импульсного потока системы. С входа передающего канального устройства 1,

10 импульсный поток поступает на вход формирователя 2, тактовых импульсов и на выход передающего канального устройства 1( . Формирователь 2, тактовых импульсов выделяет из импульс15 ного потока спектральную составляющую тактовой частоты и формирует тактовые импульсы считывания для остальных канальных, устройств.

Для остальных импульсных потоков

20 рассмотрим работу на примере передающего канального устройства 1. На фиг.2 изображены временные диаграммы в характерных точках передающего канального устройства 1,2.

25 С входа передающего канального

устройства 1 импульсный поток поступает на вход формирователя 2 тактовых импульсов и на вход передающего селектора 3} синхросигнала. Формирозадержки, передающий блок 7- динами- 30 ватель 2 тактовых импульсов выделя- ческой памяти, временной детектор первый 9ц и третий 10, блоки запрета; а на приемной стороне - k-1-приемных канальных устройств 11ц (где , 2 .,.), каждое приемное канальное 5 устройство содержит приемный селектор 12| синхросигнала, приемный блок 13 управления, второй 14, и третий 15i делители частоты, приемный блок 16| управляемой задержки, приемный блок 0 М динамической памяти, второй блок 18 запрета, четвертый блок 19ц. запрета, блок 20t фазовой автоподстройка частоты (ФАПЧ).

ет из импульсного потока спектральную составляющую тактовой частоты и формирует тактовые импульсы, которые используются для хронирования работы блоков передающего канального устройства 1.

Импульсный поток с входа передающего селектора 3 синхросигнала проходит через регистр сдвига, расположенный в нем, и поступает на вьпсод передающего селектора 3 синхросигнала и далее на вход блока 7 передающей динамической памяти (фиг.2а). С выхода передающего селектора 3

Система асинхронного сопряжения импульсных ПОТ-ОКОВ работает следующим образом.

На передающей стороне для каждого

импульсного потока имеется передающее канальное устройство 1j,, вход которого является входом соответствующего импульсного потока системы. С входа передающего канального устройства 1,

импульсный поток поступает на вход формирователя 2, тактовых импульсов и на выход передающего канального устройства 1( . Формирователь 2, тактовых импульсов выделяет из импульсного потока спектральную составляющую тактовой частоты и формирует тактовые импульсы считывания для остальных канальных, устройств.

Для остальных импульсных потоков

рассмотрим работу на примере передающего канального устройства 1. На фиг.2 изображены временные диаграммы в характерных точках передающего канального устройства 1,2.

С входа передающего канального

устройства 1 импульсный поток поступает на вход формирователя 2 тактовых импульсов и на вход передающего селектора 3} синхросигнала. Формирователь 2 тактовых импульсов выделя-

ет из импульсного потока спектральную составляющую тактовой частоты и формирует тактовые импульсы, которые используются для хронирования работы блоков передающего канального устройства 1.

Импульсный поток с входа передающего селектора 3 синхросигнала проходит через регистр сдвига, расположенный в нем, и поступает на вьпсод передающего селектора 3 синхросигнала и далее на вход блока 7 передающей динамической памяти (фиг.2а). С выхода передающего селектора 3

синхросигнала синхроимпульсы поступают на вход перелающего блока 4 управления.

Первый делитель 5 частоты осуществляет деление тактовой частоты на m+n. В результате на его выходе формируются импульсы с частотой, равной частоте следования циклов в импульсном потоке, и поступают на вход блока 4 управления, который формирует импульсы для установки первого делителя частоты 5 в начальное состояние, тем самым обеспечивает режим синфазной работы его. Кроме того, передающий блок 4 управления формирует импульсы для управления согласованием скоростей, которые снимают с второго выхода и поступают на вход передающего блока 6 управляемой за- держки и вход третьего блока запрета (фиг.26).

С помощью тактовых импульсов записи, поступающих с формирователя 2 тактовых импульсов черея третий блок запрета 10 на вход блока 7 передающей динамической памяти, осуществляется запись поступающих импульсов импульсного потока в блок 7 передающей динамической памяти, а с помощью тактовых импульсов считывания, поступающих от формирователя 2 тактовых импульсов через первый блок запрета 9j на первый вход передающего блока 7 динамической памяти, осуществляется считывание записанных импульсов. При этом в зависимости от знака i разности скоростей записи и считыва- ния периодически вводятся положительные или отрицательные вставки для согласования скоростей, когда изменение временных интервалов мелоду импульсными последовательностями записи и считывания достигает периода считывания. Этот момент обнаруживается с помощью временного детектора S, на соответствующем выходе которого при этом формируется потенциал 1 и поступает на соответствующий вход первого 9 или третьего 10, блоков

запрета. С этого момента соответст- вующий блок 9 или 10 запрета переходит в режим ожидания импульса согласования скоростей (фиг.2в - 2м).

При f J fg, где fj и f. - частоты записи и считывания соответствен- но, вводятся отрицательные вставки.

Импульс согласования скоростей с второго выхода передающего блока

о с ,.

5 5

0

управления поступает на вход третьего блока lOj запрета и при наличии на его входе импульса с временного детектора 8 запрещает прохожденг1е одного тактового импульса записи па вход блока 72 передающей динамической памяти. Таким образом осуществляется введение отрицательной рставки.

При f, « f(.- вводятся положительные нставки. Импульс согласованял скоростей с выхода передающего блока 4., управления поступает на вход передающего блока 6 управляемой задержки, задерживается им до момента считывания соответствующего символа из передающего блока 7 динамической памяти, поступает на вход первого блока 92 запрета и при наличии H;-i- пульса с временного детектора 8 на входе первого блока 9 запрета запрещает прохождение одного тактового импульса считывания на вхпл передающего блока 7 динамической Г1а--.яти. Таким образом осуществлягтся введр.нке положительной вставкя. Далее импульсный поток поступает на выход передающего канального устройства 1.

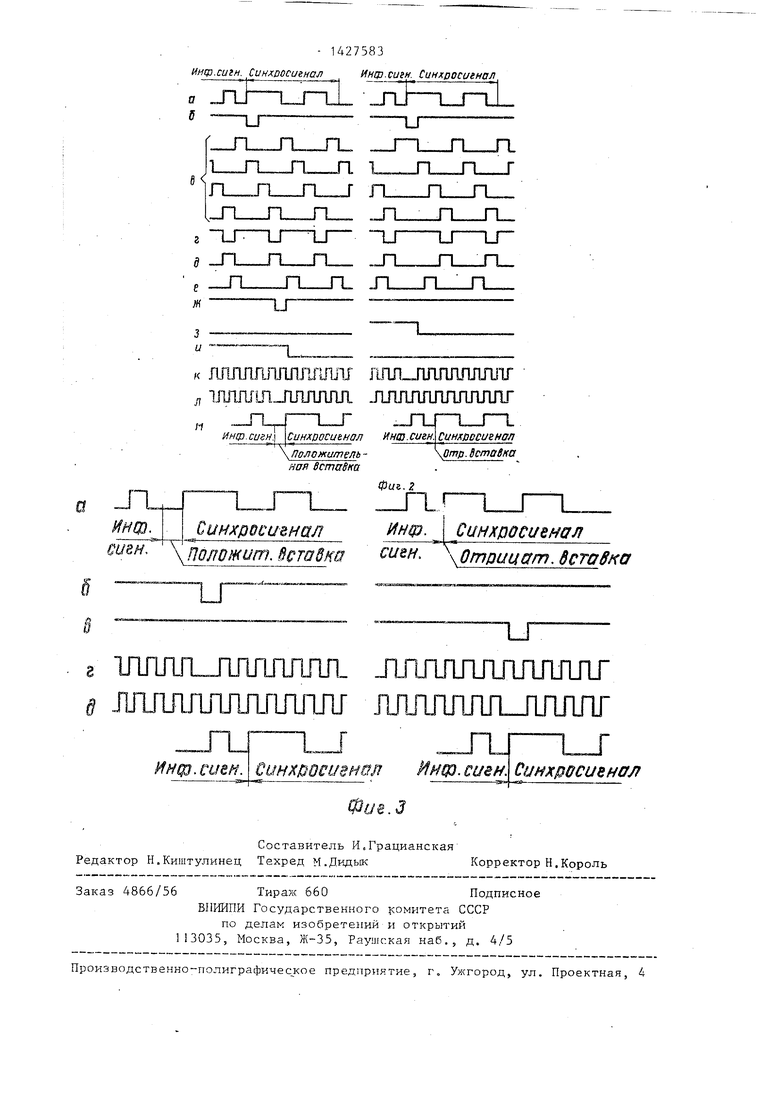

На приемной сторо -е первый импульсный поток не нуяодаетск в кпкпй- либо обработке, поэтому канально .: устройство для Hei o отсутствует, .пя остальных импульсных потоков paccMCf РИМ работу на примере приемного канального устройства 11. На фиг.З изображены временные- диаграммы р характерных точках приемного канального устройства 11,,.

Импульсньш поток с входа приемного селектора 12 синхросигнала проходит через регистр сдвига, расположенный в нем, и поступает на выход приемного селектора 12 синхросигнала и далее на вход приемного блока 172 динамической памяти (фиг.За). С выхода приемного селектора 12,2 синхросигнала синхроимпульсы поступают на вход приемного блока 13 управления.

Второй 14,2 и третий 15, делители частоты осуществляют деление такговой частоты на т+п, В результате ка их выходах формируются импульсы с частотой, равной частоте следования цкк:лов в импульсном потоке, и поступают на входы приемного блока 13, управления соответственно. Приемный блок 13 управления формирует импульсы для установки второго 14 и третьего 15 делителей частоты в начальное состояние, тем самым обеспечииает режнм синфазной работы их. Второй делитель 1, частоты включен в цепь поиска CHHxpoHHSNja приемного блока 13, уп- а третий делитель 15. часинтервале дублиругощеч вставки руется 1. Таким образом исключаются введенные на передающей стороне отрицательные вставки и восстанавливаются первые символы синхросигналов. Восстановленный импульсный поток поступает на соответствующий выход системы . Формула изобретения

10

i тоты - в цепь удерлчания синхронизма.

; Приемный блок Г3,2 управления обна:руживает циклы, в которых введены вставки, определяет характер этих вставок (положительные или отрицательные) и в зависимости от того, об- положительные или отрицательные вставки, формирует одну ия

двух последовательностей импульсов ,д ных устройств (где ,2,...), каж- для управления процессом исключения, дое из которых содержит формирователь введенных на передающей стороне положительных или отрицательных вставок соответственно.

Импульсные последовательности для д ройства, каждое передающее.канальное исключения положительных вставок фор- устройство, кроме первого, содержит мкруются на выходе приемного б:тока 3 управления и поступают на вход второго блока 18, запрета в момент поступления в приемный блок 17 дина- 25 нального устройства, второй и третий мической памяти положительной встав- выходы -,соединены соответственно с ки,, запрещая каждым импульсом прохождение одного тактового импульса через второй блок 18, запрета на первый вход приемного блока 17 динамической памяти (фиг.Зб, г). При этом положительная вставка в приемном блоке 17,2 динамической памяти не записывается. Таким образом осуществляется исключеСистема асинхронного сопряжения импульсных потоков, содержащая на передающей стороне k передающих канальтактов1з1Х импульсов, вход которого является сигнальным входом соответствующего передающего канального устпередающий блок динамической памяти, первый выход которого является выходом соответствующего передающего ка30

первым и вторым входами временного детектора, а к первому входу передающего блока динамической памяти подключен выход первого блока запрета, а на приемной стороне - k-1 (где k 1,2,...) приемных канальных устройств, каждое из которых содержит приемный блок динамической памяти, к первому входу которого подключен выход второго блока запрета, первый выход блока динамической памяти соединен с первым входом блока фазовой автоподстройки частоты (ФАЛЧ), а второй выход является выходом соответствующего приемного канального устройства, отличающаяся тем, что, с целью повышения надежности работы системы, сигнальный вход первого передающего канального устние положительной вставки . Импульсная последовательность /щя исключения отрицательных вставок формируется на выходе приемного блока 13, управления и через приемный блок 16 управляемой задержки, которым каждый импульс задерживается до момента считывания соответствующей отрицательной вставки из приемного блока 17 динамической памяти, поступает на вход четвертого блока 19 запрета, запрещая каждым

35

40

первым и вторым входами временного детектора, а к первому входу перед ющего блока динамической памяти по ключен выход первого блока запрета а на приемной стороне - k-1 (где k 1,2,...) приемных канальных устройств, каждое из которых содержит приемный блок динамической памяти, к первому входу которого подключен выход второго блока запрета, первы выход блока динамической памяти со динен с первым входом блока фазово автоподстройки частоты (ФАЛЧ), а второй выход является выходом соот ветствующего приемного канального устройства, отличающаяс тем, что, с целью повышения надежн ти работы системы, сигнальный вход первого передающего канального уст

импульсом прохождение одного тактово- ройства соединен с первым выходом

го импульса через четвертый блок 19 запрета на вход блока 17 приемного динамической памяти (фиг.Зв, д). В этом случае при считывании из приемного блока 17 динамической памяти в импульсный поток на месте отрицательной вставки вводится дублирующая вставка, т.е. восстанавливается тактовый интервал в цикле, а при преобразовании в последовательный код этим же импульсом, поступающим на четвертый вход приемного блока 17 динамической памяти, во временном

50

55

первого передающего канального уст ройства, второй выход которого явл ется выходом формирователя тактовых импульсов и соединен с тактовы входом всех, кроме первого, переда щих канальных устройств, а в каждо передающее канальное устройство, кроме первого, введены передающий селектор синхросигнала, к сигнальн му и тактовому входам которого под ключен соответственно вход и выход формирователя тактовых импульсов, передающий блок управления, первый

275836

интервале дублиругощеч вставки руется 1. Таким образом исключаются введенные на передающей стороне отрицательные вставки и восстанавливаются первые символы синхросигналов. Восстановленный импульсный поток поступает на соответствующий выход системы . Формула изобретения

10

Система асинхронного сопряжения импульсных потоков, содержащая на передающей стороне k передающих канальных устройств (где ,2,...), каж- дое из которых содержит формирователь

тактов1з1Х импульсов, вход которого является сигнальным входом соответствующего передающего канального устройства, каждое передающее.канальное устройство, кроме первого, содержит нального устройства, второй и третий выходы -,соединены соответственно с

передающий блок динамической памяти, первый выход которого является выходом соответствующего передающего каройства, каждое передающее.канальное устройство, кроме первого, содержит нального устройства, второй и третий выходы -,соединены соответственно с

первым и вторым входами временного детектора, а к первому входу передающего блока динамической памяти подключен выход первого блока запрета, а на приемной стороне - k-1 (где k 1,2,...) приемных канальных устройств, каждое из которых содержит приемный блок динамической памяти, к первому входу которого подключен выход второго блока запрета, первый выход блока динамической памяти соединен с первым входом блока фазовой автоподстройки частоты (ФАЛЧ), а второй выход является выходом соответствующего приемного канального устройства, отличающаяся тем, что, с целью повышения надежности работы системы, сигнальный вход первого передающего канального устройства соединен с первым выходом

0

5

первого передающего канального устройства, второй выход которого является выходом формирователя тактовых импульсов и соединен с тактовым входом всех, кроме первого, передающих канальных устройств, а в каждое передающее канальное устройство, кроме первого, введены передающий селектор синхросигнала, к сигнальному и тактовому входам которого подключен соответственно вход и выход формирователя тактовых импульсов, передающий блок управления, первый

7

делитель частоты, передающий блок управляемой задержки и третий блок запрета, к первому входу которого

подключены третий вход временного детектора и тактовые входы передаю- щег.о блока управления, первого делителя частоты и передающего селектора синхросигнала, первый и второй выходы которого соединены соответственно с вторым входом передающего блока динамической памяти и первым сигнальным входом передающего блока управления, к второму сигнальному входу которого подключен выход перво го делителя частоты, к сигнальному входу которого подключен первый выход передающего блока управления, второй выход которого соединен с вторым .входом третьего блока запрета и первым входом передающего блока управляемой задержки, к второму входу которого подключен первый вход первого блока запрета, который является тактовым входом соответствующего передающего канального устройства, а также к третьему входу передающего блока динамической памяти подключен выход третьего блока запрета, к третьему входу которого подключен первый выход временного детектора, второй выход которого соединен с вторым входом первого блока запрета, к третьему входу которого подключен четвертый вход временного детектора и выход передающего блока управляемо задержки, к третьему входу которого подключен четвертый выход передающего блока динамической памяти, L дополнительных выходов которого соединены соответственно с L дополнительными входами передающего блока управляемой задержки, а на приемной стороне в приемные канальные устройства введены приемный селектор синхросигнала, первый сигнальный и тактовый входы которого являются соответствую

.

10

20

25

- 15 й 4275838

щими входами каждого, кроме первого, приемного канального устройства, а выход - соединен с вторыМ входом приемного блока динамической памяти«

Ц

приемный блок управления, второй и третий делители частоты, приемный блок управляемой задержки и четвертый блок запрета, к первому входу кото рого подключен первый вход приемного блока управляемой задержки к выход блока ФАПЧ, к второму входу которого подключен третий выход приемного блока динамической памяти, к третьему входу которого подключен второй вход четвертого блока запрета и выход приемного блока управляемой задержки, к второму входу которого подключен первый выход приемного блока управления, второй выход которого соединен а первым входом второго блока запрета, к второму входу которого псдхл;э чены тактовые входы второго н т етье- го делителей частоты, псовый вхсд приемного блока управления и тактэв ш вход приемного селектора синхрссигка1530

35

40

45

ла, к второму сигнальному входу которого подключен второй сигнальные e,v. к приемного блока управления и }зьжо,- второго делителя частоты, к сигка 1Ьному входу которого подключен третий

I

выход приемного Ьлока управления, к

третьему входу которого подключа- ;зы- ход третьего делите. йч чястоты, к сигнальному входу которого подкл:-:чен третий выход приемного блока у рарле НИН, другие выходы которого соединзны с соответствующими входами приекг1ого селектора синхросигнала. Ьтогой выход которого соединен с четвертым входом приемного блока управления, четвертый выход приемного блока динамической памяти соединен с третьим входом приемного блока управляемой задержки, к L дополнительным входам которого подключены L дополнительных выходов приемного блока динамической папятп

к ллллллш1Я1гш ллл.лллштшгг л iiuvum juuirum .ллллпллллляг

инф.сигн. Синхоосиенал Иню.сигн Синхярсиенал

0тр. Встойка

Положитель - ная BcmaSKtt

л..

Синхросиенал

.

. Вставка - OmpuLiam. дстов/ а

а .1ЛШ1Г1Ш1. Л1Л1ЛЯШ1ПЛ .Ш1 Ш 1ЛШ1Г1ЛЛЯГ JinJlJTJUlJLrLrmnr

Фае. 2

инф. Синхросиёнал

| Левин Л.С., Плоткин М.А | |||

| Цифровые системы передачи информации | |||

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1988-09-30—Публикация

1986-04-23—Подача