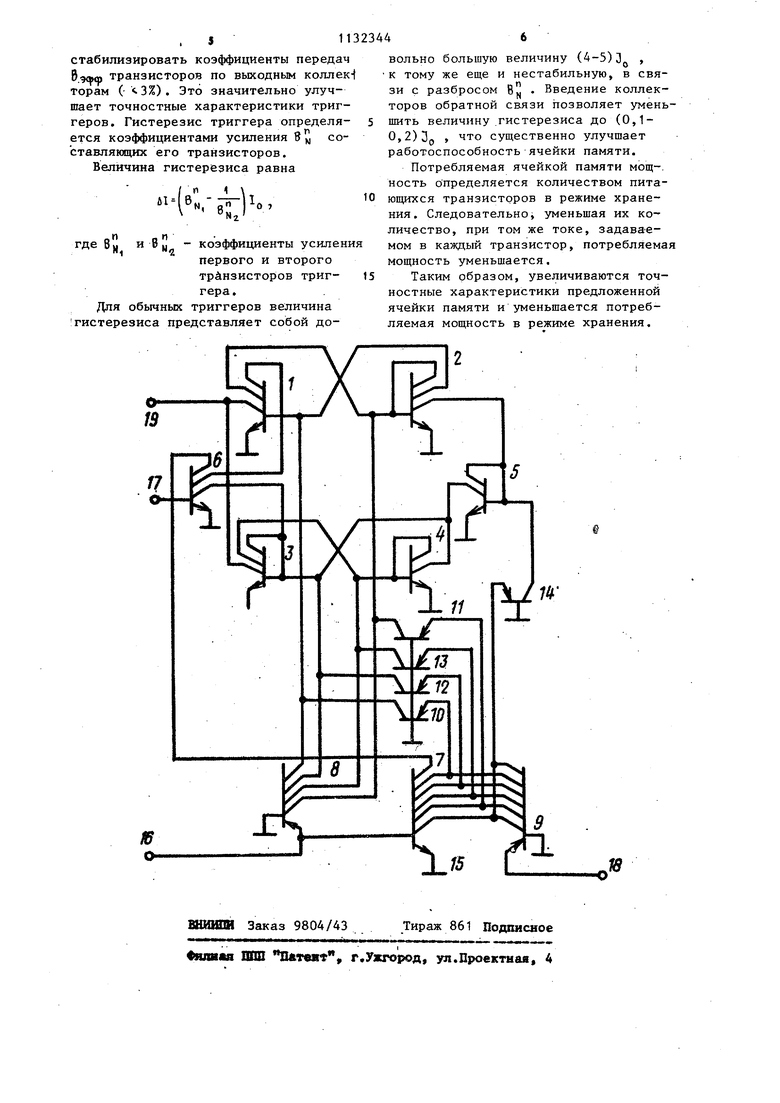

. Изобретение относится к микроэлектронике и предназначено для построения многоуровневых БИС обработки и хранения информации. Известен четырехуровневый D -три гер, содержащий квантизатор, в цепи обратной связи которого стоит токовый повторитель, и схему управления l , Недостатками его является сложность, и большая потребляемая мощность. Наиболее близким к изобретению по технической сущности является ячейка памйти, содержащая три триггера с непосредственными связями, выполненные на шести транзисторах типа п-р-р, блокировочный транзистор типап-р- 1, т око задающий и опорный транзисторы типа р -п-р и шесть транзисторов связи типа р-ч-р эмиттеры транзисторов и блокировочного транзистора, базы токозадающег и опорного транзисторов и базы тран зисторов связи соединены с шиной нулевого потенциала, база блокировочного и эмиттер токозадающего тра зистора - с тактовой шиной, соответ ствующий коллектор блокировочного транзистора - с входной шиной, соот ветствующие коллекторы токозадающег транзистора - с обозами транзисторов, эмиттер опорного транзистора с шиной питания, эмиттеры первого, второго и третьего транзисторов связи - с соответствующими колле- -. кторами блокировочного и опорного транзисторов, коллекторы первого и третьего транзисторов связи - соответственно с базами первого и треть го трайзисторов, коллекторы четвертого, пятого 1 и шестого транзисторов связи - с выходом ячейки. Недостатками этой ячейки памяти являются малая точность преобразова ния, вызванная гистерезисом триггеров - компараторов, и большая потре ляемая мопщость в режиме хранения. Цель изобретения - увеличение то ности преобразования и уменьшение потребляемой мощности в режиме хра ния. Поставленная цель достигается . тем, что в ячейке памяти, содержащ два триггера с непосредственными связями, выполненные на первом и втором, третьем и четвертом транзи торах типап-р-И, пятый, шестой и блокировочный транзистооы типа п-р-п, токозадающий и опорный транзисторы типар-п-р и пять транзисторов связи типа р-п-р, эмиттеры первого, второго,третьего,четвертого,пятого, шестого и блокировочного транзисторов, базы токозадающего и опорного транзисторов и базы транзисторов связи соединены с шиной нулевого потенциала, база блокировочного и эмиттер токозадающего транзисторов - с тактовой шиной, коллектор блокировочного транзистора - с входной шиной, соответсвующие коллекторы токозадающего транзистора - с базами первого, второго, третьего и четвертого транзисторов, эмиттер опорного транзистора с шиной питания, эмиттеры первого, второго и третьего транзисторов связи - с соответствующими коллекторами блокировочного и опорного транзисторов, коллекторы первого и третьего транзисторов связи - соответственно с базами первого и третьего транзисторов, соответствующий коллектор первого, второго, третьего, четвертого, пятого и шестого транзисторов соединен с собственной базой, дополнительные коллекторы первого и третьего транзисторов - с выходной шиной, дополнительный коллектор второго транзистора и коллектор пятого транзистора связи - с базой пятого транзистора, дополнительный коллектор которого - с базой третьего транзистора, эмиттеры четвертого и пятого транзисторов связи - с соответствующими коллекторами опорного.и блокировочного транзисторов, коллекторы второго и четвертого транзисторов связи - с базами второго и четвертого транзисторов,соответствующие дополнительные коллекторы шестого транзистора - с базами первого и третьего транзисторов, а его база - с входной шиной. На чертеже представлена принципиальная схема предложенной ячейки .памяти. Ячейка памяти содержит два триггера с непосредственными связями, выполненные на первом и втором, третьем и четвертом транзисторах 1-4, пятый, шестой и блокировочный транзисторы 5-7 типа п -р-п, токозадающий и опорный транзисторы 8 и 9 и пять транзисторов 10-14 типар -П-р, эмиттеры первого, второго, третьего,, четвертого, пятого и шестого и блокировочного транзисторов 1-7, базы токозадающего и опорного транзисторов 8 и 9 и базы транзисторов связи 10-14 соединены с шиной нулевого потенциала 15, база блокировочного и эмиттер токозадающего транзисторов 7 и 8 - с тактовой шиной 16, коллек тор блокировочного транзистора 7 с входной шиной 17, соответствующие коллекторы токозадающего транзистора 8 - с базами первого, второго, третьего и четвертого транзисторов 1-4, эмиттер опорного транзистора 9 с шиной питания 18, эмиттеры первог второго и третьего транзисторов связи 10 - 12 с соответствующими колле;;торами блокировочного и опорного транзисторов 7 и 9, коллекторы первого и третьего транзисторов свя зи 10 и 12 - соответственно с базам первого и третьего транзисторов 1 и 3, соответствующий коллектор первого, второго, третьего,, четвертого пятого и ше.стого транзисторов 1-6 соединен с собственной базой, дополнительные коллекторы первого и третьего транзисторов 1 и 3 - с выходной шиной 19, дополнительный кол лектор второго транзистора 2 и коллектор пятого транзистора связи 14 с базой пятого транзистора 5, дополнительный коллектор которого - с ба зой третьего транзистора 3,эмиттеры четвертого и пятого транзисторов связи 13 и 14 - с соответствующими коллекторами опорного и блокировочного транзисторов 9 и 7, коллекторы второго и четвертого транзисторов связи 11 и 13 - с базами второго и четвертого транзисторов 2 и 4, дополнительные соответствующие коллек торы шестого транзистора 6 - с база первого и третьего транзисторов 1 и 3, а его база - с входной шиной 1 Тра,нзисторы 9, 11, 13, 12, 10 и 14 являются управляемыми источник ми взвешенных токов, величины которых для транзисторов 1-5 составляют соответственно 1,510,5 2JO,5 и 0,5 уровней тока 0, Для получения стабильного коэффи циента передачи транзисторов 1-5 в них введены коллекторы обратной связи. Соотношением площадей коллек торных областей транзисторов 1-5 обеспечиваются необходимые коэффици .енты передач Bqcpm по каждому выходно му коллектору. Для коллекторов, об- , разующих триггерные связи,,051,1, для коллекторов, соединенных с шиной 19, транзисторов 1 и 3 - 1 и О,5 соответственно, для коллектора транзистора 5 -В,2, для коллекторов транзистора6-B,q,ф 0,5. Работает ячейка памяти следующим образом. Во время т.актового имЬульса транзистор 7 открыт, шунтирует вход ячейки памяти и транзисторы 10-14, а транзистор 8 задает ток в транзисторы 1-4. Это режим хранения. При отсутствии тактового импульса ячейка памяти в режиме записи. Если во входной шине 17 нулевой уровень тока, транзистор 6 закрыт, в транзисторы 1 и 3 задается ток 1,5o ,; и Jjj , т.е. больше, чем в транзисторы 2 и 4 (по 0,5). Триггеры устанавливаются в первое состояние, транзисторы 1 и 3 открыты. При уровне входного токаЗ - З 23о транзистор 6 отводит через каждый коллектор ток, равный половине этого тока, в результате в базу транзистора 3 задается ток меньше, чем в базу транзистора 4, второй триггер переключается. Теперь транзистор 3 выключен, а транзистор 1 включен. При уровне входного тока 22,JS33o ток, задаваемый в базу транзистора 1, меньше П,53д , что приводит к выключению последнего и включению транзистора 2, который отводит ток базы транзистора 5, последний выключается. В резульфате в базу транзистора 3 задается больший ток, равный разнице задаваемого транзистором 10 и отводимого транзистором 6. Величина этого тока больше 0,53. Поэтому транзистор 3 включится. Таким образом, в этом состоянии транзистор 1 выключен, а транзистор 3 включен. При уровне входного тока больше ЗОд транзистор 3 выключается. С приходом тактового импульса транзистор 7 шунтирует входную шину 17 и транзисторы 10-14, а транзистор 8 своим током сохраняет состояние триггеров до прихода следующего тактового импульса. При этом, в зависимости от хранимой информации, с выходной шины 19 транзисторы 1 и 3 отводят О, 1, 2 или 3 уровня тока. Использование коллекторов обратной связи позволяет существенно

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти | 1977 |

|

SU705523A1 |

| Ячейка памяти | 1982 |

|

SU1140165A1 |

| Многоуровневая ячейка памяти | 1980 |

|

SU1067534A1 |

| Т-триггер (его варианты) | 1984 |

|

SU1226615A1 |

| Стробируемый компаратор | 1982 |

|

SU1056445A1 |

| Тактируемый JK-триггер И @ Л-типа | 1987 |

|

SU1422367A1 |

| Ячейка памяти для регистра сдвига | 1979 |

|

SU851495A1 |

| Триггер Шмидта | 1981 |

|

SU1137571A1 |

| Аналоговый перемножитель | 1989 |

|

SU1709353A1 |

| @ К-триггер | 1984 |

|

SU1185578A1 |

ЯЧЕЙКА ПАМЯТИ, содержащая ,два триггера с непосредственными свя-зями, выполненные на первом и втором, . третьем и четвертом транзисторах типап-р-h, пятый, шестой и блокировочный транзисторы типа п -р- п, токозадаюпц1й и опорный транзисторы типа р -п-р и пять транзисторов связи типар-п-р, эмиттеры первого, второго, третьего, четвертого, пятогоj шестого и блокировочного транзисторов, базы токозадающего и опорного транзисторов и базы транзисторов связи соед 1нены с шиной нулевого потенциала, блокировочного .и эмиттер токозадающего транзисторов - с тактовой шиной, соответствую1ций коллектор блокировочного транзистора - с входной шиной, соответствующие коллекторы токозаданицего транзистора - с ба- , зами первого , второго, третьего и четвертого.транзисторов, эмиттер опорного транзистора - с шиной питания, эмиттеры первого, второго и третьего транзисторов связи - с соответствующими коллекторами блокировочного и опорного транзисторов, коллекторы первого и третьегб транзисторов связи - соответственно с базами первого и третьего транзисторов, отличающаяся тем, что, с целью увеличения точности и уменьшения потребляемой мощности, соответствующий коллектор первого, второго, третьего и четвертого, пятого и шестого транзисторов соединен с собственной базой, дополнительные коллекторы первого и третьего транзисторов- соединены с выходной шиной, дополнительный коллектор второго транзистора и коллектор пятого транзистора связи - с базой пятого транзистора,дополнительный коллектор кото:о рого - с базой третьего транзистора,эмит hO 9 4: lib теры четвертого и пятого транзисторов связи - с соответствующими коллекторами опорного и блокировочного транзисторов, коллекторы второго и четвертого транзисторов связи - с базами второго и четвертого тр,анзисторов, соответствующие дополнительные коллекторы шестого транзистора - с базами первого и третьего транзисто ров, а его база - с входной шиной.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Dao Т.Т., Me.Cluskey E.J., Russell L.K | |||

| Multivalued Integrated Injection Loguc - IEEE Transacation on Computers, vol | |||

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| Устройство для избирательного вызова телефонных аппаратов | 1923 |

|

SU1240A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Ячейка памяти | 1977 |

|

SU705523A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-12-30—Публикация

1983-08-26—Подача