Изобретение относится к вычислительной технике, а конкретно к мно- : гопроцессорным вычислительным систе- ;.мам, и предназначено для распределе- ния вычислительной нагрузки между

процессорами в таких системах, i Целью изобретения является расши- рение функциональных возможностей устройства за счет перераспределения I задач с учетом их важности между ра- ботоспособными процессорами после полного отказа одного или нескольких I процессоров,

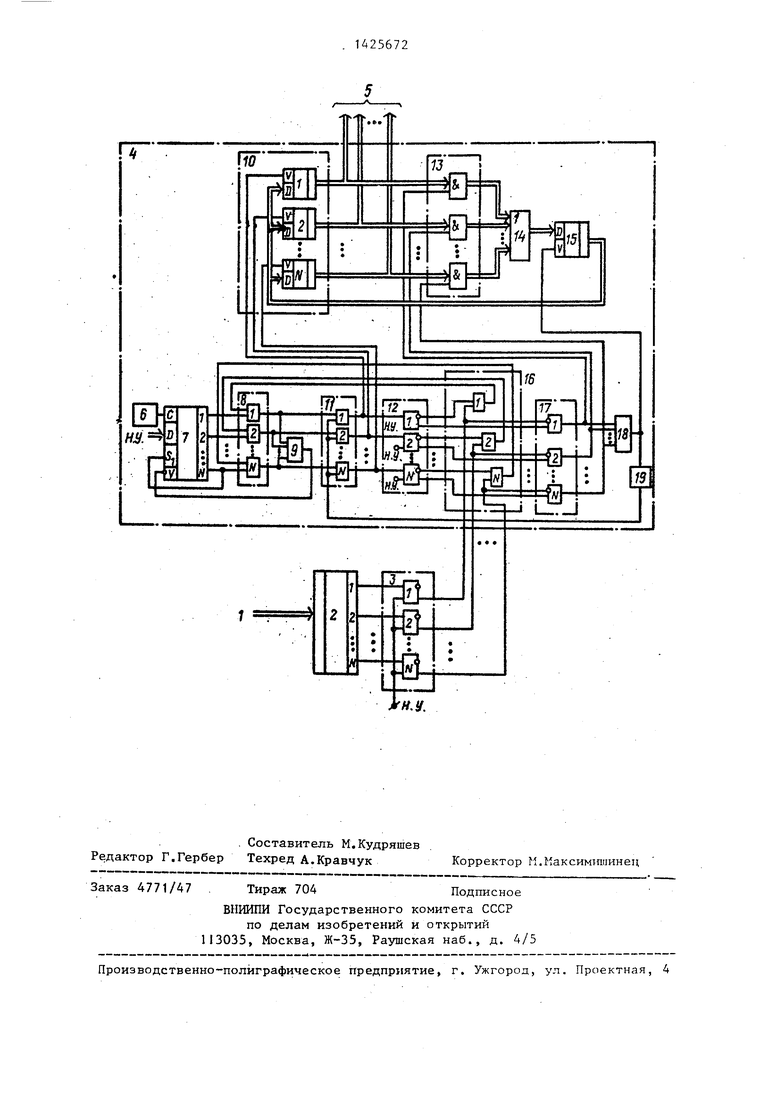

I На чертеже представлена структурная схема устройства.

Устройство содержит группу кодовы входов 1 устройства, дешифратор 2, груыту триггеров 3, блок 4 перебора задач, группу выходов 5 устройства. Блок 4 перебора задач содержит в своем составе генератор 6 импульсов, сдвиго- I вый регистр 7, группу 8 элементов И, I элемент ИЛИ 9, группу 10 регистров, I группу 11 элементов И, группу 12 I триггеров, группу 13 элементов И, блок 14 элементов ИЛИ, регистр 15, I группу 16 элементов И, группу 17 эле :ментов И, элемент ИЛИ 18, элемент 19 I задержки, Все решаемые вычислительной систе i мой задачи разбиты на две группы: основные и неосновные задачи. При отказе процессора решение основной задачи должно обеспечиваться либо ре зервным процессором (если такой имеется) , либо путем передачи основной задачи процессору, решаемому неосновную задачу.

Устройство работает следующим образом,

В регистрах группы 10 регистров блока 4 перебора задач хранятся коды настройки связанных с этими per гистрами процессоров на решение определенных задач, В начальный момент времени (и вплоть до первого отказа в системе) в первом регистре группы 10 регистров хранится код настройки первого процессора, во втором регистре код настройки второго процессора и т„д, в соответствии с первоначальным распределением задач в системе. Если в системе имеются резервные процессоры; то в соответствующих им регистрах группы 10 записывается, например, нулевой код,

В триггерах 3 хранится информация о состоянии процессоров системы, В

5

0

5

0

5

0

5

0

5

начальный момент времени, когда все процессоры системы работоспособны, триггеры группы 3 подачей сигнала с соответствующего входа начальной установки устройства переводятся в единичное состояние,

Процессоры системы периодически осуществляют самодиагностирование; при фиксации отказа каким-либо процессорам на входы 1 устройства поступает код отказавшего процессора. На соответствующем выходе дешифратора 2 появляется логическая единица, перебрасывающая соответствующий триггер 3 в нулевое состояние.

Регистрам группы 10 соответствуют триггеры группы 12, В процессе задания начальных условий триггеры группы 12, соответствующие регистрам группы 10, в которые занесены коды основных задач-, переводятся в единичное состояние; остальные триггеры группы 12 переводятся в нулевое состояние, В дальнейшем триггеры группы 12 могут переходить только из нулевого в еди- ничное состояние. Это обстоятельство отображает тот факт, что в системе возможно только такое перераспределение задач, при котором передача основной задачи возможна только на процессор, ;решающий неосновную задачу, либо на процессор, находящийся в резерве.

На выходе соответствующего элемента И группы 16 поддерживается логическая 1 до.тех пор, пока сохраняет работоспособность соответствующий процессор, решающий неосновную задачу, или находящийся в резерве.

На выходе элемента И группы 17 появляется логическая 1 в том случае, если фиксируется отказ соответствующего процессора, решающего OCHOBHJTO задачу.

При задании начальных условий в один из разрядов кольцевого сдвигового регистра 7 заносится логическая 1, остальные разряды уртанавливаются в нулевое состояние, I

При условии, что на вход разрешения сдвига регистра 7 поступает логический О с выхода элемента ИЛИ 9 с приходом очередного импульса генератора 6 на синхровход регистра 7 в последнем происходит сдвиг логической 1 в следующий разряд. Таким образом, в каждый момент времени логическая 1 присутствует лишь на

одном из выходов сдвигового регистра 7, а на остальных выходах поддерживаются логические О. С выхода регистра 7 логическая 1 поступает- на первый вход элемента И группы 8. В случае, если на второй вход этого элемента И с выхода элемента И групп

16поступает логический О на выход элемента И группы 8 поддерживается логи ческий О, На выходах всех остальных элементов И группы 8 также поддерживаются логические О, так как на их первые входы поступают логические

О с соответствующих выходов регист ра 7. Таким образом, на выходе элемента ИЛИ 9 поддерживается логически О и с приходом очередного импульса генератора 6 логическая 1 из разряда регистра 7 переходит в следующий разряд этого регистра. Описанный процесс происходит до тех пор, пока на выходе одного из элементов И группы 8 не будет сформирована логическая 1, которая через элемент ИЛИ 9 по- ступает на разрешения сдвига регистра 7 и запрещает тем самым дальнейши сдвиг логической 1 в разрядах регистра 7.. При этом на выходе элемента И группы 8 также поддерживается логическая 1, Такая ситуация возможна лишь в случае, когда на выходе элемента И группы 16 поддерживается логическая 1, что свидетельствует о том, что соответствующий процессор сохраняет работоспособность и либо находится в разрезе, либо решает неосновную задачу.

Пусть в системе происходит отказ какого-то процессора, решающего ос- новную задачу. При этом соответствующий триггер группы 3 перебрасывается в нулевое состояние и на выходе соответствующего элементами группы

17появляется логическая 1, кото- рая открывает соответствующий элемент И группы 13. В результате код задачи, хранящийся в соответствующем регистре группы 10, через блок 14 элементов ИЛИ поступает на информа- ционные входы регистра 15. Одновре-менно логическая 1 с выхода элемента И группы 17 через элемент ИЛИ 18 поступает на элемент 19 задержки и вход разрешения записи регистра 15. В регистре 15 фиксируется код основной задачи, решавшейся отказавшим процессором. Через интервал времени определяемый элементом 19 задержки.

логическая 1 с выхода элемента ИЛИ 18 поступает на вторые вхбды элементов И группы 11,

Как отмечалось выше, в группе 8 элементов И логическая 1 поддерживается лишь на выходе одного элемента И и поступает на первый вход соответствующего элемента И группы 11. Следовательно, с приходом логической 1 с выхода элемента 19 задержки логическая 1 появляется на выходе элемента И группы 11. Указанная логическая 1 сбрасывает триггер группы 12 в нулевое состояние и разрешает запись выходного кода регистра 15 в соответствующий регистр группы 10. Таким образом, код основной задачи, хранившийся до отказа процессора в соответствующем регистре группы 10, записывается в другой регистр этой же группы и поступает на выходы группы 5 выходов устройства. В результате соответствующего прот ессору, находившемуся до отказа другого процессора в режиме резерва или решавшему неосновную задачу, передается код основной задачи, которая решалась ранее отказавшим процессором.

Сброс триггера группы 12 в нулево состояние приводит к появлению логического О на выходе элемента И группы 16, в результате чего на выходах элемента И группы 8, а также элемента ИЛИ 9 появляются логические О. С приходом очередного импульса генератора 6 в единичное состояние установлен следующий разряд регистра 7, логическая 1 зафиксируется в этом разряде до следующего отказа одного из процессоров, решающих-основную задачу, если на выходе соответствующего -элемента И группы 16 . поддерживается логическая 1, что имеет место, если соответствующий процессор исправлен и решает неосновную задачу или находится в резерве. В противном случае, как описывалось выше, с приводом каждого очеред кого импульса генератора 6 логическая 1 продвигается в следующий разряд сдвигового регистра 7, пока не происходит совпадение логических 1 на входах одного из элементов И группы 8.

Таким образом, в устройстве фиксируются отказы процессоров и в случае, если отказавший процессор решал основную задачу, устройство передает

код этой задачи исправному процессору, которьш до фиксации отказа в системе либо находился в резерве, либо рещал неосновную задачу.

Формула изобретения

Устройство для распределения задач в многопроцессорной вычислитель- ной системе, содержащее дешифратор, группу триггеров и блок перебора задач, причем группа кодовых входов устройства соединена с группой входов дешифратора, каждый выход кото- рого соединен с входом сброса одноименного триггера группы,блок перебора задач содержит регистр, группу регистров, выходы которых являются группами выходов устройства, о т - личающееся тем, что, с целью расширения функциональных возмож i ностей устройству за счет перераспре деления задач с учетом их важности : между работоспособными прои;ессорами ; после полного отказа одногс или нес- : кольких процессоров, в блок перебо- ра задач введены группа триггеров, первая, вторая, третья, четвертая : группы элементов И, генератор импуль : сов, группа блоков элементов И, пер- : вый и второй элементы ИЛИ, блок элементов ИЛИ, элемент задержки и сдви- : говьй регистр, причем выход генераТо; ра импульсов подключен к синхровходу

;

: СДВИГОВОГО регистря, выходы которого

; подсоединены к первым входам соответ ствующих элементов И первой группы, ; выходы которых соединены с первыми

входами элементов И второй группы и

с входами первого элемента ИЛИ, выходом подключенного к входу разреше- ния сдвига сдвигового регистра, выходы элементов И второй группы подоединены к нулевым входам триггеров группы блока перебора задач и входам азрешения записи соответствуюищх егистров группы, единичные входы триггеров группы, единичные входы триггеров группы блока перебора задач и информационные входы сдвигового регистра соединены с группой входов. начальной установки устройства,вход установки в 1 первого разряда сдвигового регистра соединен с выходом его последнего разряда, нулевые вы- ходы триггеров группы блока перебора задач соединены с первыми входами элементов И третьей группы, вторые входы которых соединены с выходами триггеров группы и с инверсными вхоами элементов И четвертой группы, прямые входы которых соединены с прямыми выходами триггеров группы блока перебора задач, выходы элементов И четвертой группы соединены с входами второго элемента ИЛИ, выход которого соединен с входом разрешения записи регистра и через элемент задержки - с вторыми входами элементов И второй группы, выходы элементов И третьей группы соединены с вторыми входами одноименных элементов И первой группы, группа выходов каждого регистра группы соединена с группой информационных входов одноименного -блока элементов И группы, управляющий вход каждого блока элементов И группы соединен с выходом одноименного элемента И четвертой группы, выходы блоков элементов И группы соединены с входа- ми блока элементов ИЛИ, группа выходов которого соединена с группой информационных входов регистра, группа выходов которого соединена с группами информационных входов регистров группы. ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий между процессорами | 1989 |

|

SU1716514A2 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1989 |

|

RU1819116C |

| УСТРОЙСТВО ДЛЯ ПЕРЕРАСПРЕДЕЛЕНИЯ ЗАДАЧ МЕЖДУ ПРОЦЕССОРАМИ | 1999 |

|

RU2153699C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕРАСПРЕДЕЛЕНИЯ ЗАДАЧ МЕЖДУ ПРОЦЕССОРАМИ | 1991 |

|

RU2023292C1 |

| Устройство для распределения заданий между процессорами | 1987 |

|

SU1474645A1 |

| Устройство для распределения задач между процессорами | 1989 |

|

SU1663611A1 |

| Устройство для распределения задач между процессорами | 1988 |

|

SU1532929A1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1290324A1 |

| Резервированная вычислительная система | 1990 |

|

SU1755400A1 |

Изобретение относится к вычислительной технике, в частности к многопроцессорным вычислительным системам, и предназначено для распределения вычислительной нагрузки между процессорами в таких системах. Цель изобретения - расширение функциональных возможностей устройства за счет перераспределения задач с учетом их важ- , ности между работоспособными процессорами после полного отказа одного или нескольких процессоров. Устройство содержит дешифратор, группу триггеров, блок памяти и блок перебора задач. Блок перебора, задач содержит группу регистров, группу триггеров, пять групп элементов И, генератор импульсов, два элемента ИЛИ, группу элементов ИЛИ, элемент задержки, регистр и кольцевой сдвиговьш регистр. В блоке памяти устройства хранится информация о состоянии процессоров. Сообщение об отказе процессора в виде кода отказавшего процессора поступает на вход устройства.Щ При этом, если отказавший процессор решал основную задачу, то устройство f передает код.этой задачи исправному процессору, который до фиксации отказа либо находился в резерве, либо решал неосновную задачу. 1 ил.

L:

fH.y.

| Криоаппликатор терапевтический | 1974 |

|

SU639538A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения задач между процессорами | 1981 |

|

SU982005A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1987-03-19—Подача