Изобретение относится к вычислительной технике и может найти применение в отказоустойчивых многопроцессорных системах для распределения нагрузки между процессорами.

Цель изобретения - повышение надежности функционирования устройства за счет продолжения распределения заданий при отказе одного или нескольких процессоров вычислительной системы.

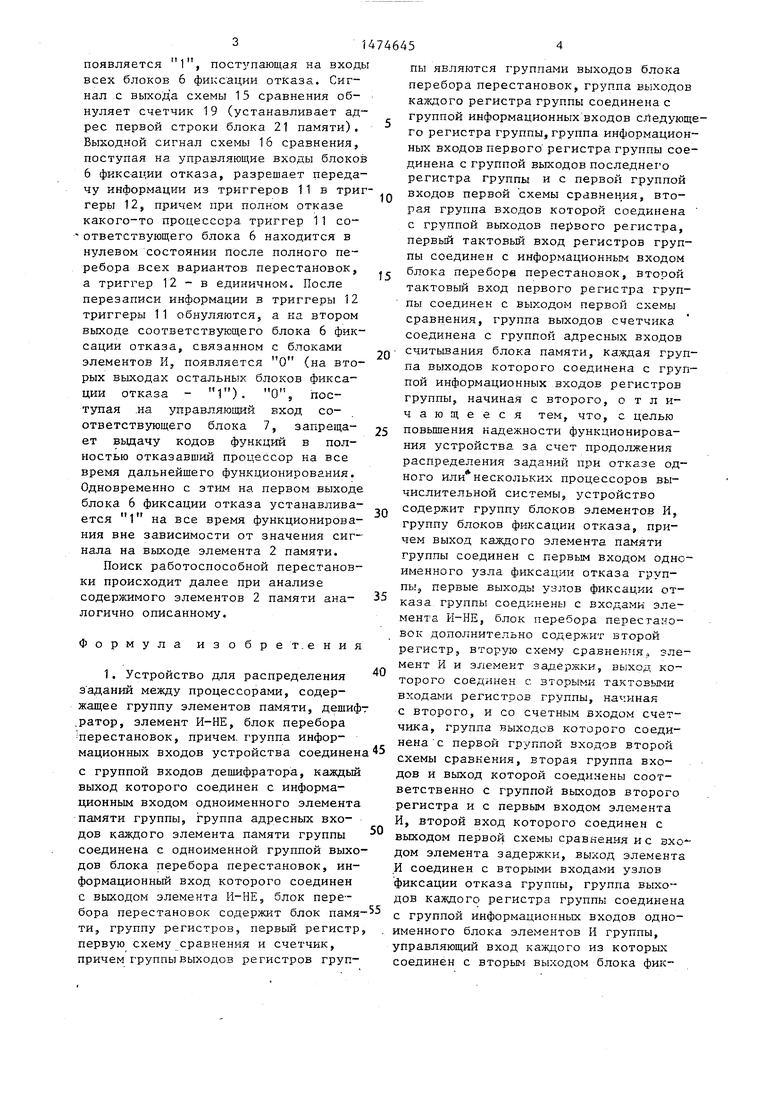

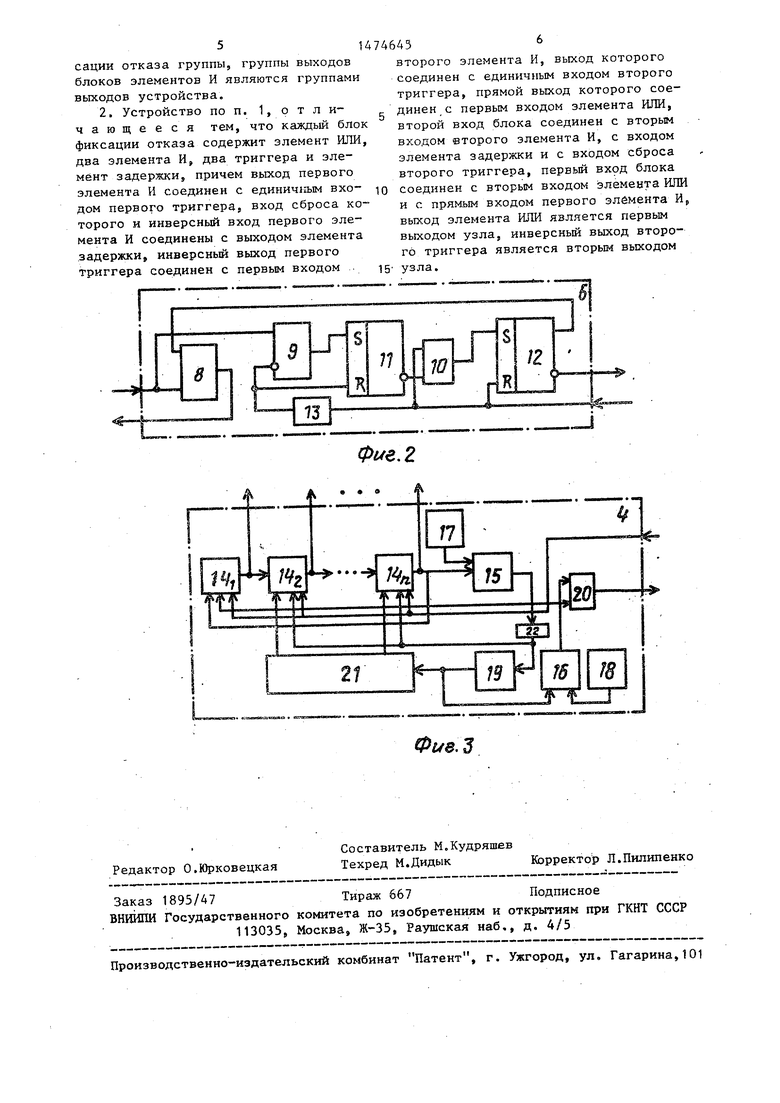

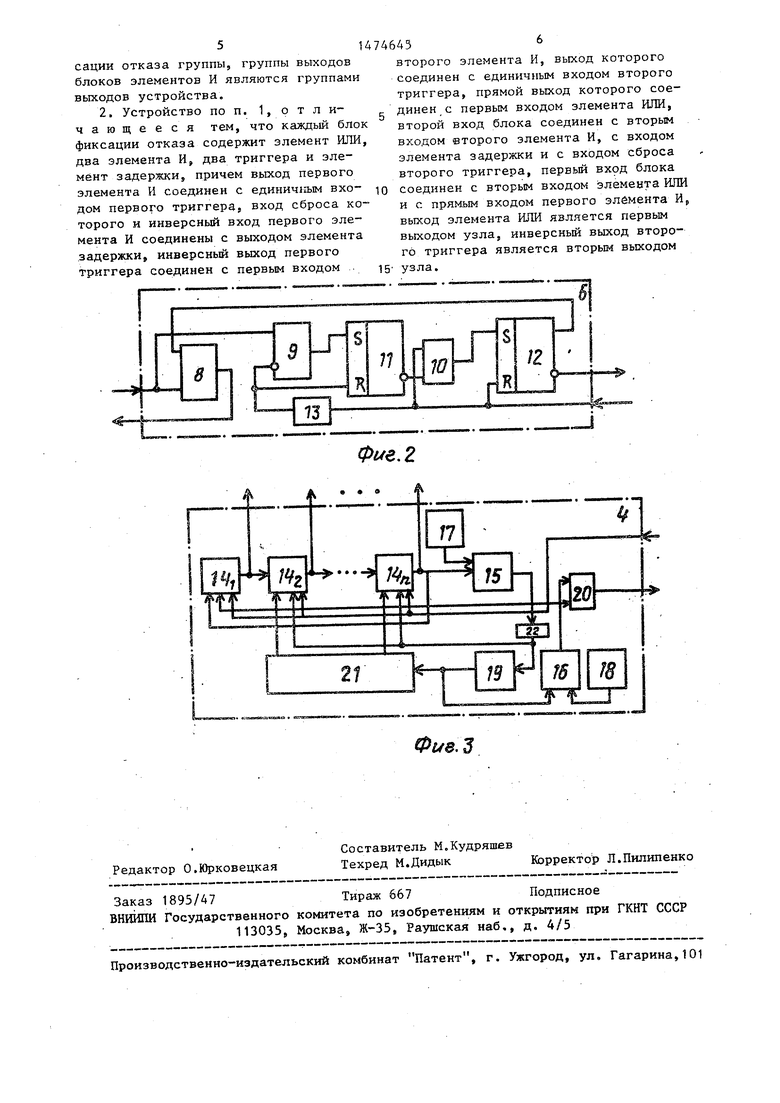

На фиг. 1 приведена структурная схема устройства на фиг 2 - вариант реализации блока фиксации отка- за на фиг. 3 - вариант реализации блока перебора перестановок.

Устройство для распределения заданий между процессорами содержит (фиг. 1) группу 1 элементов 2 памяти, элемент И-НЕ 3, блок 4 перебора перестановок, дешифратор 5Э блоки 6 фиксации отказа, группу блоков 7 элементов И.

Блок фиксации отказа (фиг. 2) содержит элемент ИЛИ 8, элементы И 9 и 109 триггеры 11 и 12 и „элемент 13 задержки.

Блок перебора перестановок (фиг.З) содержит регистры 14, схемы 15 и 16 сравнения, регистры 17 и 18, счетчик 19, элемент И 20s блок 21 памяти и элемент 22 задержки.

Устройство работает следующим образом.

Формирование различных вариантов распределения функций производится блоком 4 перебора перестановок, код функции на соответствующем выходе которого соответствует настройке процессора на выполнение определенной функции Проверка работоспособности распределения функций (перестройки) между процессорами происходит по информации , хранимой в элементах 2 памяти. Б элементы 2 памяти заносится 1, если соответствующий процессор способен выполнять функцию в противном случае - О.

Запись О происходит при потере процессором способности выполнения возложенной на него соответствующей функции. На вход дешифратора 5 подается код отказавшего процессора в конце цикла работы на котором произошел отказ этого процессора. Возбужденным выходом дешифратора 5 осуществляется выборка элемента памяти. Адрес, соответствующий коду потерянной функции,подается с соответствующей группы выходов блока 4 перебора перестановок на выходы адреса элемента 2 памяти.

При этом на выход элемента 2 памяти подается О (содержимое выбранной ячейки в c;rv4ae потери процессоров функции), ч на первом выходе блока фиксации 6 отказа появляется О (в исходном состоянии триггеры.11

и 12 всех блоков фиксации отказа обнулены) . На выходе элемента И-НЕ 3 формируется 1, поступающая на вход блока ц перебора перестановок. Блок 4 перебора перестановок формирует

следующий по порядку вариант распределения функций

ч Если сформированное распределение является работоспособным9 то на выходы всех элементов 2 памяти выдаются

0 1, которые появляются на первых выходах всех блоков 6 фиксации отказа, и на вход блока 4 перебора перестановок с выхода элемента И-НЕ 3 импульс не поступает. Если выбранный вариант распределения функций не является работоспособным, но на выходе элемента И-НЕ 3 вырабатывается 1, поступающая на вход блока 4 перебора перестановок. При этом вырабатывается

0 следующий вариант распределения функций, и т.д.

Для выработки всевозможных перестановок кодов настроек предназначен блок 4 перебора перестановок.

5 В блок 21 памяти построчно заносятся всевозможные перестановки ко- , дов функций, в регистры 14 - коды этих функций, в регистр 17 - код первой функции, в регистр 18 - адрес

0 последней строки блока 21 постоянной памяти.

В регистрах 14,- 140 происходит циклический сдвиг кодов функций. При поступлении в последний регистр 14

5 кода первой функции на выходе схемы 15 сравнения вырабатывается сигнал, по которому происходит изменение адреса строки блока 21 памяти в счетчике 19 и запись в регистры 14 пере0 становки кодов, зафиксированной в данной строке блока 21 памяти. Если после полного перебора всех перестановок кодов функцич работоспособное распределение не найдено, это озна5 чает, что в каком-либо элементе 2 памяти сформировался нулевой код, указывающий на полный отказ по всем функциям какого-то процессора. В эчом случае на выходе схемы 16 сравнения

10

15

31474645

появляется 1, поступающая на входы всех блоков 6 фиксации отказа. Сигнал с выхода схемы 15 сравнения обнуляет счетчик 19 (устанавливает адрес первой строки блока 21 памяти). Выходной сигнал схемы 16 сравнения, поступая на управляющие входы блоков 6 фиксации отказа, разрешает передачу информации из триггеров 11 в триггеры 12, причем при полном отказе какого-то процессора триггер 11 со- ответствующего блока 6 находится в нулевом состоянии после полного перебора всех вариантов перестановок, а триггер 12 - в единичном. После перезаписи информации в триггеры 12 триггеры 11 обнуляются, а на втором выходе соответствующего блока 6 фиксации отказа, связанном с блоками элементов И, появляется О (на вторых выходах остальных блоков фиксации отказа - 1). О, поступая на управляющий вход соответствующего блока 7, запрещает выдачу кодов функций в полностью отказавший процессор на все время дальнейшего функционирования. Одновременно с этим нэ первом выходе блока 6 фиксации отказа устанавливается 1 на все время функционирования вне зависимости от значения сигнала на выходе элемента 2 памяти.

Поиск работоспособной перестановки происходит далее при анализе содержимого элементов 2 памяти аналогично описанному.

20

25

30

35

к г н д в р с п п б т п с со с п п гр ч по ни ра

но чи со гр че гр им пы ка ме во ре ме то вх с чи не сх до ве ре И, вы до И фи до

Формула изобретения

40

1. Устройство для распределения заданий между процессорами, содержащее группу элементов памяти, дешифт ратор, элемент И-НЕ, блок перебора перестановок, причем группа информационных входов устройства соединена 45

с группой входов дешифратора, каждый выход которого соединен с информационным входом одноименного элемента памяти группы, группа адресных входов каждого элемента памяти группы соединена с одноименной группой выходов блока перебора перестановок, информационный вход которого соединен с выходом элемента И-НЕ, блок пере50

ного или нескольких процессоров вычислительной системы, устройство содержит группу блоков элементов И, группу блоков фиксации отказа, причем выход каждого элемента памяти группы соединен с первым входом одноименного узла фиксации отказа группы, первые выходы узлов фиксации отказа группы соединены с входами элемента И-НЕ, блок перебора перестановок дополнительно содержит второй регистр, вторую схему сравненияа элемент Й и элемент задержки, выход которого соединен с вторыми тактовыми входами регистров группы, начиная с второго, и со счетным входом счетчика, группа выходов которого соединена с первой группой входов второй схемы сравнения, вторая группа входов и выход которой соединены соответственно с группой выходов второго регистра и с первым входом элемента И, второй вход которого соединен с выходом первой схемы сравнения и с входом элемента задержки, выход элемента И соединен с вторыми входами узлов фиксации отказа группы, группа выходов каждого регистра группы соединена

бора перестановок содержит блок памя-55 с группой информационных входов одно0

5

0

5

пы являются группами выходов блока перебора перестановок, группа выходов каждого регистра группы соединена с группой информационных входов следующего регистра группы, группа информационных входов первого регистра группы соединена с группой выходов последнего регистра группы и с первой группой входов первой схемы сравнения, вторая группа входов которой соединена с группой выходов первого регистра, первый тактовый вход регистров группы соединен с информационным входом блока перебора перестановок, второй тактовый вход первого регистра группы соединен с выходом первой схемы сравнения, группа выходов счетчика соединена с группой адресных входов считывания блока памяти, каждая группа выходов которого соединена с группой информационных входов регистров группы, начиная с второго, отличающееся тем, что, с целью повышения надежности функционирования устройства за счет продолжения распределения заданий при отказе од

ного или нескольких процессоров вычислительной системы, устройство содержит группу блоков элементов И, группу блоков фиксации отказа, причем выход каждого элемента памяти группы соединен с первым входом одноименного узла фиксации отказа группы, первые выходы узлов фиксации отказа группы соединены с входами элемента И-НЕ, блок перебора перестановок дополнительно содержит второй регистр, вторую схему сравненияа элемент Й и элемент задержки, выход которого соединен с вторыми тактовыми входами регистров группы, начиная с второго, и со счетным входом счетчика, группа выходов которого соединена с первой группой входов второй схемы сравнения, вторая группа входов и выход которой соединены соответственно с группой выходов второго регистра и с первым входом элемента И, второй вход которого соединен с выходом первой схемы сравнения и с входом элемента задержки, выход элемента И соединен с вторыми входами узлов фиксации отказа группы, группа выходов каждого регистра группы соединена

с группой информационных входов одно

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий между процессорами | 1989 |

|

SU1716514A2 |

| Устройство для распределения задач между процессорами | 1981 |

|

SU982005A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕРАСПРЕДЕЛЕНИЯ ЗАДАЧ МЕЖДУ ПРОЦЕССОРАМИ | 1991 |

|

RU2023292C1 |

| Устройство для распределения задач в многопроцессорной вычислительной системе | 1987 |

|

SU1425672A1 |

| Устройство для контроля параллельной вычислительной системы | 1987 |

|

SU1451697A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕРАСПРЕДЕЛЕНИЯ ЗАДАЧ МЕЖДУ ПРОЦЕССОРАМИ | 1999 |

|

RU2153699C1 |

| Устройство для распределения заданий в неоднородной вычислительной среде | 1990 |

|

SU1725220A1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных гиперкубических циклических системах | 2019 |

|

RU2718166C1 |

| Устройство поиска нижней оценки размещения в гибридных многопроцессорных системах при направленной передаче информации | 2021 |

|

RU2769967C1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

Изобретение относится к вычислительной технике и может быть использовано в отказоустойчивых многопроцессорных системах с постепенной деградацией для распределения нагрузки между процессорами. Цель изобретения- повышение надежности функционирования устройства за счет продолжения распределения заданий при отказе одного или нескольких процессоров вычислительной системы. Устройство содержит группу элементов памяти 2, элемент И-НЕ 3, блок 4 перебора перестановок, дешифратор 5, блоки фиксации отказа 6, группу блоков элементов И 7. Устройство сохраняет работоспособность при полном отказе по всем функциям какого-либо процессора /процессоров/ и может продолжать функционирование при наличии в системе одного процессора, способного выполнять хотя бы единственную функцию.1 з.п. ф-лы, 3 ил.

тиэ группу регистров, первый регистр, первую схему сравнения и счетчик, причем группы выходов регистров групименного блока элементов И группы, управляющий вход каждого из которых соединен с вторым выходом блока фикГ

41

8 1

Фне.2

Фив.Ъ

| Устройство для распределения заданий процессорам | 1977 |

|

SU629538A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения задач между процессорами | 1981 |

|

SU982005A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-23—Публикация

1987-07-06—Подача