i4

to

СЛ

00

tc

00

1

Изобретение относится к области автоматики и вычислительной техники и может использоваться для преобразования быстроизменяющихся аналоговых сигналов в цифровой код.

Цель изобретения - повьпиение точности преобразования.

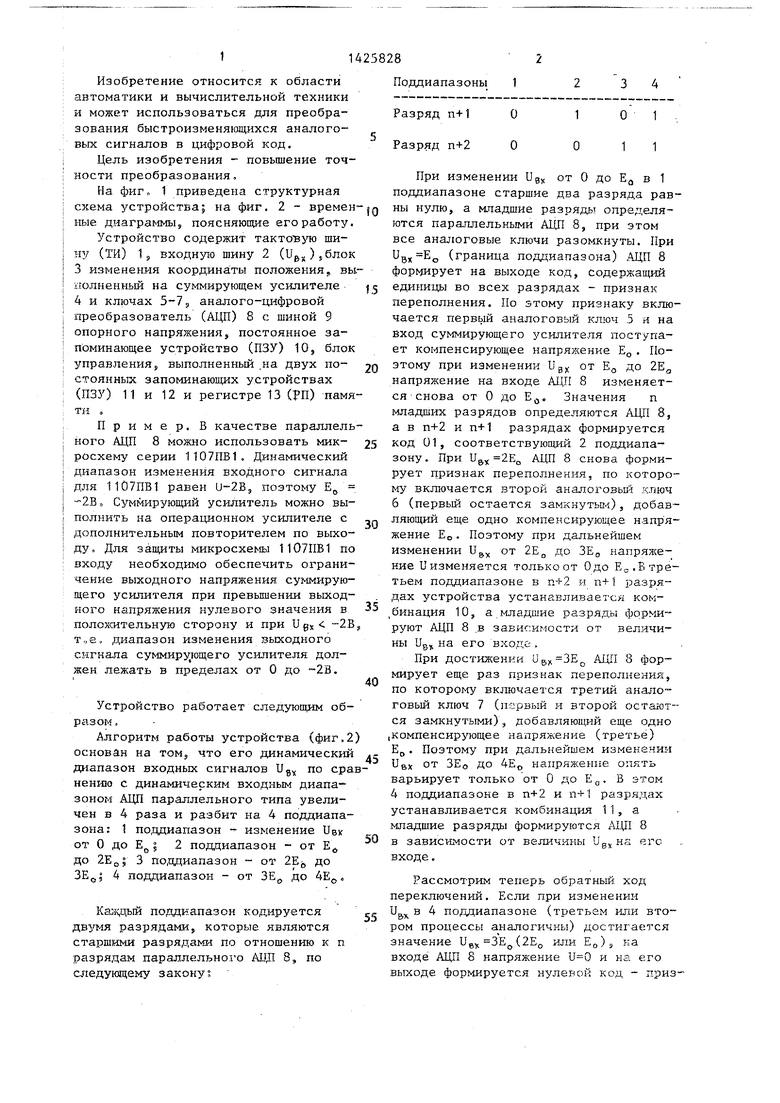

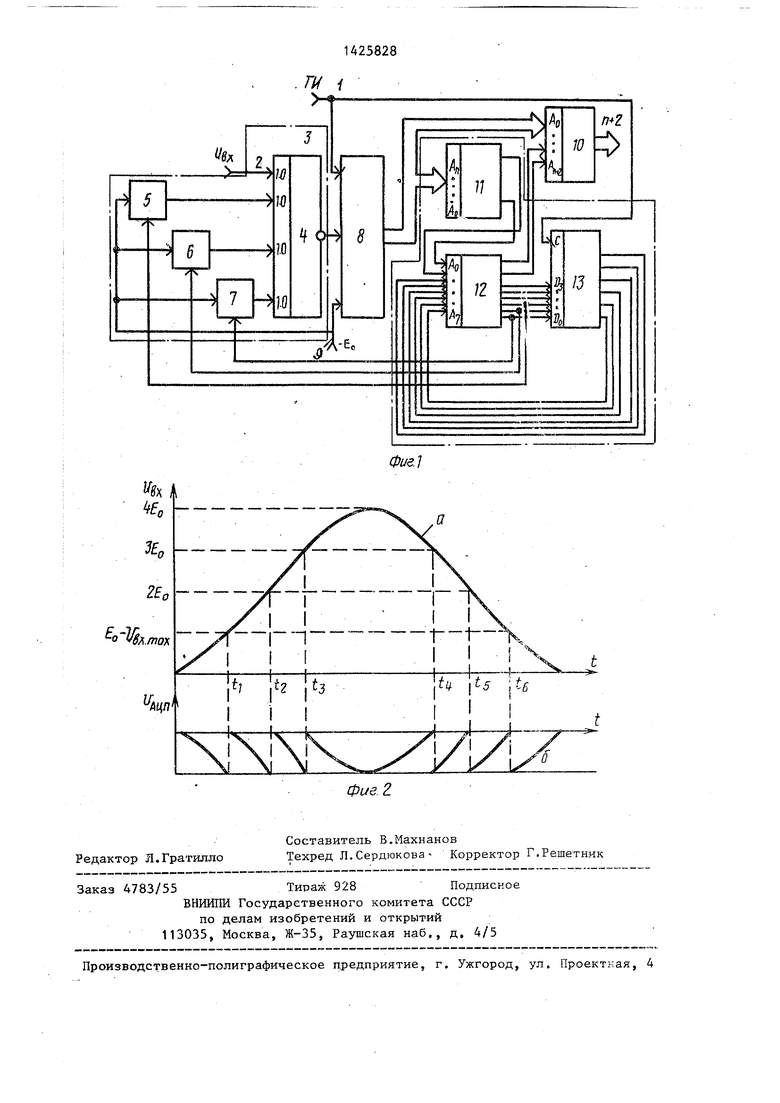

На фиг 1 приведена структурная схема устройства; на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство содержит тактовую ши- нз/ (ТИ) Is входную шину 2 (Ug., ) 5,блок

3изменения координа ты положения., вы хюлненный на суммирующем усилителе

4и ключах 5-7, аналого-цифровой преобразователь () 8 с шиной 9 опорного напряжения, постоянное запоминающее устройство (ПЗУ) 10, блок управления, выполненный .на двух постоянных запоминающих устройствах (ПЗУ) 11 и 12 и регистре 13 (РП) памяти .

Пример. Б качестве параллельного .АЦП 8 можно использовать микросхему серии 1107ПВ1, Динамический диапазон изменения входного сигнала для 1107ПВ1 равен U-2B5 поэтому Е , Суммирующий усилитель можно выполнить на операционном усилителе с дополнительным повторителем по выходу. Для защиты микросхемы 1107ПВ1 по входу необходимо обеспечить ограничение выходного напряжения суммирующего усилителя при превышении выходного напряжения нулевого значения в полохсительную сторону и при Ugx -23 т„е, диапазон изменения выходного сигнала суммиру ощего усилителя должен лежать в пределах от О до -2В.

Устройство работает следующим образом.

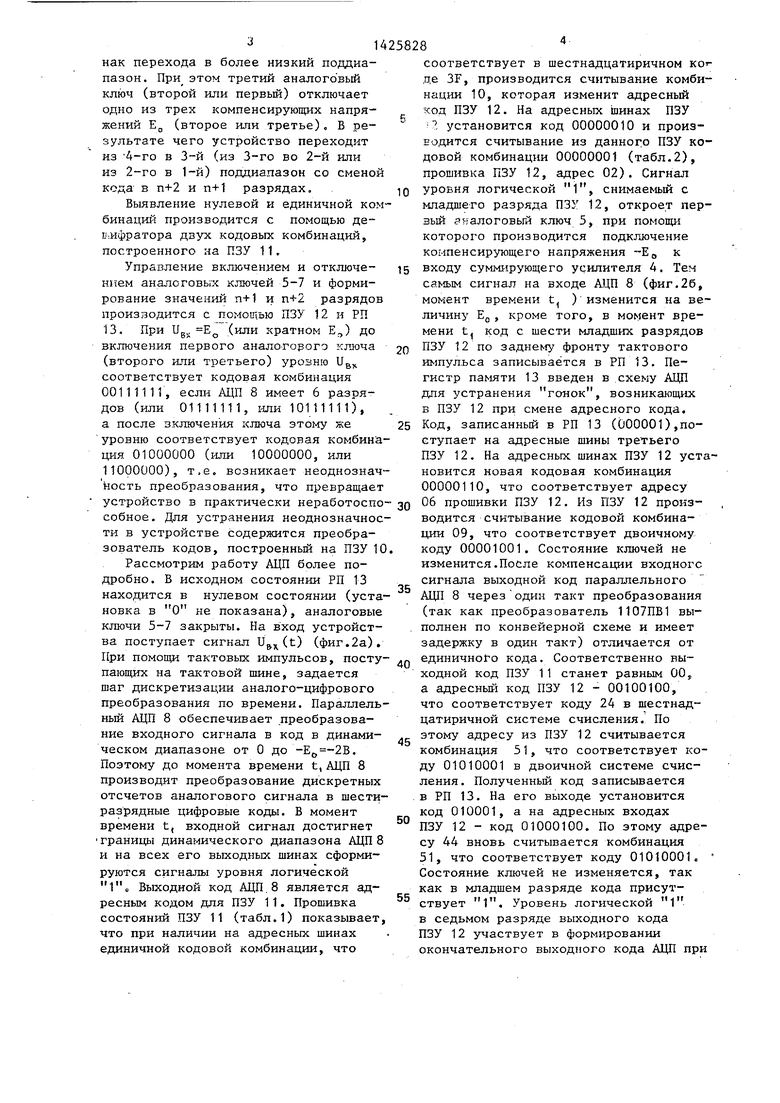

Алгоритм работы устройства (фиг.2 основан на том, что его динамический диапазон входных сигналов Ug по сранению с динамическим входным диапазоном АЦП параллельного типа увеличен в 4 раза и разбит на 4 поддиапазона: 1 по,цдиапазон - изменение UBK от О до Ед 5 2 поддиапазон - от Е до 2Ео; 3 по,цдиапазон от 2Ej, до 4 поддиапазон - от ЗЕ, до 4Ej.

Казкдьш поддиапазон кодируется двз мя разрядами, которые являются старшими разрядами по отношению к разрядам параллельного АИД 8, по следующему закону;

.5

0

При изменении Ug от О до Е в 1 поддиапазоне старшие два разряда равны нулю, а младшие разрядь определяются параллельными АЦП 8, при этом все аналоговые ключи разомкнуты. При , (граница поддиапазона) АЦП 8 формирует на выходе код, содержащий единицы во всех разрядах - признак переполнения. По этому признаку включается первьш аналоговый ключ 5 и на вход суммирующего усилителя поступает компенсирующее напрял ение Е . Поэтому при изменении Ug от E до 2Е,,, напряжение на входе АЦП 8 изменяется снова от О до Е.

Значения

5

0

г 0

5

5

младших разрядов определяются АЦП 8, а в п+2 и п+1 разрядах формируется код 01, соответствующий 2 поддиапазону . При и 2Ео АЦП 8 снова формирует цризнак переполнения, по которому включается второй аналоговый ключ б (первый остается замкнутьп-:), добавляющий еще одно компенсирующее напр я- жение ЕО. Поэтому при дальнейшем изменении К от 2E до ЗЕд напрялсе- ние и изменяется только от О до Е,,.В третьем поддиапазоне в п+2 и п+1 разрядах устройства устанавливаетск ком- бинация 10, а младшие разряды формируют АЦП 8 .в зависимости от величины Ugj на его входе.

При достижении Up,3E АЦП 8 формирует еще раз признак переполнения, по которому включается третий аналоговый ключ 7 (первый и второй остаются замкнутыми), добавляющий еще одно (Компенсирующее напряжение (третье) ЕО. Поэтому при дальнейшем изменении UBX от ЗЕо до 4Ео напряжение опять варьирует только от О до Е„. В этом 4 поддиапазоне в п+2 и п+1 разрядах устанавливается комбинация 11, а .младшие разряды формируются AIJJI 8 в зависимости от величины Ug на его входе.

Рассмотрим теперь обратный ход переключений. Если при изменении

и,,„ в 4 поддиапазоне (третьем или втором процессы аналогичны) достигается значение Ug ЗЕ (2Е(, или ЕО) ка входе АЦП 8 напряжение и на его выходе формируется нулевой код - приз

14

нак перехода в более низкий поддиапазон. При этом третий аналоговый ключ (второй или первьй) отключает одно из трех компенсирующих напряжений ЕО (второе или третье), В результате чего устройство переходит из 4-го в 3-й (из 3-го во 2-й или из 2-го в 1-й) поддиапазон со сменой кода в п+2 и п+1 разрядах.

Выявление нулевой и единичной комбинаций производится с помощью де- и,ифратора двух кодовых комбинаций, построенного на ПЗУ 11,

Управление включением и отключением аналоговьи ключей 5-7 и формирование значений п+1 и п+2 разрядов производится с помощью ПЗУ 12 и РП 13, При Ug,, Ед (или кратном Е,,) до включения первого аналогорогэ ключа (второго или третьего) уровню U соответствует кодовая комбинация 00111111, если АЦП 8 имеет 6 разрядов (или 01111111, или 10111111), а после включения ключа этому же уровню соответствует кодовая комбинация 01000000 (или 10000000, или 11000000), т.е. возникает неоднознач- hocTb преобразования, что превращает

4

0

соответствует в шестнадцатиричном де 3F, производится считывание комбинации 10, которая изменит адресный ход ПЗУ 12, На адресных шинах ПЗУ 2 установится код 00000010 и производится считывание из данного ПЗУ кодовой комбинации 00000001 (табл,2), прошивка ПЗУ 12, адрес 02), Сигнал уровня логической 1, снимаемый с младшего разряда ПЗУ 12, откроет первый аналоговый ключ 5, при помощи которого производится подключение компенсирующего напряжения -Eg к

5 входу суммирующего усилителя 4, Тем самым сигнал на входе А.ЦП 8 (фиг,26, момент времени t, ) изменится на величину ЕО, кроме того, в момент времени t( код с шести младших разрядов

0 ПЗУ 12 по заднему фронту тактового импульса записывается в РП 13, Пе- гистр памяти 13 введен в схему АЦП для устранения гонок, возникаю цих в ПЗУ 12 при смене адресного кода.

5 Код, записанный в РП 13 (000001),поступает на адресные шины третьего ПЗУ 12, На адресных шинах ПЗУ 12 установится новая кодовая комбинация 00000110, что соответствует адресу

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для аналого-цифрового преобразования | 1988 |

|

SU1608796A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1996 |

|

RU2114501C1 |

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2311731C1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1522400A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Способ многоканального широтно-импульсного преобразования аналогового сигнала и устройство для его осуществления | 1990 |

|

SU1818688A1 |

| Устройство для управления преобразователем частоты с непосредственной связью и широтно-импульсным регулированием | 1989 |

|

SU1624629A1 |

| СПОСОБ ИЗМЕРЕНИЯ УГЛА ПОВОРОТА ВАЛА | 1995 |

|

RU2108664C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для преобразования быстроизменяющихся аналоговых сигналов в цифровой код. Изобретение позволяет повысить точность преобразования параллельных АЦП, в KOTOpbix с помощью суммирующего усилителя j ключей, трех постоянных запоминающих устройств и регистра памяти производится адаптивный выбор диапазона преобразования. 2 is.п. ф-лы, 2 ил 4 табл. .

устройство в практически неработоспо- зо прошивки ПЗУ 12, Из ПЗУ 12 произ- собное. Для устранения неоднозначное- водится считывание кодовой комбинации 09, что соответствует двоичному коду 00001001. Состояние ключей не изменится,После компенсации входного сигнала выходной код параллельного

ти в устройстве содержится преобразователь кодов, построенный на ПЗУ 10.

Рассмотрим работу АЦП более подробно, В исходном состоянии РП 13

35

находится в нулевом состоянии (установка в О не показана), аналоговые

АЦП 8 через один такт преобразования (так как преобразователь 1107ПВ1 выполнен по конвейерной схеме и имеет задержку в один такт) отличается от

45

ключи 5-7 закрыты. На вход устройства поступает сигнал U(t) (фиг.2а). При помощи тактовых импульсов, посту- ,,, единичного кода. Соответственно вы- пающих на та1 ;товой шине, задается ходной код ПЗУ 11 станет равным 00,

а адресньш код ПЗУ 12 - 00100100, что соответствует коду 24 в шестнадцатиричной системе счисления. По этому адресу из ПЗУ 12 считывается комбинация 51, что соответствует коду 01010001 в двоичной системе счисления. Полученный код записывается в РП 13, На его выходе установится код 010001, а на адресных входах ПЗУ 12 - код 01000100. По этому адре- границы динамического диапазона АЦП 8 и на всех его выходных шинах сформируются сигналы уровня логической 1,, Выходной код АЦП. 8 является адресным кодом для ПЗУ 11. Прошивка состояний ПЗУ 11 (табл,1) показывает, что при наличии на адресных шинах единичной кодовой комбинации, что

шаг дискретизации аналого-цифрового преобразования по времени. Параллельный АЦП 8 обеспечивает преобразование входного сигнала в код в динамическом диапазоне от О до -Ej,-2B, Поэтому до момента времени t, АЦП 8 производит преобразование дискретных отсчетов аналогового сигнала в шестиразрядные цифровые коды, В момент времени t, входной сигнал достигнет

50

су 44 вновь считывается комбинация 51, что соответствует коду 01010001. Состояние ключей не изменяется, так

55

как в младшем разряде кода присут- Уровень логической 1

ствует 1 в седьмом разряде выходного кода ПЗУ 12 участвует в формировании окончательного выходного кода АЦП при

прошивки ПЗУ 12, Из ПЗУ 12 произ- водится считывание кодовой комбинации 09, что соответствует двоичному коду 00001001. Состояние ключей не изменится,После компенсации входного сигнала выходной код параллельного

АЦП 8 через один такт преобразования (так как преобразователь 1107ПВ1 выполнен по конвейерной схеме и имеет задержку в один такт) отличается от

единичного кода. Соответственно вы- ходной код ПЗУ 11 станет равным 00,

45

50

а адресньш код ПЗУ 12 - 00100100, что соответствует коду 24 в шестнадцатиричной системе счисления. По этому адресу из ПЗУ 12 считывается комбинация 51, что соответствует коду 01010001 в двоичной системе счисления. Полученный код записывается в РП 13, На его выходе установится код 010001, а на адресных входах ПЗУ 12 - код 01000100. По этому адре-

су 44 вновь считывается комбинация 51, что соответствует коду 01010001. Состояние ключей не изменяется, так

а адресньш код ПЗУ 12 - 00100100, что соответствует коду 24 в шестнадцатиричной системе счисления. По этому адресу из ПЗУ 12 считывается комбинация 51, что соответствует коду 01010001 в двоичной системе счисления. Полученный код записывается в РП 13, На его выходе установится код 010001, а на адресных входах ПЗУ 12 - код 01000100. По этому адре-

5

как в младшем разряде кода присут- Уровень логической 1

ствует 1 в седьмом разряде выходного кода ПЗУ 12 участвует в формировании окончательного выходного кода АЦП при

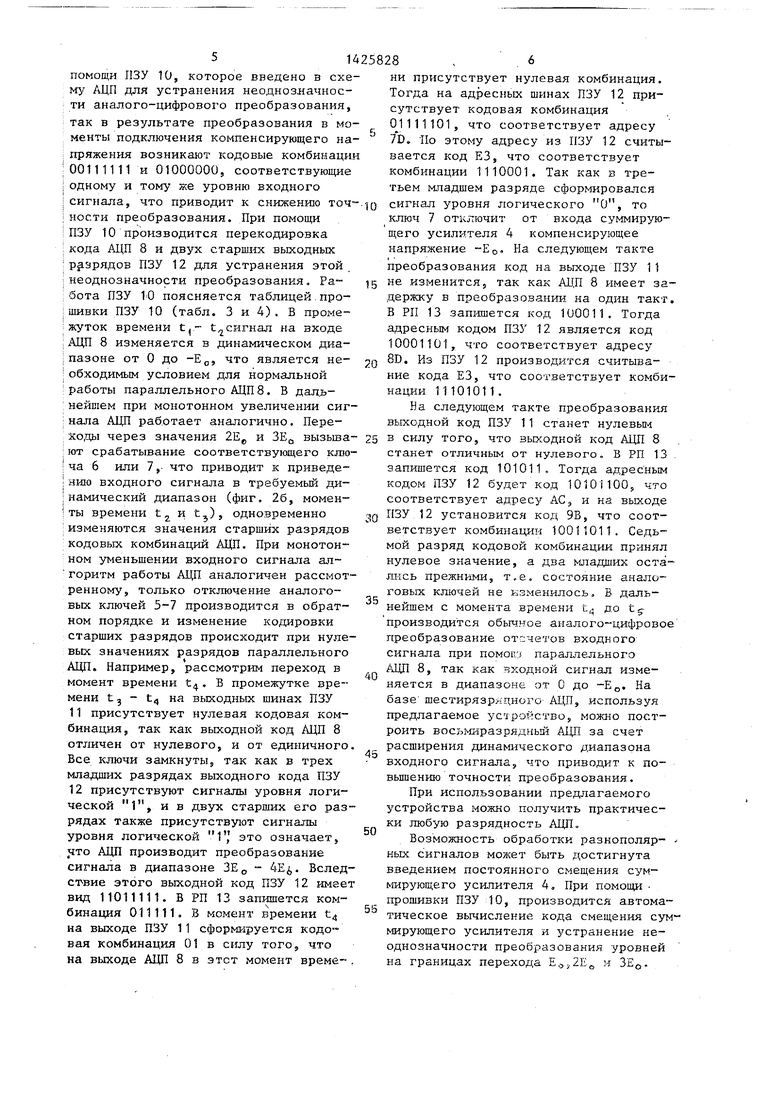

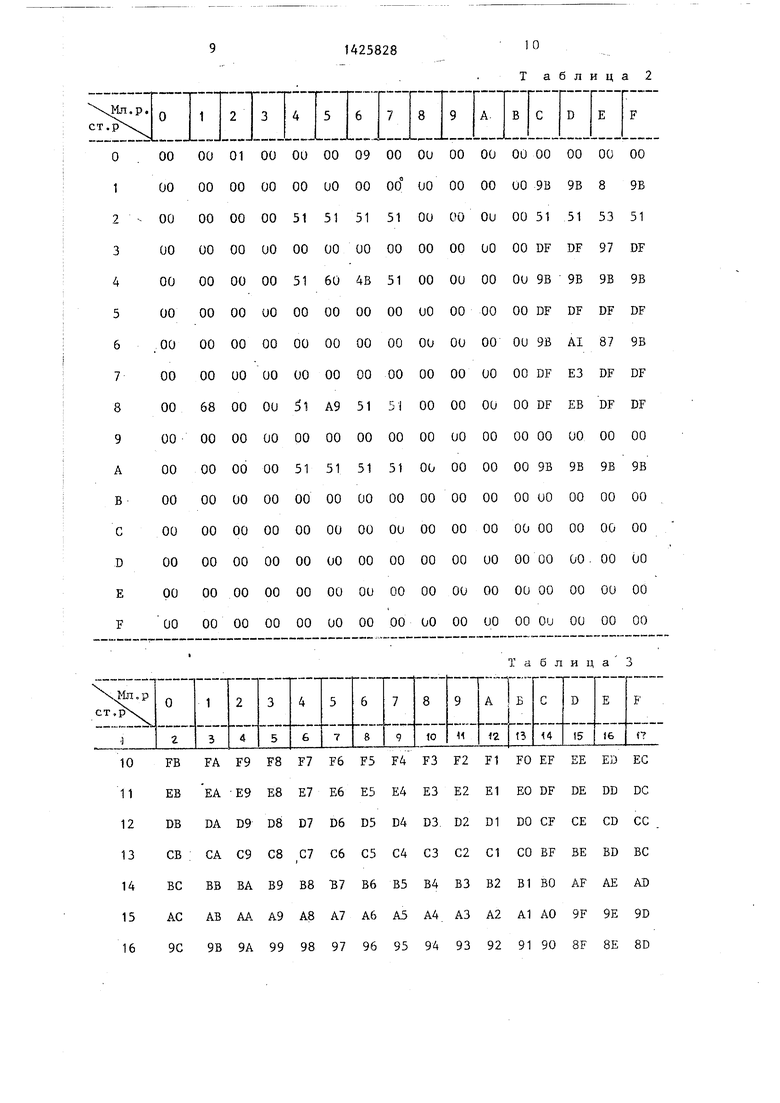

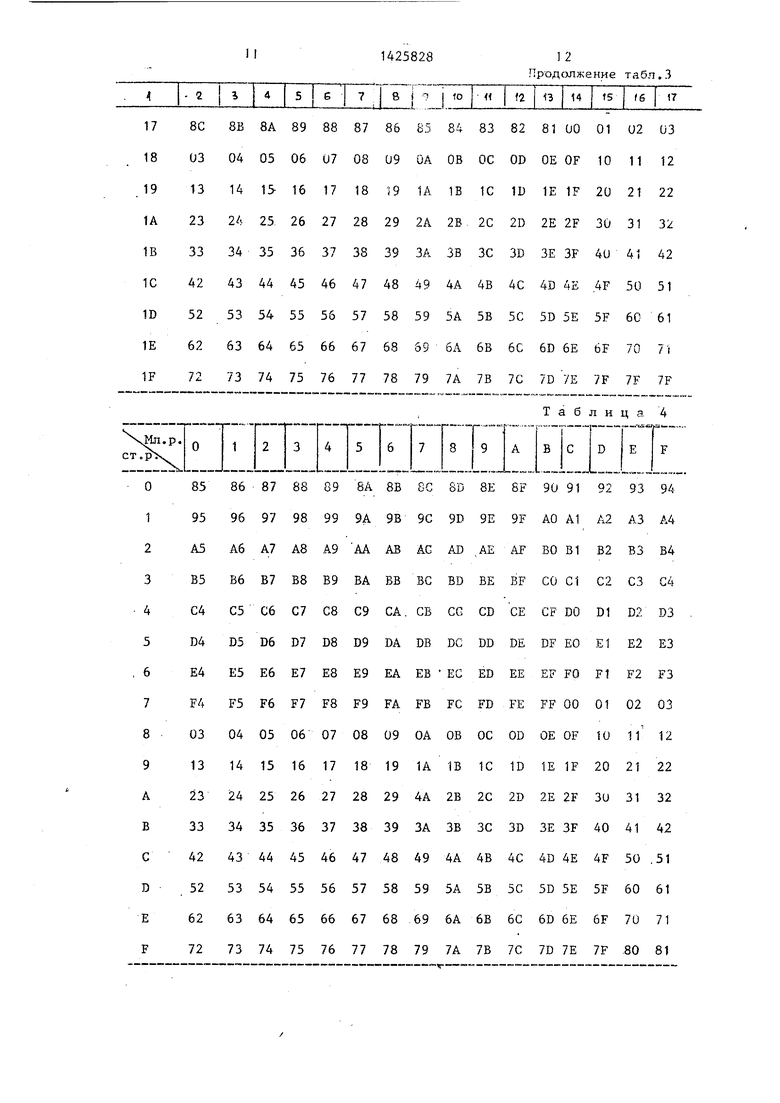

помощи ПЗУ 10, которое введено в схему АЦП для устранения неоднозначности аналого-цифрового преобразования, так в результате преобразования в моменты подключения компенсирующего на- гфяжения возникают кодовые комбинации 00111111 и 01000000, соответствующие одному и тому же уровню входного j сигнала, что приводит к снижению точ- нести преобразования. При помощи ;ПЗУ 10 производится перекодировка ;кода А1Щ 8 и двух старших выходных :разрядов ПЗУ 12 для устранения этой неоднозначности преобразования, Ра- бота ПЗУ 10 поясняется таблицей.про- iшивки ПЗУ 10 (табл, 3 и 4). В проме- : жуток времени t,. t cигнaл на входе ;АЦП 8 изменяется в динамическом диа- пазоне от О до -Е, что является не- I обходимым условием для нормальной работы параллельного АЦП8. В дал.ь- :нейшем при монотонном увеличении сиг- нала АЦП работает аналогично. Пере

Зсо,цы через значения 2Ер и ЗЕд вызьша- 25 в силу того, что выходной код АЦП 8

:ЮТ срабатывание соответствующего клю- i ча 6 или 7,- что приводит к приведе- ниш входного сигнала в требуемый ди- i на1 ический диапазон (фиг. 26, момен- ты времени t и t), одновременно изменяются значения старших разрядов кодовых комбинаций АЦП. При монотонном уменьшении входного сигнала ал горитм работы АЦП аналогичен рассмотренному, только отключение аналоговых ключей 5-7 производится в обратном порядке и изменение кодировки старших разрядов происходит при нулевых значениях разрядов параллельного АЦП, Например, рассмотрим переход в момент времени t. Б промежутке времени 15 - t на выходных шинах ПЗУ

11присутствует нулевая кодовая комбинация, так как выходной код АЦП 8 отличен от нулевого, и от единичного. Все ключи замкнуты, так как в трех младших разрядах выходного кода ПЗУ

12присутствуют сигналы уровня логической 1, и в двух старших его разрядах также присутствуют сигна/ш уровня логической 1 это означает, что АЦП производит преобразование сигнала в диапазоне ЗЕ - 4Е. Вслед- сгвие этого выходной код ПЗУ 12 имеет вид 11011111. В РП 13 запишется комбинация 011111. В момент времени t на выходе ПЗУ 11 cфop шpyeтcя кодовая комбинация 01 в силу того, что

на выходе АЦП В в этот момент време- .

ни присутствует нулевая комбинация. Тогда на адресных шинах ПЗУ 12 присутствует кодовая комбинация 01111101, что соответствует адресу 7D, По этому адресу из ПЗУ 12 считывается код ЕЗ, что соответствует комбинации 1110001. Так как в третьем младшем разряде сформировался Q сигнал уровня логического О, то

ключ 7 отключит от входа суммирую- щего усилителя 4 компенсирующее напряжение -Ео« На следующем такте преобразования код на выходе ПЗУ 11

5 не изменится, так как AU,n 8 имеет задержку в преобразовании на один такт. В РП 13 запишется код 100011. Тогда адресным кодом ПЗЗ 12 является код 10001101, что соответствует адресу

Q 8D. Из ПЗУ 12 производится считывание кода ЕЗ, что соответствует комбинации 11101011.

На следующем такте преобразования выходной код ПЗУ 11 станет нулевьп

0

5

0

станет отличным от нулевого, В РП 13 . запишется код 101011. Тогда адресным кодом ПЗУ 12 будет код 10101100, что соответствует адресу АС, и на выходе ПЗУ 12 установится код 9В, что соответствует комбинации 10011011, Седьмой разряд кодовой комбинации принял нулевое значение, а два младших оста- л1-1сь прежними, т.е. состояние аналоговых ключей не изменилось. В дальнейшем с момента времени t до tg- производится обычное аналого-цифровое преобразование отсчетов входного сигнала при помогл параллельного /ЛДТ 8, так как входной сигнал изменяется в диапазоне от О до -Е,

На

базе шестирязрядного АЦП, используя предлагаемое устройство, можно построить восьмиразрядный АЩ за счет расширения динамического диапазона входного сигнала, что приводит к по- вьшению точности преобразования.

При использовании предлагаемого устройства можно получить практически любую разрядность АЦП,

Возможность обработки разнополяр- - ных сигналов может быть достигнута введением постоянного смещения сум- шpyющeгo усилителя 4, При помощи прошивки ПЗУ 10, производится автоматическое вычисление кода смещения суммирующего усилителя и з странение неоднозначности преобразования уровней на границах перехода Е,э;2Е„ и ЗЕд.

Формула изобретения

inillEI

№i.p

ст.р

0001

1 000000

о 000000 0 000000. 0000000

5

0

5

0

венно с первым, вторым и третьим входами сумьшрующего усилителя, чет- i-ертый вход которого является инфор- , ацконным входом блока, группой уп- р ; ;ля;о11Г1 1х входов которого являются управляющие входы соответственно первого, второго и третьего ключей, информационные входы которых объединены и являются опорньЕ 1 входом блока, а его выходом является выход суммирующего усилителя,

а б л и ц а 1

Т аблица 2

а

| Микропроцессорные средства и системы, 1985, № 1, с.75-77, рис,1 | |||

| Коломиец О.М | |||

| и др | |||

| Автоматический выбор диапазона измерений в цифровых приборах, 1980, с. | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1988-09-23—Публикация

1987-03-06—Подача