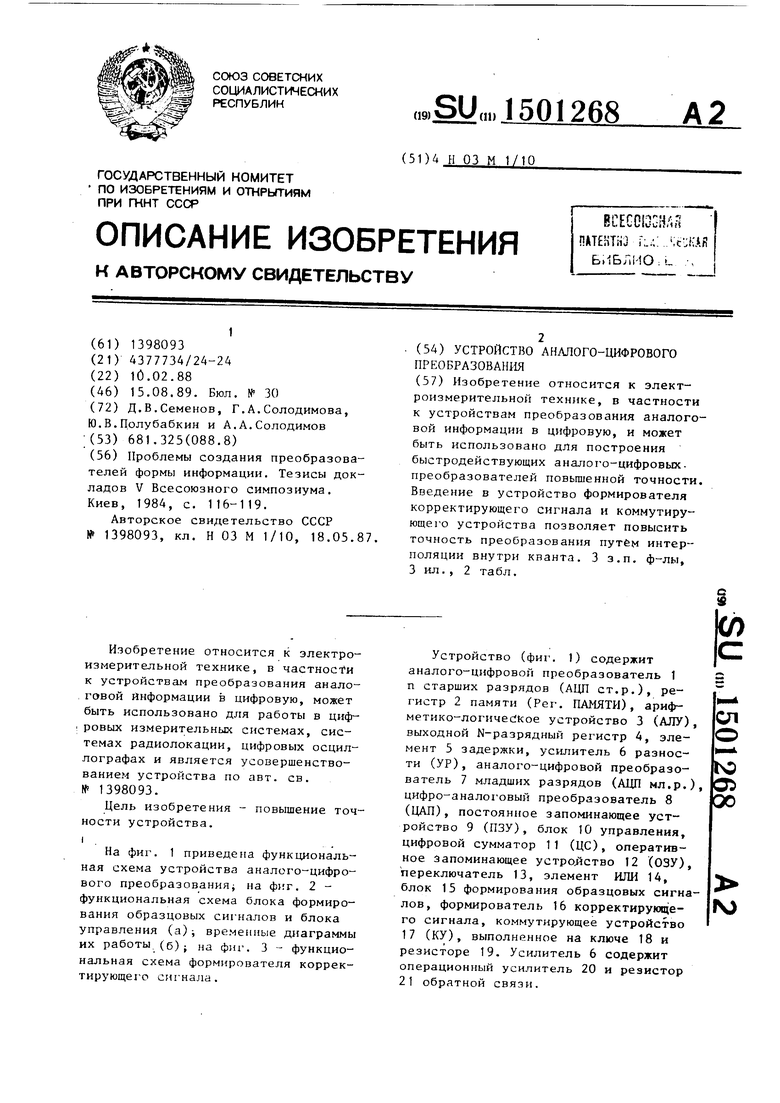

Изобретение относится к электроизмерительной технике, в частности к устройствам преобразования аналоговой Информации в цифровую, может быть использовано для работы в цифровых измерительных системах, системах радиолокации, цифровых осциллографах и является усовершенствованием устройства по авт. св. № 1398093.

Цель изобретения - повышение точности устройства.

I

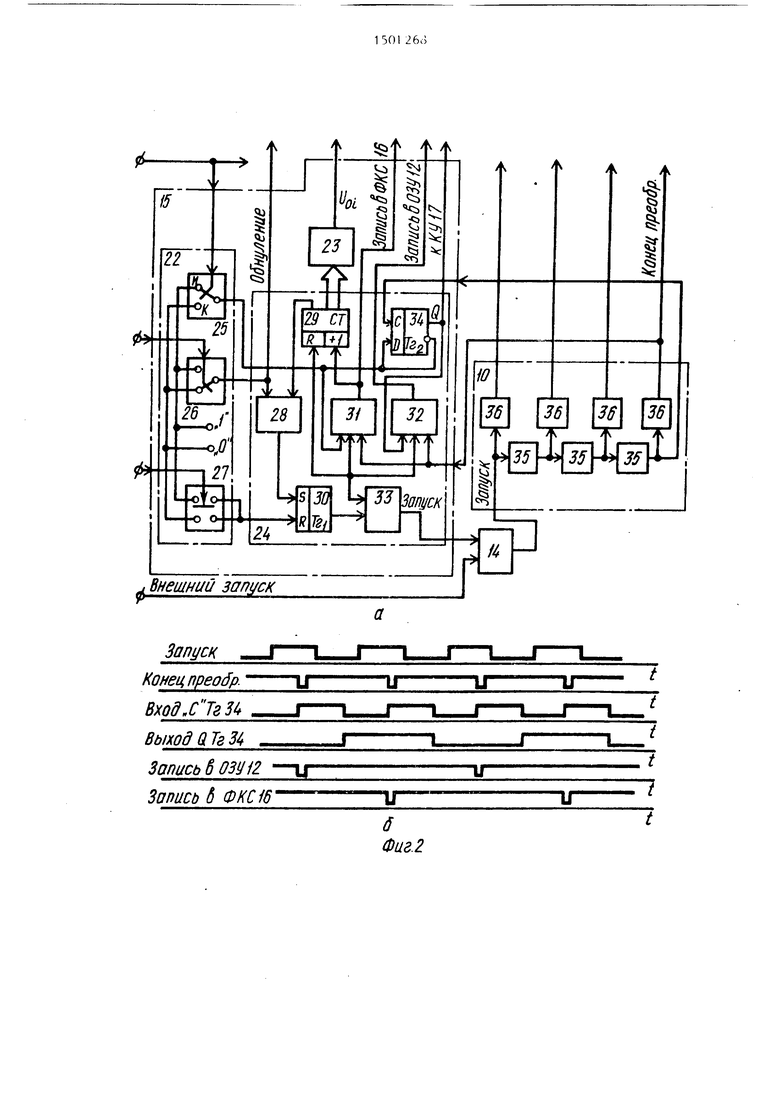

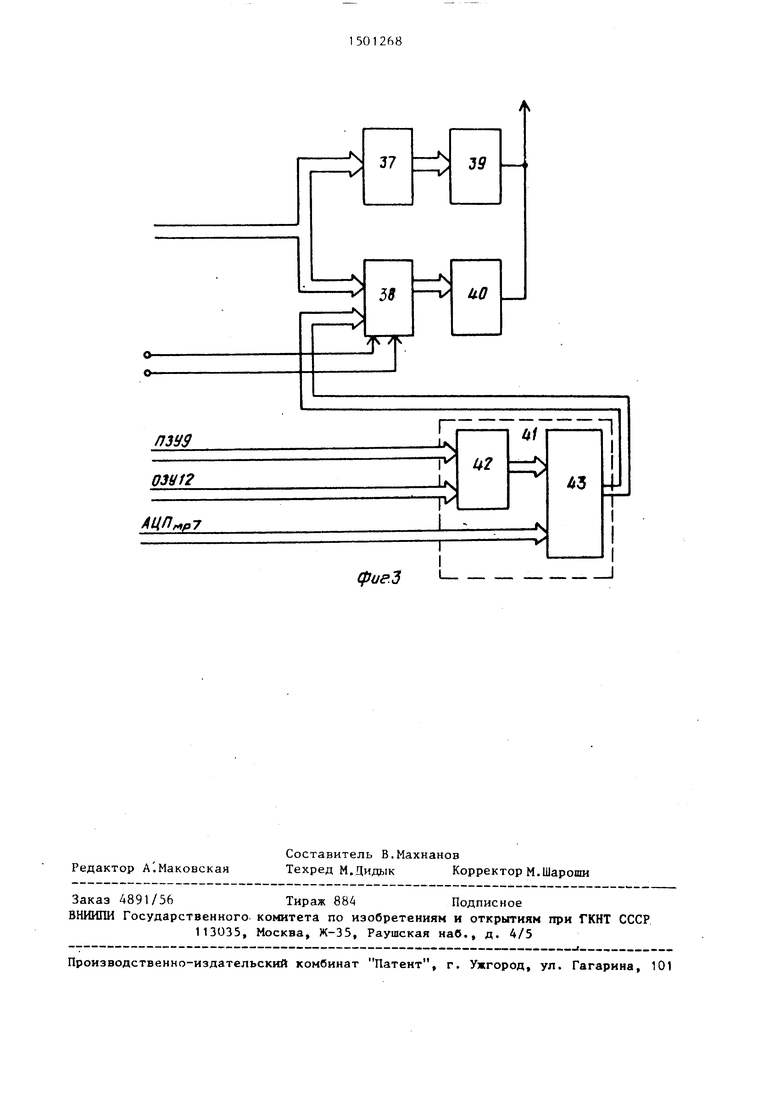

На фиг. 1 приведена функциональная схема устройства аналого-цифрового преобразования; на фиг. 2 - функциональная схема блока формирования образцовых сигналов и блока управления (а); временные диаграммы их работы (б); на фиг. 3 - функциональная схема формирователя корректирующего сигнала.

Устройство (фиг. 1) содержит аналого-цифровой преобразователь 1 п старших разрядов (АЦП ст.р.), регистр 2 памяти (Per. ПАМЯТИ), арифметико-логическое устройство 3 (АЛУ), выходной N-разрядный регистр 4, элемент 5 задержки, усилитель 6 разности (УР), аналого-цифровой преобразователь 7 младших разрядов (АЦП мл.р.), цифро-анало1 овый преобразователь 8 (ЦАП), постоянное запоминающее устройство 9 (ПЗУ), блок 10 управления, цифровой сумматор 11 (ЦС), оперативное запоминающее устройство 12 (ОЗУ), переключатель 13, элемент ИЛИ 14, блок 15 формирования образцовых сигналов, формирователь 16 корректирующего сигнала, коммутирующее устройство 17 (КУ), выполненное на ключе 18 и резисторе 19. Усилитель 6 содержит операционный усилитель 20 и резистор 21 обратной связи.

СП

bo

05

00

N

3150

Блок 15 формирования образцовых сигналов и блок 10 управления (фиг, 2) содержат узел 22 задания режимов, источник 23 опорного напряжения и блок 24. Узел 22 задания режимов содержит первый 25, второй 26 и третий 27 переключатели. Блок 24 выполнен на элементе И 28, счетчике 29 импульсов (СТ), первом триггере 30, элементах ИЛИ 31, 32, генераторе 33 импульсов (ГИ), втором триггере 34.

Блок 10 управления выполнен на трех элементах 35 задержки и четырех формирователях 36 импульсов (ФИ).

Формирователь (ФКС) корректирующего сигнала (фиг. 3) содержит постоянное запоминающее устройство 37 (ПЗУ), оперативное запоминающее устройство 38 (ОЗУ), малоразрядные цифроаналоговые преобразователи 39 и 40 (МЦАП); цифровой сумматор 41 включает в себя сумматоры 42 и 43.

Рассмотрим работу устройства на конкретном примере. Пусть число разрядов N всего устройства, включая знаковьп разряд, равно 11, число разрядов п АЦП ст.р. 1 равно 4; ЛДП мл.р. 7: N-n+m 8 (где m 1 - число разрядов коррекции), диапазон входного сигнала U j( -1,024 - - +1,014 В.

В качестве узла 8 используется быстродействующий интегральный ЦАП (например, типа 1118ПА1) низкой точности. Инструментальная погрещность таког о ЦАП значительна и превышает в несколько раз требования, предъявляемые к узлу 8 в составе устройства АЦ-преобразования.

Допустим, чтр значения разрядных уровней ЦАП 8 с учетом их инструментальных погрешностей равны: U, 128 - 1,25 126,75 мВ; 256 + + 2 258 мВ; 512 - 2,25 509,75 мВ; ик4 -1024 + 4 -1020 мВ. Значения всех остальных уровней определяются линейной комбинацией разрядных уровней (для упрощения примем также смеп;ение нуля усилителя 6 разности равным нулю).

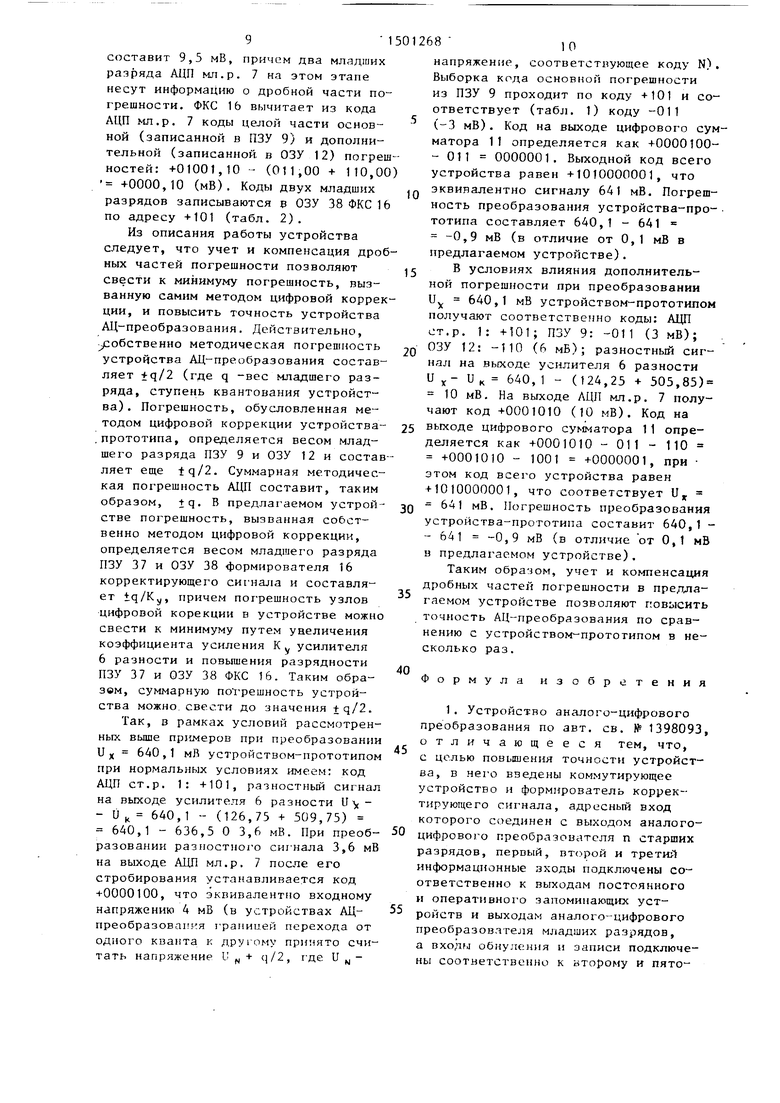

На этапе изготовления и настройки устройства, при нормальных условиях определяются погрешности ЦАП 8 присущие каждому уровню, и записываются в цифровой форме с учетом знака: целые знгтения (единицы Мв) в ячейки ПЗУ У, дробные (доли мВ) - в ячейки ФКС 16. При зтом вес млад2684

шего разряда ПЗУ 9 соответствует ,1 мВ, значительно меньше ступени квантования всего АЦП и, допустим, равен 0,25 мВ.

5 Адресом каждой ячейки ПЗУ -9 и ФКС 16 является соответствующий код АЦП ст.р. 1 (см. табл. 1, составленную только для положительного входного

jQ сигнала Uy; для отрицательного диапазона входного сигнала алгоритм коррекции аналогичен положительному диапазону).

В процессе эксплуатации устройст.с во может быть работоспособным в двух режимах - в режиме Измерение и в режиме Контроль.

В режиме Измерение переключатель 13 устанавливают в положение И, при

20 этом на вход АЦП ст.р. 1 подается сигнал и 640,1 мВ. После стробирова- ния АЦП ст.р. 1 формируется код +101, который с помощью ЦАП 8 преобразуется в компенсирующее напряжение U .

25 (128-1,25)+(512-2,25) 636,5 мВ. По коду старших разрядов -t-101 производится выборка кодов основной погрешности: кода из ячейки ПЗУ 9: -011(-3 мВ) и кода дробной части из

30 я 1ейки ФКС 16 10 (0,5 мВ) (см.табл.1), Код дробной части погрешности с помощью ФК) 16 преобразуется в корректирующее напряжение и орзнак которог о противоположен знаку погрешности. Напряжение суммируется (с учетом

35

45

знака) с компенсирующим напряжением и и сравнивается с входньм напряжением и с помощью усилителя 6 разности. Разностный сигнал ((U - (Uj +

40 установившийся на входе УР о, преобразуется АЦП мл.р. 7 после его стробирования в код, которьш складывается в цифровом сумматоре 11 с кодом целой части основной погрешности, записанной в ПЗУ 9. В рамках рассматриваемого примера и х- (И квр к 640,1 - (636,5 + 0,5) 3,1 мВ. На выходе АЦП мл.р. 7 имеем код: +0000011 (3 мВ), код на выходе цифрового сумматора 11 определяется как

50 -t-0000011 - 011 +0000000-. Выходной код него устройства равен+1010000000, что эквивалентно сигналу U 640 мВ. Погрешность преобразования устройства составит 640,1 - 640 0,1 мВ.

При желании ее можно уменьшить,

уменьшив ступени квантования дробной части или (что равносильно) повысив разрядность обоих МЦАП в ФКС 16).

51

При работе устройства в условиях отличных от нормальных, появляется дополнительная инструментальная погрешность. Коррекция погрешности с помощью предварительной ее записи в ПЗУ 9 и ПЗУ 37 в ФКС 16 теряет свою эффективность, так как не приводит к ее компенсации.

Так, в рамках условий рассмотрен- него вьнпе npPiMepa можно допустить, 1ЧТО разрядные уровни ЦАП 8 при наличии дополнительной погрешности из|(

менились и стали равны: U

к, 126,73и;, 509,75 -2,5 124,25 мВ; U 258 + + 3,25 261,25 мВ;

-3,9 505,85 мВ.

В этом случае коды целой части дополнительной погрешности хранятся в ОЗУ 12, а коды дробной части записываются в ОЗУ 38 ФКС 16. Запись кодов дополнительной погрешности осуществляется в соответствии с табл. 2, составленной для положителного Входного сигнала U;.

При преобразовании входного сигнала, например при U 640,1 мВ

получим коды - АЦП ст.р. ПЗУ

1: +101,

9: -011 (-3 мВ); ОЗУ 12: -110 (-6 мВ); коды дробных частей-основной -10 (-0,5 мВ) и дополнительной -10 (-0,5 мВ) погрешностей, записанных в ФКС 16; соответственно в ПЗУ 37 и ОЗУ 38 (фиг. 3). На выходе АЦП мл.р. 7 получим код +0001001 (+9 мВ), что соответствует разностному сигналу и ,( - (и { + ) 640,1 - (124,25 + 505,85 + 0,5 -i- + 0,5) 9 мВ. После сложе ния кодов АЦП мл.р. 7 с кодами ПЗУ 9 и ОЗУ 12 в цифровом сумматоре 11 получим код младших разрядов устройства: +0001001-011-110 +0000000. При этом код всего устройства N +1010000000, что соответствует Uy 640 мВ. Погрешность преобразования в рассматриваемом примере составляет 0,1 мВ.

.Определение и запись кодов дополнительной norpeujHocTH проводится в режиме Контроль. В этом режиме устройство переводится установкой переключателя 13 в положение К. На вход АЦП ст..р. 1 с выхода блока 15 формирования образцовых сигналов поступает ступенчатое напряжение, уровни которог о соответствуют значениям идеальных уровней ЦАП 8.

0

5

0

5

0

5

0

5

Определение и запись кодов дополнительной погрешности осуществляют в два этапа. На первом этапе - этапе грубой оценки погрешности - при подаче очередного уровня образцового напряжения на вход АЦП ст.р. 1 после запуска устройства на выходе цифрового сумматора 11 формируется код, численно равный значению целой части дополнительной погрешности. По сигналу с блока 15 этот код записывается в ячейку ОЗУ 12, адрес которой соответствует коду АЦП ст.р. 1 в данном такте коррекции. На втором этапе - этапе уточненной оценки погрешности - по сигналу с шестого выхода блока 15 размыкается ключ 18 коммутирующего устройства 17, что приводит к увеличению коэффициента усиления усилителя 6 разности. В результате этого на выходе АЦП мл.р. 7 формируется код, численно равный уточненному значению дополнительной погрешности. Этот код поступает на вход ФКС 16, который вьщеляет код дробной части дополнительной погрешности и осуществляет запись его по команде с блока 15 в ячейки своего ОЗУ 2.

При поступлении сигнала Конец преобразования с четвертого выхода блока 10 управления разрешается установка следующего уровня образцового напряжения. После формирования последнего уровня образцового напряжения происходит остановка блока 15, что свидетельствует об окончании процесса контроля.

Блок 15 формирования образцовых сигналов и блок 10 управления БУ 10 (фиг. 2) работают следующим образом.

В исходном состоянии переключатели 25-27 узла 22 задания режимов устанавливают в положение, показанное на фиг. 2. Перед началом режима Контроль перекхпочатель 25 переводят в противоположное положение, при этом прекращается процесс обнуления ОЗУ 12 (фиг. 1) и ОЗУ 38 формирователя 16 (фиг. 3) и через элемент И 28 триггер 30 устанавливается в единичное состояние. Это дублирует сигнал запрета на первом управляющем входе генератора 33 импульсов. Далее одновременно с переключателем 13 устройства (фиг. 1) переключается переключатель 25, что приводит к обнулению двоичного счетчика 29 и подаче сигнала

715

разрешения (логического О) на вторые входы элементов ШШ 31 и 32 и второй управляющий вход генератора 33. По нулевому коду счетчика 2У источник 23 опорного напряжения формирует на пряжение, соответствующее идеальному значению напряжения для точки шкалы АЦП (Ug, -1024 мВ). После такой подготовки блок 15 готов к работе.

При необходимости коррекции дополнительной инструментмльной погрешнос- И нажимают кнопки (переключатель) 27, и триггер 30 запускает генератор 33 импульсов, обеспечиваю1ций периодический ззпуск АЦП (см. диаграмму импульсов Запуск на фиг. 2б). Триггер 34, В1,мючеины11 по схеме делителя члс 1 оты, проводит распределение тактов работы устройства АЦ-преобразова- ния на так1ы 1рубой и уточненной оценки гто1 решности: при наличии на выходе Q григтера 34 лог ического О (см. диаграмму импульсов Выход Q Тг 34) осуществляется грубая оценка погрешности, логической 1 - уточне)и1ая оценка. Сигн;1лом Конец преобразования с четвертого выхода блока 10 управления через элемент HJiH 32 проводится запись кодов целой г О1 решнос ги в ОЗУ 12 (такт I pyCo оценки), .5 через элемент РШН 31 - запись кодов дробной части (такт уточненной оценки) в ФКС 16 (см. ди;.и рамму импульс)в Запись в ОЗУ 12

и Запись в ФКС 16 на фиг. 2б). Импульсом Запись в ФКС 16 с выхода элемента ИЛИ 31 изменяется состояние c4eT4tfiva 29 импульсов на единицу и устанавливается следуюшее значение образцового уровня напряжения и т.д.

Сигнал переполнения счетчика 29 через элемент И 28 переводи ipniTep 30 в исходное состояние, ос1ананли- вая Тем самым генератор 33 импульсои Это свидетельс 1 вуст об сткоичании процесса коррекции погрешности. При переводе переключателей 13 (фиг. 1) и 25 (фиг. 2) в положение И устройство АЦ-преобразования готово к работе в условиях.

Формирователь 16 корректирующего сигнала ФКС (фиг. 3) работает спедую щим образом.

При коррекции основной norpciiniocT напряжение корректирующег о сигнала и снимается с выхода мало 5азрядно- I o ИЦАП 3 (в заявленном устройстве МЦАП 3 и МЦАП 4 реа-чизованы на преоб

8 8

разователях код - ток), преобразующего коды дробной части основной погрешности, записанной в ПЗУ 1 на этапе изготовления и настройки устройства АЦ-преобразования. При коррекции дополнительной г.огрешности напряжение определяется суммой выхол,нь1х напряж(;-ний токов МЦАП 3 и Ми/Л 4, при этом МЦАП 4 преобразует кеды дробнь х частей дополнительной погрешности, записанной в ОЗУ 2. Коды дробных частей дополнительной погрешности выделяются цифровым сумматорюм 41, вычитающим из кодов уточненной оценки погрешности, с;нимае- мых с выхода АЦП мл.р. 7 устройства (фиг. 1), код грубо оценки, чис- ленно равный целой части noi реипюс

ти. Коды целой части основной погрешности записа1Н5| в ПЗУ 9, допол- ните льной погрешности - в ОЗУ 12.

Рассмотрим запись кодов дополнительной погрешности на примере.

Пусть в режиме Контроль на вход АЦП ст.р. 1 подается образцовое нап- ряже1П1е Llo; 640 мВ. Б условиях влияния дополнительной погрешности на выход,е УР 6- разность IJ х (IJ k,

,+ и;, + UK,P,. - 640 - (124,25-ь + 503,85.+ 0,5) 5,4 мВ (см. табл. 1 и 2). На выходе цифрового сумматора 11 на этапе грубой оценки формируется код, равнь й (табл. 1) сумме кодов ПЗУ 9 и АЦП мл.р. 7 (в начальный момент KOHTpojn коды ОЗУ 12 И ОЗУ 38 формирователя 16 равны нулю): +0001001 + (-011) +0000110. Полу- ченн1,|й код эквивалентен целой части допо.пнительной погрешности, взятой с противоположным знаком, т.е. --6 мВ (таб Т. 2). Инверсию знака погрешности м .)жно произвести при выполнении операции сложения в ЦС 11 или при загшси яепосредственно крд; Югреш

ности в ОЗУ 12.

Н,ч этапе уточненной оценки погрешности увеличивается коэффипиент усиления К усилителя 6 разности, например, в четыре раза. Это эквивалентно уменьшению значения ступени квантования АЦП мл.р. 7 и для рассматриваемого примера составляет q 0,25 мВ. Тогда при преобразовании напряжения КУуСи - (U + 11,1 4-9,4 37,6 мВ на выходе АЦП мл.р. 7 получаем код +01001,10, численное значение которого, приведенное к входу усилителя 6 разности,

составит 9,5 мВ, причем два младших разряда АЦП мл.р. 7 на этом этапе несут информацию о дробной части погрешности. ФКС 16 вычитает из кода АЦП мл.р. 7 коды целой части основной (записанной в ПЗУ 9) и дополнительной (записанной, в ОЗУ 12) погрешностей: +01001,10 - (011,00 + 110,00)

+0000,10 (мВ). Коды двух младших разрядов записываются в ОЗУ 38 ФКС 16 по адресу +101 (табл. 2).

Из описания работы устройства следует, что учет и компенсация дробных частей погрешности позволяют свести к минимуму погрешность, вызванную самим методом цифровой коррекции, и повысить точность устройства Ц-преобразования. Действительно,

обственно методическая погрешность устройства АЦ-преобразования составяет ±q/2 (где q -вес младшего разряда, ступень квантования устройства). Погрешность, обусловленная методом цифровой коррекции устройствапрототипа, определяется весом младшего разряда ПЗУ 9 и ОЗУ 12 и составяет еще tq/2. Суммарная методическая погрешность АЦП составит, таким образом, iq. В предлагаемом устройстве погрешность, вызванная собственно методом цифровой коррекции, определяется весом младшего разряда ПЗУ 37 и ОЗУ 38 «формирователя 16 корректирующего сигнала и составляет tq/Ky, причем погрешность узлов цифровой корекции в устройстве можно свести к минимуму путем увеличения коэффициента усиления К у усилителя 6 разности и повьш1ения разрядности ПЗУ 37 и ОЗУ 38 ФКС 16. Таким обра- звм, суммарную по 1 решность устройства можно свести до значения tq/2.

Так, в рамках условий рассмотренных выше примеров при преобразовании и X - 640 ,1 мВ устройством-прототипом при нормальных условиях имеем: код АЦП ст.р. 1: +101, разностный сигнал на выходе усилителя 6 разности U - и 640,1 - (126,75 + 509,75) 640,1 - 636,5 О 3,6 мВ. При преобразовании разностного сиг нала 3,6 мВ на выходе АЦП мл.р. 7 после его стробирования устанавливается код +0000100, что эквивалентно входному напряжению 4 мВ (в устройствах АД- преобразовапия границей перехода от одного кванта к другому принято считать напряжение U + Ч/2, г-де

U,10

15

0

5

0

5

0

5

0

5

напряжение, соответствующее коду N), Выборка кода основной погрешности из ПЗУ 9 проходит по коду +101 и соответствует (табл. 1) коду -011 (-3 мВ). Код на выходе цифрового сумматора 11 определяется как +0000100-011 0000001. Выходной код всего устройства равен +1010000001, что эквивалентно сигналу 641 мВ. Погрешность преобразования устройства-про- тотипа составляет 640,1 - 641

-0,9 мВ (в отличие от О,1 мВ в предлагаемом устройстве).

В условиях влияния дополнительной погрешности при преобразовании и 640,1 мВ устройством-прототипом получают соответственно коды: АЦП ст.р. 1: +101; ПЗУ 9: -011 (3 мВ); ОЗУ 12: -110 (6 мБ); разностный сигнал на выходе усилителя 6 разности UK 640,1 - (124,25 + 505,85) 10 мВ. На выходе АЦП мл.р. 7 получают код +0001010 (10 мВ). Код на выходе цифрового сумматора 11 определяется как +0001010 - 011 - 110 +0001010 - 1001 +0000001, при этом код всего устройства равен + 1010000001, что соответствует U 641 мВ. Погрешность преобразования устройства-прототипа составит 640,1 -641 -0,9 мВ (в отличие от 0,1 мВ в предлагаемом устройстве).

Таким образом, учет и компенсация дробных частей погрешности в предлагаемом устройстве позволяют повысить точность АЦ-преобразования по сравнению с устройством-прототипом в несколько раз.

Формула изобретения

1. Устройство аналого-цифрового преобразования по авт. св. № 1398093, отличающееся тем, что, с целью повышения точности устройства, в него введены коммутирующее устройство и формирователь корректирующего сигнала, адресный вход которого соединен с выходом аналого- цифрового преобразов ятсля п старших разрядов, первый, второй и третий информационные зходы подключены соответственно к выходам постоянного и оперативног о запоминающих устройств и выходам аналого-цифрового преобразо)зятеля младших разрядов, а входы обнулегния и записи подключены соответственно к второму и пяточ150

му выходам блока формирования образцовых сигналов, выход формирователя корректирующего сигнала подключен к второму входу усилителя разности и входу коммутирующего устройства, выход которого подключен к выходу усилителя разности, а управляющий вход соединен с шестым выходом блока формирования образцовых сигналов, при этом пятый выход блока управления Соединен с пятым входом блока формирования образцовых сигналов.

2.Устройство по п. 1, о т л и- чающееся тем, что формирователь корректирующего сигнала выполнен на постоянном и оперативном запоминающих устройствах, двух цифроана- логовых преобразователях и цифровом сумматоре, причем адресным входом блока являются соответствующие адресные входы постоянного и оперативного запоминающих устройств, первым, вторым и третьим информационными входами являются соответствующие первый, второй и третий входы цифрового сумматора, входами обнуления и записи являются входы обнуления и записи оперативного запоминающего устройства, выходом блока являются объединенные выходы цифроаналоговых преобразователей, входы которых подключены

к выходам соответственно постоянного и оперативного запоминающих устройств выход цифрового сумматора подключен к информационному входу оперативного запоминающего устройства.

3.Устройство по п. 1, о т л и - чающееся тем, что коммутирующее устройство выполнено на последовательно соединенных ключе и резисторе, причем входом блока является информационный вход КЛЮЧ9, управляющий вход которого является управляющим входом блока, выходом которог о является свободный вывод резистора.

4.Устройство по п. 1, о т л и- чающееся тем, что блок формирования образцовых сигналов выполнен на источнике опорного напряжения, пе вом, втором и третьем переключателях

двух элементах ИЛИ, счетчике импульсов, элементе И, днух триггерах и генераторе импульсов, причем первым, вторым и третьим входами блока являются соответственно управляющие входы первог о, второго и третьего переключателей, а первым выходом - выход источника опорного напряжения, входы

д которого соединены с соответствующим информационными выходами счетчика импульсов, вход обнуления которого объединен с первым управляющим входом генератора импульсов, первым вхо- 5 дом первого элемента ИЛИ и подключен к выходу первого переключателя, первый и второй входы которого объедине- ны соответственно с первыми и вторыми входами второго и третьего переQ ключателей и являются соответственно шинами логического нуля и единицы, выход второго переключателя соединен с первым входом элемента И и является вторым выходом блока, третьим выC ХОДОМ которого является выход первого элемента ИЛИ, второй вход которого является четвертым входом блока, выход переполнения счетчика импульсов соединен с вторым входом элемента И, выход которого подключен к входу установки в 1 первого триггера, прямой выход Ko-foporo соединен с вторым управляющим входом генератора импульсов, а вход установки О подключен к выходу третьего переключателя, вы5 ход генератора импульсов является четвер тым выходом блока, а первый вход второго элемента ИЛИ является четвертым входом блока, второй вход объединен с первым входом первого элемента ИЛИ, а третий вход объединен с информационным входом второго триггера и подключен к его инверсному выходу, выход второго элемента ИЛИ соединен со счетным входом счетчика

импульсов и является пять 1м выходбм блока, пятым входом которого является счетный вход второго триггера, прямой выход которого подключен к третьему входу первого элемента ИЛИ

0

0

0

и является шестым выходом .блока.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1398093A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2020751C1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Устройство контроля аналого-цифровых преобразователей | 1988 |

|

SU1711327A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2013863C1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДАВЛЕНИЯ И СПОСОБ ПОДГОТОВКИ ЕГО К РАБОТЕ | 2008 |

|

RU2384824C1 |

| Устройство контроля аналого-цифровых преобразователей | 1983 |

|

SU1128381A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1690197A1 |

Изобретение относится к электроизмерительной технике , в частности, к устройствам преобразования аналоговой информации в цифровую, и может быть использовано для построения быстродействующих аналого-цифровых преобразователей повышенной точности. Введение в устройство формирователя корректирующего сигнала и коммутирующего устроиства. Позволяет повысить точность преобразования путем интерполяции внутри кванта. 3 з.п. ф-лы, 3 ил. , 2 табл.

|t

.

Внешний зап1/ск

Запуск

KoHeu,npeodp.

Вход.

U

фиг.З

| Проблемы создания преобразователей формы информации | |||

| Тезисы докладов V Всесоюзного симпозиума | |||

| Киев, 1984, с | |||

| Способ получения бензидиновых оснований | 1921 |

|

SU116A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1398093A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-15—Публикация

1988-02-10—Подача