Из обретение относится к радиотехнике и может использоваться в устройствах автоматической подстройки частоты

: Цель изобретения - повышение чув- твитехшности,

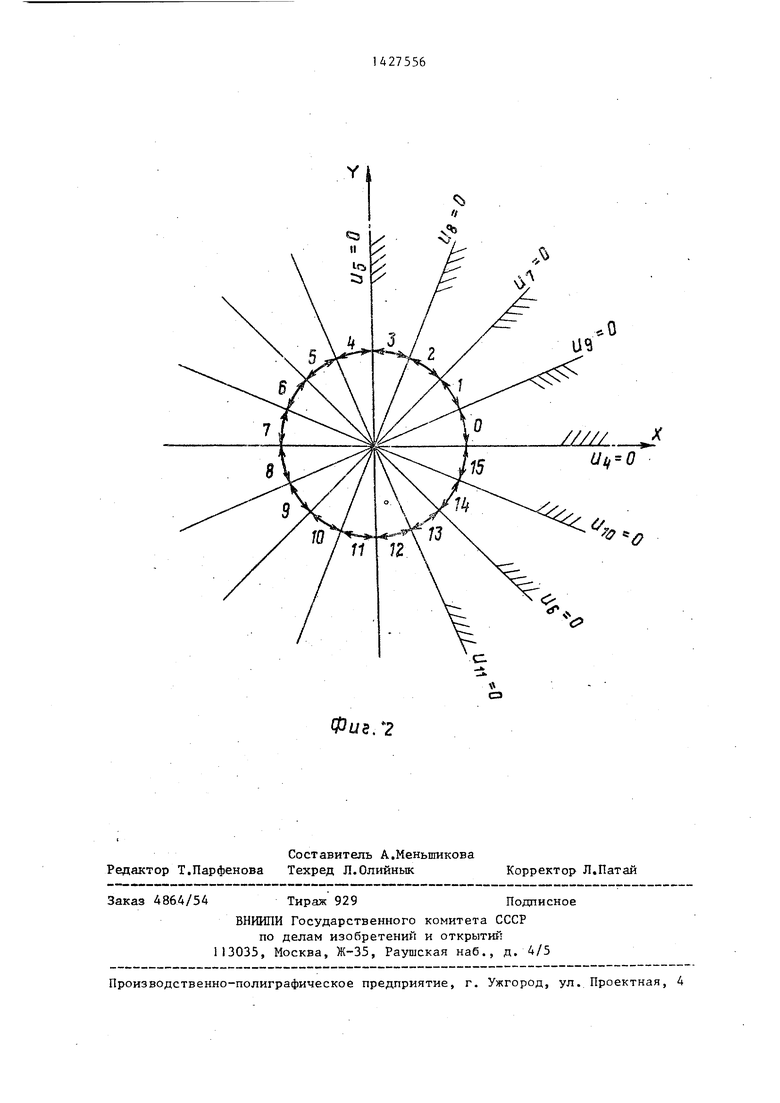

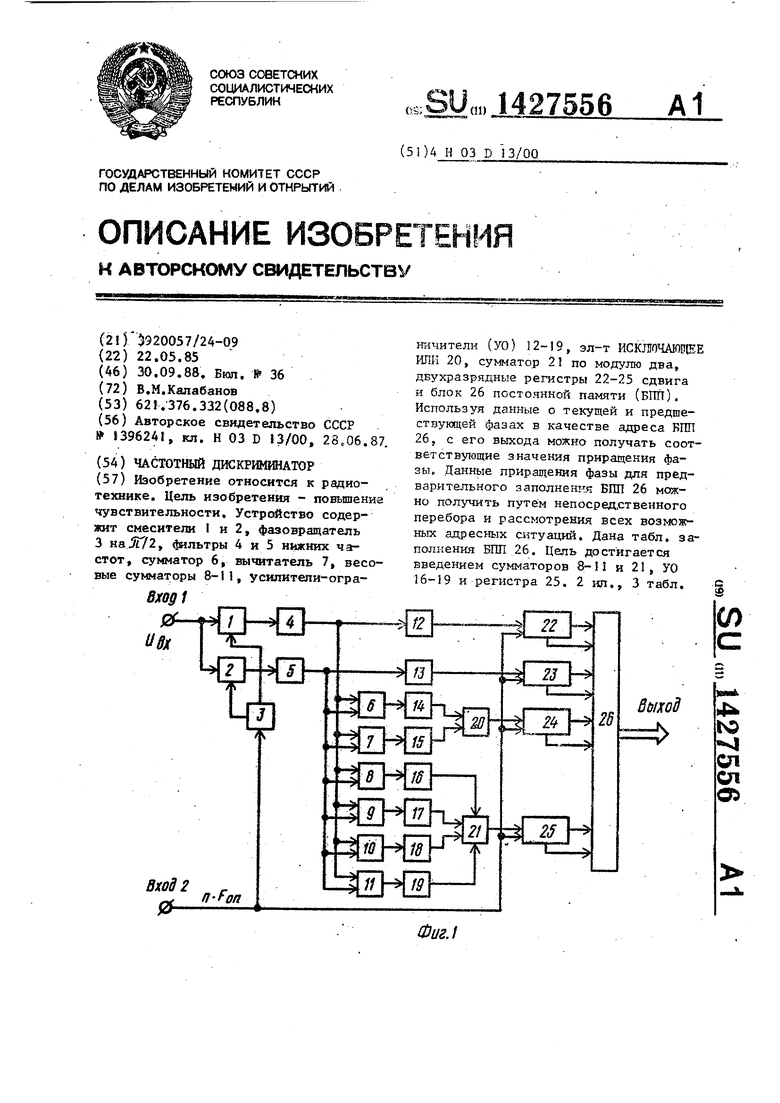

I На фиг. 1 приведена принципиаль- ая электрическая схема предлагаемого частотного цяскрк -тпатора. фиг., 2 д - аграмма, поясняющая его работу

Частотный дискриминатор содержит первый и второй смесители и 2 фаовращатель 3 на.31/2, первьй н вто- |5 рой фитгьтры нижних частот (ФНЧ) 4 и 5, сумматор б, Бычитатель 7, первьй, второй, третий.и четвертый весовые Сум :1аторы 8-11, первыйэ второй,, тре- tssfi, четвертый, пятый, шестой, ..седь- 20 йой,; восьмой усилители-ограничители 12-595 элемент ИСКЛЮМЩЕЕ ВДИ 20., СУ шатор 21 по модулю два, первый, второй-, третий и четвертьй двухразрядные регистры 22-25 сдвигаа блок 25 26 постоянной памяти. ; Частотный дискриминатор работает следующим образом

Смесители и 2, на вторые входы которьш подаются взаишго квадратурньш 30 сигналы (sin 21Гроп t и cos 2ГГад1) спорной частоты Гоп э переносят входные сигналы с частотами в область сзП Шарных (fc-i-fot, ) и разностньга ::

(1)

При этом суммирование сигналов в весовых сумматорах 8-11 должно выполняться алгебраически с учетом определенных знаков и определен1л х весовых коэффициентов5 пропорциональных некоторым тригонометрическим функци- , ям отЗГ/В, например, по выражениям:

Ug-Uj-U tgCS /S) tp:(7r/8)U (T/8)+U4 lln UsH-U tgdr/S)

где U{ - сигнал на выходе i-го узла.

С учед ом этих выражений линии частотного дискриминатора, делят всю область на 16 фазовых секторов - по ,F/8 радиан каждый; условно принятые номера секторов с О по 15 показаны на фиг, 2 по окружности. По диаграм ме фиг. 2 можно легко определить для каждого фазового сектора знак (полярность) каж,цого из сигналов U: |i 4-lljj Hj следовательно, и значения сигналов на выходах усилителей ограничителей 12-19.

Приняв для конкретности, что на выходе каждого усилителя-ограничителя сигнал равен

ft ; П

НОИ

и

скгнал U,v . О S

э И

если его ЕКОД- равен О, если

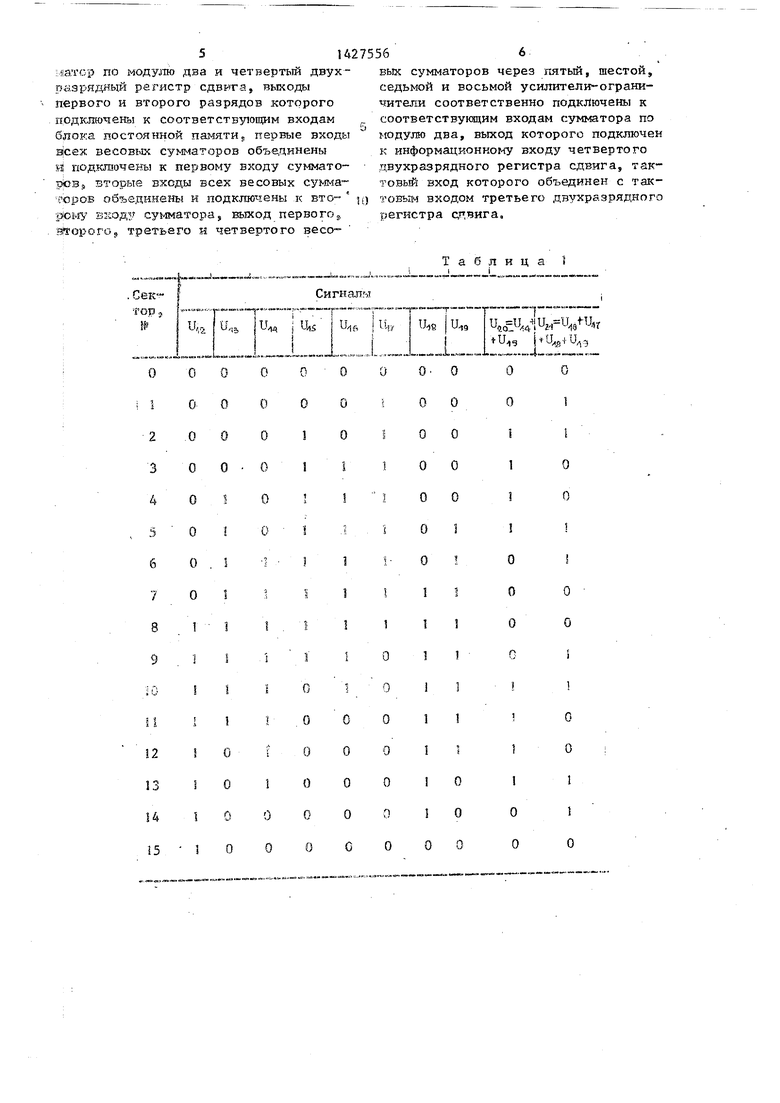

g,, получаем для отдельнь х секторов комбинации сигналов Ц -U-sg показ анные в табл. ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотный дискриминатор | 1985 |

|

SU1396241A1 |

| Следящий фильтр фазоманипулированного псевдослучайного сигнала | 1982 |

|

SU1072252A1 |

| Многоканальное устройство для измерения амплитудно-фазового распределения поля фазированной антенной решетки | 1986 |

|

SU1474563A1 |

| Устройство для формирования сигналов с изменяющейся частотой | 1982 |

|

SU1149373A1 |

| Система управления вибростендом | 1984 |

|

SU1259224A2 |

| Устройство для измерения амплитуд и фаз излучения элементов фазированной антенной решетки | 1986 |

|

SU1442940A1 |

| Многочастотный цифровой фильтр | 1987 |

|

SU1474827A1 |

| МОНОИМПУЛЬСНАЯ РЛС | 2004 |

|

RU2267137C1 |

| Преобразователь угла поворота вала в код | 1980 |

|

SU866570A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

Изобретение относится к радиотехнике. Цель изобретения - повьапениз чувствительности. Устройство содержит смесители I и 2, фазовращатель 3 наД72, «Jильтpы 4 и 5 нижних частот, сумматор 6, вычитатель 7, весовые сумматоры 8-11, усилители-ограBxogl 0- ЙГ Вход 2 ничители (УО) 12-19, эл-т ИСКЛОЧАЮЩЕЕ Р1ПК 20, сумматор 21 по модулю два, двухразрядные регистры 22-25 сдвига и блок 26 постоянной памяти (БПТТ). Используя данные о текущей и предшествующей фазах в качестве адреса БГШ 26, с его выхода можно получать соответствующие значения приращения фазы. Данные приращения фазы для предварительного заполненкч БГШ 26 можно получить путем непосред.ственного перебора и рассмотрения всех возможных адресных ситуаций. Дана табл. заполнения БПП 26, Цель достигается введением сумматоров 8-11 и 21, УО и регистра 25. 2 ип., 3 табл. ш Зшод 4 Ю N| СП О1 Од

( ) частот. ФНЧ 4 и 5 подашш- « ют составляющие суммарных частот к ту- мьц сигналы на выходах ФНЧ 4 и 5 содержат- информацию о разностной частО - те fr -Fon ; частота их соответствует

(-f F

, -Lr -Г л

а

модулю разности частот взаимный фазовый сдвиг (-i-90° или 90°) зависит от знака этой разнос™ тИс, Обозначим выходные сигналы с ФНЧ 4 и 5 Щ и Us- соответственно,,

Работа ,всего частотного дискрими™ натора в целом может быть пояснена с помощью диaгpaм lы изобра;«енной на фиг о 2« При этом на координатной ;гшоскости Хр Y, принимая можно провести ряд прямых :рых сигнал на выходе i-ro узла (номера узлов соответствуют фиг 1) , при этом Ug Uj-fU ; 11. 1)5 U о Соответствукшзйе прямые показаны на фиг„ 2, При этом U 0 и Us 0 совпадают с осями X и Y. Косой штриховкой на диаграмме отмече-- нь те стороны линий :на которых Ui 0

5 S 7- S

на кото

50 э -iS 4i9

В табл. J приведены и сигналы Uji, , определяеьгые сигналами

в соответствии с логикой работы элемента ИСКЛ10 1АЮЩЕЕ ШМ 20 и сумматор 21 по модул два, При определе- ьши bV, можно у читывать 4 что суммирование двух одноразрядных чисел яо кодулю 2 эквизалйн гыо ИСКЛЮЧАЮЩЕЮ ШМ,, поэтоь -/ можно записать

5

и,,

(и

Sb

и„ )4(и,„+и

Цч

ап21

0

5

-IT Это выражеиете подсказьгаает и паратурную реализацию сумматора по модулю два, например в виде трех двухвходовых одноразрядньтх элементов ИСКПЮЧАЮиЩЕ ИЛИд каждая из которых вьшолняет операцию t для двз к 4Kce:i7: первая для и Urrj втораяДЛЯ и Ujq-j третья - для ,ОДНЫХ

сигналов первых двух,

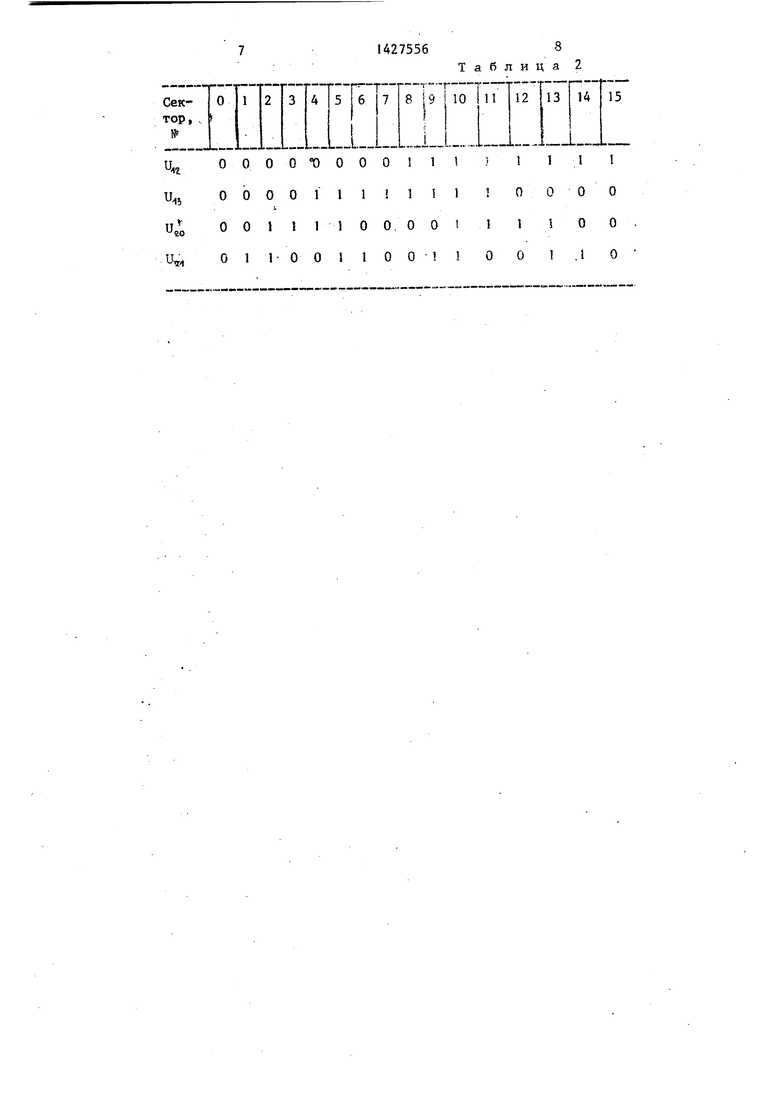

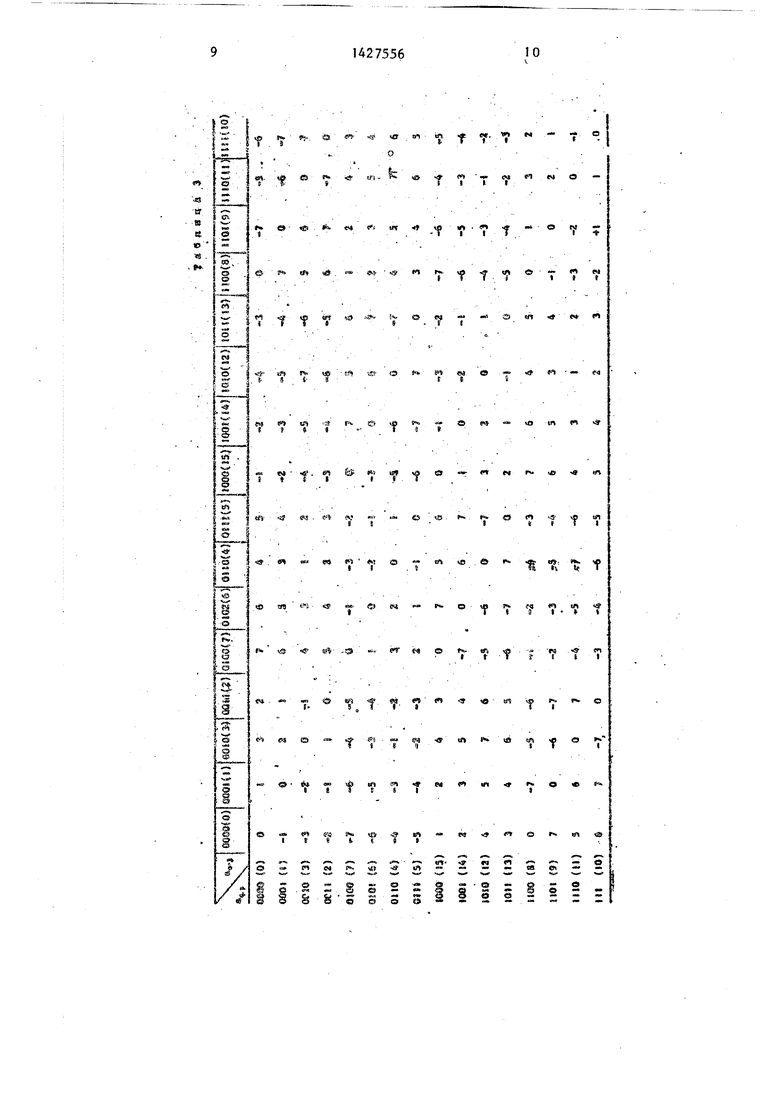

В табл. 2 приве гены коды для секторов ц,5, UM, IJ7,

Мажду номером сектора н четырех- разрядньш двоичным кодом -,составл.ен- иьш из сигналов ., Ъ -и, Uou, Uj, имеет место взаимно однозначное соответствие (табл, 1). Это легко подтверждается на основе выборки из табл 3 соответствующих данных,

Поскольку сигналы Ц , U. г Ь га з U. полностью определяют сектор, то информация о их текущих значеш-гяХ; записываемая в первые разряды двухраз- рядньзх регистров 22-25, и информация о кх предшествую1 тих зкачениях, имеющаяся во вторых разрядах дкухразряд- клх регистров 22-25 сдвига полностью определяет приращение фазь- {в количе ст ве кр ет сек г ор о в по 7Г / /8 рзд) за интервал следования сдвигающих cинxpoи myльcoв Аt. Этот факт полностью объясняет принцип работы предпагаемох-о частотного ,п -cкpи инa тора. При этом понятно, что,, используя данные о текупхей и предшгстБуюп.,;; фазе в качестве адреса блока 25, с вь1хода блока .26 можно получать соответствующие значения Д, Данные о для предварительного заполяеякя блока 26 можно получитьS например; путем непосредственного перебера и рассмотрения всех возможные: адресные ситуаций (при конкретном выборе соответствия между поляркостягда сигналов и значекия1-ш двоичных кодов )

Блок 26 должен иметь В-разряднуи адресахдао 4 двоичных разряда для

текущего значения фазы и 4 двоичных разряда для предшествующего. Поскольку приращения фазы ( различив; Б пределах ± 7 дискрет,, то для Данных в блоке 26 достаточно четырех дзоичиь х разрядов,

В табл, 3 приведен:- пример конкретной реализации запопкения блока

26 да: случая, когда младшие разряды адреса () соединены с выходам первых разрядов двухразрядных стров 22-25 (характеризующих текущую фазу), а разрядь . адреса блока 26 соединены с вьпсодами вторьтх разрядов двухразрядных регистров 22-25 (характеризующих предшествующую фазу уровни сигналов приняты теми же, В

скобках около кодов указан и соот . ветствующий порядковый номер сектора что облегчает вычисление изменения фазы д -), указываемого обычным десятичным кодом в централышх клетках т аблицы.

14275564

Фор м у л а изобретения

Частот1П:,К дискриминатор, содержа:; 1Й первьй смеситель,, вьгход которого .;;;;5eз первый фильтр нижт- х частот 4 одкпючен к входу первого усилителя- сгрaHH trHTe.nH,, выход которого под1 л1-э- чен к ннсрормацг онно г. вход, первого

Д5уxp Tp;,D;Kcro регкстра сдвига второй смеситель,, Перл/ый вход которого объединен с перБЫМ входом первого ,- еси : ля и пвпяется входом частотного дискрИ1 гкна ; ора, элход В опого смесит лк чЯ;рез второй йильтр Шлтлжи: частот подкшочеи к второго усяля- таля-ограничктс ля 5 фазовращатель ка ., состветствуюиие зькоды которого ;;одключен : к вторым зходак первсго i

второго с -;егк7елай; последо: атель;йа соецинениьте су первьа и вто рзй ; лО1л:; которого псдкл;:- 4е;1ь; соот- зйтствекно к выходам первого и второго ф тьтпо з нижнил частот, и третий

усилитель-ограничитель.; выход- которого подключен к перЕс:-:у входу элемента ИСКИЮ ЧАЮ щЕЕ 1-ШИ, последовательно соеди-некные вь.читьтель .первые и вт.., Бхэды хоторого подкл 7ч:ены к

ijepBCi-v и r Topoi-: входаг су,-;а.;г горл есотБетгч ланкс, и четЕгртъй усилз- - телг-огракичнгель,, выход кстор оги подклю -1ек к втopo Iy входу элемента ИСКЛОЧг О 1(ЕЕ К;:И,, второй и третш

двухра рпд:1ь е ргг:;:стрк СДВИГЕ, при . этом тактсвыг входы двухразрядг к регистров сдБ17га объедкксны с р-юдом

дон напряжения смгкьла опорпон часто- ты -lacTCTHoro дискриминатора, а так- жа -;но.гораз рядный cyм 5aтop , к сост- ветств;тсщи : гзходаг-: которого подютюче- ны выхоцм первых и вторьпс разрядов двухразрядных регчстров сдвига, о т- jT и ч а ю гд и и с я тем что« с и& лью повьпт-егтия чувствительности, вы-, ход второго усилителя-огранячнтеля подключен к ик.рмационном входу второго двухразрядного регистра сд.вига, выход зленен-а ИСКЛЮЧАЮЩЕЕ Ш Ш подктаочен к ннформационному РлО-- ду третьего двухразрядного регнстр.а сдвига, при этом многоразрядный сумматор выполнен в виде блока постоянной пш-штт;, при этом введены первьш, второй J трет1гй и четвертый весовые су1-1маторы, пятый5 шестой, седьмой и восьт ой уси,п :,1тели-ограннчители.

514275566

liia i Gp по модулю два и четвертый двух-вых сумматоров через пятый, шестой,

разрядный регистр сдвига, выходыседьмой и восьмой усилители-огранипервого и второго разрядов которогочители соответственно подключены к

подключены к соответствующим входам ...соответствукщим входам сумматора по

блока постоянной памяти, первые входы юдулю два, выход которого подключен

йсех весовых сумг аторов объе,циненык информационному входу четвертого

и подключены к первому входу суммато- двухразрядного регистра сдвига, такptoBj вторые входы всек весовых cy яIa товьй вход которого объединен с такгоров обьединень и подклю тены к вто- ц ТОЕЪВД входом третьего двухразрядного

0oiviy входз; сумматораS выход первого,,регистра сдвига, второго5 третьего я четвертого 5зесо

Таблица I

11

О О О О 1 I 1 « 1 11

О О I 1 1 О О, О О1

О 11-00 I 1

Таблица 2

rf .. о « -a « гп «ft -y 7 Т О

t-

e № « tn- к (

lfa. t fi UV «в|/«-Л л .-в tj)

о (ft чО « г e -ff Л л « , ....( it-

- i M л «at «t -sf-

(ч. и W

I « ii« n.

e --T«J 7 о

S

(4 t« m t e в t e «Ч o « «

918

« «««. 63 «s Kj a e -:

tfl «S «Ч . e-

«-a 5

jrtsfj®is, .ф. M, Пъ.

II. Jfj ll fe

05 «S «- e Щ4 «. p О « 5 fj « n

I

P« vS B РГ c« e f«. л тЯ -f 14 .-S «

rt SJ S

« i«4 tn к tie tA %e G ()(II

-«I TttTt

(.

ЭТ « ч

. I

ё ё о ё) о

- 1 1 ч СЧ««Чв -

«©«.« (

(ч. и W e M - M

f «

e 4f tf%

.«. es e t « e sn 1 t Т I

n

I t

о «

f irt ff w о

1 (

i ®

Зое

5 S

Фуе.7

.

/

О

| Частотный дискриминатор | 1985 |

|

SU1396241A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-09-30—Публикация

1985-05-22—Подача