со со

Ci

ю

4:

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотный дискриминатор | 1985 |

|

SU1427556A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2006 |

|

RU2309430C1 |

| Дискриминатор нулевых биений | 1978 |

|

SU780154A1 |

| ЦИФРОВОЙ ФАЗОРАЗНОСТНЫЙ МАНИПУЛЯТОР | 2011 |

|

RU2450322C1 |

| Устройство для синхронного радиоприема частотно-манипулированных сигналов | 1986 |

|

SU1363517A2 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1996 |

|

RU2099739C1 |

| Устройство для моделирования нейрона | 1991 |

|

SU1831715A3 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ МГНОВЕННОЙ ЧАСТОТЫ | 1991 |

|

RU2022278C1 |

Изобретение относится к радиотехнике и может использоваться в устр-вах автоподстройки частоты, например в следящих измерителях доплеровских частот. Цель изобретения - повышение чувствительности. Устр-во содержит смесители 1, 2, фазовращатель 3 на л/2, фильтры нижних частот 4,,5, сумматор 6, вычитатель 7, усилители-ограничители , элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 12-14, двухразрядные регистры сдвига (PC) 15-17, трехразрядный сумматор 18, элементы ИЛИ 19, И. 20. Вся область углов разделена на 8 секторов. В результате работы блоков 8-14 на выходах блоков 8, 12, 14 формируется двоичный код, равный номеру сектора, которому соответствует мгновенное значение вектора X, у. Значение номера сектора записывается в первые разряды PC 15-17. Во вторых разрядах PC 15-17 хранится номер сектора из предшествующего отсчета времени. На основании кодов, сформированных PC 15-17, трехразрядный сумматор 18 и элементы ИЛИ 19 и И 20 вычисляют знак и величину приращения фазы с дискретностью до одного сектора. Для оценки приращения фазы используется усеченный двоичный код; сигнал переноса с сумматора 18 не используется, третий его разряд рассмат- риватся как знаковый. 2 ил., 2 табл. (Л

(раг.1

Изобретение относится к радиотехнике и может быть использовано в устройствах автоматической подстройки частоты, в частности в следящих измерителях доплеров- ских частот.

Цель изобретения - новышение чувствительности.

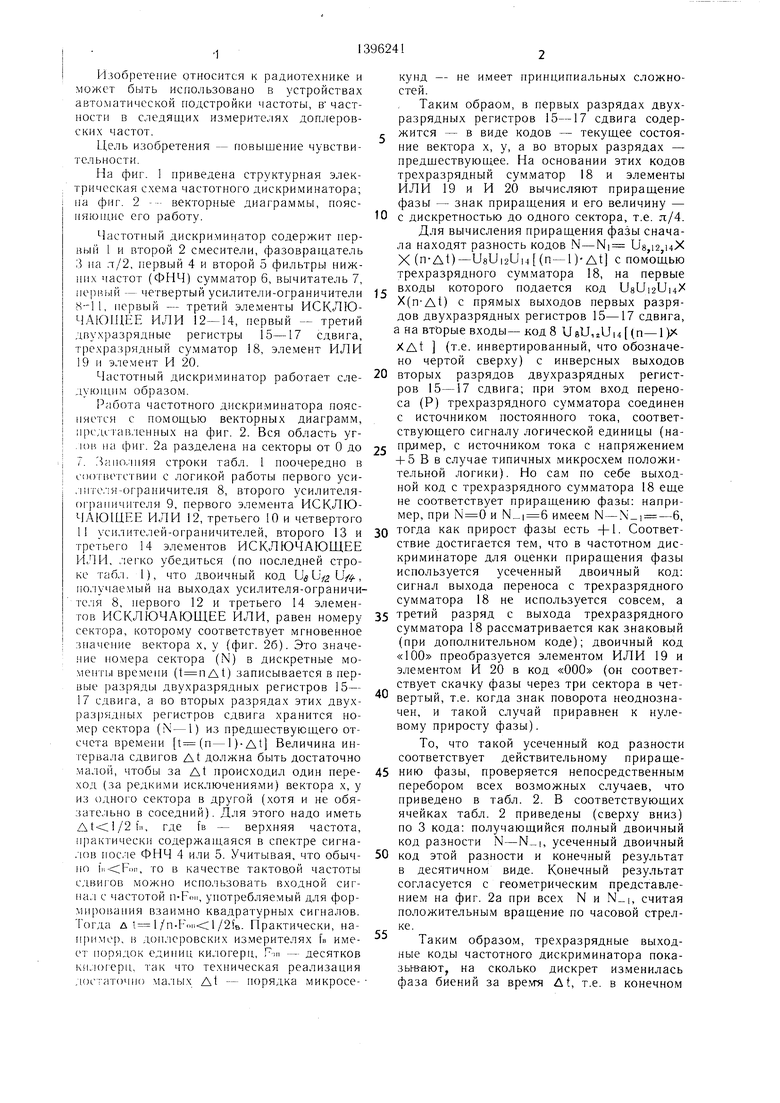

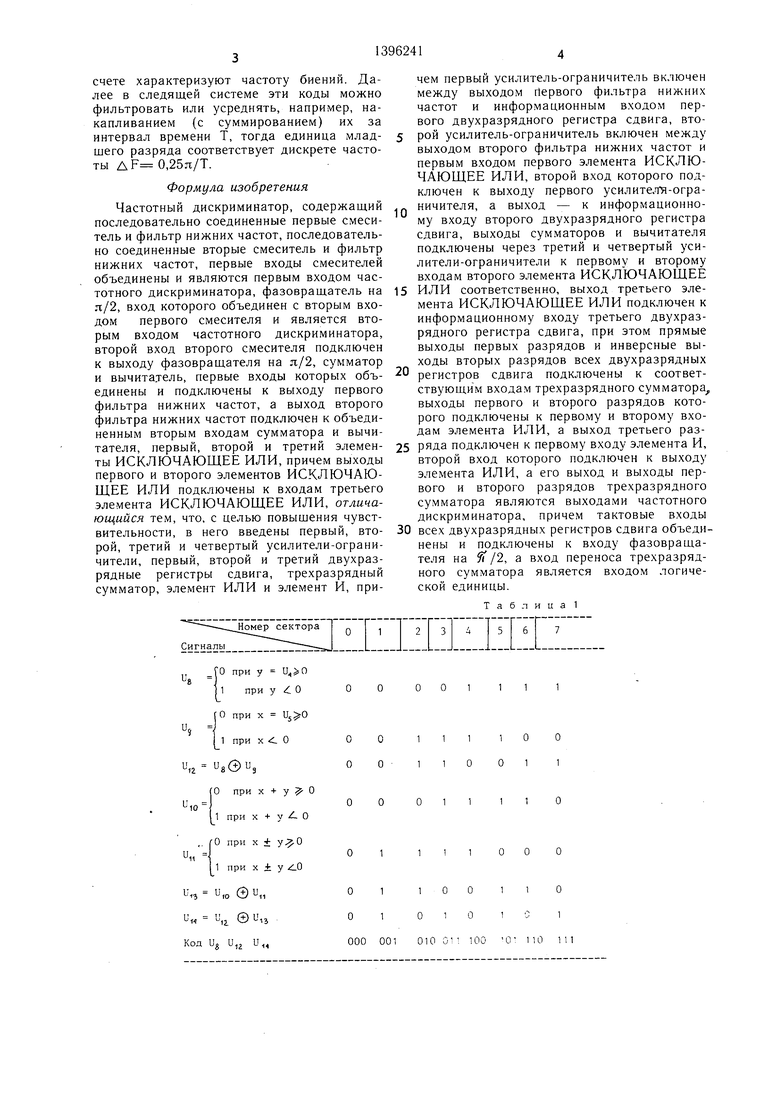

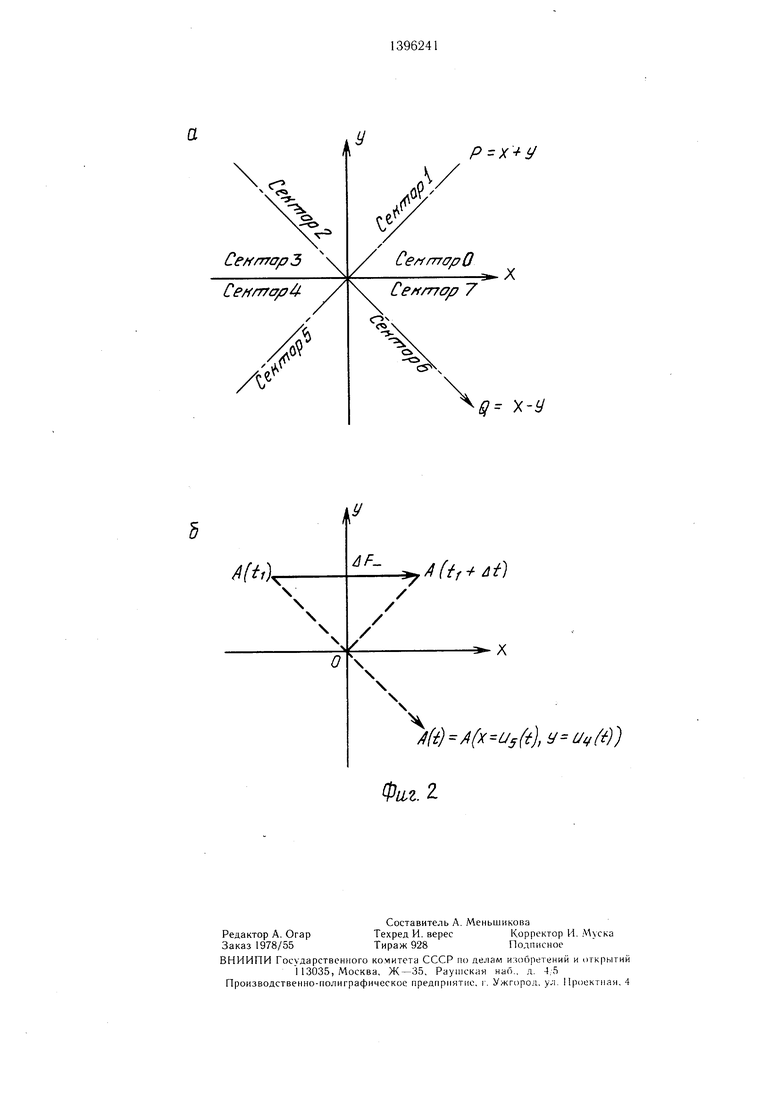

На фиг. 1 приведена структурная электрическая схема частотного дискриминатора; па фиг. 2 -- векторные диаграммы, поясняющие его работу.

Частотный дискриминатор содержит нер- вый 1 и второй 2 смесители, фазовращатель 3 на л/2, первый 4 и второй 5 фильтры нижних частот (ФНЧ) сумматор 6, вычитатель 7, первьп1 - четвертый усилители-ограничители S-11, первый - третий элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 12-14, первый - третий дву.хразрядпые регистры 15-17 сдвига, тре.раз|)ядный су.мматор 18, эле.мент ИЛИ 19 и элемент И 20.

Частотный дискриминатор работает следующим образом.

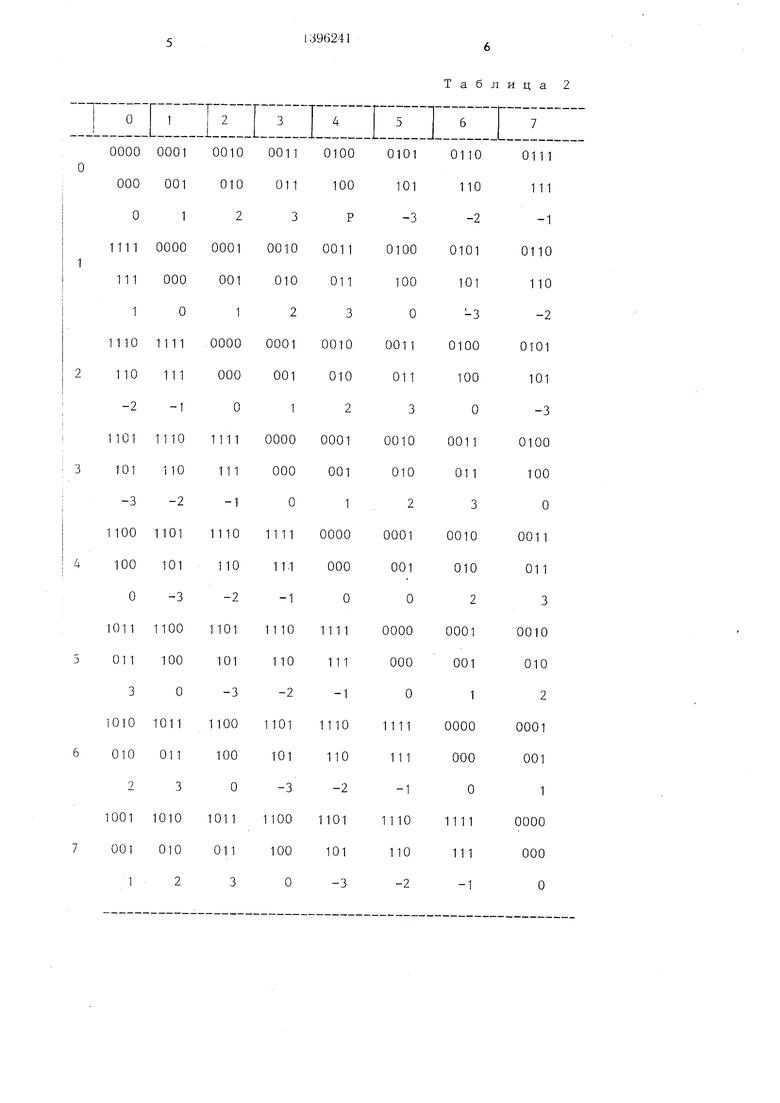

Работа частотного дискриминатора поясняется с помощью векторных диаграмм, представленных на фиг. 2. Вся область уг- ,к)в на фнг. 2а разделена на секторы от О до 7. ..-щяя строки табл. 1 поочередно в cooTiiCTCTBHH с логикой работы первого уси- ,|птс.1нч)граничителя 8, второго усилителя- огра11ИЧ1ггеля 9, первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12, третьего 10 и четвертого 11 усилителей-ограничителей, второго 13 и третьего 14 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, легко убедиться (по последней строке табл. 1), что двоичный код .-, по.чучаемый па выходах усилителя-ограничителя 8, первого 12 и третьего 14 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, равен номеру сектора, которому соответствует мгновенное значение вектора х, у (фиг. 26). Это значение номера сектора (N) в дискретные мо- меп П) времени () записывается в первые |)аз)яды двухразрядных регистров 15- 17 сдвига, а во вторых разрядах этих двух- раз|)ядных регистров сдвига хранится помер сектора (N - 1) из предществующего отсчета времени t (п-l)-At Величина интервала сдвигов At должна быть достаточно малой, чтобы за At происходил один переход (за редкими исключениями) вектора х, у из с)дного сектора в другой (хотя и не обязательно в соседний). Для этого надо иметь At ;l/2fn, ГлТе в - верхняя частота, практически содержавшаяся в спектре сигна- . юв пос.пе ФНЧ 4 или 5. Учитывая, что обычно , то в качестве тактовой частоты сдвиг ов можно использовать входной сигнал с частотой ii-F oii, употребляемый для формирования взаимно квадратурных сигналов. Тогда д t 1/п-Е 11 ; . Ирактически, на- нримо), к донлеровских измерителях в имеет порядок единиц килогерп, Г)м - десятков килогерц, так что техническая реализация достаточно ма.чых At - порядка микросе-

кунд - не имеет принципиальных сложностей.

Таким обраом, в первых разрядах двухразрядных регистров 15-17 сдвига содер- жится - в виде кодов - текущее состояние вектора х, у, а во вторых разрядах - предществующее. На основании этих кодов трехразрядный сумматор 18 и элементы ИЛИ 19 и И 20 вычисляют приращение фазы - знак приращения и его величину -

0 с дискретностью до одного сектора, т.е. л/4. Для вычисления приращения фазы сначала находят разность кодов U8,i2,i4X X (п-At)-U8Ui2Ui4(n-) At с помощью трехразрядного сум.матора 18, на первые

г входы которого подается код U8Ui2Ui4X X(n-At) с прямых выходов первых разрядов двухразрядных регистров 15-17 сдвига, а на вторые входы-код 8 U8U,iUi4 (п-1)Х XAt (т.е. инвертированный, что обозначено чертой сверху) с инверсных выходов

0 вторых разрядов двухразрядных регистров 15-17 сдвига; при этом вход переноса (Р) трехразрядного сумматора соединен с источником постоянного тока, соответствующего сигналу логической единицы (на5 прлмер, с источником тока с напряжением + 5 В в случае типичных микросхем положительной логики). Но сам по себе выходной код с трехразрядного сумматора 18 еще не соответствует приращению фазы: например, при и имеем -6,

0 тогда как прирост фазы есть -fl. Соответствие достигается тем, что в частотном дискриминаторе для оценки приращения фазы используется усеченный двоичный код: сигнал выхода переноса с трехразрядного сумматора 18 не используется совсем, а

5 третий разряд с выхода трехразрядного сумматора 18 рассматривается как знаковый (при дополнительном коде); двоичный код «100 преобразуется элементом ИЛИ 19 и элементом И 20 в код «000 (он соответствует скачку фазы через три сектора в чет вертый, т.е. когда знак поворота неоднозначен, и такой случай приравнен к нулевому приросту фазы).

То, что такой усеченный код разности соответствует действительному прираще5 нию фазы, проверяется непосредственным перебором всех возможных случаев, что приведено в табл. 2. В соответствующих ячейках табл. 2 приведены (сверху вниз) по 3 кода: получающийся полный двоичный код разности , усеченный двоичный

0 код этой разности и конечный результат в десятичном виде. Конечный результат согласуется с геометрическим представлением на фиг. 2а при всех N и , считая положительным вращение по часовой стрелке.

Таким образом, трехразрядные выходные коды частотного дискриминатора пока- зь№ают, на сколько дискрет изменилась фаза биений за врем At, т.е. в конечно.м

счете характеризуют частоту биений. Далее в следящей системе эти коды можно фильтровать или усреднять, например, накапливанием (с суммированием) их за интервал времени Т, тогда единица младшего разряда соответствует дискрете частоты ДР 0,25л/Т.

Формула изобретения

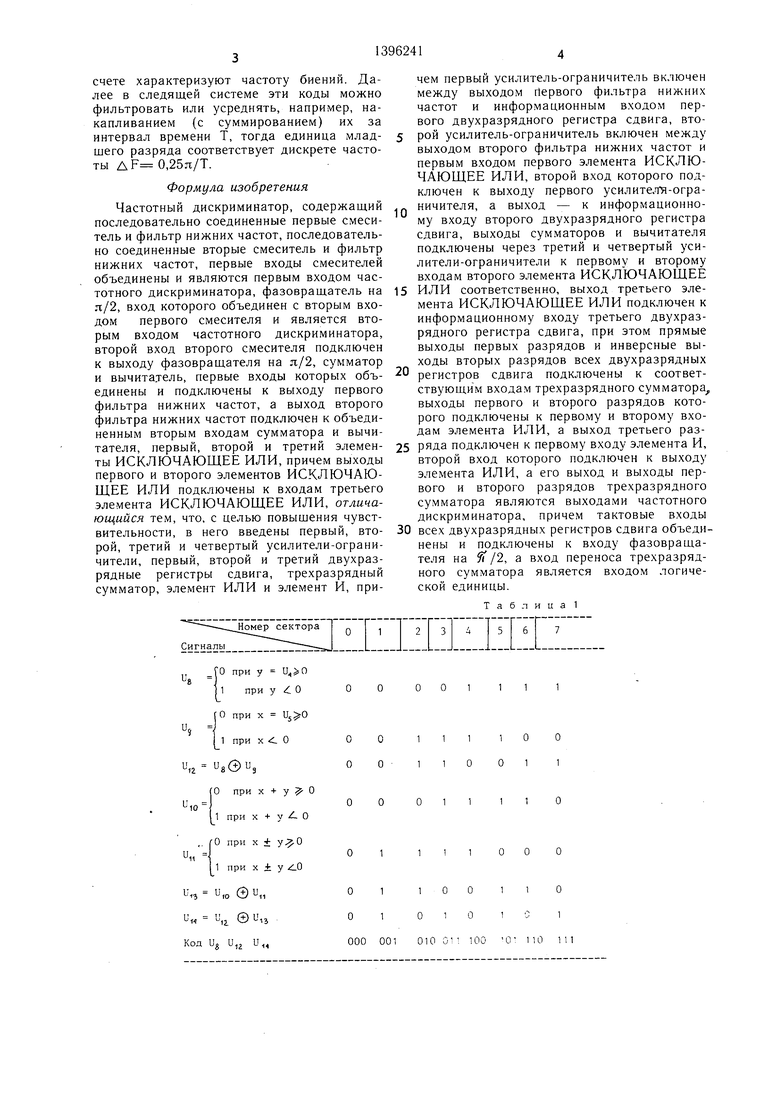

Частотный дискриминатор, содержащий последовательно соединенные первые смеситель и фильтр нижних частот, последовательно соединенные вторые смеситель и фильтр нижних частот, первые входы смесителей объединены и являются первым входом частотного дискриминатора, фазовращатель на л/2, вход которого объединен с вторым входом первого смесителя и является вторым входом частотного дискриминатора, второй вход второго смесителя подключен к выходу фазовращателя на л;/2, сумматор и вычитатель, первые входы которых объединены и подключены к выходу первого фильтра нижних частот, а выход второго фильтра нижних частот подключен к объединенным вторым входам сумматора и вычи- тателя, первый, второй и третий элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выходы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к входам третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, отличающийся тем, что, с целью повышения чувствительности, в него введены первый, второй, третий и четвертый усилители-ограничители, первый, второй и третий двухразрядные регистры сдвига, трехразрядный сумматор, элемент ИЛИ и элемент И, приСигналы

О

О

О

О

1

о

0110011

01010101

000 001 010011 100 ЧТ 110 111

0

чем первый усилитель-ограничитель включен между выходом rtepBoro фильтра нижних частот и информационным входом первого двухразрядного регистра сдвига, второй усилитель-ограничитель включен между выходом второго фильтра нижних частот и первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу первого усилителтч-огра- ничителя, а выход - к информационному входу второго двухразрядного регистра сдвига, выходы сумматоров и вычитателя подключены через третий и четвертый усилители-ограничители к первому и второму входам второго элемента ИСКЛЮЧАЮЩЕЕ

5 ИЛИ соответственно, выход третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к информационному входу третьего двухразрядного регистра сдвига, при этом прямые выходы первых разрядов и инверсные выходы вторых разрядов всех двухразрядных регистров сдвига подключены к соответствующим входам трехразрядного сумматора выходы первого и второго разрядов которого подключены к первому и второму входам элемента ИЛИ, а выход третьего раз5 ряда подключен к первому входу элемента И, второй вход которого подключен к выходу элемента ИЛИ, а его выход и выходы первого и второго разрядов трехразрядного сумматора являются выходами частотного дискриминатора, причем тактовые входы

0 всех двухразрядных регистров сдвига объединены и подключены к входу фазовращателя на /2, а вход переноса трехразрядного сумматора является входом логической единицы.

Таблица 1

0

001111

111100

110011

Oil11о

о

а

Л

М

p x-i-y

х

Q

A(

ч

/i(i)A((f),)

| Патент США № 4338574, кл | |||

| Накладной висячий замок | 1922 |

|

SU331A1 |

Авторы

Даты

1988-05-15—Публикация

1985-04-26—Подача