Изобретение относится к технике связи и может быть использовано для помехоуЪтойчивого выделения синхросигналов и сигналов фазового пуска аппаратуры двоичной информации.

Цель изобретения - повьшение помехоустойчивости приема сигналов начальной синхронизации,

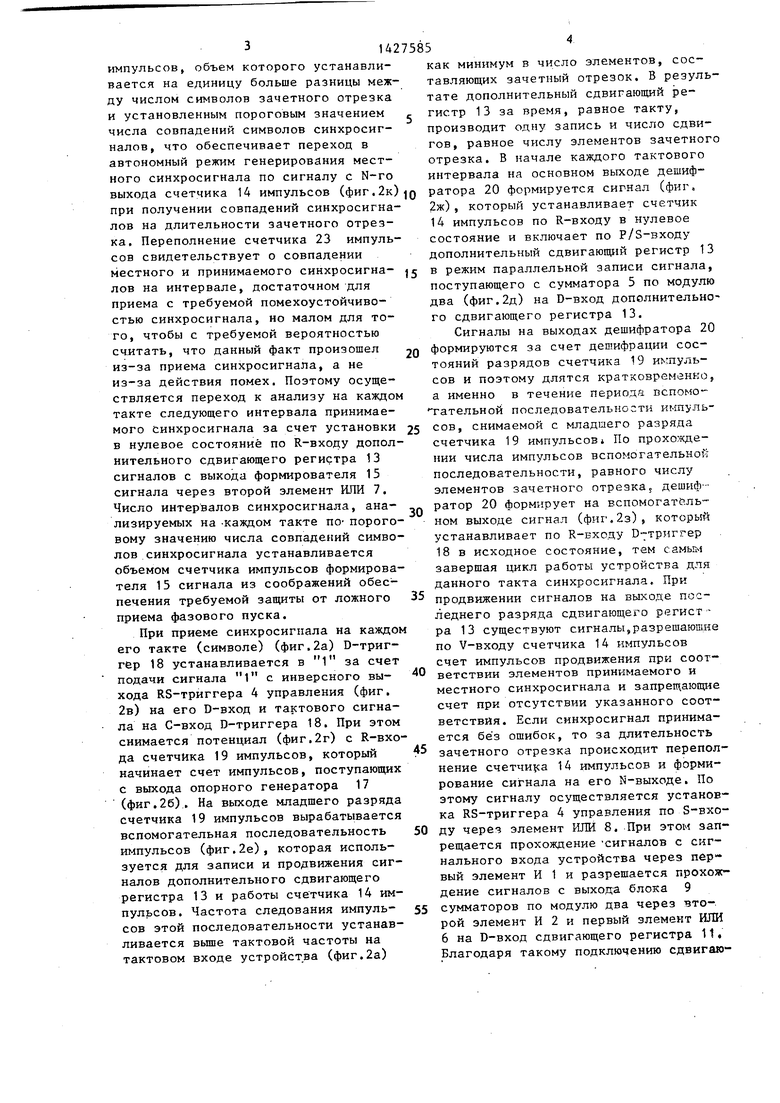

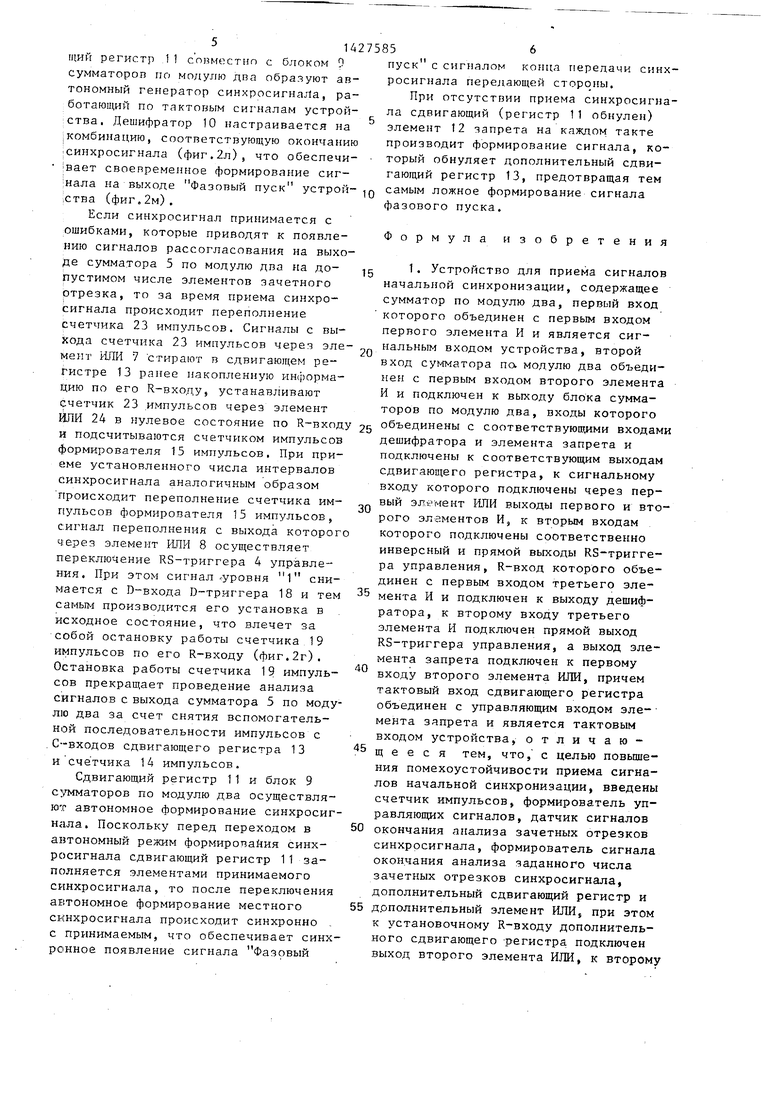

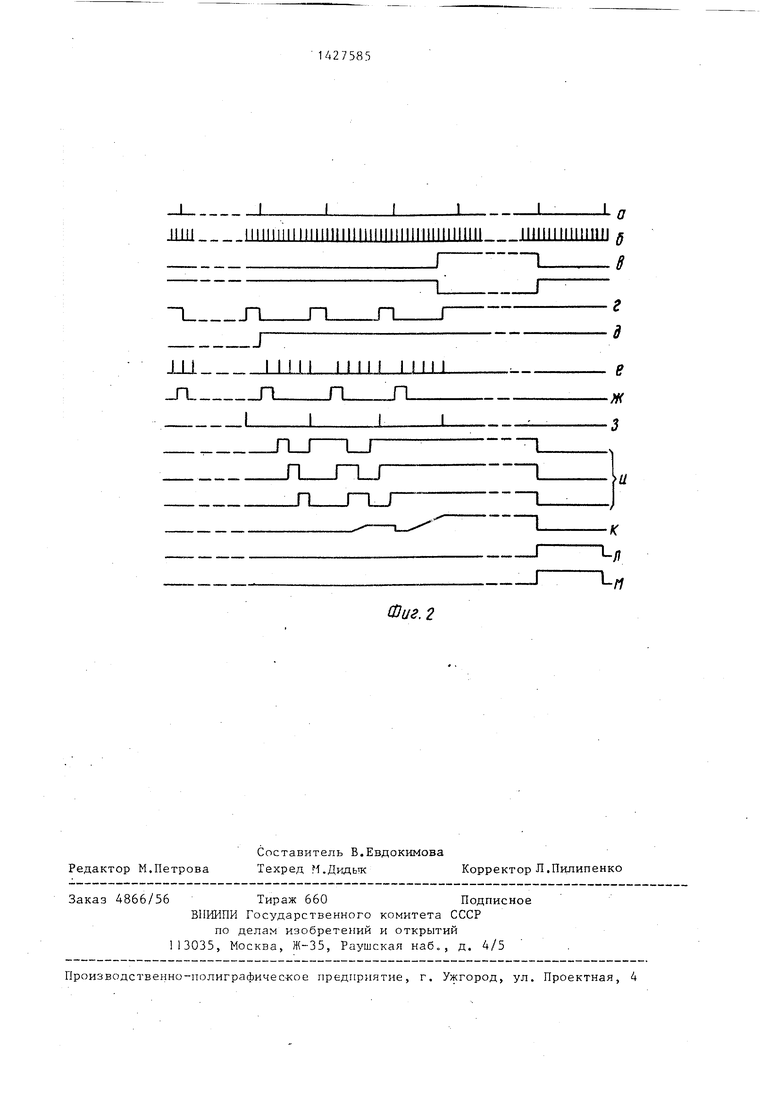

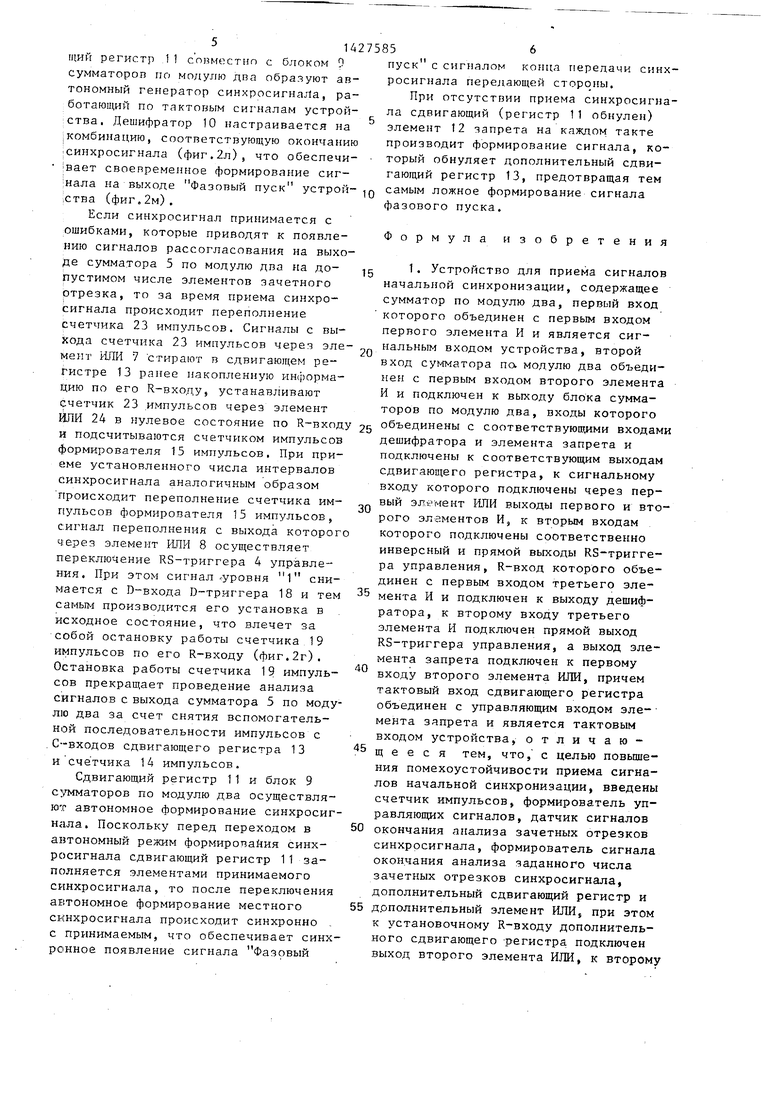

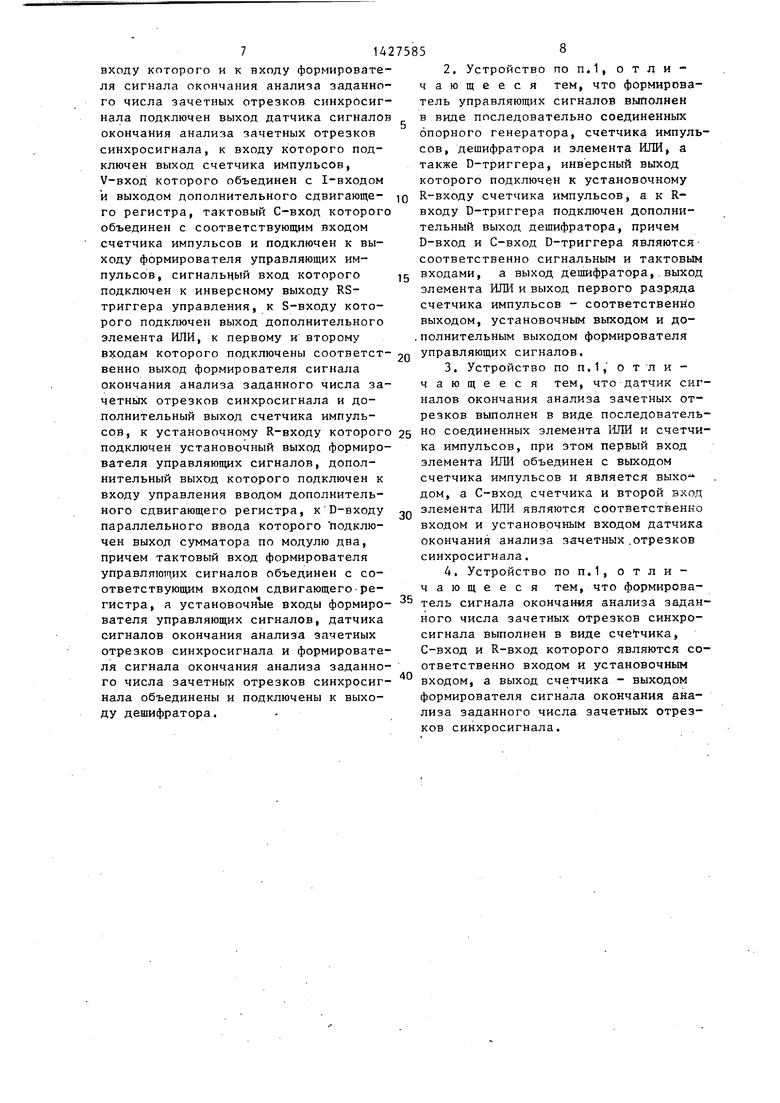

На фиг.1 представлена структурная электрическая схема устройства для приема сигналов начальной синхронизации; на фиг,2 - временные диаграммы сигналов, поясняющие работу устройства,

Устройство для приема сигналов на- :чальной синхронизации содержит пер- 1ВЫЙ, второй и третий элементы И 1, 2 и 3, RS-триггер 4 управления, сумматор 5 по модулю два, первый, второй и дополнительный элементы ИЛИ 6, 7 и 8, блок 9 .с сумматоров по модулю два, дешифратор 10, сдвигающий регистр 11, элемент 12 запрета, дополнительный сдвигающий регистр 13, счетчик 14 импульсов, формирователь 15 сигнала окончания анализа заданного числа зачетных отрезков синхросигнала, выполненный в виде счетчика

импульсов, формирователь 16 управляю- о синхросигнала. Если при дальнейшем

(фиг.2д) в отдельные разряды дополнительного сдвигающего регистра 13 и последующего анализа записанной в этот регистр последовательности путем определения числа совпадающих симво- лов принимаемого и местного синхросигналов на интервале зачетного отрезка. Осуществляется такой анализ на каждом тактовом интервале принимаемого синхросигнала за счет продвижения записанных в дополнительный сдвигающий регистр 13 сигналов (фиг,2и) со скоростью выше скорости поступления символов принимаемого синхросигнала и подсчета счетчиком 14 импульсов импульсов продвижения, на которые в разрядах дополнительного сдвигающего регистра 13 существуют сигналы совпадения символов местного и принимаемого синхросигналов. При достижении порогового значения числа совпадений символов синхросигналов формируется сигнал на R-выходе счетчика 14 импульсов и анализ продолжается дальше,Указанное пороговое значение числа совпадений символов синхросигналов устанавливается из соображений обеспечения приема с требуемой помехоустойчивостью

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазового пуска | 1984 |

|

SU1225035A1 |

| Система передачи и приема информации рекуррентными последовательностями | 1985 |

|

SU1338101A1 |

| УСТРОЙСТВО ФАЗОВОГО ПУСКА | 2002 |

|

RU2240655C2 |

| УСТРОЙСТВО ФАЗОВОГО ПУСКА РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТЬЮ | 1996 |

|

RU2109407C1 |

| Устройство для передачи и приема сигналов начальной синхронизации | 1987 |

|

SU1543559A1 |

| Система передачи дискретной информации | 1985 |

|

SU1325719A1 |

| УСТРОЙСТВО ФАЗОВОГО ПУСКА | 1995 |

|

RU2115248C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ МАТРИЧНОЙ ОБРАБОТКИ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2803318C1 |

Изобретение относится к технике связи. Цель изобретения - повышение помехоустойчивости приема сигналов начальной синхронизации. Устр-во содержит эл-ты И 1, 2 и 3,. RS-триггер 4 управления, сумматор 5 -по модулю два, эл-ты ИЛИ 6, 7 и 8, блок 9 сумматоров по модулю два, дешифратор 10, сдвигающие регистры 11 и 13, эл-т запрета 12, счетчик 14 импульсов, формирователь 15 сигнала окончания анализа заданного числа зачетных отрезков синхросигнала, формирователь 16 управляющих сигналов и датчик 22 сигналов окончания анализа зачетных отрезков синхросигнала. Цель достигается путем предотвращения ложного формирования сигнала Фазовый пуск с помощью введенных эл-та ИЛИ 8, регистра 13, счетчика 14, формирователя 15 и 16 и датчика 22. Устр-во по п,п. 2, 3 и 4 отличается выполнением формирователей 15 и 16 и датчика 22. 3 3 . fi. Ь1, 2 ил. Фазо&ый пуск а 00 О1

от- 35

щих сигналов, в состав которого входят опорный генератор 17, D-триггер 18, счетчик 19 импульсов, дешифратор 20 и элемент ИЛИ 21, и датчик 22 сигналов окончания анализа зачетных резков синхросигнала, в состав кото рого входят счетчик 23 импульсов и элемент ИЛИ 24.

Устройство для приема сигналов начальной синхронизации работает следующим образом.

При включении устройства RS-триггер 4 управления устанавливается в исходное состояние, при этом потенциалом уровня 1 с его инверсного вы40

анализе оказывается, что число совпа-. дающих символов выше порога и равно числу символов зачетного отрезка, то устройство переключается в режим автономного генерирования местного синхросигнала за счет переключения D-входа сдвигающего регистра 11 от входа, устройства на выход блока 9 сумматоров по модулю два. Сигнал переключения поступает с N-ro выхода счетчика 14 импульсов (фиг.2к) на S-вход RS-триггера 4 управления через дополнительный элемент ИЛИ 8, .Цлина за четного отрезка устанавливается из соображений обеспечения требуемой

хода.(фиг,2в) обеспечивается поступ- защиты от ложных наборов синхросигиаЛение принимаемых символов синхросигнала через первый элемент И 1 и первый элемент ИЛИ 6 на D-вход сдвигающего регистра 11. По значениям сигналов разрядов сдвигающего регистра 11 блоком 9 сумматоров вырабатываются символы местного синхросигнала, которые сравниваются со значениями символов принимаемого синхросигнала в сумматоре 5 по модулю два. Затем произ- водится последовательная запись результатов сравнения каждого символа принимаемого и местного синхросигнала

анализе оказывается, что число совпа-. дающих символов выше порога и равно числу символов зачетного отрезка, то устройство переключается в режим автономного генерирования местного синхросигнала за счет переключения D-входа сдвигающего регистра 11 от входа, устройства на выход блока 9 сумматоров по модулю два. Сигнал переключения поступает с N-ro выхода счетчика 14 импульсов (фиг.2к) на S-вход RS-триггера 4 управления через дополнительный элемент ИЛИ 8, .Цлина за четного отрезка устанавливается из соображений обеспечения требуемой

защиты от ложных наборов синхросигиала. По окончании периода ген-ерирова- ния местного синхросигнала дешифратор 10 формирует сигнал (фиг.2л), который через третий элемент И 3 поступает на выход Фазовый пуск устройства (фиг.2м). Если при анализе оказывается, что число совпадающих символов вьше порога, но меньше числа символов зачетного отрезка, то осуществляется анализ на последующих тактах принима-, емого синхросигнала. Сигналы с Р-вы- хода счетчика 14 импульсов в этом случае подсчитываются счетчиком 23

импульсов, объем которого устанавливается на единицу больше разницы между числом символов зачетного отрезка и установленным пороговым значением числа совпадений символов синхросигналов, что обеспечивает переход в автономный режим генерирования местного синхросигнала по сигналу с N-ro выхода счетчика 14 импульсов (фиг.2к) при получении совпадений синхросигналов на длительности зачетного отрезка. Переполнение счетчика 23 импульсов свидетельствует о совпадении местного и принимаемого синхросигна- лов на интервале, достаточном для приема с требуемой помехоустойчивостью синхросигнала, но малом для то- то, чтобы с требуемой вероятностью считать, что данный факт произошел из-за приема синхросигнала, а не из-за действия помех. Поэтому осуществляется переход к анализу на каждом такте следующего интервала принимаемого Синхросигнала за счет установки в нулевое состояние по R-входу дополнительного сдвигающего регистра 13 сигналов с выхода формирователя 15 сигнала через второй элемент ИЛИ 7. Число интервалов синхросигнала, анализируемых на -каждом такте по- пороговому значению числа совпадений символов синхросигнала устанавливается объемом счетчика импульсов формирователя 15 сигнала из соображений обеспечения требуемой защиты от ложного приема фазового пуска.

При приеме синхросигнала на каждом его такте (символе) (фиг.2а) D-триг- гер 18 устанавливается в 1 за счет подачи сигнала 1 с инверсного вы- хода RS-триггера 4 управления (фиг, 2в) на его D-вход и тактового сигнала на С-вход D-триггера 18. При этом снимается потенциал (фиг.2г) с R-BXO

да счетчика 19 импульсов, который начинает счет импульсов, поступающих с выхода опорного генератора 17 (фиг.26), На выходе младшего разряда счетчика 19 импульсов вырабатывается вспомогательная последовательность импульсов (фиг.2е), которая используется для записи и продвижения сигналов дополнительного сдвигающего регистра 13 и работы счетчика 14 импульсов. Частота следования импульсов этой последовательности устанавливается Bbmie тактовой частоты на тактовом входе устройства (фиг.2а)

0 j п 5 5

0

0

5

0

5

как минимум в число элементов, составляющих зачетный отрезок. В результате дополнительный сдвигающий регистр 13 за время, равное такту, производит одну запись и число сдвигов, равное числу элементов зачетного отрезка. В начале каждого тактового интервала на основном выходе дешифратора 20 формируется сигнал (фиг, 2ж), который устанавливает счетчик 14 импульсов по К-входу в нулевое состояние и включает по P/S-входу дополнительный сдвигающий регистр 13 в режим параллельной записи сигнала, поступающего с сумматора 5 по модулю два (фиг.2д) на D-вход дополнительного сдвигающего регистра 13.

Сигналы на выходах дешифратора 20 формируются за счет дешифрации состояний разрядов счетчика 19 икпуль- сов и поэтому длятся кратковременно, а именно в течение периода вспомо- Тательной последовательности импульсов, снимаемой с младшего разряда счетчика 19 импульсов По прохождении числа импульсов вспомогательной последовательности, равного числу элементов зачетного отрезка, дешифратор 20 формирует на вспомогатйль™ ном выходе сигнал (фиг.2з), который устанавливает по R-БХоду В- триггер 18 в исходное состояние, тем самьм завершая цикл работы устройства для данного такта синхросигнала. При продвижении сигналов на выходе последнего разряда сдвигающех- о регист-- ра 13 существуют сигналы,разрешающие по V-входу счетчика 14 импульсов счет импульсов продвижения при соответствии элементов принимаемого и местного синхросигнала и запрещающие счет при отсутствии указанного соответствия. Если синхросигнал принимается без ошибок, то за длительность зачетного отрезка происходит переполнение счетчи са 14 импульсов и формирование сигнала на его N-выходе. По этому сигналу осуществляется установка RS-триггера 4 управления по S-BXO- ду через элемент ИЛИ 8. При этом запрещается прохождение сигналов с скг нального входа устройства через пер вый элемент И 1 и разрешается прохож дение сигналов с выхода блока 9 сумматоров по модулю два через второй элемент И 2 и первый элемент ИЛИ 6 на D-вход сдвигающего регистра 11, Благодаря такому подключению сдвигающий регистр 1 1 coBNfecTHn с блоком 9 сумматоров по модулю два образуют автономный генератор синхросигнала, работающий по тактог ым сиг налам устрой- :ства, Дешифратор 10 настраивается на ;комбинацию, соответствующую окончанию :синхросигнала (фиг.2л), что обеспечи- :вает своепременное формирование сиг- нала на выходе Фазовый пуск устрой- iCTBa (фиг. 2м) .

Если синхросигнал принимается с ошибками, которые приводят к появлению сигналов рассогласования на выходе сумматора 5 по модулю два на допустимом числе элементов зачетного отрезка, то за время приема синхросигнала происходит переполнение счетчика 23 импульсов. Сигналы с выхода счетчика 23 импульсов через элемент ИЛИ 7 стирают в сдвигающем регистре 13 ранее накопленную ин(рорма- цию по его R-входу, устанав гивают счетчик 23 импульсов через элемент

ИЛИ 24 в нулевое состояние по R-входу 25 объединены с соответствуюгцими входами

и подсчитываются счетчиком импульсов формирователя 15 импульсов. При приеме установленного числа интервалов синхросигнала аналогичным образом происходит переполнение счетчика импульсов формирователя 15 импульсов, сигнал переполнения с выхода которого ч;ерез элемент ИЛИ 8 осуществляет переключение RS-триггера 4 управления. При этом сигнал .уровня 1 сни30

дешифратора и элемента запрета и подключены к соответствующим выходам сдвигающего регистра, к сигнальному входу которого подключены через первый элемент ИЛИ выходы первого и вто рого элементов И, к вторым входам . которого подключены соответственно инверсный и прямой выходы RS-триггера управления, R-вход которого объединен с первым входом третьего элемается с D-входа D-триггера 18 и тем мента И и подключен к выходу дешифсамым производится его установка в исходное состояние, что влечет за собой остановку работы счетчика 19 импульсов по его R-входу (фиг.2г). Остановка работы счетчика 19 импульсов прекращает проведение анализа сигналов с выхода сумматора 5 по модулю два за счет снятия вспомогательной последовательности импульсов с С-входов сдвигающего регистра 13 и сче тчика 14 импульсов.

Сдвигающий регистр 11 и блок 9 с; д шаторов по модулю два осуществляют автономное формирование синхросигнала. Поскольку перед переходом в автономный режим формировайия синхросигнала сдвигающий регистр 11 заполняется элементами принимаемого синхросигнала, то после переключения автономное формирование местного синхросигнала происходит синхронно . с принимаемым, что обеспечивает синхронное появление сигнала Фазовый

5

0

пуск с сигналом конца передачи синхросигнала передающей cTopqiibi.

При отсутствии приема синхросигнала сдвигающий (регистр 11 обнулен) элемент 12 запрета на каждом такте производит формирование сигнала, который обнуляет дополнительный сдвигающий регистр 13, предотвращая тем самым ложное формирование сигнала фазового пуска.

Формула изобретения

0

дешифратора и элемента запрета и подключены к соответствующим выходам сдвигающего регистра, к сигнальному входу которого подключены через первый элемент ИЛИ выходы первого и второго элементов И, к вторым входам . которого подключены соответственно инверсный и прямой выходы RS-триггера управления, R-вход которого объединен с первым входом третьего эле0

5

ратора, к второму входу третьего элемента И подключен прямой выход RS-триггера управления, а выход элемента запрета подключен к первому входу второго элемента ИЛИ, причем тактовый вход сдвигающего регистра объединен с управляющим входом эле- мента запрета и является тактовьм входом устройства, отличающееся тем, что, с целью повышения помехоустойчивости приема сигналов начальной синхронизации, введены счетчик импульсов, формирователь управляющих сигналов, датчик сигналов окончания анализа зачетных отрезков синхросигнала, формирователь сигнала окончания анализа заданного числа зачетных отрезков синхросигнала, дополнительный сдвигающий регистр и 5 дополнительный элемент ИЛИ, при этом к установочному R-входу дополнительного сдвигающего -регистра подключен выход второго элемента ИЛИ, к второму

0

714

входу которого и к входу формирователя сигнала окончания анализа заданного числа зачетных отрезков синхросигнала подключен выход датчика сигналов окончания анализа зачетных отрезков синхросигнала, к входу которого подключен выход счетчика импульсов, V-вход которого объединен с 1-входом и выходом дополнительного сдвигающего регистра, тактовый С-вход которого объединен с соответствующим входом счетчика импульсов и подключен к выходу формирователя управляющих импульсов, сигнальный вход которого подключен к инверсному выходу RS- триггера управления, к S-входу которого подключен выход дополнительного элемента ИЛИ, к первому и второму входам которого подключены соответственно выход формирователя сигнала окончания анализа заданного числа зачетных отрезков синхросигнала и дополнительный выход счетчика импуль

сов, к установочному R-входу которого 25 ° соединенных элемента IfflH и счетчи- подключен установочный выход формирователя управляющих сигналов, дополнительный выход которого подключен к входу управления вводом дополнительного сдвигающего регистра, K D-входу параллельного ввода которого подключен выход сумматора по модулю два, причем тактовый вход формирователя управляющих сигналов объединен с соответствующим входом сдвигающегоре30

ка импульсов, при этом первый вход элемента ИЛИ объединен с выходом счетчика импульсов и является выхо дом, а С-вход счетчика и второй вход элемента ИЛИ являются соответственно входом и установочным входом датчика окончания анализа зачетных .отрезков синхросигнала.

сигналов окончания анализа зачетных отрезков синхросигнала и формирователя сигнала окончания анализа заданного числа зачетных отрезков синхросигнала объединены и подключены к выходу дешифратора.

40

5

0

в виде последовательно соединенных опорного генератора, счетчика импульсов, дешифратора и элемента ИЛИ, а также D-триггера, инверсный выход которого подключен к установочному R-Бходу счетчика импульсов, а к R- входу D-триггера подключен дополнительный выход дешифратора, причем D-вход и С-вход D-триггера являются- соответственно сигнальным и тактовым входами, а выход дешифратора,.выход элемента ИЛИ и выход первого разряда счетчика импульсов - соответственно выходом, установочным выходом и дополнительным выходом формирователя управляющих сигналов.

ка импульсов, при этом первый вход элемента ИЛИ объединен с выходом счетчика импульсов и является выхо ом, а С-вход счетчика и второй вход элемента ИЛИ являются соответственно входом и установочным входом датчика окончания анализа зачетных .отрезков синхросигнала.

40

IIHIninilllllllllllllllllllllHIIIIIIIIIIIIIIIIIllinilllllinil я

--- -

-I

L

L

u

Ч T-/f

(Пиг.2

| Устройство фазового пуска | 1984 |

|

SU1225035A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Мартынов .Е-.М | |||

| Синхронизация в системах передачи дискретных сообщений | |||

| М.: Связь, 1972, с.200, рис.11 | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-09-30—Публикация

1986-11-17—Подача