1338

блок 4 сумматоров по модулю два, передающий п-разрядный регистр 5 сдвига, генератор 6 тактовьк импульсов, элементы ИЛИ 7, 8, п-канальный муль- I типлексор 9, RS-триггер 10 режима передачи, счетчик 11 циклов, выделитель 12 фронта, дополнительный блок 13 сумматоров по модулю два, дешифратор 1А нулевого состояния регистра, а на приемной стороне - демодулятор 15, п-разрядный регистр 16 сдвига, основной приемный блок 17 сумматоров по модулю два, приемный дешифратор 18

1

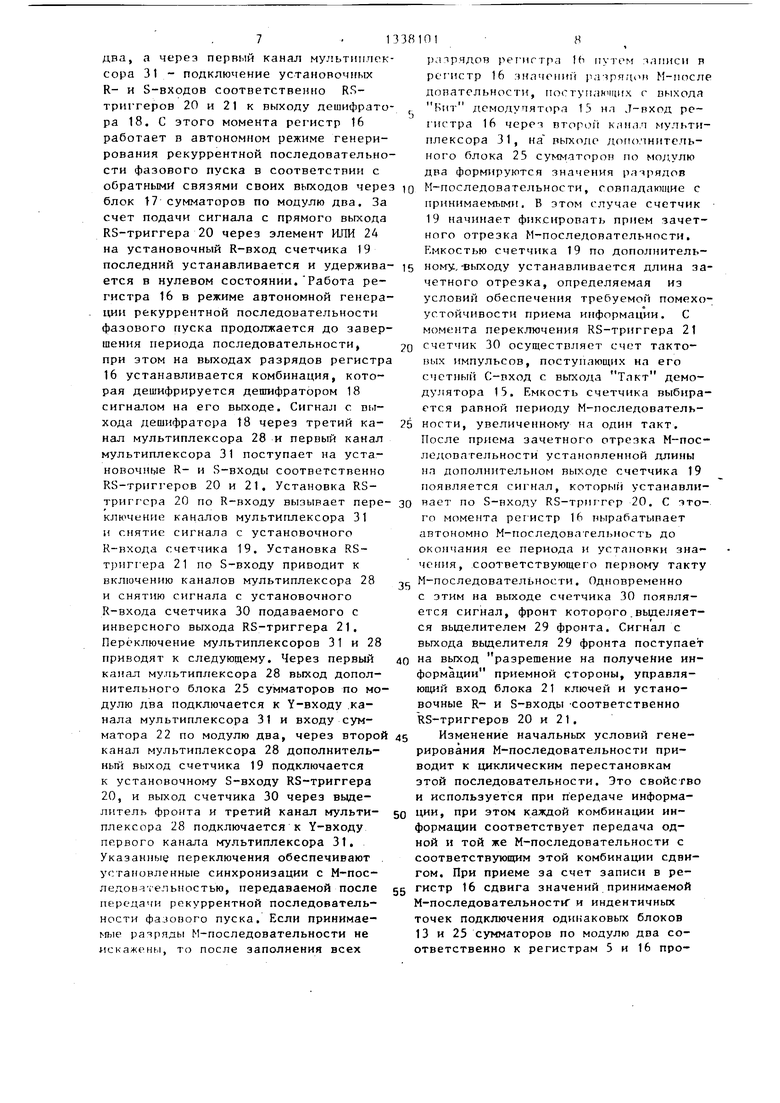

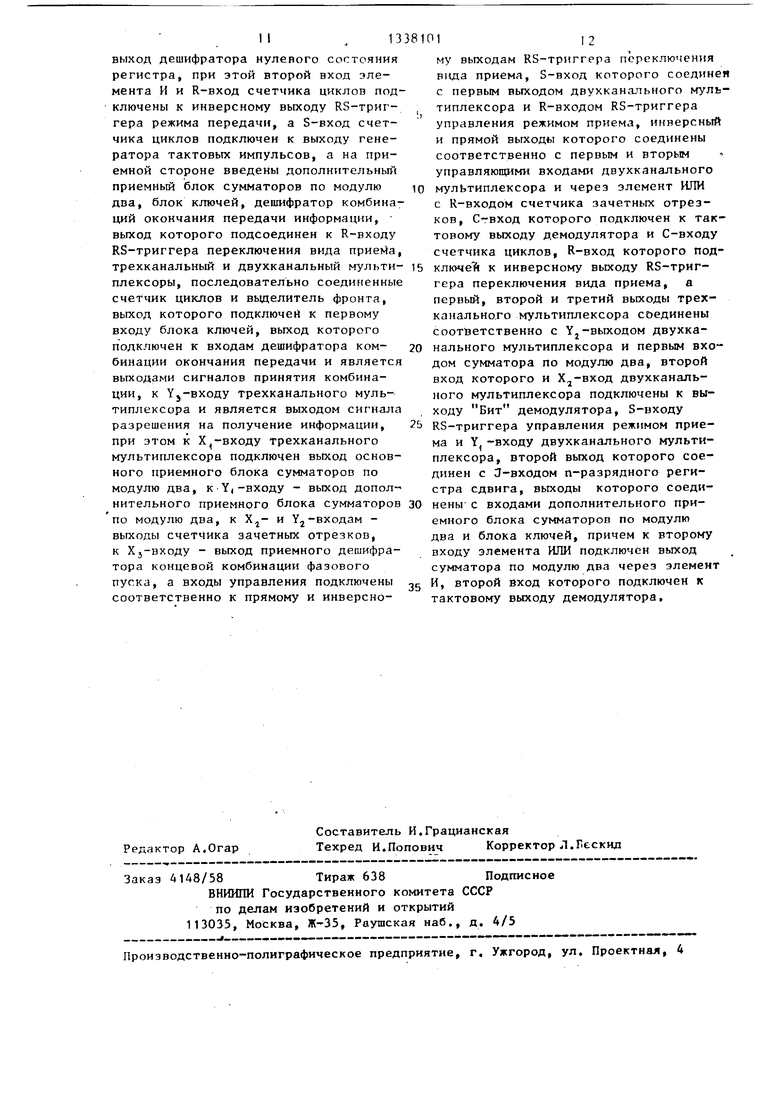

Изобретение относится к технике передачи дискретной информации и может быть применено для сеансной передачи дискретной информации.

Цель изобретения - повышение помехоустойчивости системы.

На черго.же представлена структурная элекгрическая схема системы.

CHL; гема передачи и приема информации рекуррентн 1мл последовательностями С(дс-ржит на передающий стороне элемент 1 И, КЯ-триггер 2 управления дешифратор 3, основной блок 4 сумматоров по модулю два, передающий разрядньи регистр 5 сдвига, генератор 6 тактоньгх импульсов, первый элемент ИЛИ 7, второй -элемент ИЛИ 8, п-канальный мультиплексор 9, RS-триггер 10 режима передачи, счетчик 11 циклов, выделитель 12 фронта, дополнительный блок 13 сумматоров по модулю два и дешифратор 14 нулевого состояния регистра, а на приемной стороне- демодулятор 15, п-разрядный регистр 16 сдвига, основной приемный блок 17 сумматоров по модулю два, приемный дешифратор 18 концевой комбинации фазового пуска, счетчик 19 зачетных отрезков, RS-триггер 20 управления режимом приема, RS-триггер 21 переключения вида приема, сумматор 22 по модулю два, элемент И 23, элемент ИЛИ 24, дополнительный приемный блок 25 сумматоров по модулю два, блок 26 ключей, дешифратор 27 комбинации окончания передачи информации, трехкаконцевой комбинации фазового пуска, счетчик 19 зачетных отрезков, RS- триггер 20 управления режимом приема, RS-триггер 21 переключения вида приема, сумматор 22 по модулю два, эле- мент И 23, элемент РШИ 24, дополнительный приемный блок 25 сумматоров по модулю два, блок 26 ключей, дешифратор 27 комбинации окончания передачи информатора, трехканальный мультиплексор 28, выделитель 29 фронта, счетчик 30 циклов и двухканальный мультиплексор 31. 1 ил.

нальный Ь1ультиплексор 28, выделитель фронта 29, счетчик 30 циклов и двухканальный мультиплексор 31. , Система работает следующим обраЗОМ..

В исходном состоянии на передающей стороне RS-триггер 2 управления режимом приема находится в нулевом состоянии, что обеспечивает сигнал на его

инверсном выходе, который удерживает по установочному R-выходу RS-триггер 10 режима передачи непосредственно, а передающий п-разрядный регистр сдвига - через первый элемент ИЛИ 7

в нулевом состоянии. При этом сигналом с инверсного выхода RS-триггера 10 режима передачи обеспечивается установка и удержание счетчика 11 циклов в нулевом состоянии и включение каналов X п-канального мультиплексора 9. Нулевое состояние передающего п-разрядного регистра 5. сдвига дешифрируется дешифратором 14, сигнал с выхода которого при этом обеспечивает включение режима параллельной записк по P/S входу управления режимом записи передающего п-разрядиого регистра 5 сдвига. За счет включения каналов X п-канального мультиплексора

9 обеспечивается подключение на U- вход последовательной записи передающего п-разрядного регистра 5 сдвига основного блока 4 сумматоров по модулю два и на D-входы передающего

п-разрядного регистра 5 сдвига сигнала с инверсного выхода к RS-триггера

.

10 режима передачи. Поступающие на тактовый С-вход регистра 5 и счетный С-вход счетчика 11 циклов тактовые импульсы с выхода генератора 6 такто вых импульсов не вызывают их работы из-за наличия сигнала на их установочных R-входах, Описанное состояние сохраняется до поступления сигнала с входа Начало передачи передающей части. На приемной стороне при этом RS-триггер 20 управления режимом приема и RS-триггер 21 переключения вид приема находятся также в нулевом состоянии. Сигнал с инверсного выхода RS-триггера 20 обеспечивает включени каналов X двухканального мультиплексора 31, а сигнал с инверсного выход RS-триггера 21 - включение каналов X трехканального мультиплексора 28 и установку и удержание в нулевом состоянии счетчика 30 циклов. Включение каналов X трехканального мультиплексора 28 обеспечивает подключение к J-входу второго канала двухканального мультиплексора 31 и входу сумматора 22 по модулю два выхода основного приемного блока 17 сумматоров по модулю два, к установочному S-входу RS-триггера 20 основного выхода счет- чика 19 зачетньгх отрезков и к Y-входу первого канала двухканального мультиплексора 31 выхода приемного дешифратора 18 концевой комбинации фазового пуска. Включение каналов X двух- канального мультиплексора 31 обеспечивает подключение J-входа последовательной записи приемного п-разрядного регистра 16 сдвига к выходу Бит синхронного демодулятора 15 через второй канал двухканального мультиплексора 31 и отключение установочных R- и S-входов соответственно RS- триггеров 20 и 21 по первому каналу мультиплексора 31. Таким образом передающая часть оказывается подготовленной к передаче информации, начинающейся с передачи сигнала фазового пуска, а приемная часть - к приему информации, начинающемуся с приема сиг нала фазового пуска.

Процесс передачи информации начинается с поступления сигнала с входа Начало передачи передающей части, при этом происходит установка по S-пходу RS-триггера 2 управления и ратречиение работы передающего п-раз- рядпого регистра 5 сдвига за счет снятия удерживающего сигнала с его

I О I

R-входа. Под дгГк .пчюм псрнспч) так-, тового импульсл от генератор, 6 так товых импульсов в разряды регистра производится параллельная запись начальных условий рекуррентной последовательности фазового пуска. Установка начальных условий обеспечипает ся подачей на соответствуюп1ие D-BXO- ды разрядов регистра 5 сигнала с инверсного выхода RS-триггера 10 через Х-каналы п-канального мультиплексора

9и сигнала на P/S-вход регистра 5. По последующим импульсам от генератора 6 происходит выработка символов peKyppeHTHofi последовательности фазового пуска. Характер рекуррентной последовательности фазового пуска задается соответствующим соединением сумматоров по мoдyJ ю два блока 4 сумматоров по модулю два и соответствующим подключением к выходам разрядов регистра 5 сдвига. Процесс передачи последовательности фазового пуска длится до окончания его периода. В момент окончания периода последовательности фазового пуска-на выходе дешифратора 3 формируется сигнал, который через элемент И 1 и элемент ИПК 8 поступает на пьгход Запрос информации на передачу передающей части, установочный S-нход RS-Tpni-repa

10и через элеме)п- lUlU 7 на установочный R-вход регистра 5. RS-триггер 10 под деГ1Ствием этого сигнала переключается, что обеспсчинаст включение каналов Y мультиплексора 9. Регистр

5 устанавливается в нулевое состояние, что обеспечивает на P/S-входе с выхода дешифратора 27 сигнал включения режима параллельной записи в регистр 5.

По сигналу Запрос информации на входы Передаваемая информация передающей части подаются значения комбинации передаваемой информации. Практически это может осуществляться либо со стартстопного трансмиттера, либо с накопителя в виде буферной памяти. Сигналы с входов Передаваемая информация через соответствующие Y-каналы мультиплексора 9 поступают на D-входы разрядов регистра 5 сдвига. На Y-вход последовательной записи регистра 5 через первый канал мультиплексора 9 поступают сигналы с выхода блокл 13 сумматоров по модулю два. Под действием очередного тактового импульса от гемсратоpa 6 происходит запись в регистр 5 значений передаваемой информации в виде начальных условий М-последова- тельности, вьфабатыпаемой в соответ- ствим с обратными связями, задаваемыми соединением сумматоров по модулю два блока 13 сумматоров по модулю дпа, и подключением к соответ-- стиующим выходам разрядов регистра 5 сдвига. За счет снятия удерживающего сигнала с R-входа счетчика 11 диклов нри установке КЗ-трип ера 10 счетчик 11 начинает подсчет импульсов, поступающих на его счетньш С- |ВХод от генератора 6. Емкость счетчика 11 циклов устанавливается на единицу больше числа разрядов М-носле- довательно.с и. Передача значений М-последовательности происходит до поянления сш нала на выходе счетчика 11, фронт которого выделяется выделителем 12 фронта. Сигнал с выделителя 12 фронта через элемент ИЛИ 7 устанавливает в нулсиос состояние регист 5 сдвига и поступает на выход Запрос и)1формации на передачу передающей стороны, при происходит дополнительное под 1чич1ядт,ение установки но S-входу RS-ipHjTcpa 10. Процессы п lit. рецсШ щеи ч.ттн при передаче вто- pofi и последующих К(1мби1 лций проте- ivnioT таь/кс , клк ч njiH передаче пер- ьои комбинации. Зав(ри1ается передача г|(цачеГ| на r:xo/i Передаваемая инфор- . 11,111)й комбинации окончания передачи по сигналу запроса и сигнала на нход Конец передачи но сигналу Запрос информации на передачу, следующему после передачи комбинации окончания передачи,

Сигнан поступак11Щ1Й на синхронный демодулятор 15, который осуществляет выделение,значений посылок принимаемого сигнала. В процессе демодуляции значений посылок на выходе Бит демодлятора формируются сигналы посыпок, синхронные с сигналами на выходе Такт демодулятора 15.

Сигналы с выхода Бит демодулятора 15 поступают через второй канал мул))Типлексора 31 на 3-вход последовательной записи приемного регистра 16. По сигналам с выхода Такт демодулятора 15 производится запись значений демодулированного сигнала в разряды регистра 16. Основной прием- Hbrfi блок 17 сумматоров по модулю два в соответствии со значениями сигна

5

0

лов, записанными в регистр 16, вырабатывает сигналы, ко1чн1ые через первый канал трехканального мультиплексора 28 подаются для сравнения со значениями демоду1Н1ропанньгх сигналов в сумматоре. 22 по модулю два. Если искажения в линии связи отсутствуют, то после заполнения всех разрядов регистра 16 на выходе основного приемного блока 17 значения сигналов бу- цут соответствовать значениям демо- дулированньгх сигналов на выходе Бит демодулятора 15. Это условлено тем, что на передающей и прием- . ной сторонах использованы индентичные блоки 4 и 17 сумматоров по модулю два и их точки подключения к выходам разрядов регистров 5 и 16. При совпадениях значений сигналов с выхода БИТ демодулятора 15 и блока 17 сумматоров по модулю два отсутствует сиг нал на выходе сумматора 22 по модулю два, что приводит к запрету проЪ хождения сигналов с выхода Такт демодулятора 15 через элемент И 23 и элемент ИЛИ 24 на установочный R-вход счетчика 19 зачетных отрезков, Счетчик 19 начинает счет сигналов

;() Такт, пос гупанччих на его счетный С-вход с выход.ч TaKi демодулятора 15, отмечая число 1гринимаем)1х без искажений рек-уррентной последовательности фазового цуска. Емкость счетчика 19 но основному выходу выбирается из условия обеспечения требуемой от ложного приема фазового пуска. Безошибочный прием подряд идущих разрядов рекуррентной последовательности фазового пуска в числе, равном объему счетчика 19 зачетных отрезков, сопровождается формированием сигна.па на его выходе. Ложные накопления сигналов в счетчике 19 иск-

5 лючается за счет его установки .по R-.входу при Ka;tu;oM обнаружении несоответствия сигналов на входах сумматора 22 по модулю два. Сигнал с выхода счетчика 19 через второй канал трехканального мультиплексора 28 поступает на установочный S-БХОД RS- триггера 20.

При переключении RS-триггера 2U включаются каналы Y двухканальног о

5 мультиплексора 31, при этом через

второй канал Nr/льтиплексора 31 производится переключение J-входа регистра 16 с выхода Бит демодулятора 15 на вход блока 17 сумматоров но модулю

0

0

7 . 133 два, а через первый канал мультиплексора 31 - подключение установочных R- и S-входов соответственно R.S- трш геров 20 и 21 к выходу дешифратора 18. С этого момента регистр 16 работает в автономном режиме генерирования рекуррентной последовательности фазового пуска в соответствии с

обратными связями своих выходов через ю М-последовательности, совпадающие с

20

30

блок 17 сумматоров по модулю два. За счет подачи сигнала с прямого выхода RS-триггера 20 через элемент ИЛИ 2А на установочный R-вход счетчика 19 последний устанавливается и удержива- 15 ется в нулевом состоянии. Работа регистра 16 в режиме автономной генерации рекуррентной последовательности фазового пуска продолжается до завершения периода последовательности, при этом на выходах разрядов регистра 16 устанавливается комбинация, которая дешифрируется дешифратором 18 сигналом на его выходе. Сигнал с выхода дешифратора t8 через третий канал мультиплексора 28 и первый канал мультиплексора 31 поступает на установочные R- и S-входы соответственно RS-триггеров 20 и 21. Установка RS- триггера 20 по R-входу вызывает переключение каналов мультиплексора 31 и снятие сигнала с установочного К-входа счетчика 19. Установка RS- триггера 21 по S-входу приводит к включению каналов мультиплексора 28 и снятию сигнала с установочного R-входа счетчика 30 подаваемого с инверсного выхода RS-триггера 21. Переключение мультиплексоров 31 и 28 приводят к следующему. Через первый канал мультиплексора 28 выход дополнительного блока 25 сумматоров по модулю два подключается к Y-входу .канала мультиплексора 31 и входу сумматора 22 по модулю два, через второй 45 канал мультиплексора 28 дополнитель- Hbrfi выход счетчика 19 подключается к установочному S-входу RS-триггера 20, и выход счетчика 30 через выделитель фронта и третий канал мультиплексора 28 подключается к Y-входу первого канала мультиплексора 31. Указанные переключения обеспечивают установленные синхронизации с М-пос- ледонательностью, передаваемой после пе редачи рекуррентной последовательности фазового пуска. Если принимаемые разряды М-последовательности не искажены, то после заполнения всех

принимаемыми, В этом случае счетчик 19 начинает фиксировать прием зачетного отрезка М-последовательности. Емкостью счетчика 19 по дополнительному, -выходу устанавливается длина за четного отрезка, определяемая из условий обеспечения требуемой помехо устойчивости приема информации. С момента переключения RS-триггера 21 счетчик 30 осуществляет счет тактовых импульсов, поступающих на его счетный С-вход с выхода Тпкт демодулятора 15. Емкость счетчика выбира ется равной периоду М-последовательности, yвeличeннo ry на один такт. После приема зачетного отрезка ледовательностй установленной длины на дополнительном выходе счетчика 19

иает по S-входу RS-триг-грр 20. С этого момента рег истр 16 вырабатывает автономно М-последовательность до окончания ее периода и установки значения, соответствующего первому такту j М-последовательности. Одновременно с этим на выходе счетчика 30 появляется сигнал, фронт которого.выделяется выделителем 29 фронта. Сигнал с выхода выделителя 29 фронта поступает 40 на выход разрешение на получение информации приемной стороны, управляющий вход блока 21 ключей и установочные R- и В-входы -соответственно RS-триггеров 20 и 21.

Изменение начальных условий генерирования М-последовательности приводит к циклическим перестановкам этой последовательности. Это свойство и используется при передаче информации, при этом каждой комбинации информации соответствует передача одной и той же М-последовательности с соответствующим этой комбинации сдвигом. При приеме за счет записи в ре- 55 гистр 16 сдвига значений принимаемой М-последовательностИ и индентичньсх точек подключения одинаковых блоков 13 и 25 сумматоров по модулю два соответственно к регистрам 5 и 16 про50

8

разрядов рег игтрс 1 Id riyi-ем :1Л11иси в рег истр 16 зипчоииГ 11а-чряц(1н М-посл доватсльности, поступанпцих г выхода Вит дсмодупяторл 15 нл J-вход регистра 16 черет птореи клнлл мультиплексора 31, на выходе дополнительного блока 25 cyM faTopoH по модулю два формируются значения разрядов

принимаемыми, В этом случае счетчик 19 начинает фиксировать прием зачетного отрезка М-последовательности. Емкостью счетчика 19 по дополнительному, -выходу устанавливается длина зачетного отрезка, определяемая из условий обеспечения требуемой помехоустойчивости приема информации. С момента переключения RS-триггера 21 счетчик 30 осуществляет счет тактовых импульсов, поступающих на его счетный С-вход с выхода Тпкт демодулятора 15. Емкость счетчика выбирается равной периоду М-последовательности, yвeличeннo ry на один такт. После приема зачетного отрезка ледовательностй установленной длины на дополнительном выходе счетчика 19

30

15 45

иает по S-входу RS-триг-грр 20. С этого момента рег истр 16 вырабатывает автономно М-последовательность до окончания ее периода и установки значения, соответствующего первому такту j М-последовательности. Одновременно с этим на выходе счетчика 30 появляется сигнал, фронт которого.выделяется выделителем 29 фронта. Сигнал с выхода выделителя 29 фронта поступает 40 на выход разрешение на получение информации приемной стороны, управляющий вход блока 21 ключей и установочные R- и В-входы -соответственно RS-триггеров 20 и 21.

Изменение начальных условий генерирования М-последовательности приводит к циклическим перестановкам этой последовательности. Это свойство и используется при передаче информации, при этом каждой комбинации информации соответствует передача одной и той же М-последовательности с соответствующим этой комбинации сдвигом. При приеме за счет записи в ре- 55 гистр 16 сдвига значений принимаемой М-последовательностИ и индентичньсх точек подключения одинаковых блоков 13 и 25 сумматоров по модулю два соответственно к регистрам 5 и 16 про50

91338101

сходит синхронизация вырабатываемой помоп1ью регистра 16 местной М-пос- едовательности с принимаемой.

Синхронизация последовательностей беспечивает формирование на выходах азрядов регистра 16 в первый тактоый интервал после последнего тактоого интервала периода М-последова- ельности комбинации начальных услоий, с которых генерировалась М-пос- едовательность на передающей сторое. Отсчет интервалов, равных увелиенному на единицу периоду М-последо- ательности, обеспечивает счетчик 30. ледовательно, в каждый момент выдеения фронта выделителем 29 фронта с выхода разрядов регистра 16 через блок 26 кл1очей на выходы Принятая информация приемной стороны поступает -комбинация, соответствующая комбинации передаваемой информации. Сигнал с выхода выделителя 29 фронта через третий каиап мультиплексора 28 и первый канал мультиплексора 31 производит установку по R-входу RS-триг- гера 20 и подтверждение по S-входу состояния RS-триггера 21. Переключение RS-триггера 20 вызывает включение Х-каналон мультиплексора 31, что переводит приемную чггсть, в )еж11м начала приема очередной информации. Прием очередной кс мбинации информации протекает аналогично приему первой комбинации информации после фазовот о пуска. Процесс приема информации завершается по приему комбинации о завершении передачи. Указанная комбинация дешифрируется дешифратором 27, и сигнал с его выхода устанавливает по R-входу RS-триггер 21. Переключение RS-триггера 21 обеспечивает включение каналов X мультиплексора 28 и установку и удержание по R-входу счетчика 30. Указанные переключения п1феБодят приемную часть в режим приема сигнала фазового пуска, после приема которого становится возможным новый прием информации.

та по ра

g Ко су то во ст

10 жи ви эл че ко

15 ст Свыпр дв

20 ко

те

25

30

ЗГ)

40

45

ус вв ро во ко бл хо вв со вы р {Щ вх м с вы в т т л п х п м

Формула изобретения

Система передачи и приема информации рекуррентными последовательностями, содержащая на передающей стороне RS-триггер управления, З-вход которого является входом сигнала Начало передачи, а R-вход - входом сигнала Конец передачи, генератор

101

10

тактовых импульсов, выход которого подключен к С-входу передающего п- разрядного регистра сдвига, выходы

Которого подключены к входам блока сумматоров по модулю два и дешифратора, выход которого подключен к первому входу элемента И, а на приемной стороне - RS-триггер управления режимом приема, RS-триггер переключения вида приема, сумматор по модулю два, элемент И, элемент ИЛИ, счетчик зачетных отрезков, демодулятор, вход которого является входом приемной

5 стороны, тактовый выход подключен к Свходу п-разрядного регистра сдвига, выходы которого подключен к входам приемного блока сумматоров по модулю два и приемного дешифратора концевой

0 комбинации, отличающ

тем, что, с целью повьш1ения

а я с я помехо- стороне

5

0

Г)

0

5

0

55

устойчивости, на передающей введены дополнительный блок сумматоров по модулю два и дешифратор нулевого состояния регистра, к входам которых подключены входы основного блока сумматоров по модулю два, вы- ход которого соединен с X,-входом введенного п-канального мультиплексора, к Y,-входу которого подключен выход дополнительного блока сумматоров по модулю два, первый элемент {ЩИ, второй элемент ПЛИ, к первому входу которого подключен выход элемента И, последовательно соединенные счетчик циклов и вьщелитель фронта, выход которого подключен к второму входу второго элемента ИЛИ, выход которого подключен к S-входу введенного RS-триггера режима передачи и первому входу первого элемента ИЛИ, ;( второму входу которого подключен выход RS- триггера управления и вход триггера режима передачи, S-вход которого является входом Запрос информации на передачу, а прямой и инверсный выходы соединены с управляющими входами п-канального мультиплексора, (Х-1)-е входы которого подключены к инверсному выходу RS-триггера режима передачи, (Y-1) входы являются входами Пе- редалаемая информаиия, первый выход янляется выходом передающей стороны и подключен к Л-входу передающего п-разрядного регистра сдвига, к D- входам которого подключены (п-1)-е выходы п-канального му.чьтиплексора, к входу подключен выход первого элемента ИЛИ, а к Р/S-входу подключен

выход дешифратора нулевого состояния регистра, при этой второй вход элемента И и R-вход счетчика циклов подключены к инверсному выходу RS-триг- гера режима передачи, а S-вход счетчика циклов подключен к выходу генератора тактовых импульсов, а на приемной стороне введены дополнительный приемный блок сумматоров по модулю два, блок ключей, дешифратор комбинаций окончания передачи информации, выход которого подсоединен к R-входу RS-триггера переключения вида приейа,

10

му выходам RS-триггера переключения вида приема, S-вход которого соединен с первым выходом двухканального мультиплексора и R-входом RS-триггера управления режимом приема, инверсный и прямой выходы которого соединены соответственно с первым и вторым управляющими входами двухканального мультиплексора и через элемент ИЛИ с R-входом счетчика зачетных отрезков, С-вход которого подключен к такпервый, второй и третий выходы трех- канальното мультиплексора соединены соответственно с Yj-выходом двухкатовому выходу демодулятора и С-входу счетчика циклов, R-вход которого под- трехканальный и двухканальный мульти- is ключе А к инверсному выходу RS-триг- плексоры, последовательно соединенные гера переключения вида приема, а счеТчик циклов и выделитель фронта, выход которого подключей к первому входу блока ключей, выход которого

подключен к входам дешифратора ком- 20 нального мультиплексора и первым вхо- бинации окончания передачи и является дом сумматора по модулю два, второй выходами сигналов принятия комбина- вход которого и Х -вход двухканаль- ции, к Yj-входу трехканального муль- ного мультиплексора подключены к вы- типлексора и является выходом сигнала ходу Бит демодулятора, З-входу

25 RS-триггера управления режимом приема и Y, -входу двухканального мультиплексора, второй выход которого соединен с J-входом п-разрядного регистра сдвига, выходы которого соедиразрешения на получение информации, при этом к Х -входу трехканального мультиплексора подключен выход основного приемного блока сумматоров по модулю два, к Y(-входу - выход дополнительного приемного блока сумматоров зо нены с входами дополнительного припо модулю два, к и Yj-входам - выходы счетчика зачетных отрезков, к ХЗ-ВХОДУ - выход приемного дешифратора концевой комбинации фазового

пуска, а входы управления подключены и, второй вход которого подключен к соответственно к прямому и инверсно- тактовому выходу демодулятора.

Редактор А.Огар

Составитель И.Грацианская

Техред И.Попович Корректор Л.Рескид

Заказ 4148/58Тираж 638Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

му выходам RS-триггера переключения вида приема, S-вход которого соединен с первым выходом двухканального мультиплексора и R-входом RS-триггера управления режимом приема, инверсный и прямой выходы которого соединены соответственно с первым и вторым управляющими входами двухканального мультиплексора и через элемент ИЛИ с R-входом счетчика зачетных отрезков, С-вход которого подключен к такпервый, второй и третий выходы трех- канальното мультиплексора соединены соответственно с Yj-выходом двухкатовому выходу демодулятора и С-входу счетчика циклов, R-вход которого под- ключе А к инверсному выходу RS-триг- гера переключения вида приема, а

нального мультиплексора и первым вхо- дом сумматора по модулю два, второй вход которого и Х -вход двухканаль- ного мультиплексора подключены к вы- ходу Бит демодулятора, З-входу

емного блока сумматоров по модулю два и блока ключей, причем к второму входу элемента ИЛИ подключен выход сумматора по модулю два через элемент

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема сигналов начальной синхронизации | 1987 |

|

SU1543559A1 |

| Устройство для передачи сигналов начальной синхронизации | 1985 |

|

SU1338100A1 |

| Система передачи дискретной информации | 1986 |

|

SU1406806A1 |

| Устройство фазового пуска | 1984 |

|

SU1225035A1 |

| Устройство для передачи и приема дискретной информации | 1988 |

|

SU1529459A1 |

| Устройство для приема сигналов начальной синхронизации | 1986 |

|

SU1427585A1 |

| Устройство для передачи и приема дискретной информации | 1987 |

|

SU1443178A1 |

| Устройство для передачи сигналов синхронизации | 1985 |

|

SU1241508A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2005 |

|

RU2284668C1 |

| СИСТЕМА СЕАНСНОЙ СВЯЗИ | 1992 |

|

RU2027312C1 |

Изобретение относится к технике передачи дискретной информации и обеспечивает повышение помехоустойчивости. Система содержит на перед ю- |цей стороне элемент И 1 , RS-триггер 2 управления, дешифратор 3, основной г .1 4- Передоёаемоя { информация Запрос с/ - Формо:4и напередоид т Начало передачи Конец передачи Ш 4711 iLrп Г 7Ьат Stu (Л со со 00 ниена nowveffiff (b(/

| Мартынов Б.М | |||

| Синхронизация в системах передачи дискретных сообщений | |||

| М.: Связь, 1972, с.199-200, рис.11.10 и 11.11. |

Авторы

Даты

1987-09-15—Публикация

1985-10-09—Подача